# **NetFPGA: Cambridge Spring School**

# Presented by:

# **Andrew W. Moore and David Miller**

(University of Cambridge)

(Brno University of Technology)

Nadi Sarrar

(TU-Berlin/T-Labs)

Cambridge, UK - March 15-19, 2010

http://NetFPGA.org

SNPIFPGA NetFPGA Cambridge Spring School 15-19 Mar 2010

UNIVERSITY OF BOOTEAR

# Welcome

# Please organize into teams 2 or 3 People/computer

# **Wireless network for Cambridge Guests**

SSID: as written on whiteboard (wired connections also available)

# The NetFPGA machines

Username: root Password: on whiteboard

NetFPGA homepage http://NetFPGA.org

# **Spring School Schedule**

Day 1 - Monday 15th March, 2010

00 - 10:30 Session I

Introduction, background, Stanford Reference Router

11:00 - 12:30 Session II

Research with the NetFPGA, Enhanced Reference Router

13:45 - 15:15 Session III

Life of a Packet, Datapath, Extending the Router – an example

15:45 - 17:00 Session IV

Further hardware platforms, NetFPGA in research and teaching, group discussion

18:00 Punt trip – weather dependent 19:30 Dinner – India House

Day 2 - Tuesday 16th March, 2010

9:00 - 10:30 Session V

Openflow on NetFPGA 11:00 – 12:30 Session VI

Introducing Module development in the

13:45 – 15:15 Session VII

Implement verification test

(for use against the ModelSim simulator)

15:45 – 17:00 Session VIII

Implement hardware regression test allowing

mechanised testing of your new module

NetFPGA Cambridge Spring School 15-19 Mar 2010

Day 3 – Wednesday 17th March, 2010

8:30 – 9:30 Group discussion Projects ideas

Scope of work that can be accomplished in 2-3 days

Team up for Projects

Project leaders will describe projects

Group will provide feedback on the scope

Be sure to have one hardware designer per team

16:00 – 17:30 Example Hardware Designs

Background and review of block diagrams Show design running on nf-test machines including

a demonstration of running code Discuss relevant Verilog Code

Day 4 - Thursday 18th March, 2010

9:00 - 17:30 Work on Projects

NetFPGA users available for Questions and Answers

Day 5 - Friday 19th March, 2010

9:00 - 15:15 Complete Projects

NetFPGA, Implement an example module 15:45 – 17:30 Final Session

10-minute project presentations. Live demonstrations Award prizes to winning projects

Group Dinner at 7A Jesus Lane

# **Day 1: Tutorial Outline**

### Background

- Introduction

- Basics of an IP Router

- The NetFPGA Platform

### The Stanford Base Reference Router

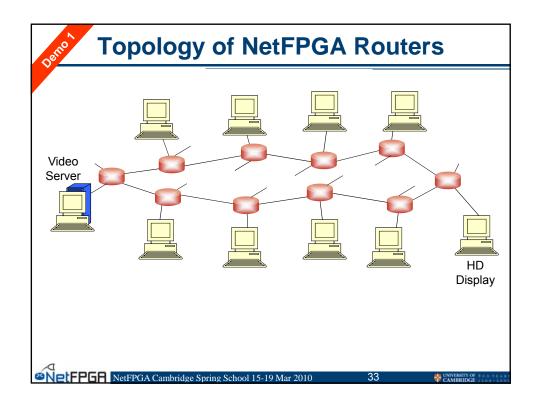

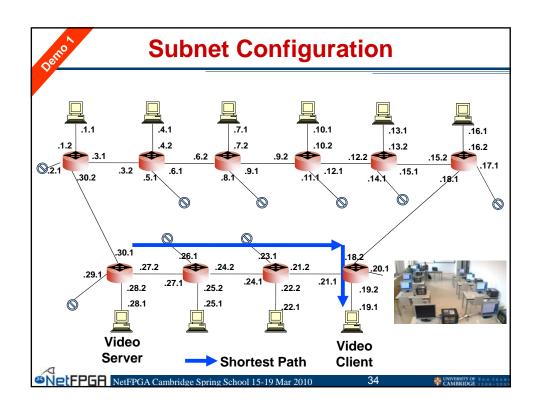

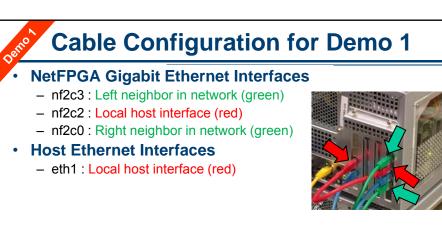

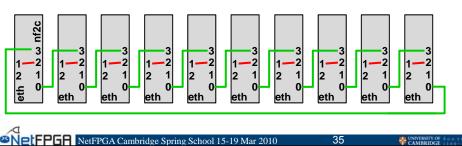

- Demo1: Reference Router running on the NetFPGA

- Inside the NetFPGA hardware (Andrew)

- Breakneck introduction to FPGAs and Verilog

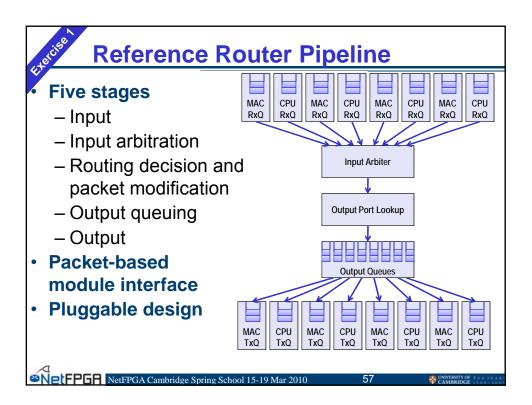

- Exercise 1: Build your own Reference Router

# The Enhanced Reference Router

- Motivation: Understanding buffer size requirements in a router

- Demo 2: Observing and controlling the queue size

- Exercise 2: Enhancing the Reference Router

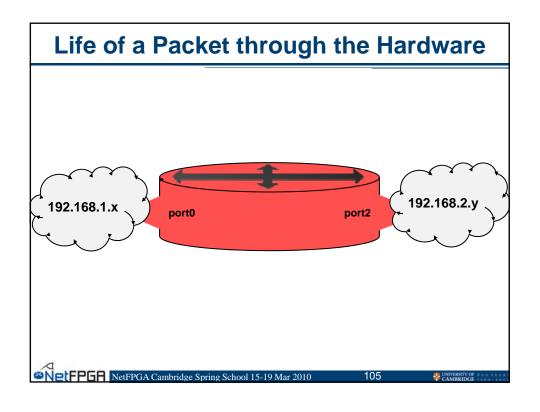

# The Life of a Packet Through the NetFPGA

- Hardware Datapath

- Interface to software: Exceptions and Host I/O

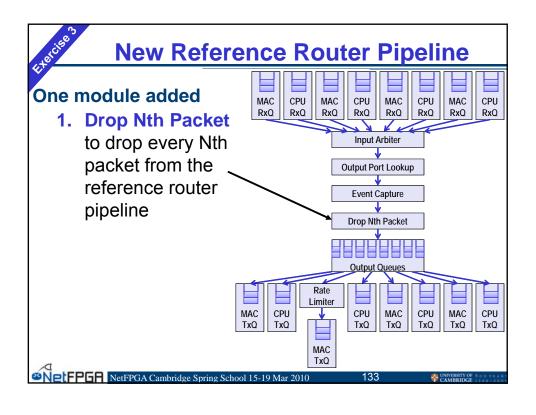

- Exercise 3: Drop 1 in N Packets

### Concluding Remarks

- Additional Hardware Platforms

- Using NetFPGA for research and teaching

- Group Discussion

# Who, How, Why

# Who uses the NetFPGA?

- Teachers

- Students

- Researchers

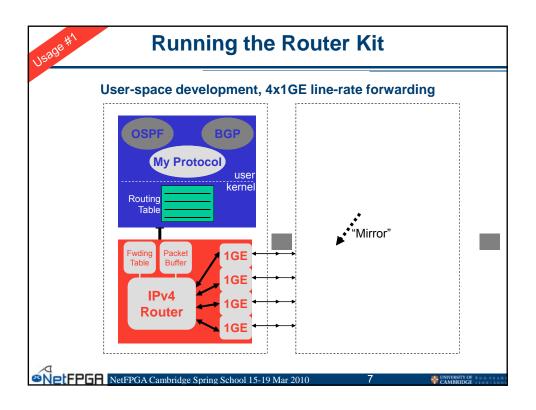

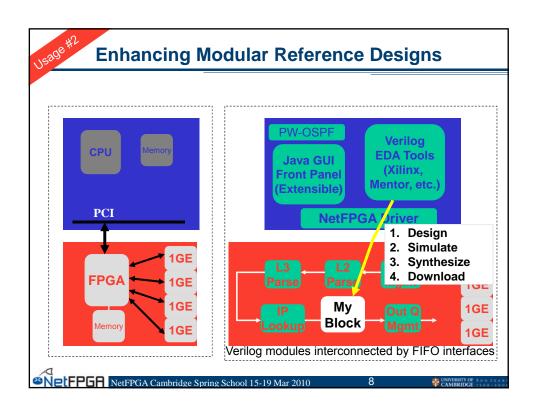

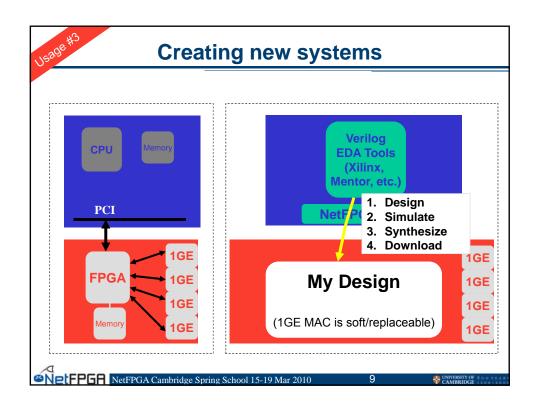

# How do they use the NetFPGA?

- To run the Router Kit

- To build modular reference designs

- IPv4 router

- 4-port NIC

- Ethernet switch, ...

# Why do they use the NetFPGA?

- To measure performance of Internet systems

- To prototype new networking systems

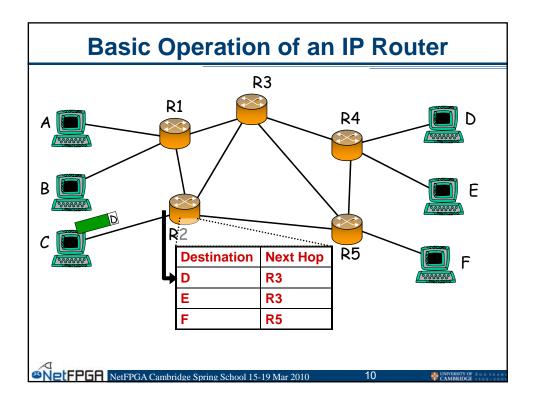

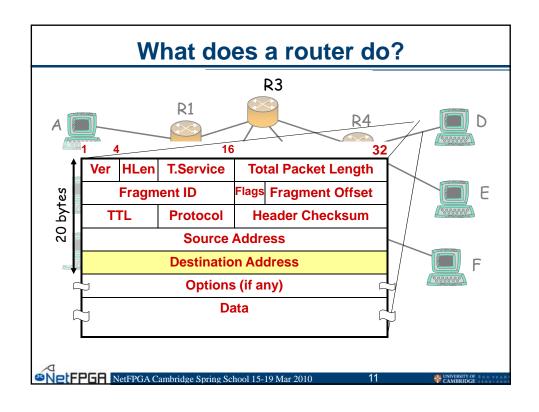

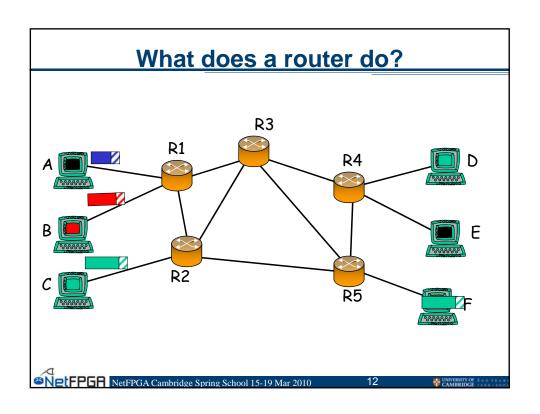

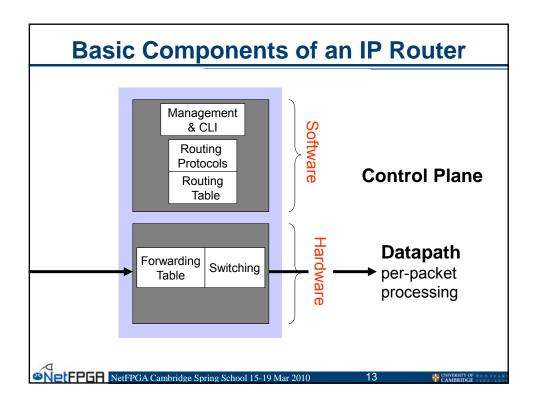

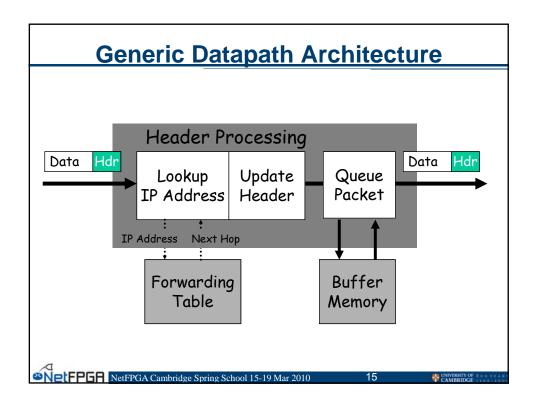

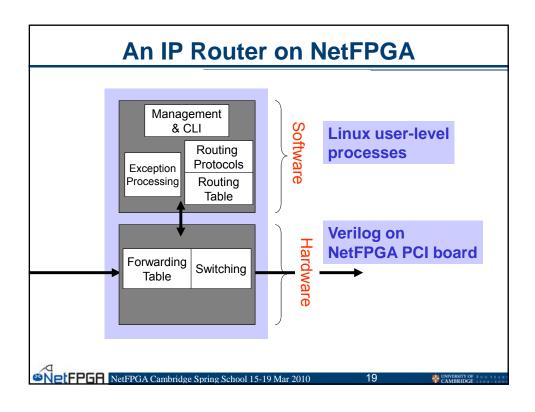

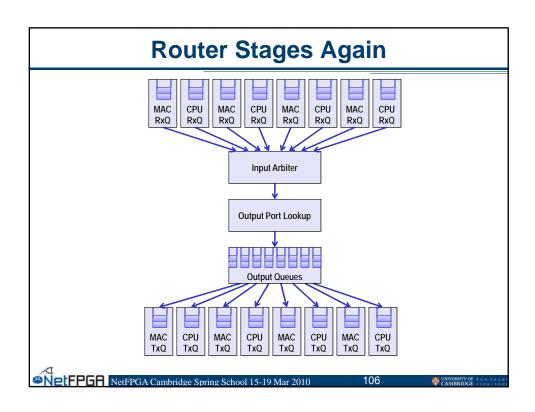

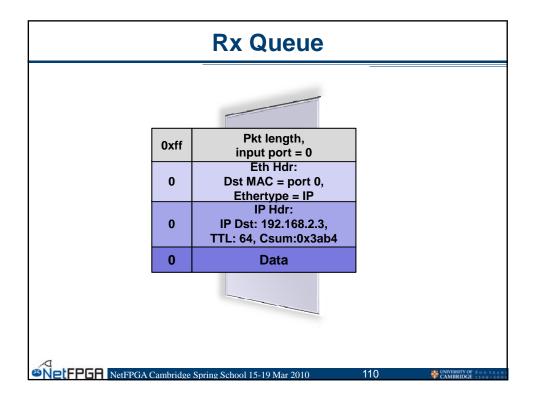

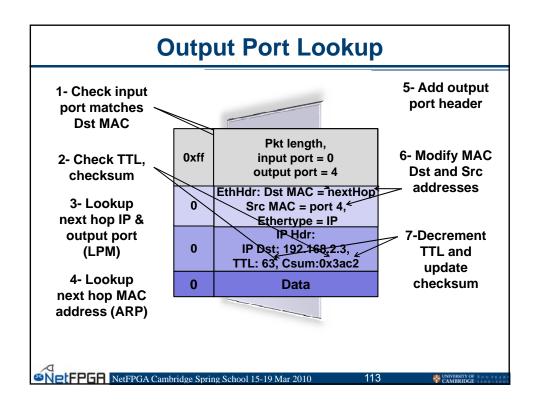

# Per-packet processing in an IP Router

- 1. Accept packet arriving on an incoming link.

- 2. Lookup packet destination address in the forwarding table to identify outgoing port(s).

- 3. Manipulate IP header: e.g., decrement TTL, update header checksum.

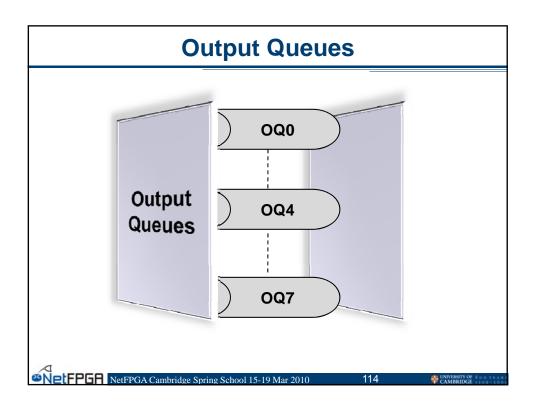

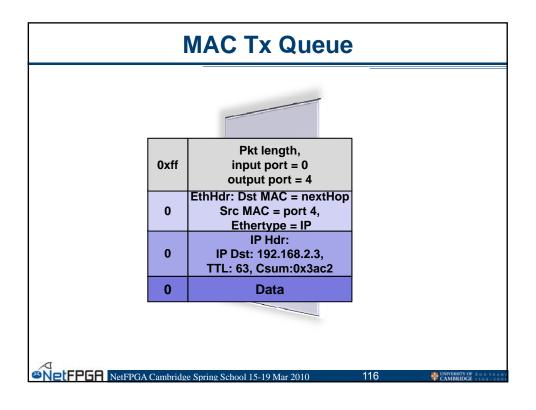

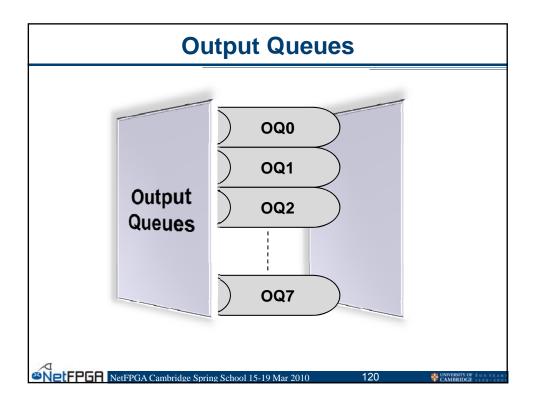

- 5. Buffer packet in the output queue.

- 6. Transmit packet onto outgoing link.

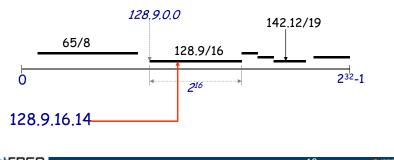

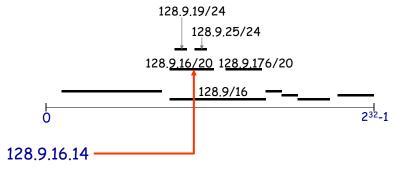

# **CIDR and Longest Prefix Matches**

- The IP address space is broken into line segments.

- \* Each line segment is described by a prefix.

- A prefix is of the form x/y where x indicates the prefix of all addresses in the line segment, and y indicates the length of the segment.

- e.g. The prefix 128.9/16 represents the line segment containing addresses in the range: 128.9.0.0 ... 128.9.255.255.

Most specific route = "longest matching prefix"

NetFPGA Cambridge Spring School 15-19 Mar 2010

17

UNIVERSITY OF BOOYEAR

# **Techniques for LPM in hardware**

- Linear search

- Slow

- Direct lookup

- Currently requires too much memory

- Updating a prefix leads to many changes

- Tries

- Deterministic lookup time

- Easily pipelined but require multiple memories/references

- TCAM (Ternary CAM)

- Simple and widely used but have lower density than RAM and need more power

- Gradually being replaced by algorithmic methods

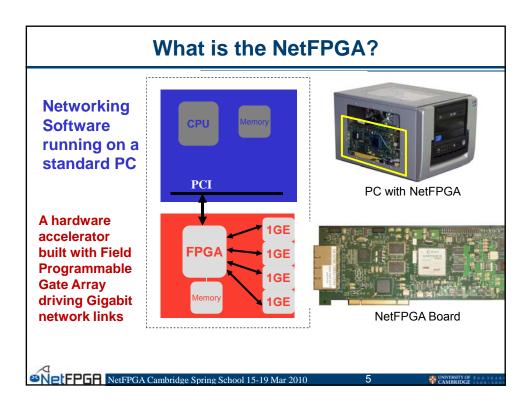

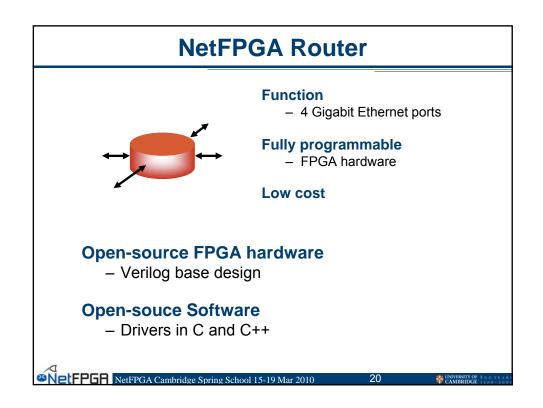

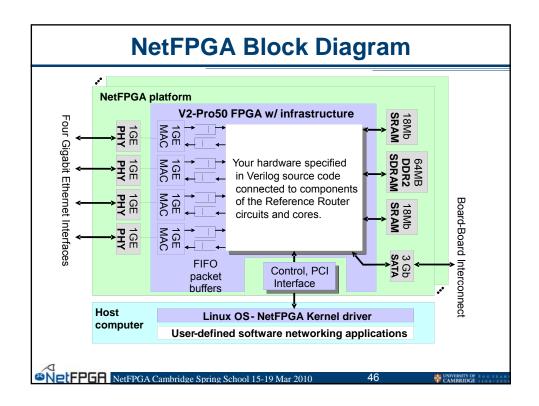

# **NetFPGA v2 Platform**

# **Major Components**

- Interfaces

- 4 Gigabit Ethernet Ports

- PCI Host Interface

# - Memories

- 36Mbits Static RAM

- 512Mbits DDR2 Dynamic RAM

# - FPGA Resources

- Block RAMs

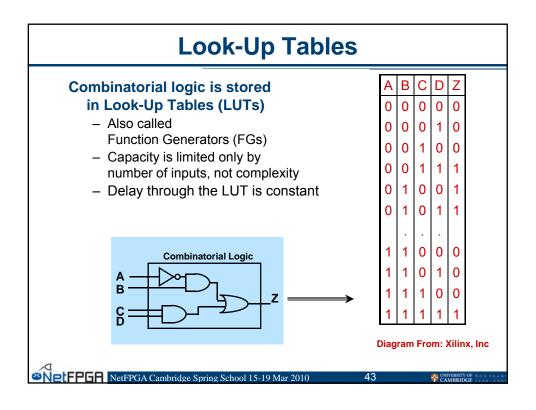

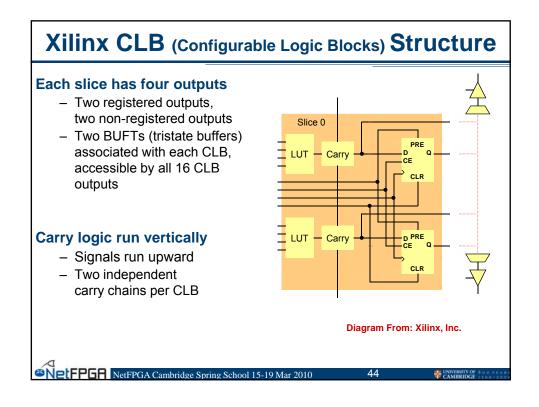

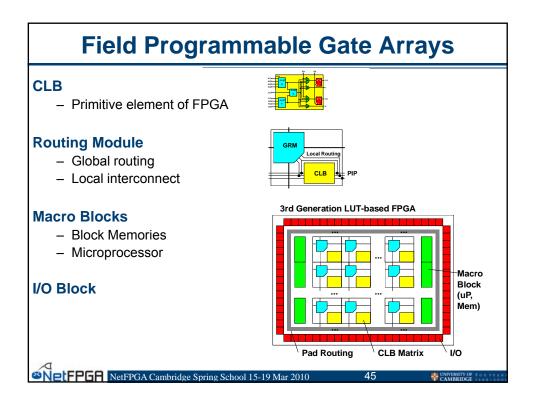

- Configurable Logic Block (CLBs)

- Memory Mapped Registers

NetFPGA Cambridge Spring School 15-19 Mar 2010

UNIVERSITY OF #00 YEAR

# **NetFPGA v2 Hardware Components**

- Xilinx Virtex-2 Pro FPGA for User Logic

Xilinx Spartan for PCI Host Interface

Cypress: 2 \* 2.25 MB ZBT SRAM

Micron: 64MB DDR2 DRAM

- Broadcom: PHY for 4 Gigabit Ethernet ports

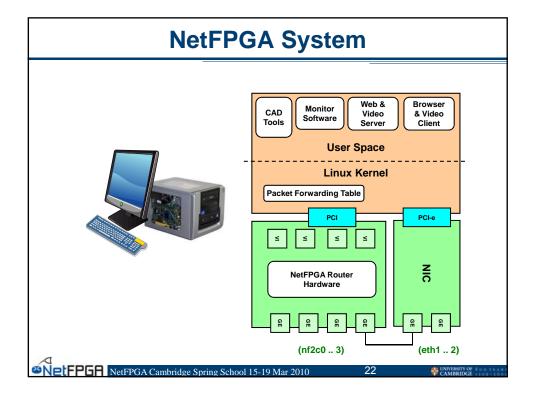

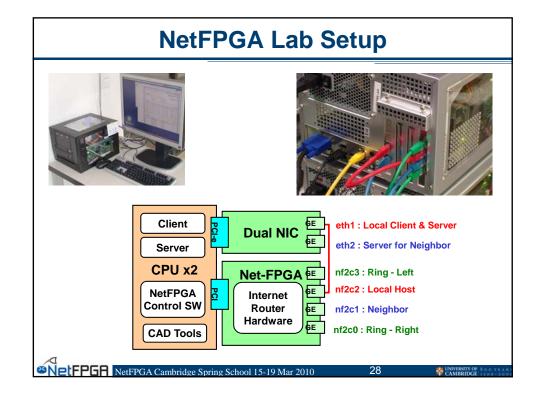

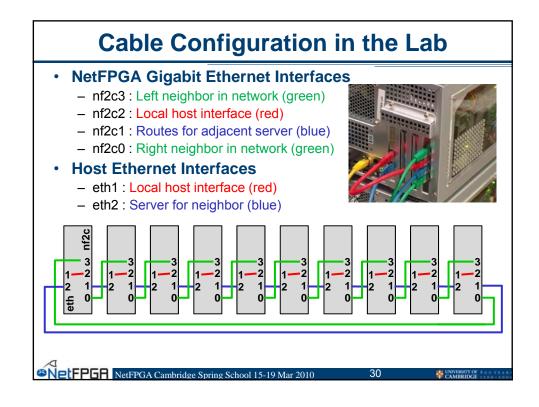

# **NetFPGA System Components**

- **Network Ports**

- Host PCI-express NIC

- Dual Gigabit Ethernet ports on PCI-express card

- NetFPGA

- Quad Gigabit Ethernet ports on NetFPGA PCI card

- **Motherboard**

- Standard AMD or Intel-based x86 computer with PCI and PCI-express slots

- **Processor**

- Dual or Quad-Core CPU

- **Operating System**

- Linux CentOS 5.2

# **NetFPGA Cube Systems**

- PCs assembled from parts

- Stanford University

- Cambridge University

- Pre-built systems available

- Accent Technology Inc.

- · Details are in the Guide

http://netfpga.org/static/guide.html

etFPGA Cambridge Spring School 15-19 Mar 2010

25

CAMBRIDGE

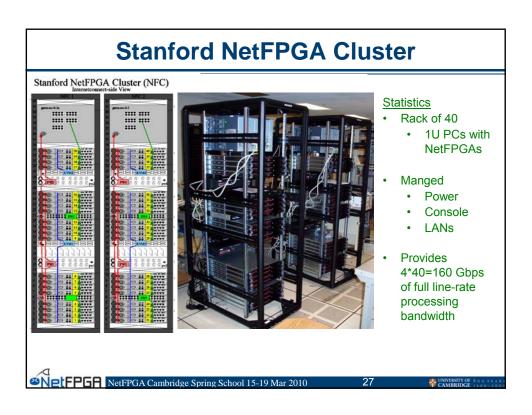

# **Rackmount NetFPGA Servers**

2U Server (Dell 2950)

NetFPGA inserts in PCI or PCI-X slot

Thanks: Brian Cashman for providing machine

NetFPGA Cambridge Spring School 15-19 Mar

26

UNIVERSITY OF BOOYEAR

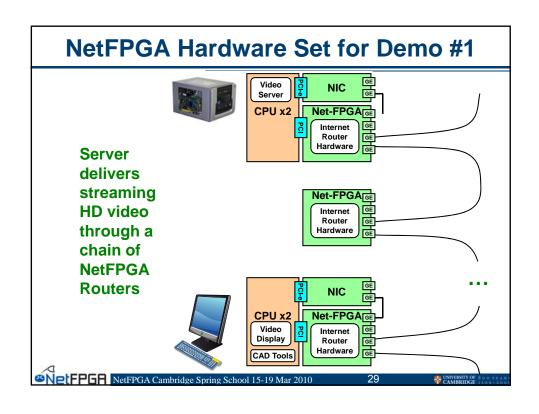

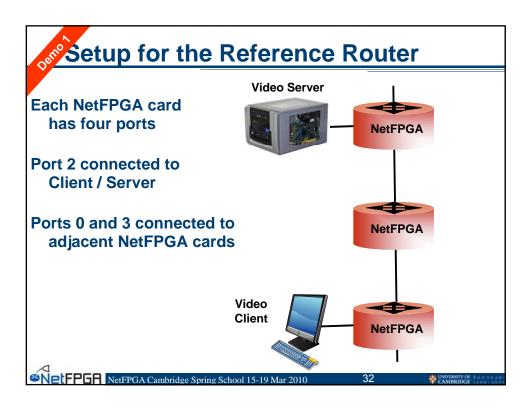

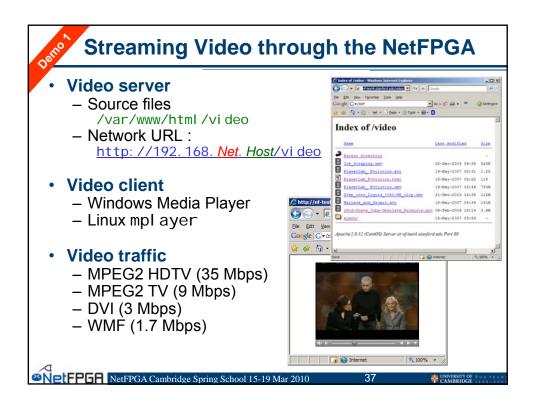

# Demo 1

# Reference Router running on the NetFPGA

Demo

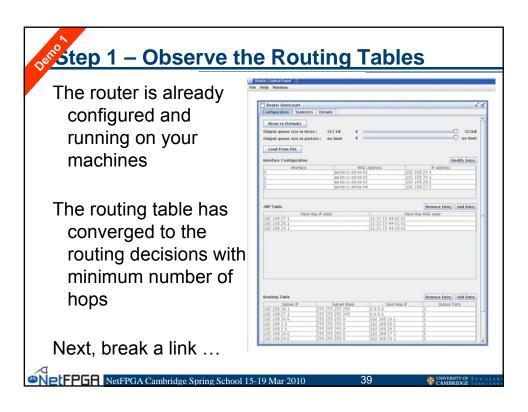

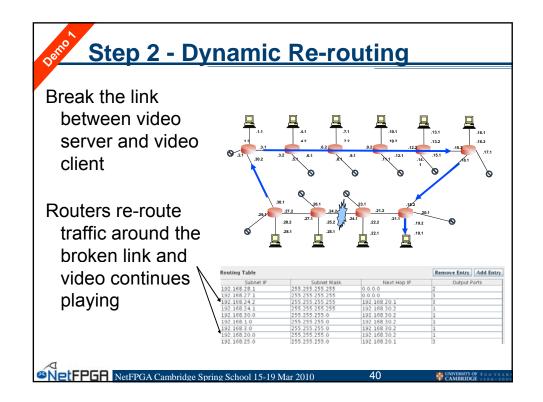

# **Working IP Router**

- Objectives

- Become familiar with

Stanford Reference Router

- Observe PW-OSPF re-routing traffic around a failure

# Integrated Circuit Technology And Field Programmable Gate Arrays (FPGAs)

NetFPGA Cambridge Spring School 15-19 Mar 2010

1

UNIVERSITY OF HOOTEAR

# **Integrated Circuit Technology**

# **Full-custom Design**

Complementary Metal Oxide Semiconductor (CMOS)

# **Semi-custom ASIC Design**

- Gate array

- Standard cell

# **Programmable Logic Device**

- Programmable Array Logic

- Field Programmable Gate Arrays

# **Processors**

- Network Processors

- General Purpose Processors

# **Details of the NetFPGA**

- Fits into standard PCI slot

- Standard Bus: 32 bits, 33 MHz

- · Provides interfaces for processing network packets

- 4 Gigabit Ethernet Ports

- Allows hardware-accelerated processing

- Implemented with Field Programmable Gate Array (FPGA) Logic

NetFPGA Cambridge Spring School 15-19 Mar 2010

47

UNIVERSITY OF BOOTEAR

# Introduction to the Verilog Hardware Description Language

# **Hardware Description Languages**

- Concurrent

- By default, Verilog statements evaluated concurrently

- Express fine grain parallelism

- Allows gate-level parallelism

- Provides Precise Description

- Eliminates ambiguity about operation

- Synthesizable

- Generates hardware from description

Net FPGA Net FPGA Cambridge Spring School 15-19 Mar 2010

49

UNIVERSITY OF BOOTEAS

# **Verilog Data Types**

```

reg [7: 0] A; // 8-bit register, MSB to LSB

// (Preferred bit order for NetFPGA)

```

reg [0: 15] B; // 16-bit register, LSB to MSB

$B = \{A[7:0], A[0:7]\};$  // Assignment of bits

reg [31:0] Mem [0:1023]; // 1K Word Memory

integer Count; // simple signed 32-bit integer

integer K[1: 64]; // an array of 64 integers

time Start, Stop; // Two 64-bit time variables

From: CSCI 320 Computer Architecture

Handbook on Verilog HDL, by Dr. Daniel C. Hyde:

<a href="http://eesun.free.fr/DOC/VERILOG/verilog-manual.html">http://eesun.free.fr/DOC/VERILOG/verilog-manual.html</a>

NetFPGA Cambridge Spring School 15-19 Mar 2010

50

UNIVERSITY OF BOOTEA

# D-type flip flop reg q; always @ (posedge clk) q <= d; D type flip flop with data enable reg q; always @ (posedge clk) if (enable) q <= d; From: http://eesun.free.fr/DOC/VERILOG/synvig.html

#

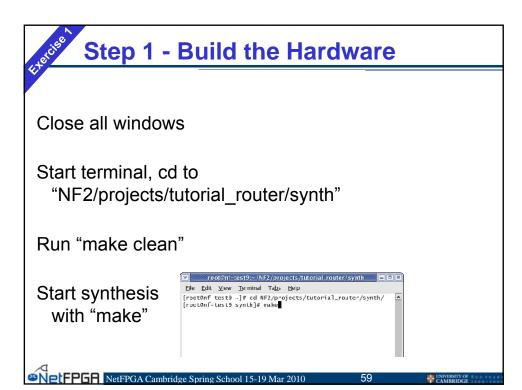

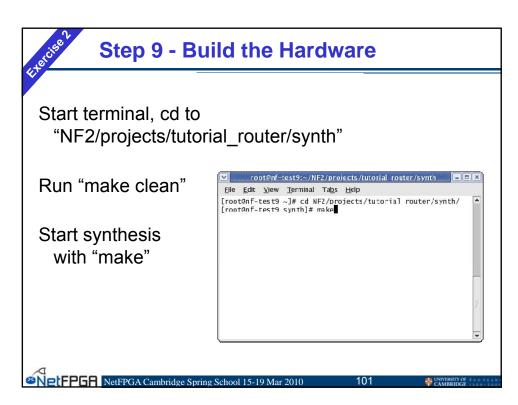

# Make your own router

# **Objectives:**

- Learn how to build hardware

- Run the software

- Explore router architecture

# **Execution**

- Start synthesis

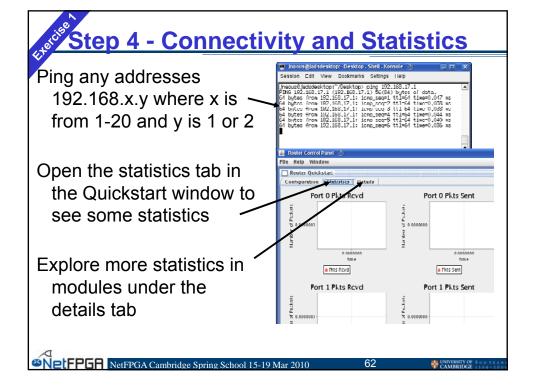

- Rerun the GUI with the new hardware

- Test connectivity and statistics with pings

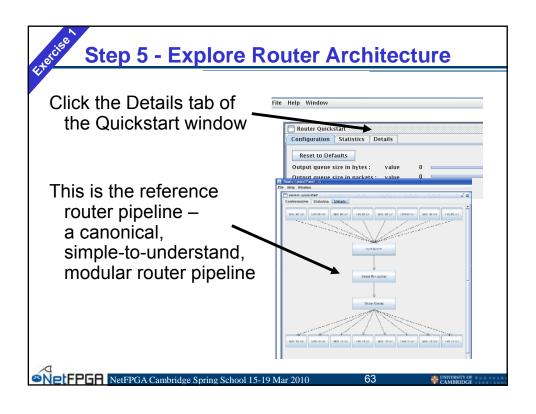

- Explore pipeline in the details page

- Explore detailed statistics in the details page

# **First Break**

(while hardware compiles)

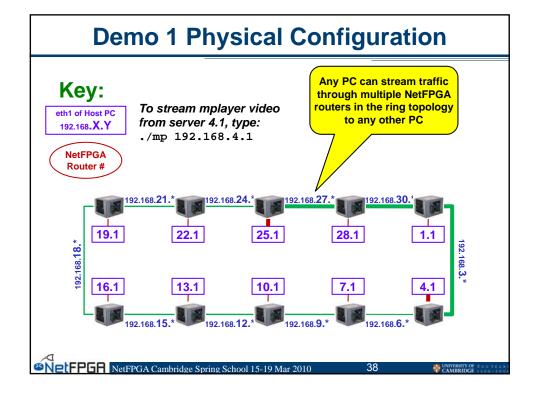

# Step 2 - Run Homemade Router

cd to "NF2/projects/tutorial\_router/sw"

To use the just-built router hardware, type:

./tut\_router\_gui.pl --use\_bin ../../bitfiles/tutorial\_router.bit

To stream video, run:

./mp 192.168.X.Y where X.Y = 25.1 or 19.1 or 7.1 (or other server as listed on Demo 1 handout)

etFPGA Cambridge Spring School 15-19 Mar 2010

61

UNIVERSITY OF BOOTEAR

# **Understanding Buffer Size Requirements in a Router**

JetFPGA Cambridge Spring School 15-19 Mar 2010

65

UNIVERSITY OF BOOTEAS

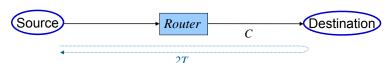

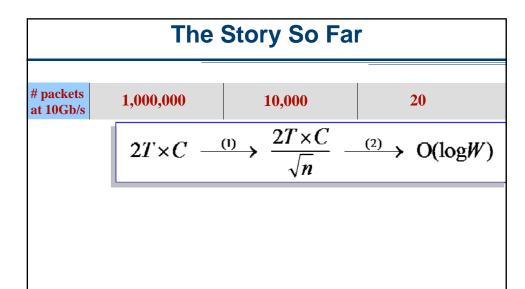

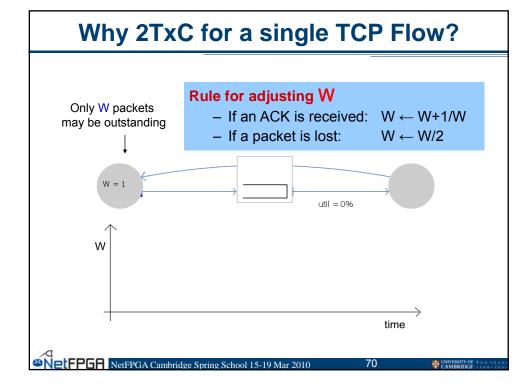

# **Buffer Requirements in a Router**

# **Buffer size matters:**

- Small queues reduce delay

- Large buffers are expensive

# Theoretical tools predict requirements

- Queuing theory

- Large deviation theory

- Mean field theory

# Yet, there is no direct answer

- Flows have a closed-loop nature

- Question arises on whether focus should be on equilibrium state or transient state

# Rule-of-thumb

- · Universally applied rule-of-thumb:

- A router needs a buffer size:  $B = 2T \times C$

- 2T is the two-way propagation delay (or just 250ms)

- C is capacity of bottleneck link

- Context

- Mandated in backbone and edge routers

- Appears in RFPs and IETF architectural guidelines

- Already known by inventors of TCP

- [Van Jacobson, 1988]

- Has major consequences for router design

NetFPGA Cambridge Spring School 15-19 Mar 2010

67

UNIVERSITY OF HOCTEARS

- (1) Assume: Large number of desynchronized flows; 100% utilization

- (2) Assume: Large number of desynchronized flows; <100% utilization

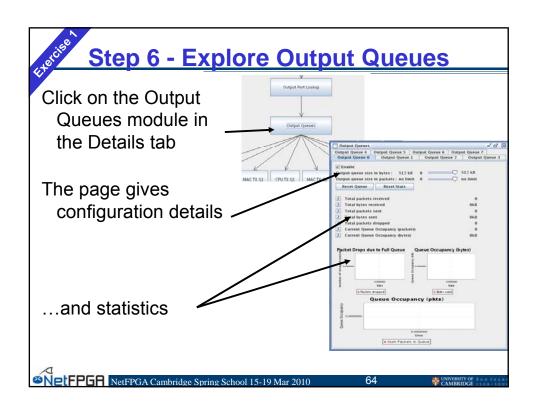

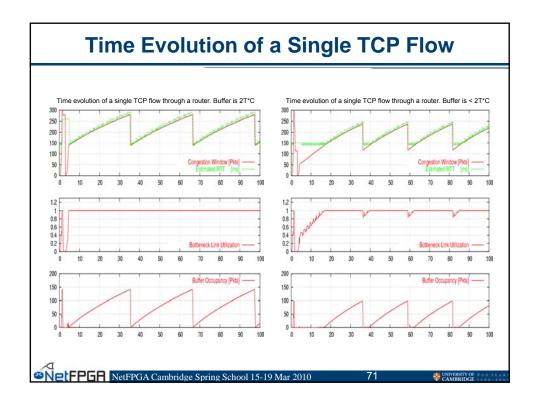

# Using NetFPGA to explore buffer size

- Need to reduce buffer size and measure occupancy

- Alas, not possible in commercial routers

- So, we will use the NetFPGA instead

# **Objective:**

Use the NetFPGA to understand how large a buffer we need for a single TCP flow.

NetFPGA Cambridge Spring School 15-19 Mar 2010

69

UNIVERSITY OF HOOTEARS

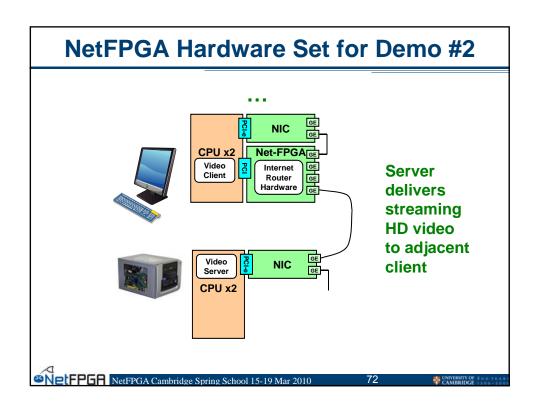

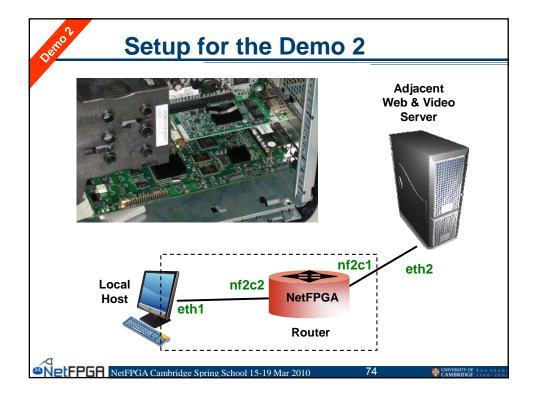

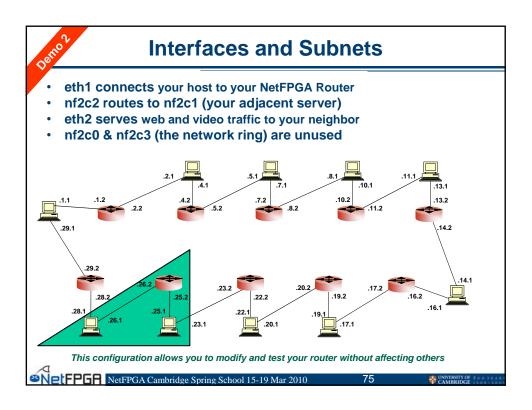

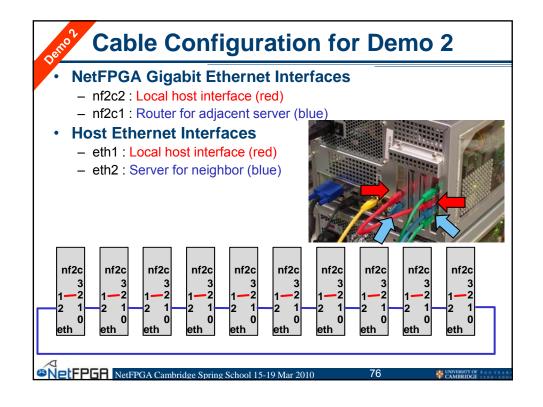

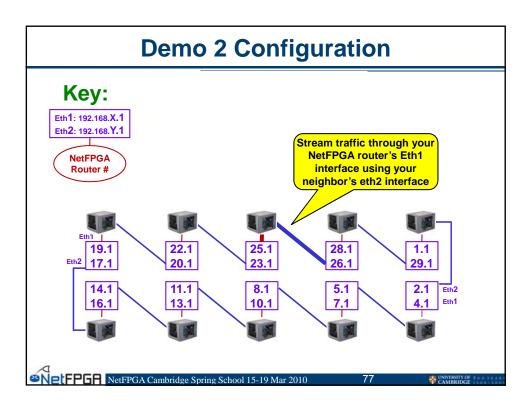

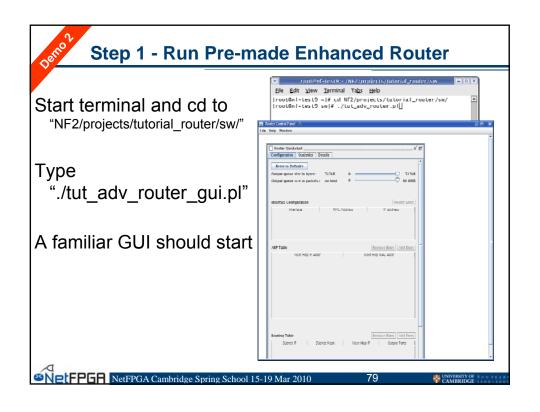

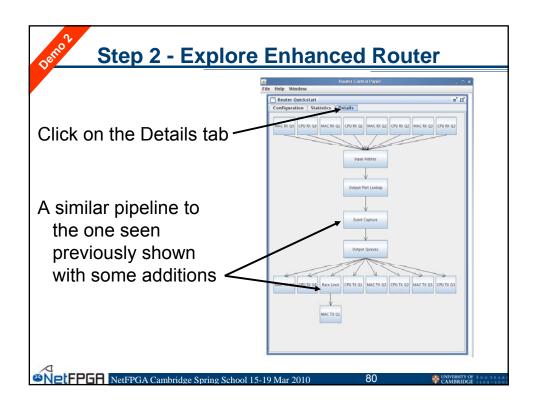

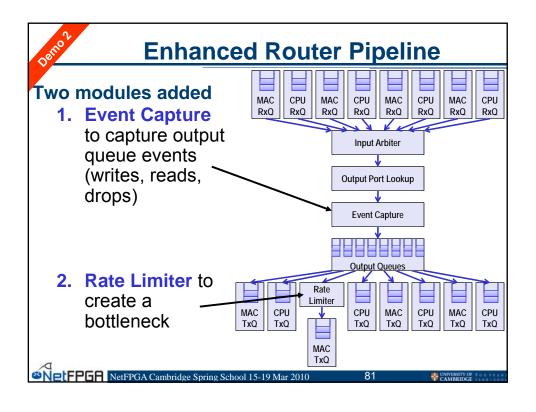

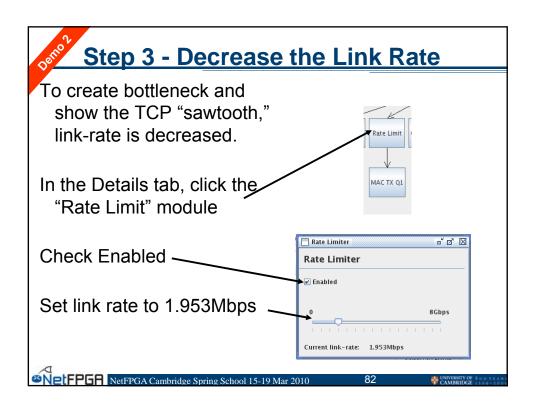

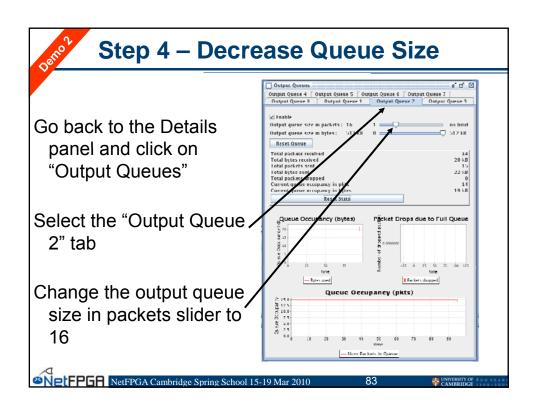

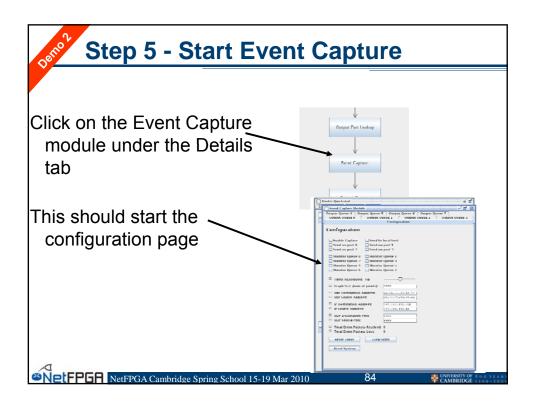

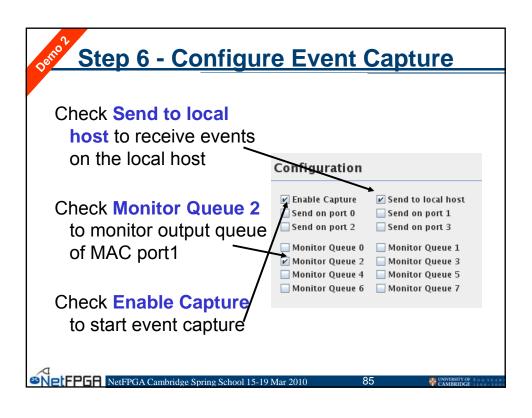

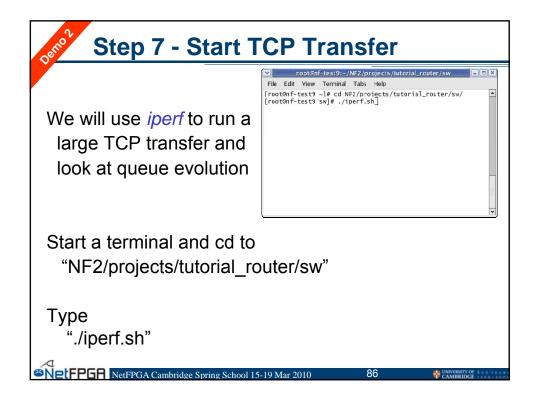

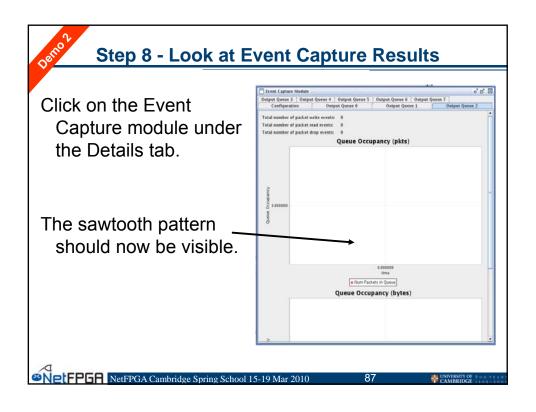

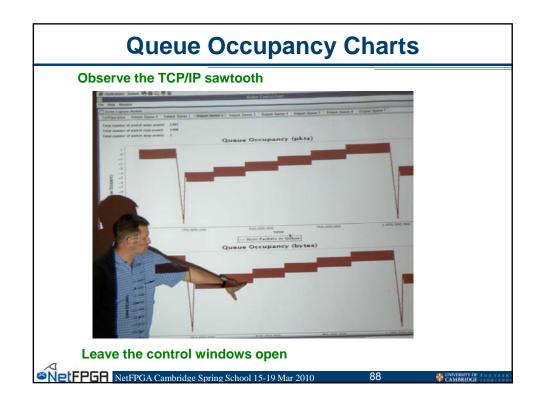

#### Demo 2

# Observing and Controlling the Queue Size

## **Enhanced Router**

#### **Objectives**

- Observe router with new modules

- New modules: rate limiting, event capture

#### **Execution**

- Run event capture router

- Look at routing tables

- Explore details pane

- Start tcp transfer, look at queue occupancy

- Change rate, look at queue occupancy

# **Exercise 2: Enhancing the Reference Router**

NetFPGA Cambridge Spring School 15-19 Mar 2010

89

UNIVERSITY OF BOOTEAR

## ercise

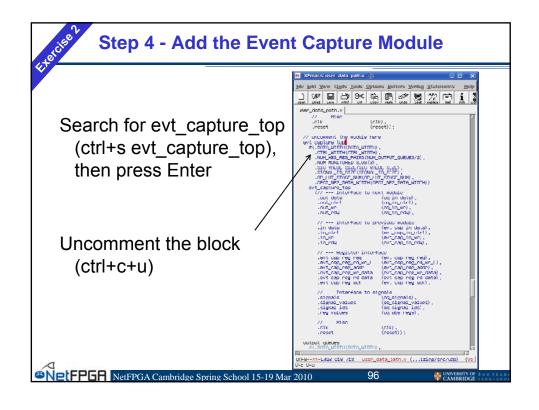

#### **Enhance Your Router**

#### **Objectives**

- Add new modules to datapath

- Synthesize and test router

#### **Execution**

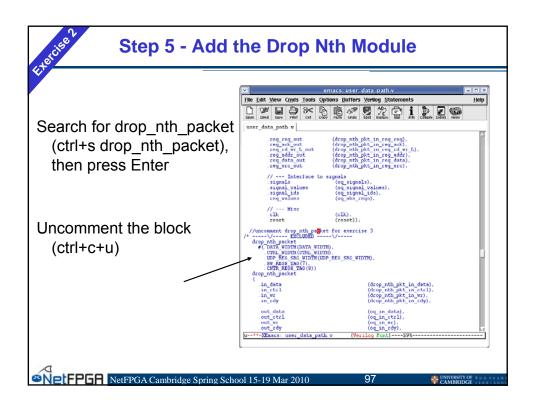

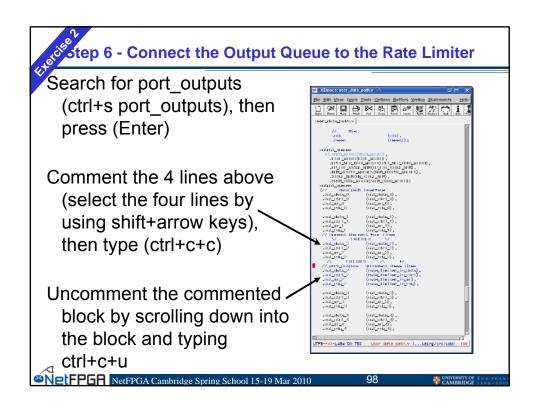

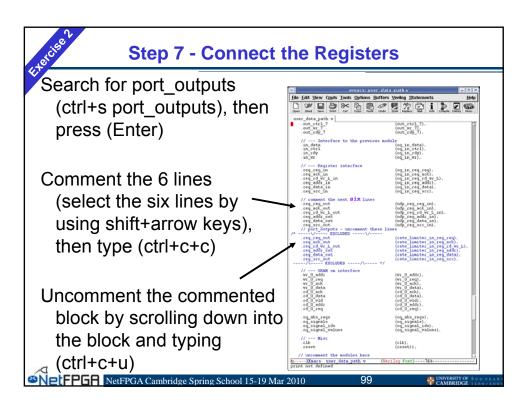

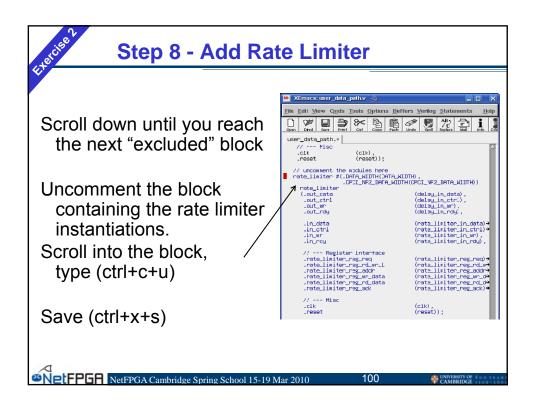

- Open user\_datapath.v, uncomment delay/rate/event capture modules

- Synthesize

- After synthesis, test the new system

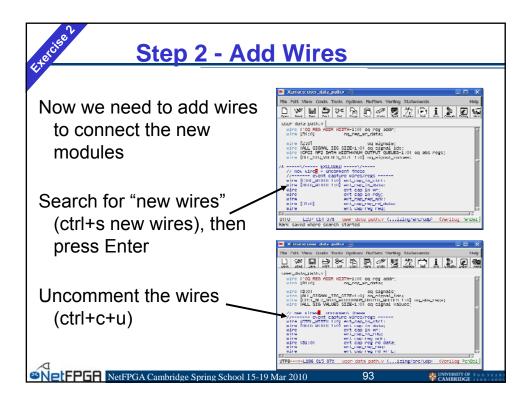

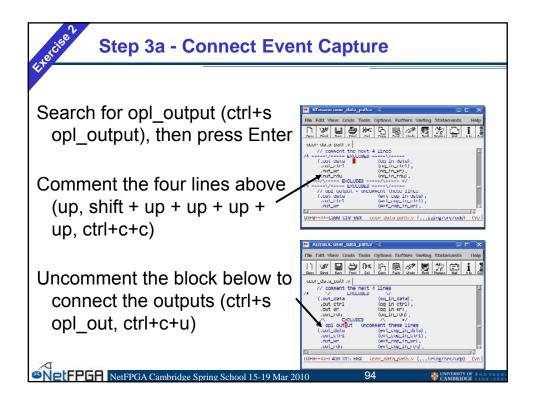

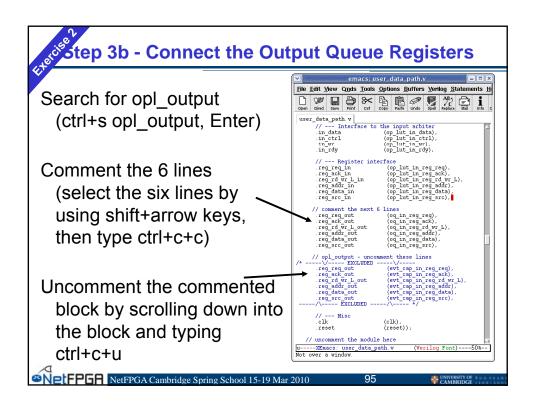

## An aside: emacs Tips

#### We will modify Verilog source code with emacs

- To undo a command, type

- ctrl+shift+'-'

- To cancel a multi-keystroke command, type

- · ctrl+g

- To select lines,

- · hold shift and press the arrow keys

- To comment (remove from compilation) selected lines, type

- ctrl+c+c

- To uncomment a commented block,

- · move the cursor inside the commented block

- type ctrl+c+u

- To save, type

- ctrl+x+s

- To search for a term, type

- · ctrl+s search pattern

NetFPGA Cambridge Spring School 15-19 Mar 2010

CAMBRIDGE 1208-20

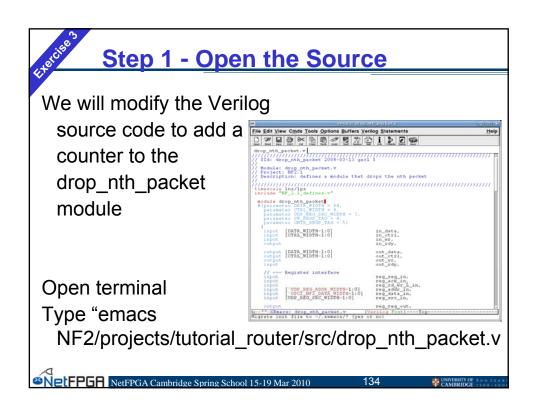

## Step 1 - Open the Source

We will modify the Verilog source code to add event capture and rate limiter modules

We will simply comment and uncomment existing code

Open terminal

Type emacs

NF2/projects/tutorial\_router/src/user\_data\_path.v

NetFPGA Cambridge Spring School 15-19 Mar 2010

UNIVERSITY OF BOOTEAS

#### **Second Break**

(while hardware compiles)

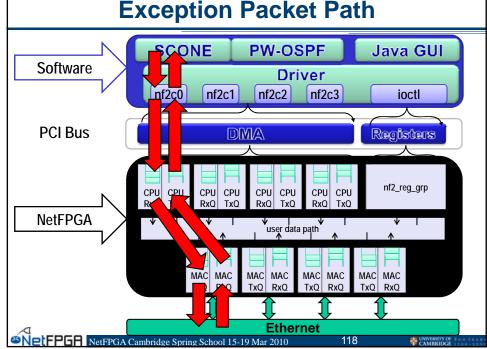

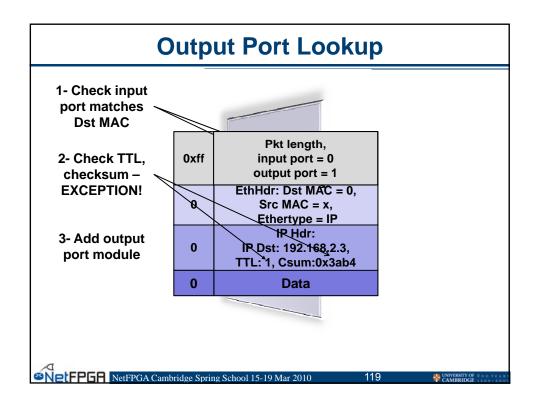

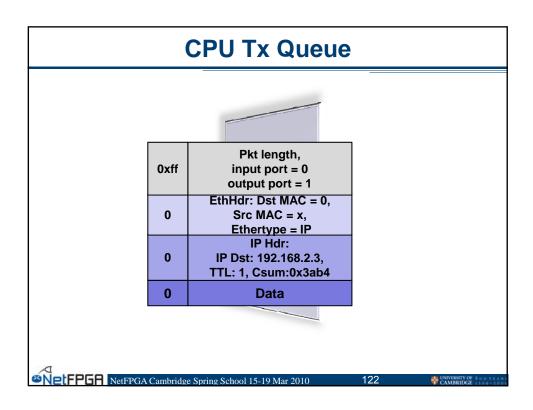

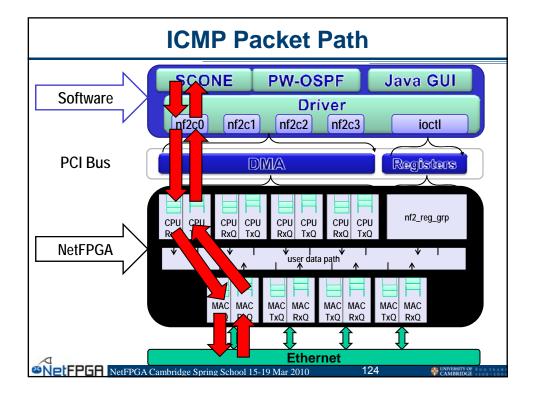

## **Exception Packet**

- Example: TTL = 0 or TTL = 1

- Packet has to be sent to the CPU which will generate an ICMP packet as a response

- Difference starts at the Output Port lookup stage

#### **ICMP Packet**

- For the ICMP packet, the packet arrives at the CPU Rx Queue from the PCI Bus

- It follows the same path as a packet from the MAC until it reaches the Output Port Lookup

- The OPL module sees the packet is from the CPU Rx Queue 1 and sets the output port directly to 0

- The packet then continues on the same path as the non-exception packet to the Output Queues and then MAC Tx queue 0

SNPIFPGA NetFPGA Cambridge Spring School 15-19 Mar 2010

3

CAMBRIDGE

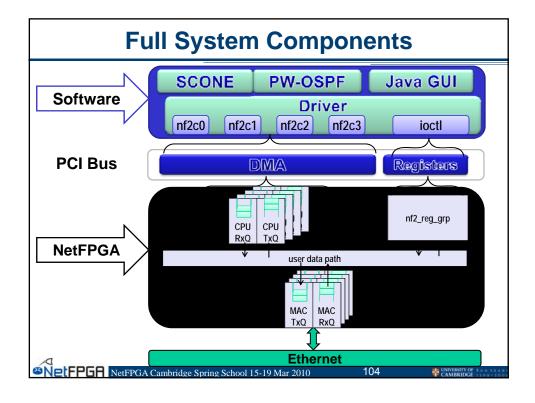

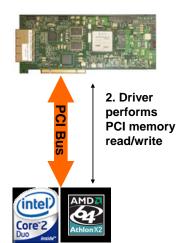

#### **NetFPGA-Host Interaction**

- Linux driver interfaces with hardware

- Packet interface via standard Linux network stack

- Register reads/writes via ioctl system call with wrapper functions:

- readReg(nf2device \*dev, int address, unsigned \*rd\_data);

- writeReg(nf2device \*dev, int address, unsigned \*wr\_data);

eg:

readReg(&nf2, OQ\_NUM\_PKTS\_STORED\_0, &val);

NetFPGA NetFPGA Cambridge Spring School 15-19 Mar 2010

125

CAMBRIDGE

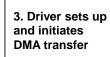

## NetFPGA to host packet transfer

1. Packet arrives – forwarding table sends to CPU queue

2. Interrupt notifies driver of packet arrival

NetFPGA Cambridge Spring School 15-19 Mar 20

126

UNIVERSITY OF BOOTEAR

#### **NetFPGA-Host Interaction**

## **NetFPGA** to host packet transfer (cont.)

## **NetFPGA-Host Interaction**

#### **Host to NetFPGA packet transfers**

## **NetFPGA-Host Interaction**

#### **Register access**

1. Software makes ioctl call on network socket

ioctl passed to driver

NetFPGA Cambridge Spring School 15-19 Mar 2010

129

UNIVERSITY OF BOOYEAR

#### **NetFPGA-Host Interaction**

- Packet transfers shown using DMA interface

- Alternative: use programmed IO to transfer packets via register reads/writes

- slower but eliminates the need to deal with network sockets

## **Step 10 – Perfect the Router**

Go back to "Demo 2: Step 1" after synthesis completes and redo the steps with your own router

#### To run your router:

- 1- cd NF2/projects/tutorial\_router/sw

- 2- type "./tut\_adv\_router\_gui.pl --use\_bin ../../bitfiles/tutorial\_router.bit"

You can change the bandwidth and queue size settings to see how that affects the evolution of queue occupancy

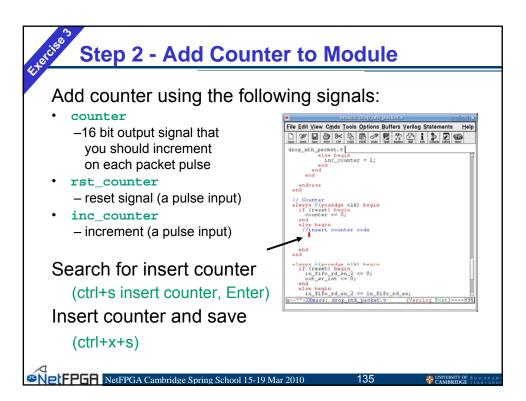

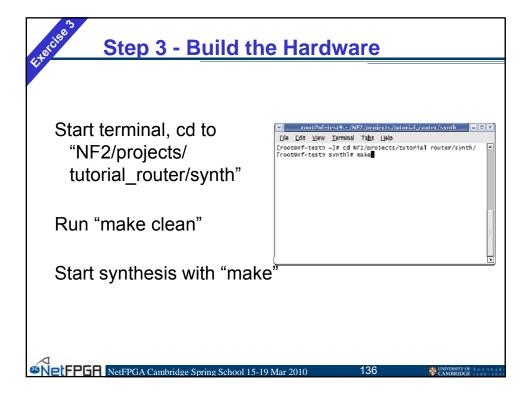

#### **Drop 1 in N Packets**

#### **Objectives**

- Add counter and FSM to the code

- Synthesize and test router

#### Execution

- Open drop\_nth\_packet.v

- Insert counter code

- Synthesize

- After synthesis, test the new system.

# **Using the NetFPGA** in the Classroom

etFPGA Cambridge Spring School 15-19 Mar 2010

137

UNIVERSITY OF BOOTEAR

#### **NetFPGA** in the Classroom

- Stanford University

- •EE109 "Build an Ethernet Switch"

Undergraduate course for all EE students http://www.stanford.edu/class/ee109/

•CS344 "Building an Internet Router" (since '05)

Quarter-long course targeted at graduates

- •Rice University

- •Network Systems Architecture (since '08)

http://comp519.cs.rice.edu/

- Cambridge University

- •Build an Internet Router (since '09)

Quarter-long course targeted at graduates

- University of Wisconsin

- •CS838 "Rethinking the Internet Architecture"

http://pages.cs.wisc.edu/~akella/CS838/F09/

See: http://netfpga.org/teachers.html

138

UNIVERSITY OF #00 YZAR CAMBRIDGE 1209-100

## **Components of NetFPGA Course**

- Documentation

- System Design

- Implementation Plan

- Deliverables

- Hardware Circuits

- System Software

- Milestones

- Testing

- Proof of Correctness

- Integrated Testing

- Interoperabilty

- Post Mortem

- Lessons Learned

NetFPGA Cambridge Spring School 15-19 Mar 2010

139

UNIVERSITY OF BOOTEAS

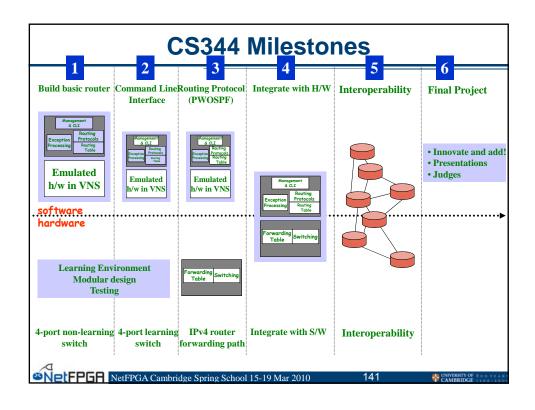

#### **NetFPGA** in the Classroom

- Stanford CS344: "Build an Internet Router"

- Courseware available on-line

- Students work in teams of three

- 1-2 software

- 1-2 hardware

- Design and implement router in 8 weeks

- Write software for CLI and PW-OSPF

- Show interoperability with other groups

- Add new features in remaining two weeks

- Firewall, NAT, DRR, Packet capture, Data generator, ...

| Typical NetFPGA Course Plan                         |                                  |                              |                          |

|-----------------------------------------------------|----------------------------------|------------------------------|--------------------------|

| Week                                                | Software                         | Hardware                     | Deliver                  |

| 1                                                   | Verify Software Tools            | Verify CAD Tools             | Write Design<br>Document |

| 2                                                   | Build Software Router            | Build Non-Learning<br>Switch | Run Software Router      |

| 3                                                   | Cmd. Line Interface              | Build Learning Switch        | Run Basic Switch         |

| 4                                                   | Router Protocols                 | Output Queues                | Run Learning Switch      |

| 5                                                   | Implement Protocol               | Forwarding Path              | Interface SW & HW        |

| 6                                                   | Control Hardware                 | Hardware Registers           | HW/SW Test               |

| 7                                                   | Interoperate Software & Hardware |                              | Router Submission        |

| 8                                                   | Plan New Advanced Feature        |                              | Project Design Plan      |

| 9                                                   | Show new Advanced Feature        |                              | Demonstration            |

| ©NELFPGA Cambridge Spring School 15-19 Mar 2010 142 |                                  |                              |                          |

## **Presentations**

#### **Stanford CS344**

http://cs344.stanford.edu

## **Cambridge P33**

http://www.cl.cam.ac.uk/teaching/0910/P33/

NetFPGA Cambridge Spring School 15-19 Mar 2010

#### **Photos from NetFPGA Tutorials**

SIGCOMM - Seattle, Washington, USA

SIGMETRICS - San Diego, California, USA

EuroSys - Glasgow, Scotland, U.K.

Beijing, China

Bangalore, India

http://netfpga.org/pastevents.php and http://netfpga.org/upcomingevents.php

#### **Deployed NetFPGA hardware** (July 2008)

- **Cambridge University**

- Rice University

- Georgia Tech

- **Washington University**

- University of Utah

- **University of Toronto**

- **University of Wisconsin**

- **University of Connecticut**

- University of California, San Diego (UCSD)

- University of California, Los Angeles (UCLA)

- University of Idaho

- University of Massachusetts (UMass)

- University of Pennsylvania (UPenn)

- North Carolina State University

- Lehigh University

- State University of New York (SUNY), Buffalo

- State University of New York (SUNY), Binghamton.

- University of Florida

- Rutgers

- Western New England College

- **Emerson Network Power**

- ICSI

- Agilent

- Cisco

- Quanta Computer, Inc.

- Zones Inc.

- CESNET

- Princeton University

- India Institute of Science (IISc), Bangalore

- Ecole Polytechnique de Montreal

- **Beijing Jaiotong University**

- China Zhejiang University

- National Taiwan University

- **University of New South Wales**

- University of Hong Kong

- University of Sydney

- University of Bologna

- **University of Naples**

- University of Pisa, Italy

- University of Quebec

- University of Jinan

- University of Amsterdam

- University of Waterloo

- University of Victoria

- Chung Yuan Christan University, Taiwan (CYCU)

- Universite de Technologie de Compiegne (UTC)

- Catholic University of Rio De Janeiro

- University Leiden (The Netherlands)

- **National United University**

- Kookman University (South Korea)

- Kasetsart University (Thailand)

- Helsinki Institute for Information Technology (HIIT)

#### **Networked FPGAs in Research**

#### 1. Managed flow-table switch

- http://OpenFlowSwitch.org/

- 2. Buffer Sizing

- Reduce buffer size & measure buffer occupancy

#### 3. RCP: Congestion Control

- New module for parsing and overwriting new packet

- New software to calculate explicit rates

#### Deep Packet Inspection (FPX)

- TCP/IP Flow Reconstruction

- Regular Expression Matching

- **Bloom Filters**

#### 5. Packet Monitoring (ICSI)

**Network Shunt**

#### 6. Precise Time Protocol (PTP)

Synchronization among Routers

#### **Third Break**

(while hardware compiles)

<u> NetFPGA</u>

NetFPGA Cambridge Spring School 15-19 Mar 2010

147

UNIVERSITY OF BOOTEAR

ideo

## **Step 5 – Test your Router**

You can watch the number of received and sent packets to watch the module drop every Nth packet. Ping a local machine (i.e. 192.168.7.1) and watch for missing pings

To run your router:

- 1- Enter the directory by typing: cd NF2/projects/tutorial\_router/sw

- 2- Run the router by typing:

./tut\_adv\_router\_gui.pl --use\_bin ../../../bitfiles/tutorial\_router.bit

To set the value of N (which packet to drop)

type regwrite 0x2000704 N

- replace N with a number (such as 100)

To enable packet dropping, type: regwrite 0x2000700 0x1 To disable packet dropping, type: regwrite 0x2000700 0x0

@NetFPGA

FPGA Cambridge Spring School 15-19 Mar 2010

148

UNIVERSITY OF BOOYEAR

## **Step 5 – Measurements**

- Determine iperf TCP throughput to neighbor's server for each of several values of N

- Similar to Demo 2, Step 8

- Ping 192.168.x.2 (where x is your neighbor's server)

- TCP throughput with:

- · Drop circuit disabled

- TCP Throughput =

- Drop one in N = 1,000 packets

- TCP Throughput = \_\_\_\_ Mbps

- Drop one in N = 100 packets

- TCP Throughput = \_\_\_\_\_ \_ Mbps

- Drop one in N = 10 packets

- TCP Throughput = \_\_\_\_\_ \_ Mbps

- Explain why TCPs throughput is so low given that only a tiny fraction of packets are lost

NetFPGA Cambridge Spring School 15-19 Mar 2010

## Visit http://NetFPGA.org

- · Log into the Wiki

- Access the Beta code

- Join the netfpga-beta mailing list

- Join the discussion forum

NetFPGA Cambridge S

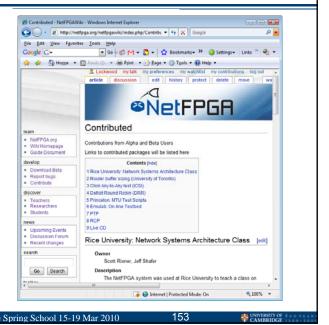

#### Learn from the On-line Guide

- Obtain hardware, software, & gateware

- Install software, CAD tools, & simulation models

- Verify installation using regression selftests

- Walk through the reference designs

- Learn about contributed packages

NetFPGA Cambridge Spring School 15-19 Mar 2010

- Search for related work

- List your project on the Wiki

- Link your project homepage

NetFPGA Camb

## (Early) Project Ideas for the NetFPGA

- IPv6 Router (in high demand)

- TCP Traffic Generator

- Valiant Load Balancing

- Graphical User Interface (like CLACK)

- MAC-in-MAC Encapsulation

- Encryption / Decryption modules

- RCP Transport Protocol

- Packet Filtering (Firewall, IDS, IDP)

- TCP Offload Engine

- DRAM Packet Queues

- 8-Port Switch using SATA Bridge

- Build our own MAC (from source, rather than core)

- Use XML for Register Definitions

http://netfpga.org/foswiki/bin/view/NetFPGA/OneGig/ModuleWishlist

## **NetFPGA Project - Going Forward**

NetFPGA

NetFPGA Cambridge Spring School 15-19 Mar 2010

155

UNIVERSITY OF BOOTEAS

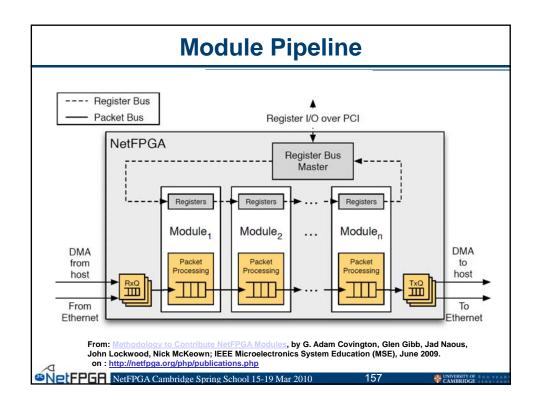

#### The 2010 v2.0 Code Release

- Modular Registers

- Simplifies integration of multiple modules

- · Many users control NetFPGAs from software

- Register set joined together at build time

- Project specifies registers in XML list

- Packet Buffering in DRAM

- Supports Deep buffering

- Single 64MByte queue in DDR2 memory

- Programmable Packet Encapsulation

- Packet-in-packet encapsulation

- Enables tunnels between OpenFlowSwitch nodes

## **Going Forward**

#### NSF Funding at Stanford

- Supports program at Stanford for next 4 years

- · Workshops, Tutorials, Support

#### Academic Collaborations

- Cambridge, NICTA, KOREN, ONL, ...

- · Academic Tutorials

- Developer Workshops

#### Industry Collaborations

- AlgoLogicSystems.com

- Designs algorithms in Logic

- · Creates systems with open FPGA platforms

- Uses and contributes to open-source cores

- · Provides customized training to industry

NetFPGA Cambridge Spring School 15-19 Mar 2010

159

UNIVERSITY OF BOOYEAR

#### **Conclusions**

#### NetFPGA Provides

- Open-source, hardware-accelerated Packet Processing

- Modular interfaces arranged in reference pipeline

- Extensible platform for packet processing

#### NetFPGA Reference Code Provides

- Large library of core packet processing functions

- Scripts and GUIs for simulation and system operation

- Set of Projects for download from repository

#### The NetFPGA Base Code

- Well defined functionality defined by regression tests

- Function of the projects documented in the Wiki Guide

#### **Thoughts for (Prospective) Contributors**

- Build Modular components

- Describe shared registers (as per 2.0 release)

- Consider how modules would be used in larger systems

- Define functionality clearly

- Through regression tests

- With repeatable results

- Disseminate projects

- Post open-source code

- Document projects on Web, Wiki, and Blog

- Expand the community of developers

- Answer questions in the Discussion Forum

- Collaborate with your peers to build new applications

## **Group Discussion**

- · Your plans for using the NetFPGA

- Teaching

- Research

- Other

- Resources needed for your class

- Source code

- Courseware

- Examples

- · Your plans to contribute

- Expertise

- Capabilities

- Collaboration Opportunities