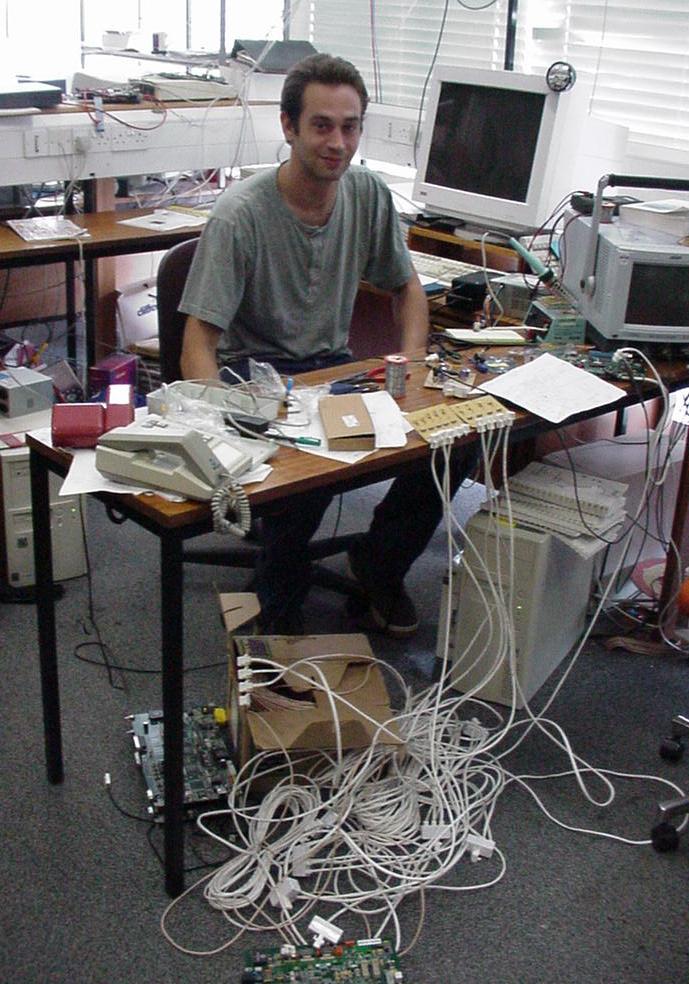

University of Cambridge, Computer Laboratory.Home Wiring Reuse Testbed (Suh/Leiser/Greaves)The picture shows Richard Leiser in the middle of some wires!

Our wiring testbed is a collection of wires and phones and xDSL splitters of various types, including the new BT NT2000 terminator. We have two simulators that can model the home wiring. Both are based on lumped-element simulation, but one works in the time-domain using a 60 ps or so time step and the other by evaluating the Laplace transforms of the complete toplogy. Example Wiring Toplogy

S3

|

|5 meter

10 meter 2 | 7 meter

S1----------------|-------- S4

|

|

|

|20 meter

|

|

|

|

S2

x axis = time axis with 5 ns resolution.

y axis = volt for the measured pulses in a,c,e, and f.

load resistor = 1 kOhm.

Output resistor of source pulse generator is 110 Ohm.

The following pdf file shows graphs of measurements and simulation of the above toplology simandmes.pdf . data1= simulation result. data2= extracted result based on the pulse measurement. Contact us for white papers or more information. We are now developing the EMC aspects of our simulation by adding models of longditudinal balance and so on. |