# Cortex - A9 MPCore

Revision: r3p0

**Technical Reference Manual**

# Cortex-A9 MPCore Technical Reference Manual

Copyright © 2008-2011 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

#### Change history

| Date             | Issue | Confidentiality                      | Change                  |

|------------------|-------|--------------------------------------|-------------------------|

| 04 April 2008    | A     | Non-Confidential                     | First release for r0p0  |

| 08 July 2008     | В     | Non-Confidential Restricted Access   | First release for r0p1  |

| 16 December 2008 | С     | Non-Confidential Restricted Access   | First release for r1p0  |

| 2 October 2009   | D     | Non-Confidential Restricted Access   | First release for r2p0  |

| 27 November 2009 | Е     | Non-Confidential Unrestricted Access | Second release for r2p0 |

| 30 April 2010    | F     | Non-Confidential Unrestricted Access | First release for r2p2  |

| 19 July 2011     | G     | Non-Confidential                     | First release for r3p0  |

#### **Proprietary Notice**

Words and logos marked with  $^*$  or  $^{\rm m}$  are registered trademarks or trademarks of ARM $^*$  in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

#### **Product Status**

The information in this document is final, that is for a developed product.

## Web Address

http://www.arm.com

# Contents

# **Cortex-A9 MPCore Technical Reference Manual**

|           | Pref  | ace                                                      |      |

|-----------|-------|----------------------------------------------------------|------|

|           |       | About this book                                          | v    |

|           |       | Feedback                                                 |      |

| Chapter 1 | Intro | oduction                                                 |      |

| -         | 1.1   | About the Cortex-A9 MPCore processor                     | 1-2  |

|           | 1.2   | Compliance                                               |      |

|           | 1.3   | Configurable options                                     |      |

|           | 1.4   | Test features                                            | 1-6  |

|           | 1.5   | Private Memory Region                                    | 1-7  |

|           | 1.6   | Interfaces                                               | 1-9  |

|           | 1.7   | MPCore considerations                                    | 1-10 |

|           | 1.8   | Product documentation and design flow                    | 1-11 |

|           | 1.9   | Product revisions                                        | 1-13 |

| Chapter 2 | Sno   | op Control Unit                                          |      |

| -         | 2.1   | About the SCU                                            | 2-2  |

|           | 2.2   | SCU registers                                            |      |

|           | 2.3   | AMBA AXI Master Port Interfaces                          |      |

|           | 2.4   | Accelerator Coherency Port                               |      |

|           | 2.5   | Event communication with an external agent using WFE/SEV | 2-23 |

| Chapter 3 | Inte  | rrupt Controller                                         |      |

| •         | 3.1   | About the Interrupt Controller                           | 3-2  |

|           | 3.2   | Security extensions support                              |      |

|           | 3.3   | Distributor register descriptions                        |      |

|           | 3.4   | Interrupt interface register descriptions                |      |

| Chapter 4  | Glob | oal timer, private timers, and watchdog registers   |      |

|------------|------|-----------------------------------------------------|------|

| -          | 4.1  | About the private timer and watchdog blocks         | 4-2  |

|            | 4.2  | Private timer and watchdog registers                | 4-3  |

|            | 4.3  | About the Global Timer                              | 4-8  |

|            | 4.4  | Global timer registers                              | 4-9  |

| Chapter 5  | Cloc | cks, Resets, and Power Management                   |      |

|            | 5.1  | Clocks                                              | 5-2  |

|            | 5.2  | Resets                                              | 5-3  |

|            | 5.3  | Power management                                    | 5-7  |

| Chapter 6  | Deb  | ug                                                  |      |

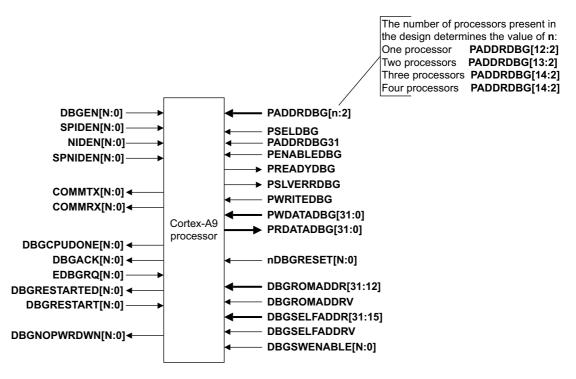

| •          | 6.1  | External Debug Interface Signals                    | 6-2  |

|            | 6.2  | Cortex-A9 MPCore APB Debug interface and memory map |      |

| Appendix A | Sign | nal Descriptions                                    |      |

|            | A.1  | Clock and clock control signals                     | A-2  |

|            | A.2  | Resets and reset control signals                    | A-3  |

|            | A.3  | Interrupts                                          | A-4  |

|            | A.4  | Configuration signals                               | A-5  |

|            | A.5  | WFE and WFI Standby signals                         | A-7  |

|            | A.6  | Power management signals                            | A-8  |

|            | A.7  | AXI interfaces                                      | A-10 |

|            | A.8  | Performance monitoring signals                      | A-19 |

|            | A.9  | Exception flags signals                             |      |

|            | A.10 | Parity error signals                                | A-21 |

|            | A.11 | MBIST interface                                     | A-22 |

|            | A.12 | Scan test signal                                    |      |

|            | A.13 | External Debug interface                            |      |

|            | A.14 | PTM interface signals                               | A-28 |

| Appendix B | Revi | isions                                              |      |

# **Preface**

This preface introduces the *Cortex-A9 MPCore Technical Reference Manual*. It contains the following sections:

- About this book on page vi

- Feedback on page x.

#### About this book

This book is for the *Cortex-A9 MPCore*.

\_\_\_\_\_Note \_\_\_\_\_

The Cortex-A9 MPCore consists of between one and four Cortex-A9 processors and a *Snoop Control Unit* (SCU) and other peripherals.

#### **Product revision status**

The rnpn identifier indicates the revision status of the product described in this book, where:

**rn** Identifies the major revision of the product.

**pn** Identifies the minor revision or modification status of the product.

#### Intended audience

This book is written for hardware and software engineers implementing Cortex-A9 system designs. The manual describes the external functionality of the Cortex-A9 MPCore. It provides information that enables designers to integrate the processor into a target system.

#### Using this book

This book is organized into the following chapters:

#### Chapter 1 Introduction

Read this for a high-level view of the Cortex-A9 MPCore processor and a description of its features.

#### Chapter 2 Snoop Control Unit

Read this for a description of the Snoop Control Unit of the Cortex-A9 MPCore processor.

#### **Chapter 3** *Interrupt Controller*

Read this for a description of the Cortex-A9 MPCore Interrupt Controller.

\_\_\_\_\_Note \_\_\_\_\_

The *PrimeCell*® *Generic Interrupt Controller* (PL390) and the Cortex A9 Interrupt Controller share the same programmers model. There are implementation-specific differences.

#### Chapter 4 Global timer, private timers, and watchdog registers

Read this for a description of the Cortex-A9 MPCore timer and watchdog registers.

#### Chapter 5 Clocks, Resets, and Power Management

Read this for a description of the clocking modes and the reset signals. This chapter also describes the power management facilities.

#### Chapter 6 Debug

Read this for a description of the Cortex-A9 MPCore debug registers and resources.

#### Appendix A Signal Descriptions

Read this for a description of the Cortex-A9 MPCore input and output signals.

#### Appendix B Revisions

Read this for a description of technical changes between released issues of this book.

#### Conventions

Conventions that this book can use are described in:

- Typographical

- Timing diagrams

- Signals on page viii.

# **Typographical**

The typographical conventions are:

| italic            | Introduces special terminology, denotes cross-references, and citations.                                                                |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bold              | Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.   |

| monospace         | Denotes text that you can enter at the keyboard, such as commands, file and program names, and source code.                             |

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. You can enter the underlined text instead of the full command or option name. |

| monospace italic  | Denotes arguments to monospace text where the argument is to be replaced by a specific value.                                           |

| monospace bold    | Denotes language keywords when used outside example code.                                                                               |

| < and >           | Enclose replaceable terms for assembler syntax where they appear in code or code fragments. For example:                                |

|                   | MRC p15, 0 <rd>, <crn>, <crm>, <opcode_2></opcode_2></crm></crn></rd>                                                                   |

#### **Timing diagrams**

The figure named *Key to timing diagram conventions* on page viii explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

| Clock                          |

|--------------------------------|

| HIGH to LOW                    |

| Transient   √                  |

| HIGH/LOW to HIGH               |

| Bus stable                     |

| Bus to high impedance          |

| Bus change                     |

| High impedance to stable bus - |

#### Key to timing diagram conventions

Timing diagrams sometimes show single-bit signals as HIGH and LOW at the same time and they look similar to the bus change shown in *Key to timing diagram conventions*. If a timing diagram shows a single-bit signal in this way then its value does not affect the accompanying description.

#### **Signals**

The signal conventions are:

Signal level

The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

- HIGH for active-HIGH signals

- LOW for active-LOW signals.

Lower-case n

At the start or end of a signal name denotes an active-LOW signal.

# **Additional reading**

This section lists publications by ARM and by third parties.

See Infocenter, http://infocenter.arm.com, for access to ARM documentation.

See the glossary, http://infocenter.arm.com/help/topic/com.arm.doc.aeg0014-/index.html, for a list of terms and acronyms specific to ARM.

#### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition (ARM DDI 0406)

- Cortex-A9 Technical Reference Manual (ARM DDI 0338)

- Cortex-A9 Floating-Point Unit Technical Reference Manual (ARM DDI 0408)

- Cortex-A9 NEON™ Media Processing Engine Technical Reference Manual (ARM DDI 0409)

- Cortex-A9 MBIST Technical Reference Manual (ARM DDI 0414)

- Cortex-A9 Configuration and Sign-Off Guide (ARM DII 0146)

- AMBA® AXI Protocol Specification (ARM IHI 0022)

- ARM Generic Interrupt Controller Architecture Specification (ARM IHI 0048)

- CoreSight™ PTM-A9 Technical Reference Manual (ARM DDI 0401)

- CoreSight PTM-A9 Integration Manual (ARM DII 0162)

- CoreSight Program Flow Trace Architecture Specification (ARM IHI 0035)

- CoreSight Technology System Design Guide (ARM DGI 0012)

- CoreSight Architecture Specification (ARM IHI 0029)

- *ARM Debug Interface v5 Architecture Specification* (ARM IHI 0031)

- Corelink™ Level 2 Cache Controller L2C-310 Technical Reference Manual (ARM DDI 0246)

- RealView<sup>®</sup> ICE and RealView Trace User Guide (ARM DUI 0155).

# Other publications

This section lists relevant documents published by third parties:

• JEP106M, Standard Manufacture's Identification Code, JEDEC Solid State Technology Association.

# **Feedback**

ARM welcomes feedback on this product and its documentation.

# Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

#### Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- the title

- the number, ARM DDI 0407G

- the page numbers to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

# Chapter 1 **Introduction**

This chapter describes the Cortex-A9 MPCore processor. It describes the major functional blocks. It contains:

- About the Cortex-A9 MPCore processor on page 1-2

- *Compliance* on page 1-4

- *Configurable options* on page 1-5

- Test features on page 1-6

- Private Memory Region on page 1-7

- *Interfaces* on page 1-9

- *MPCore considerations* on page 1-10

- Product documentation and design flow on page 1-11.

- *Product revisions* on page 1-13.

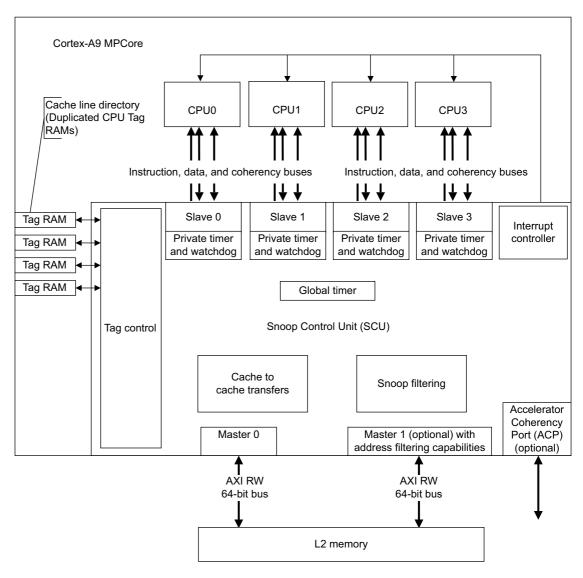

# 1.1 About the Cortex-A9 MPCore processor

The Cortex-A9 MPCore processor consists of:

- From one to four Cortex-A9 processors in a cluster and a *Snoop Control Unit* (SCU) that can be used to ensure coherency within the cluster.

- A set of private memory-mapped peripherals, including a global timer, and a watchdog and private timer for each Cortex-A9 processor present in the cluster.

- An integrated Interrupt Controller that is an implementation of the Generic Interrupt Controller architecture. The integrated Interrupt Controller registers are in the private memory region of the Cortex-A9 MPCore processor.

Individual Cortex-A9 processors in the Cortex-A9 MPCore cluster can be implemented with their own hardware configurations. See the *Cortex-A9 Technical Reference Manual* for additional information on possible Cortex-A9 processor configurations. ARM recommends you implement uniform configurations for software ease of use.

There are other configuration options that impact Cortex-A9 MPCore system integration. The major options are:

- One or two AXI master port interfaces, with address filtering capabilities

- An optional Accelerator Coherency Port (ACP) suitable for coherent memory transfers

- A configurable number of interrupt lines.

See Configurable options on page 1-5.

Figure 1-1 on page 1-3 shows an example multiprocessor configuration.

Figure 1-1 Example multiprocessor configuration

| Note |  |

|------|--|

|------|--|

It is possible to implement only one Cortex-A9 processor in a Cortex-A9 MPCore processor design. In this configuration, an SCU is still provided. The ACP, and an additional master port, are still available as configuration options.

# 1.2 Compliance

The Cortex-A9 processor complies with, or implements, the specifications described in:

- ARM architecture

- Advanced Microcontroller Bus Architecture

- Program Flow Trace architecture

- Debug architecture

- Generic Interrupt Controller architecture

This TRM complements architecture reference manuals, architecture specifications, protocol specifications, and relevant external standards. It does not duplicate information from these sources.

#### 1.2.1 ARM architecture

The Cortex-A9 processor implements the ARMv7-A architecture profile that includes the following architecture extensions:

- Advanced *Single Instruction Multiple Data* (SIMD) architecture extension for integer and floating-point vector operations

- *Vector Floating-Point version 3* (VFPv3) architecture extension for floating-point computation that is fully compliant with the IEEE 754 standard

- Security Extensions for enhanced security

- Multiprocessing Extensions for multiprocessing functionality.

See the ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition.

#### 1.2.2 Advanced Microcontroller Bus Architecture

The Cortex-A9 processor complies with the AMBA 3 protocol. See the AMBA AXI Protocol Specification.

# 1.2.3 Program Flow Trace architecture

The Cortex-A9 processor implements the *Program Trace Macrocell* (PTM) based on the *Program Flow Trace* (PFT) v1.0 architecture. See the CoreSight Program Flow Trace Architecture Specification.

#### 1.2.4 Debug architecture

The Cortex-A9 processor implements the ARMv7 Debug architecture that includes support for Security Extensions and CoreSight. See the CoreSight Architecture Specification.

#### 1.2.5 Generic Interrupt Controller architecture

The Cortex-A9 processor implements the ARM *Generic Interrupt Controller* (GIC) v1.0 architecture.

# 1.3 Configurable options

Table 1-1 shows the Cortex-A9 MPCore processor configurable options.

Table 1-1 Configurable options for the Cortex-A9 MPCore processor

| Feature                                                                           | Options                   |

|-----------------------------------------------------------------------------------|---------------------------|

| Cortex-A9 processors                                                              | One to four               |

| Instruction cache size per Cortex-A9 processor                                    | 16KB, 32KB, or 64KB       |

| Data cache size per Cortex-A9 processor                                           | 16KB, 32KB, or 64KB       |

| TLB size per Cortex-A9 processor                                                  | 64 entries or 128 entries |

| Media Processing Engine with NEON technology per Cortex-A9 processor <sup>a</sup> | Included or not           |

| FPU per Cortex-A9 processor <sup>b</sup>                                          | Included or not           |

| Preload Engine per Cortex-A9 processor                                            | Included or not           |

| Number of entries in the Preload Engine FIFO per Cortex-A9 processor              | 16, 8, or 4               |

| Jazelle DBX extension per Cortex-A9 processor                                     | Full or trivial           |

| Program Trace Macrocell (PTM) interface per Cortex-A9 processor                   | Included or not           |

| Power off and dormant mode wrappers                                               | Included or not           |

| Support for parity error detection <sup>c</sup>                                   | Included or not           |

| ARM_BIST                                                                          | Included or not           |

| Master ports                                                                      | One or two                |

| Accelerator Coherency Port                                                        | One, included or not      |

| Shared Peripheral Interrupts (SPIs)                                               | 0-224, in steps of 32     |

a. Includes support for floating-point operations. If this option is implemented then the FPU option cannot also be implemented.

b. If this option is implemented then the Media Processing Engine with NEON technology option cannot also be implemented.

c. The *Cortex-A9 TRM* describes the parity error scheme. See *Parity error signals* on page A-21 for a description of the signals.

# 1.4 Test features

The Cortex-A9 processor provides test signals that enable the use of both ATPG and MBIST to test the Cortex-A9 processor and its memory arrays. See Appendix A *Signal Descriptions* and *Cortex-A9 MBIST Controller Technical Reference Manual*.

# 1.5 Private Memory Region

All registers accessible by all Cortex-A9 processors within the Cortex-A9 MPCore are grouped into two contiguous 4KB pages accessed through a dedicated internal bus. The base address of these pages is defined by the pins **PERIPHBASE[31:13]**. See *Configuration signals* on page A-5 for more information on **PERIPHBASE[31:13]**.

Cortex-A9 MPCore global control and peripherals must be accessed through memory-mapped transfers to the Cortex-A9 MPCore private memory region.

Memory regions used for these registers must be marked as Device or Strongly-ordered in the translation tables.

Access to the private memory region is little-endian only.

Access these registers with single load/store instructions. Load or store multiple accesses cause an abort to the requesting Cortex-A9 processor and the Fault Status Register shows this as a SLVERR

Table 1-2 shows the permitted access sizes for the private memory regions.

Table 1-2 Permitted access sizes for private memory regions

| Drivete memory region                       | Permitt | ed access sizes       | 3     |             |

|---------------------------------------------|---------|-----------------------|-------|-------------|

| Private memory region                       | Byte    | Halfword <sup>a</sup> | Wordb | Doubleworda |

| Global timer, private timers, and watchdogs | No      | No                    | Yes   | No          |

| SCU registers                               | Yes     | No                    | Yes   | No          |

| Cortex-A9 processor interrupt interfaces    | =       |                       |       |             |

| Interrupt distributor                       | =       |                       |       |             |

a. Halfword or doubleword accesses cause an abort to the requesting Cortex-A9 processor and the Fault Status Register shows this as a SLVERR

The Accelerator Coherency Port (ACP) cannot access any of the registers in this memory region.

Table 1-3 shows register addresses for the Cortex-A9 MPCore processor relative to this base address.

Table 1-3 Cortex-A9 MPCore private memory region

| Offset from PERIPHBASE[31:13] | Peripheral                      | Description                        |

|-------------------------------|---------------------------------|------------------------------------|

| 0x0000 - 0x00FC               | SCU registers                   | Chapter 2 Snoop Control Unit       |

| 0x0100 - 0x01FF               | Interrupt controller interfaces | Chapter 3 Interrupt Controller     |

| 0x0200 - 0x02FF               | Global timer                    | About the Global Timer on page 4-8 |

| 0x0300 - 0x03FF               | -                               | -                                  |

| 0x0400 - 0x04FF               | -                               | -                                  |

| 0x0500 - 0x05FF               | -                               | -                                  |

b. A word access with strobes not all set causes an abort to the requesting Cortex-A9 processor and the Fault Status Register shows this as a SLVERR.

# Table 1-3 Cortex-A9 MPCore private memory region (continued)

| Offset from PERIPHBASE[31:13] | Peripheral                   | Description                                               |

|-------------------------------|------------------------------|-----------------------------------------------------------|

| 0x0600 - 0x06FF               | Private timers and watchdogs | Private timer and watchdog registers on page 4-3          |

| 0x0700 - 0x07FF               | Reserved                     | Any access to this region causes a SLVERR abort exception |

| 0x0800 - 0x08FF               | -                            |                                                           |

| 0x0900 - 0x09FF               | -                            |                                                           |

| 0x0A00 - 0x0AFF               | -                            |                                                           |

| 0x0B00 - 0x0FFF               | -                            |                                                           |

| 0x1000 - 0x1FFF               | Interrupt Distributor        | Interrupt Distributor interrupt sources on page 3-2       |

#### 1.6 Interfaces

The Cortex-A9 MPCore processor has the following interfaces:

- AMBA AXI interfaces

- Interrupts interface.

- Debug interfaces

- Design for Test interface

#### 1.6.1 AMBA AXI interfaces

The AMBA AXI interfaces include one or two AXI Master port interfaces, and one *Accelerator Coherency* (ACP) AXI Slave port. See *AMBA AXI Master Port Interfaces* on page 2-13. See also the *AMBA AXI Protocol Specification*.

#### 1.6.2 Interrupts interface

The Cortex-A9 MPCore processor provides the legacy nIRQ and nFIQ interrupt lines for each individual Cortex-A9 processor present in the cluster.

The Cortex-A9 MPCore processor also provides a separate interrupt interface, with a configurable number of interrupts lines, up to 224, connected to its internal Interrupt Controller.

See Chapter 3 Interrupt Controller.

#### 1.6.3 Debug interfaces

The external debug interface of the Cortex-A9 MPCore processor is compliant with the ARMv7 Debug Architecture that includes support for Security Extensions and CoreSight.

With the exception of a few debug configuration signals, the debug interfaces of the individual Cortex-A9 processors are presented externally so that each processor can be debugged independently.

The Cortex-A9 MPCore processor also provides an external Debug APB interface for memory-mapped accesses to debug and performance monitor registers.

See Chapter 6 Debug.

#### 1.6.4 Design for Test interface

The Cortex-A9 MBIST Controller Technical Reference Manual gives information on the MBIST interface.

#### 1.7 MPCore considerations

This section describes multiprocessing considerations. It contains the following sections:

- About Cortex-A9 MPCore coherency

- Registers with multiprocessor uses

- *Maintenance operations broadcasting.*

# 1.7.1 About Cortex-A9 MPCore coherency

Memory coherency in a Cortex-A9 MPCore processor is maintained following a weakly ordered memory consistency model.

Cache coherency among L1 data caches of the Cortex-A9 processors in the cluster is maintained when the Cortex-A9 processors are operating in *Symmetric Multi-Processing* (SMP) mode. This mode is controlled by the SMP bit of the Auxiliary Control Register.

To be kept coherent, the memory must be marked as Write-Back, Shareable, Normal memory.

| Note                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| When the Shareable attribute is applied to a memory region that is not Write-Back Normal memory, data held in this region is treated as Noncacheable. |

|                                                                                                                                                       |

# 1.7.2 Registers with multiprocessor uses

The following registers, described in the Cortex-A9 TRM, have multiprocessor uses.

- Auxiliary Control Register

- Configuration Base Address Register

- Multiprocessor Affinity Register.

# 1.7.3 Maintenance operations broadcasting

All processors working in SMP mode on the same coherent domain can send and receive TLB and Cache Maintenance operations. The *ARM Architecture Reference Manual* gives detailed information on broadcast operations. A Cortex-A9 processor in the A9-MP cluster broadcasts broadcastable maintenance operation when it operates in SMP mode (ACTLR.SMP=1) and when the maintenance operation broadcasting is enabled (ACTLR.FW=1). A Cortex-A9 processor can receive and execute broadcast maintenance operations when it operates in SMP mode, ACTLR.SMP=1.

# 1.8 Product documentation and design flow

This section describes the Cortex-A9 MPCore books and how they relate to the design flow. It includes:

- Documentation

- Design flow.

See *Additional reading* on page viii for more information about the books described in this section. For information on the relevant architectural standards and protocols, see *Compliance* on page 1-4.

#### 1.8.1 Documentation

The Cortex-A9 MPCore documentation is as follows:

#### **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the Cortex-A9 MPCore processor. It is required at all stages of the design flow. The choices made in the design flow can mean that some behavior described in the TRM is not relevant. If you are programming the Cortex-A9 MPCore processor then contact:

- the implementer to determine:

- the build configuration of the implementation

- what integration, if any, was performed before implementing the Cortex-A9 MPCore processor

- the integrator to determine the pin configuration of the device that you are using.

#### 1.8.2 Design flow

The Cortex-A9 MPCore processor is delivered as synthesizable RT. Before it can be used in a product, it must go through the following processes:

## **Implementation**

The implementer configures and synthesizes the RTL to produce a hard macrocell. This might include integrating RAMs into the design.

**Integration** The integrator connects the implemented design into a SoC. This includes connecting it to a memory system and peripherals.

#### **Programming**

This is the last process. The system programmer develops the software required to configure and initialize the Cortex-A9 MPCore processor, and tests the required application software.

#### Each process:

- can be performed by a different party

- can include implementation and integration choices affect the behavior and features of the Cortex-A9 MPCore processor.

For MCUs, often a single design team integrates the processor before synthesizing the complete design. Alternatively, the team can synthesise the processor on its own or partially integrated, to produce a macrocell that is then integrated, possibly by a separate team.

The operation of the final device depends on:

# **Build configuration**

The implementer chooses the options that affect how the RTL source files are pre-processed. These options usually include or exclude logic that affects one or more of the area, maximum frequency, and features of the resulting macrocell.

#### **Configuration inputs**

The integrator configures some features of the Cortex-A9 MPCore processor by tying inputs to specific values. These configurations affect the start-up behavior before any software configuration is made. They can also limit the options available to the software.

# **Software configuration**

The programmer configures the Cortex-A9 MPCore processor by programming particular values into registers. This affects the behavior of the Cortex-A9 MPCore processor.

| Note                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This manual refers to implementation-defined features that are applicable to build configuration options. Reference to a feature that is included means that the appropriate build and pin configuration options are selected. Reference to an enabled feature means one that has also beer configured by software. |

|                                                                                                                                                                                                                                                                                                                     |

#### 1.9 Product revisions

This section summarizes the differences in functionality between the different releases of this processor:

- Differences in functionality between r0p0 and r0p1.

- *Differences in functionality between r0p1 and r1p0.*

- Differences in functionality between r1p0 and r2p0.

- *Differences in functionality between r2p0 and r2p1* on page 1-14.

- *Differences in functionality between r2p1 and r2p2* on page 1-14.

- Differences in functionality between r2p2 and r3p0 on page 1-14.

#### 1.9.1 Differences in functionality between r0p0 and r0p1

There is no change in the described functionality between r0p0 and r0p1.

The only differences between the two revisions are:

- r0p1 includes fixes for all known engineering errata relating to r0p0

- r0p1 includes an upgrade of the micro TLB entries from 8 to 32 entries, on both the Instruction and Data side.

Neither of these changes affect the functionality described in this document.

#### 1.9.2 Differences in functionality between r0p1 and r1p0

These differences are in addition to the differences described in the Cortex-A9 TRM.

In r1p0 there is a global timer. See *About the Global Timer* on page 4-8.

In the Interrupt Controller INT becomes IRQS. See SPI Status Registers on page 3-11.

SCU CPU Power Status Register bits reassigned. See *SCU CPU Power Status Register* on page 2-6.

## 1.9.3 Differences in functionality between r1p0 and r2p0

These differences are in addition to the differences described in the Cortex-A9 TRM.

Conditions for coherent snoop for ACP requests amended. See ACP requests on page 2-20.

SCU Control register updated. See SCU Control Register on page 2-3:

- Bit 6 to enable additional clock gating on GIC,

- Bit 5 to enable additional clock gating on SCU.

SCU Secure Access Control Register renamed to SCU Non-secure Access Control Register. See *SCU Non-secure Access Control Register* on page 2-11.

Removal of SCU Invalidate All Registers in Non-secure State Register and functionality. See Table 2-1 on page 2-3.

Added speculative linefill feature to optimize L1 miss and L2 hit latency, See *SCU Control Register* on page 2-3. Bit 3.

Added SCUIDLE output. See SCU CPU Power Status Register on page 2-6

Added Filtering capabilities in the SCU for Device accesses. See *Device accesses filtering* on page 2-17.

**PERIPHCLK** can be turned off. See *Clocks* on page 5-2

Change to the behavior of the comparators for each processor with the global timer. See *About the Global Timer* on page 4-8

Added PMUEVENT See Performance monitoring signals on page A-19

1.9.4 Differences in functionality between r2p0 and r2p1

None

1.9.5 Differences in functionality between r2p1 and r2p2

None

1.9.6 Differences in functionality between r2p2 and r3p0

None

# Chapter 2 Snoop Control Unit

This chapter describes the *Snoop Control Unit* (SCU). It contains the following sections:

- *About the SCU* on page 2-2

- *SCU registers* on page 2-3.

- AMBA AXI Master Port Interfaces on page 2-13

- Accelerator Coherency Port on page 2-20

- Event communication with an external agent using WFE/SEV on page 2-23.

# 2.1 About the SCU

The SCU connects one to four Cortex-A9 processors to the memory system through the AXI interfaces.

The SCU functions are to:

- maintain data cache coherency between the Cortex-A9 processors

- initiate L2 AXI memory accesses

- arbitrate between Cortex-A9 processors requesting L2 accesses

- manage ACP accesses.

| Note                                                                                    |        |

|-----------------------------------------------------------------------------------------|--------|

| The Cortex-A9 SCU does not support hardware management of coherency of the instruction. | uction |

#### 2.1.1 TrustZone extensions

The SCU implements support for the ARM Architecture security extensions. See SCU Access Control Register (SAC) on page 2-10 See SCU Non-secure Access Control Register on page 2-11.

# 2.1.2 SCU event monitoring

The individual CPU event monitors can be configured to gather statistics on the operation of the SCU. The *Cortex-A9 TRM* describes event monitoring.

# 2.2 SCU registers

Table 2-1 shows the SCU registers. Addresses are relative to the base address of the region for the SCU memory map, that is **PERIPHBASE[31:13]**. All SCU registers are byte accessible and are reset by **nSCURESET**.

Table 2-1 SCU registers summary

| Offset from                        |                                                      | Security state |                |                                   |        |           |

|------------------------------------|------------------------------------------------------|----------------|----------------|-----------------------------------|--------|-----------|

| PERIPHBASE<br>[31:13]              | Name                                                 | Secure         | Non-<br>Secure | Reset value                       | Banked | Page      |

| 0x00                               | SCU Control Register                                 | RWa            | RW             | Implementation defined            | No     | page 2-3  |

| 0x04 SCU Configuration<br>Register |                                                      | RO             | RO             | Implementation defined            | No     | page 2-5  |

| 0x08                               | SCU CPU Power Status<br>Register                     |                | RW             | Implementation defined            | No     | page 2-6  |

| 0x0C                               | SCU Invalidate All<br>Registers in Secure State      | WOa            | -              | 0x00000000                        | No     | page 2-8  |

| 0x40                               | Filtering Start Address<br>Register                  | RWa            | RW             | Defined by FILTERSTART input      | No     | page 2-8  |

| 0x44                               | Filtering End Address<br>Register                    | RWa            | RW             | Defined by <b>FILTEREND</b> input | No     | page 2-9  |

| 0x50                               | SCU Access Control<br>(SAC) Register                 | RWa            | RW             | 0x0000000F                        | No     | page 2-10 |

| 0x54                               | SCU Non-secure Access<br>Control (SNSAC)<br>Register | RWa            | RO             | 0×00000000                        | No     | page 2-11 |

a. This register is writable if the relevant bits in the SAC are set.

Note SCU registers must not be written with NEON STR instructions.

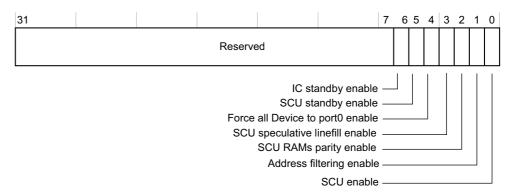

#### 2.2.1 SCU Control Register

The SCU Control Register characteristics are:

# Purpose

- enables speculative linefills to L2 with L2C-310

- enables Force all Device to port0

- enables IC standby mode

- enables SCU standby mode

- enables SCU RAM parity support

- enables address filtering

- enables the SCU.

# Usage constraints

- This register is writable in Secure state if the relevant bit in the SAC register is set.

- This register is writable in Non-secure state if the relevant bits in the SAC and SNSAC registers are set.

**Configurations** Available in all Cortex-A9 multiprocessor configurations.

**Attributes** See the register summary in *SCU registers* on page 2-3.

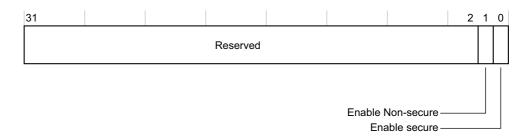

Figure 2-1 shows the SCU Control Register bit assignments.

Figure 2-1 SCU Control Register bit assignments

Table 2-2 shows the SCU Control Register bit assignments.

Table 2-2 SCU Control Register bit assignments

| Bits   | Name                             | Function                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:7] | -                                | Reserved                                                                                                                                                                                                                                                                                                                                                                                         |

| [6]    | IC standby enable                | When set, this stops the Interrupt Controller clock when no interrupts are pending, and no CPU is performing a read/write request.  This bit is set to 0 by default                                                                                                                                                                                                                              |

| [5]    | SCU standby enable               | When set, SCU CLK is turned off when all processors are in WFI mode, there is no pending request on the ACP, if implemented, and there is no remaining activity in the SCU.  When SCU CLK is off, ARREADYS, AWREADYS and WREADYS on the ACP are forced LOW. The clock is turned on when any processor leaves WFI mode, or if there is a new request on the ACP.  This bit is set to 0 by default |

| [4]    | Force all Device to port0 enable | When set, all requests from the ACP or processors with <b>AxCACHE</b> = Noncacheable Bufferable are forced to be issued on the AXI Master port M0. See <i>Address filtering capabilities</i> on page 2-17.  This bit is set to 0 by default                                                                                                                                                      |

| [3]    | SCU Speculative linefills enable | When set, coherent linefill requests are sent speculatively to the L2C-310 in parallel with the tag look-up. If the tag look-up misses, the confirmed linefill is sent to the L2C-310 and gets RDATA earlier because the data request was already initiated by the speculative request. This feature works only if the L2C-310 is present in the design.  This bit is set to 0 by default        |

Table 2-2 SCU Control Register bit assignments (continued)

| Bits | Name                     | Function                                                                                                                                                                                                                                                                                                                               |

|------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]  | SCU RAMs Parity enable   | <ul> <li>1 = Parity on.</li> <li>0 = Parity off. This is the default setting.</li> <li>This bit is always zero if support for parity is not implemented.</li> </ul>                                                                                                                                                                    |

| [1]  | Address filtering enable | <ul> <li>1 = Addressing filtering on.</li> <li>0 = Addressing filtering off.</li> <li>The default value is the value of FILTEREN sampled when nSCURESET is deasserted.</li> <li>This bit is always zero if the SCU is implemented in the single master port configuration. See Address filtering capabilities on page 2-17.</li> </ul> |

| [0]  | SCU enable               | <ul><li>1 = SCU enable.</li><li>0 = SCU disable. This is the default setting.</li></ul>                                                                                                                                                                                                                                                |

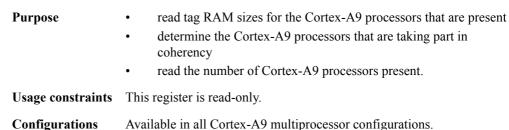

# 2.2.2 SCU Configuration Register

**Attributes**

The SCU Configuration Register characteristics are:

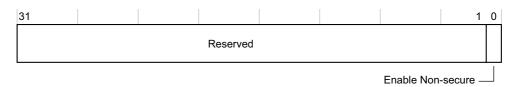

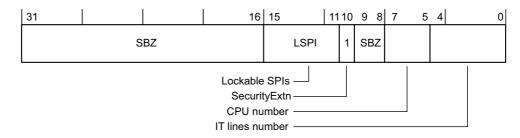

Figure 2-2 shows the SCU Configuration Register bit assignments.

See the register summary in *SCU registers* on page 2-3.

Figure 2-2 SCU Configuration Register bit assignments

Table 2-3 shows the SCU Configuration Register bit assignments.

Table 2-3 SCU Configuration Register bit assignments

| Bits    | Name          | Function                                                                                                                             |

|---------|---------------|--------------------------------------------------------------------------------------------------------------------------------------|

| [31:16] | -             | Reserved, SBZ.                                                                                                                       |

| [15:8]  | Tag RAM sizes | Bits [15:14] indicate Cortex-A9 processor CPU3 tag RAM size if present.                                                              |

|         |               | Bits [13:12] indicate Cortex-A9 processor CPU2 tag RAM size if present.                                                              |

|         |               | Bits [11:10] indicate Cortex-A9 processor CPU1 tag RAM size if present.                                                              |

|         |               | Bits [9:8] indicate Cortex-A9 processor CPU0 tag RAM size.                                                                           |

|         |               | The encoding is as follows:                                                                                                          |

|         |               | b11 = reserved                                                                                                                       |

|         |               | b10 = 64KB cache, 256 indexes per tag RAM                                                                                            |

|         |               | b01 = 32KB cache, 128 indexes per tag RAM                                                                                            |

|         |               | b00 = 16KB cache, 64 indexes per tag RAM.                                                                                            |

|         |               | Non-present CPUs have a Tag RAM size of b00, the same as 16KB.                                                                       |

| [7:4]   | CPUs SMP      | Shows the Cortex-A9 processors that are in <i>Symmetric Multi-processing</i> (SMP) or <i>Asymmetric Multi-processing</i> (AMP) mode. |

|         |               | 0 = this Cortex-A9 processor is in AMP mode not taking part in coherency or not present.                                             |

|         |               | 1 = this Cortex-A9 processor is in SMP mode taking part in coherency.                                                                |

|         |               | Bit 7 is for CPU3                                                                                                                    |

|         |               | Bit 6 is for CPU2                                                                                                                    |

|         |               | Bit 5 is for CPU1                                                                                                                    |

|         |               | Bit 4 is for CPU0.                                                                                                                   |

| [3:2]   | -             | Reserved, SBZ                                                                                                                        |

| [1:0]   | CPU number    | Number of CPUs present in the Cortex-A9 MPCore processor                                                                             |

|         |               | b11 = four Cortex-A9 processors, CPU0, CPU1, CPU2, and CPU3                                                                          |

|         |               | b10 = three Cortex-A9 processors, CPU0, CPU1, and CPU2                                                                               |

|         |               | b01 = two Cortex-A9 processors, CPU0 and CPU1                                                                                        |

|         |               | b00 = one Cortex-A9 processor, CPU0.                                                                                                 |

# 2.2.3 SCU CPU Power Status Register

The SCU CPU Power Status Register characteristics are:

| Purpose           | Specifies the state of the Cortex-A9 processors with reference to power modes                                                                                                                                                                                                                                                                                     |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Usage constraints | This register is writable in Secure state if the relevant bit in the SAC register is set.                                                                                                                                                                                                                                                                         |

|                   | This register is writable in Non-secure state if the relevant bits in the SAC and SNSAC registers are set.                                                                                                                                                                                                                                                        |

|                   | Dormant mode and powered-off mode are controlled by an external power controller. SCU CPU Status Register bits indicate to the external power controller the power domains that can be powered down.                                                                                                                                                              |

|                   | Before entering any other power mode than Normal, the Cortex-A9 processor must set its status field to signal to the power controller the mode it is about to enter. The Cortex-A9 processor then executes a WFI entry instruction. When in WFI state, the <b>PWRCTLOn</b> bus is enabled and signals to the power controller what it must do with power domains. |

The SCU CPU Power Status Register bits can also be read by a Cortex-A9 processor exiting low-power mode to determine its state before executing its reset setup.

Cortex-A9 processors status fields take **PWRCTLIn** values at reset, except for nonpresent Cortex-A9 processors. For nonpresent Cortex-A9 processors writing to this field has no effect.

**Configurations** Available in all Cortex-A9 MPCore configurations.

**Attributes** See the register summary in *SCU registers summary* on page 2-3.

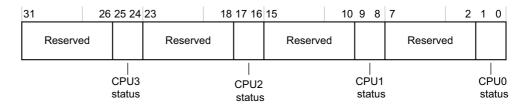

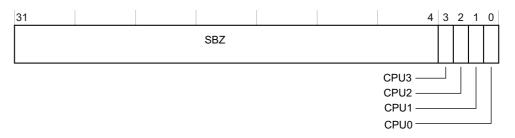

Figure 2-3 shows the SCU CPU Power Status Register bit assignments.

Figure 2-3 SCU CPU Power Status Register bit assignments

Table 2-4 shows the SCU CPU Power Status Register bit assignments.

Table 2-4 SCU CPU Power Status Register bit assignments

| Bits    | Name        | Function                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:26] | -           | Reserved, SBZ                                                                                                                                                                                                                                                                                                                                                                                                                       |

| [25:24] | CPU3 status | Power status of the Cortex-A9 processor: b00: Normal mode. b01: Reserved. b10: the Cortex-A9 processor is about to enter, or is in, dormant mode. No coherency request is sent to the Cortex-A9 processor. b11: the Cortex-A9 processor is about to enter, or is in, powered-off mode, or is nonpresent. No coherency request is sent to the Cortex-A9 processor. The default value is b00 when CPU3 processor is present, else b11 |

| [23:18] | -           | Reserved, SBZ                                                                                                                                                                                                                                                                                                                                                                                                                       |

| [17:16] | CPU2 status | Power status of the Cortex-A9 processor.  The default value is b00 when CPU2 processor is present, else b11                                                                                                                                                                                                                                                                                                                         |

| [15:10] | -           | Reserved, SBZ                                                                                                                                                                                                                                                                                                                                                                                                                       |

| [9:8]   | CPU1 status | Power status of the Cortex-A9 processor.  The default value is b00 when CPU1 processor is present, else b11                                                                                                                                                                                                                                                                                                                         |

| [7:2]   | -           | Reserved, SBZ                                                                                                                                                                                                                                                                                                                                                                                                                       |

| [1:0]   | CPU0 status | Power status of the Cortex-A9 processor.  The default value is b00 when CPU0 processor is present, else b11                                                                                                                                                                                                                                                                                                                         |

# 2.2.4 SCU Invalidate All Registers in Secure State Register

The SCU Invalidate All Registers in Secure State characteristics are:

**Purpose** Invalidates the SCU tag RAMs on a per Cortex-A9 processor and per way

basis.

Usage constraints This register:

• Invalidates all lines in the selected ways.

• Is a write-only register that always reads as zero.

**Configurations** Available in all Cortex-A9 multiprocessor configurations.

**Attributes** See the register summary in *SCU registers summary* on page 2-3.

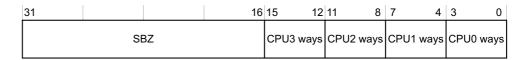

Figure 2-4 shows the SCU Invalidate All Register in Secure state bit assignments.

Figure 2-4 SCU Invalidate All Registers in Secure state bit assignments

Table 2-5 shows the SCU Invalidate All Register in Secure state bit assignments.

Table 2-5 SCU Invalidate All Registers in Secure state bit assignments

| Bits    | Name      | Function                                                                                                                                                     |

|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:16] | -         | -                                                                                                                                                            |

| [15:12] | CPU3 ways | Specifies the ways that must be invalidated for CPU3. Writing to these bits has no effect if the Cortex-A9 MPCore processor has fewer than four processors.  |

| [11:8]  | CPU2 ways | Specifies the ways that must be invalidated for CPU2. Writing to these bits has no effect if the Cortex-A9 MPCore processor has fewer than three processors. |

| [7:4]   | CPU1 ways | Specifies the ways that must be invalidated for CPU1. Writing to these bits has no effect if the Cortex-A9 MPCore processor has fewer than two processors.   |

| [3:0]   | CPU0 ways | Specifies the ways that must be invalidated for CPU0.                                                                                                        |

#### 2.2.5 Filtering Start Address Register

The Filtering Start Address Register characteristics are:

**Purpose** Provides the start address for use with master port 1 in a two-master port

configuration.

**Usage constraints** This register is writable:

• in Secure state if the relevant bit in the SAC register is set.

• in Non-secure state if the relevant bits in the SAC and SNSAC registers are set.

registers are se

**Configurations** Available in all two-master port configurations. When only one master

port is present these registers are not implemented. Writes have no effect

and reads return a value 0x0 for all filtering registers.

**Attributes** See the register summary in *SCU registers summary* on page 2-3.

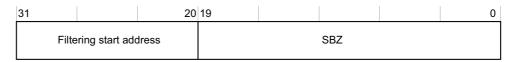

Figure 2-5 shows the Filtering Start Address Register bit assignments.

Figure 2-5 Filtering Start Address Register bit assignments

Table 2-6 shows the Filtering Start Address Register bit assignments.

Table 2-6 Filtering Start Address Register bit assignments

| Bits    | Name                    | Function                                                                                                                                                                                                                                                                 |

|---------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:20] | Filtering start address | Start address for use with master port 1 in a two-master port configuration when address filtering is enabled.  The default value is the value of <b>FILTERSTART</b> sampled on exit from reset. The value on the pin gives the upper address bits with 1MB granularity. |

| [19:0]  | -                       | SBZ                                                                                                                                                                                                                                                                      |

See *Configuration signals* on page A-5.

# 2.2.6 Filtering End Address Register

The Filtering End Address Register characteristics are:

**Purpose** Provides the end address for use with master port 1 in a two-master port configuration.

Usage constraints This register is writable

- in Secure state if the relevant bit in the SAC register is set.

- in Non-secure state if the relevant bits in the SAC and SNSAC registers are set.

- has an inclusive address as its end address. This means that the topmost megabyte of address space of memory can be included in the filtering address range.

Configurations

Available in all two-master product configurations. When only one master port is present writes have no effect and reads return a value 0x0 for all filtering registers.

**Attributes** See the register summary in Table 2-1 on page 2-3.

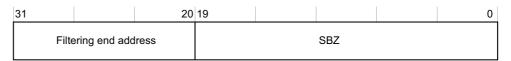

Figure 2-6 shows the Filtering End Address Register bit assignments.

Figure 2-6 Filtering End Address Register bit assignments

Table 2-7 shows the Filtering End Address Register bit assignments.

Table 2-7 Filtering End Address Register bit assignments

| Bits    | Name                  | Function                                                                                                                                                                                                                                                              |

|---------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:20] | Filtering end address | End address for use with master port 1 in a two-master port configuration, when address filtering is enabled.  The default value is the value of <b>FILTEREND</b> sampled on exit from reset. The value on the pin gives the upper address bits with 1MB granularity. |

| [19:0]  | -                     | SBZ.                                                                                                                                                                                                                                                                  |

See Configuration signals on page A-5.

#### 2.2.7 SCU Access Control Register (SAC)

The SAC characteristics are:

#### **Purpose**

Controls access to the following registers on a per Cortex-A9 processor basis:

- SCU Control Register on page 2-3

- SCU CPU Power Status Register on page 2-6

- SCU Invalidate All Registers in Secure State Register on page 2-8

- Filtering Start Address Register on page 2-8

- Filtering End Address Register on page 2-9

- SCU Non-secure Access Control Register on page 2-11.

A processor in the Cortex-A9 MPCore multiprocessor can set up the SCU and then write zero to the register. This prevents any Secure or Non-secure access from altering the configuration of the register again. This prevents any more changes to the SCU configuration after booting.

#### **Usage constraints**

This register is writable:

- in Secure state if the relevant bit in the SAC register is set.

- in Non-secure state if the relevant bits in the SAC and SNSAC are set.

# Configurations

Available in all Cortex-A9 MPCore configurations.

#### Attributes

See the register summary in *SCU registers summary* on page 2-3.

Figure 2-7 shows the SAC register bit assignments.

Figure 2-7 SAC register bit assignments

Table 2-8 shows the SAC register bit assignments.

Table 2-8 SAC register bit assignments

| Bits   | Name | Function                                                                                                     |

|--------|------|--------------------------------------------------------------------------------------------------------------|

| [31:4] | SBZ  | -                                                                                                            |

| [3]    | CPU3 | 0 = CPU3 cannot access the registers <sup>a</sup><br>1 = CPU3 can access the registers. This is the default. |

| [2]    | CPU2 | 0 = CPU2 cannot access the registers.<br>1 = CPU2 can access the registers. This is the default.             |

| [1]    | CPU1 | 0 = CPU1 cannot access the registers.<br>1 = CPU1 can access the registers. This is the default.             |

| [0]    | CPU0 | 0 = CPU0 cannot access the registers.<br>1 = CPU0 can access the registers. This is the default.             |

a. The accessible registers are the SAC Register, the SCU Control Register, the SCU CPU Status Register, the SCU Invalidate All Register in Secure State, the filtering registers, and the SCU CPU Power Status register.

#### 2.2.8 SCU Non-secure Access Control Register

The SNSAC register characteristics are:

#### **Purpose**

Controls Non-secure access to the following registers on a per Cortex-A9 processor basis:

- SCU Control Register on page 2-3

- SCU CPU Power Status Register on page 2-6

- Filtering Start Address Register on page 2-8

- Filtering End Address Register on page 2-9

- SCU Access Control Register (SAC) on page 2-10.

In addition it controls Non-secure access to the global timer, private timers, and watchdog.

#### **Usage constraints**

This register is writable in Secure state if the relevant bit in the SAC register is set.

# Configurations

Available in all Cortex-A9 multiprocessor configurations.

#### **Attributes**

See the register summary in Table 2-1 on page 2-3.

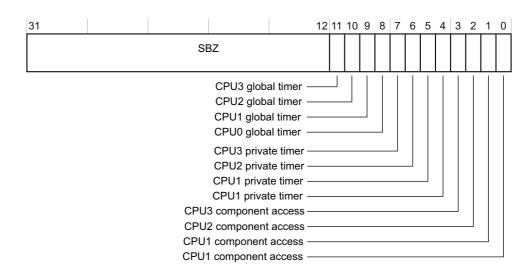

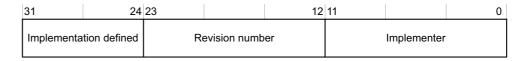

Figure 2-8 on page 2-12 shows the SNSAC register bit assignments.

Figure 2-8 SNSAC register bit assignments

Table 2-9 shows the SNSAC register bit assignments.

Table 2-9 SNSAC register bit assignments

| Bits    | Name                | Function                                                                                                                                                                                    |

|---------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:12] | SBZ                 | -                                                                                                                                                                                           |

| [11]    | CPU3 global timer   | Non-secure access to the global timer for CPU <n>.</n>                                                                                                                                      |

| [10]    | CPU2 global timer   | <ul> <li><n> is 3 for bit[11]</n></li> <li><n> is 2 for bit[10]</n></li> </ul>                                                                                                              |

| [9]     | CPU1 global timer   | • <n> is 1 for bit[19]</n>                                                                                                                                                                  |

| [8]     | CPU0 global timer   | <ul> <li><n> is 0 for bit[8].</n></li> <li>0 = Secure accesses only. This is the default value.</li> <li>1 = Secure accesses and Non-Secure accesses.</li> </ul>                            |

| [7]     | Private timers for  | Non-secure access to the private timer and watchdog for CPU <n>.</n>                                                                                                                        |

| [6]     | - CPU <n></n>       | <ul><li><n> is 3 for bit[7]</n></li><li><n> is 2 for bit[6]]</n></li></ul>                                                                                                                  |

| [5]     | -                   | • <n> is 1 for bit[5]</n>                                                                                                                                                                   |

| [4]     | -                   | <ul> <li><n> is 0 for bit[4].</n></li> <li>0 = Secure accesses only. Non-secure reads return 0. This is the default value.</li> <li>1 = Secure accesses and Non-secure accesses.</li> </ul> |

| [3]     | Register access for | Non-secure access to the registers for CPU <n>.</n>                                                                                                                                         |

| [2]     | CPU <n></n>         | <ul> <li><n> is 3 for bit[3]</n></li> <li><n> is 2 for bit[2]]</n></li> </ul>                                                                                                               |

| [1]     |                     | <ul><li><n> is 2 for bit[2]]</n></li><li><n> is 1 for bit[1]</n></li></ul>                                                                                                                  |

| [0]     | -                   | <ul> <li><n> is 0 for bit[0].</n></li> <li>0 = CPU cannot write the registers<sup>a</sup></li> </ul>                                                                                        |

|         |                     | $1 = \text{CPU can access the registers}^{\text{a}}$ .                                                                                                                                      |

a. The accessible registers are the SAC Register, the SCU Control Register, the SCU CPU Status Register, the filtering registers, and the SCU CPU Power Status Register.

# 2.3 AMBA AXI Master Port Interfaces

The following sections describe the AMBA AXI interfaces:

- *AXI issuing capabilities*

- Cortex-A9 MPCore AXI transactions on page 2-14

- AXI transaction IDs on page 2-14

- AXI USER attributes encodings on page 2-15

- *Address filtering capabilities* on page 2-17.

- AXI master interface clocking on page 2-18.

- *ACP interface clocking* on page 2-21.

#### 2.3.1 AXI issuing capabilities

The Cortex-A9 MPCore L2 interface can have two 64-bit wide AXI bus masters. In a two bus master configuration there is also an option to configure address filtering. See *Address filtering capabilities* on page 2-17. Table 2-10 shows the AXI master interface attributes.

Table 2-10 AXI master interface attributes

| Attribute                   | Format                                                                       |

|-----------------------------|------------------------------------------------------------------------------|

| Write Issuing Capability    | 10 per processor, including:                                                 |

|                             | • 8 non-cacheable writes                                                     |

|                             | • 2 evictions.                                                               |

|                             | 2 additional writes can also be performed for eviction traffic from the SCU. |

|                             | 3 more write transactions can be issued if the ACP is implemented.           |

| Read Issuing Capability     | 14 per processor, including:                                                 |

|                             | • 4 instruction reads                                                        |

|                             | • 6 linefill reads.                                                          |

|                             | • 4 non-cacheable read.                                                      |

|                             | 7 more read transactions can be issued if the ACP is implemented.            |

| Combined Issuing Capability | Up to 24 per processor.                                                      |

|                             | Plus 2 for SCU evictions                                                     |

|                             | 10 more transactions can be issued, if the ACP is implemented.               |

| Write ID Capability         | 32                                                                           |

| Write Interleave Capability | 1                                                                            |

| Write ID Width              | 6                                                                            |

| Read ID Capability          | 32                                                                           |

| Read ID Width               | 6                                                                            |

The AXI protocol and meaning of each AXI signal are not described in this document. For more information see *AMBA AXI Protocol v1.0 Specification*.

| —— Note ——— |

|-------------|

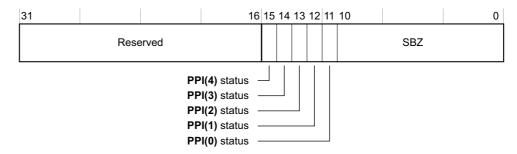

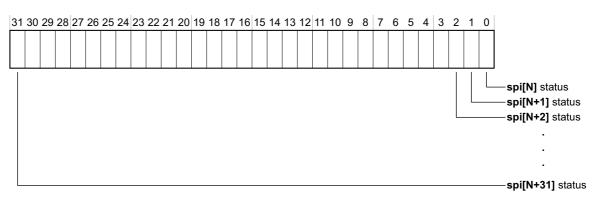

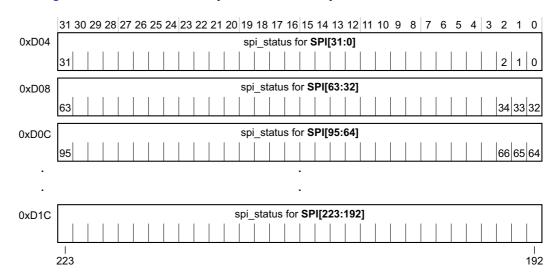

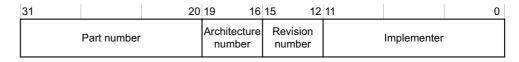

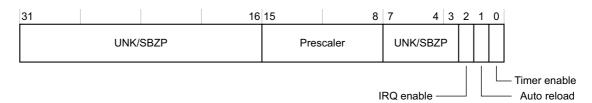

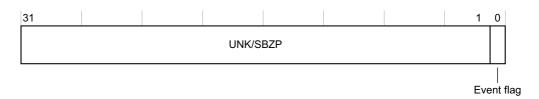

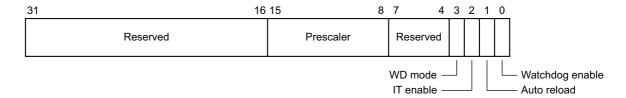

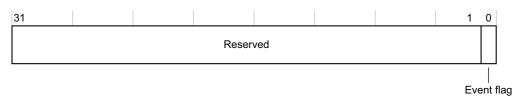

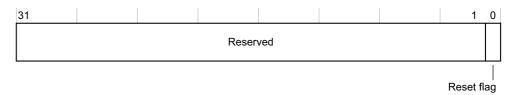

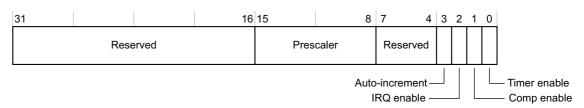

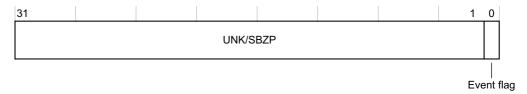

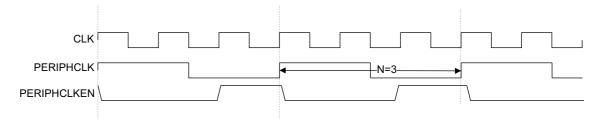

|-------------|