Technical Report

Number 975

**Computer Laboratory**

# Memory safety with CHERI capabilities: security analysis, language interpreters, and heap temporal safety

Brett Gutstein

November 2022

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

#### © 2022 Brett Gutstein

This technical report is based on a dissertation submitted July 2022 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Trinity College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Abstract

#### Memory safety with CHERI capabilities: security analysis, language interpreters, and heap temporal safety

#### Brett Ferdosi Gutstein

CHERI (Capability Hardware Enhanced RISC Instructions) is a promising research processor-architecture protection model that facilitates memory safety and fine-grained compartmentalization for software. The architecture has reached a mature state and been integrated into Arm's industrial-scale Morello system-on-chip, a large corpus of software has been adapted to support CHERI, and prior work has demonstrated that replacing integer pointers with CHERI capabilities can make C and C++ programs spatially safe. In this dissertation, I identify gaps that limit the ability of current mitigations based on CHERI to deliver real-world vulnerability protection, and I work towards addressing them.

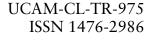

I develop the memory-operations framework (MOF) for reasoning about memory-safety mitigations and the types of attacks they prevent. I apply the MOF to analyze CheriABI, the most sophisticated memory-safety mitigation built atop CHERI. I also evaluate CheriABI's effectiveness in mitigating a set of real-world attacks that targeted devices running Apple's iOS. Based on this evaluation, I identify two key areas in CHERI-supported memory safety that require improved protections.

One of these areas involves support for contemporary programming language interpreters, which have not previously been adapted to CHERI. Using Apple's JavaScriptCore as a case study, I evaluate the feasibility, source-code compatibility, and security properties of adapting an interpreter that supports just-in-time compilation to CHERI. I determine that such an adaptation is feasible, practical, and can achieve parity with more typical applications in terms of memory protection.

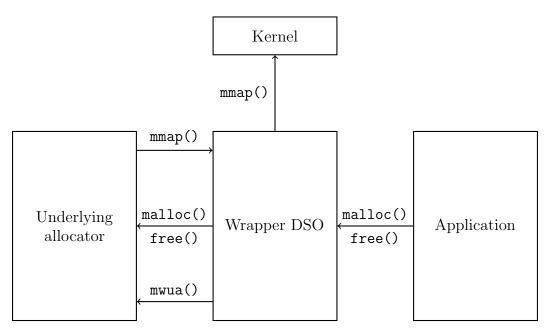

The other area is providing temporal safety for userspace heaps, which CheriABI does not currently support. I introduce novel algorithms and software components that constitute a fully elaborated system for CHERI-based userspace heap temporal safety. I implement the system, which includes the Cornucopia kernel subsystem for sweeping capability revocation and a generic userspace library that encapsulates changes required for memory allocators, in CheriBSD for Morello. Relative to the CHERIvoke algorithm for heap temporal safety, which has previously been published but not implemented on CHERI hardware, the novel algorithms reduce application runtimes by up to 23.5% and pause times by up to 11,000x, potentially making temporal safety with CHERI feasible for large, real-world workloads.

# Acknowledgements

Thanks to my supervisor Robert Watson for his guidance, understanding, and support. To my colleague Wes Filardo for his kindness and erudition. To all members of the CHERI project, and especially Alex Richardson, Jessica Clarke, Peter Neumann, and John Baldwin, for making this work possible. To my examiners Alan Mycroft and Howie Shrobe for their valuable engagement. Thanks to the Gates Cambridge Trust for the generous funding, and to Arm Limited for providing access to computing resources. Above all, thanks to my family and friends, without whom I would not have made it to the finish line.

# Contents

| 1        | $\operatorname{Intr}$ | roduction                                                                                                                 | 9  |

|----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|----|

|          | 1.1                   | Contributions                                                                                                             | 10 |

|          | 1.2                   | Publications                                                                                                              | 12 |

|          | 1.3                   | Infrastructural contributions                                                                                             | 13 |

|          | 1.4                   | Work performed in collaboration with others                                                                               | 13 |

|          | 1.5                   | Outline                                                                                                                   | 14 |

| <b>2</b> | Bac                   | kground 1                                                                                                                 | 5  |

| _        | 2.1                   | 5                                                                                                                         | 15 |

|          |                       |                                                                                                                           | 17 |

|          |                       | 0                                                                                                                         | 19 |

|          |                       | 0                                                                                                                         | 19 |

|          |                       | 1 0                                                                                                                       | 20 |

|          |                       |                                                                                                                           | 20 |

|          |                       |                                                                                                                           | 21 |

|          | 2.2                   |                                                                                                                           | 22 |

|          | 2.3                   |                                                                                                                           | 23 |

|          | -                     |                                                                                                                           | 23 |

|          |                       | 1 0                                                                                                                       | 24 |

|          | 2.4                   | 1 0 0                                                                                                                     | 25 |

|          |                       |                                                                                                                           | 26 |

|          | 2.5                   |                                                                                                                           | 27 |

|          |                       |                                                                                                                           | 28 |

|          | 2.6                   |                                                                                                                           | 28 |

|          | 2.7                   | 1                                                                                                                         | 30 |

|          | 2.8                   |                                                                                                                           | 32 |

| 3        | The                   | e memory-operations framework 3                                                                                           | 85 |

| 0        | 3.1                   | • -                                                                                                                       | 35 |

|          | 0.1                   | 1                                                                                                                         | 36 |

|          |                       | . 0                                                                                                                       | 36 |

|          |                       |                                                                                                                           | 36 |

|          |                       |                                                                                                                           | 37 |

|          | 3.2                   |                                                                                                                           | 38 |

|          | 0.2                   |                                                                                                                           | 38 |

|          |                       |                                                                                                                           | 38 |

|          | 3.3                   |                                                                                                                           | 39 |

|          | 0.0                   | •                                                                                                                         | 39 |

|          |                       | $-0\cdot0\cdot1 = 1\cdot0\cdot1 + 1\cdot1\cdot1 + 1\cdot1\cdot1\cdot1 + 1\cdot1\cdot1\cdot1\cdot1\cdot1\cdot1\cdot1\cdot$ | 10 |

|          |     | 3.3.2 Threat model $\ldots \ldots 40$                                    |

|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |     | 3.3.3 Memory protections                                                                                                                                                   |

|          | 3.4 | Project Zero iOS exploit chain analysis                                                                                                                                    |

|          |     | $3.4.1$ Exploit chains $\ldots \ldots 43$                                       |

|          |     | 3.4.2 Results                                                                                                                                                              |

|          | 3.5 | Discussion                                                                                                                                                                 |

|          |     |                                                                                                                                                                            |

| 4        |     | aScriptCore on CHERI 51                                                                                                                                                    |

|          | 4.1 | Feasibility                                                                                                                                                                |

|          |     | 4.1.1 Summary of changes                                                                                                                                                   |

|          |     | 4.1.2 Generality $\ldots \ldots 57$                                                    |

|          |     | 4.1.3 Correctness                                                                                                                                                          |

|          | 4.2 | Source-code compatibility                                                                                                                                                  |

|          | 4.3 | Security $\ldots \ldots \ldots$                            |

|          |     | 4.3.1 Pure-capability JSC                                                                                                                                                  |

|          |     | 4.3.2 Parity with CheriABI                                                                                                                                                 |

|          |     | 4.3.3 Existing mitigations                                                                                                                                                 |

|          | 4.4 | Discussion                                                                                                                                                                 |

|          |     | 4.4.1 Future work $\ldots \ldots \ldots$                   |

| <b>5</b> | Hea | p temporal safety 69                                                                                                                                                       |

| 0        | 5.1 | Introduction                                                                                                                                                               |

|          | -   | 5.1.1 Heap temporal safety as capability revocation                                                                                                                        |

|          |     | 5.1.2 Sweeping capability revocation                                                                                                                                       |

|          |     | 5.1.3 CHERIvoke                                                                                                                                                            |

|          |     | 5.1.4 Temporal safety with Cornucopia                                                                                                                                      |

|          | 5.2 | The Cornucopia kernel subsystem                                                                                                                                            |

|          | 0.2 | 5.2.1 Subsystem design                                                                                                                                                     |

|          |     | 5.2.2 Store-side barrier algorithm                                                                                                                                         |

|          |     | 5.2.3 Load-side barrier algorithm                                                                                                                                          |

|          | 5.3 | Temporally safe heap allocators                                                                                                                                            |

|          | 0.0 | 5.3.1 Heap allocator prerequisites                                                                                                                                         |

|          |     | 5.3.2 Adapting heap allocators                                                                                                                                             |

|          |     | 5.3.3 Allocator-independent wrapper                                                                                                                                        |

|          | 5.4 | Evaluation $\ldots$                                                                       |

|          | 0.1 | 5.4.1 Effectiveness                                                                                                                                                        |

|          |     | 5.4.2 Sweeping revocation algorithms                                                                                                                                       |

|          |     | 5.4.3 Cornucopia wrapper module                                                                                                                                            |

|          |     | $5.4.3.1$ Source-code compatibility $\ldots \ldots \ldots$ |

|          |     | $5.4.3.2$ Performance $\ldots \ldots \ldots$               |

|          | 5.5 | Discussion                                                                                                                                                                 |

|          | 0.0 | 5.5.1 Future work                                                                                                                                                          |

|          |     | 5.5.1 Tuture work                                                                                                                                                          |

| 6        | Cor | nclusions 107                                                                                                                                                              |

|          | 6.1 | Contributions                                                                                                                                                              |

|          | 6.2 | Future work                                                                                                                                                                |

|          |     |                                                                                                                                                                            |

#### Bibliography

# Chapter 1

# Introduction

Computers govern increasingly important aspects of our lives, but security for computer systems remains elusive. Cybersecurity breaches in major organizations, including computing giants like Facebook [16], fuel pipeline operators [80], and the United Kingdom's National Health Service [117], regularly affect millions of people, causing significant financial and human losses.

The security vulnerabilities that facilitate these breaches can be divided into three types. The first type involves problems related to human-computer use. A computer system that is perfectly engineered can still be attacked if the people using it are vulnerable to manipulation. For example, they might have their credentials stolen or be influenced to leak sensitive data. A July 2020 Twitter attack that compromised 130 of the highest profile accounts and used them to solicit cryptocurrency transfers was carried out by a 17-year-old who used social engineering to access an internal Twitter tool [114]. While defending against these kinds of attacks is crucially important, the multidisciplinary effort required to do so is beyond the scope of this dissertation.

The second type involves logic errors in the engineering of computer systems. For example, a programmer might forget to include the appropriate authentication checks before performing some privileged operation. These types of errors might seem unlikely to pass rigorous testing and quality assurance protocols, but obvious mistakes end up in even the most widely used systems. A bug in an Uber API, discovered in 2019, allowed any user to obtain sensitive information and take over the account of any other user for whom they had a phone number or email address [123]. The flaw behind this bug was a failure to authenticate the user making the request. It is impossible to detect logic errors automatically in general, since any automatic checker must be given a correct abstract specification of the system that is itself free from logic errors. Logic errors are also out of scope for this dissertation.

The third type concerns vulnerabilities in the engineering of computer systems that can be detected and mitigated automatically. Memory-safety vulnerabilities, which are possible in low-level languages like C and C++ when a program allows for the integrity of its memory objects to be violated, fall into this category. There are various techniques for mitigating memory-safety vulnerabilities automatically, but so far none has achieved widespread adoption. In 2019, Microsoft reported that memory-safety errors are behind approximately 70% of security vulnerabilities in their products [22], and in 2016 Google stated that about 86% of Android vulnerabilities are memory-safety related [23].

One way to mitigate memory-safety vulnerabilities automatically is to use higher-level languages that eliminate them by design. However, it would require a huge amount of labor and expertise to rewrite and retest the hundreds of millions of lines of low-level code that underpin current computing infrastructure. Furthermore, the loss of fine-grained system control that comes with higher-level languages limits their suitability for certain kinds of software.

It is also possible to mitigate memory-safety vulnerabilities automatically for existing C/C++ codebases by augmenting compilers with instrumentation and dynamic checks. To date, however, schemes that do so in software have come with high performance overheads that make them impractical. Hardware support has the potential to reduce overheads significantly, but past hardware designs that support the effective mitigation of memory-safety vulnerabilities have not been deployed in realistic, high-fidelity microarchitectures.

CHERI (Capability Hardware Enhanced RISC Instructions) [118, 120, 125], is a promising research processor-architecture protection model that facilitates memory safety for C and C++ codebases by extending existing instruction set architectures with hardwaretagged memory capabilities. Over more than ten years of research effort, the CHERI project has reached a mature state, and a large corpus of software has been adapted to support it. This corpus includes the CHERI-LLVM compiler [27], the general-purpose CheriBSD operating system [25], special-purpose operating systems like CheriFreeRTOS [26], and a number of substantive applications such as PostgreSQL [28]. Currently, the most sophisticated memory-safety mitigation built using CHERI is the CheriABI C/C++ execution environment, which has been shown to provide complete spatial memory safety for C/C++ programs at a reasonable performance cost [32, 99].

CHERI technology has been deployed and validated in increasingly high-fidelity systems. CHERI extensions exist for MIPS, RISC-V, and ARM architectures, and example processor implementations have been developed for QEMU and FPGA. The ARMv8-A extension, known as Morello, was developed by the University of Cambridge in collaboration with Arm and is the subject of the £187M UKRI Digital Security by Design program [69, 70, 113]. As part of this program, Arm has produced an industrial-quality system-on-chip, with superscalar, out-of-order CPU cores, that implements the CHERI Morello architecture. The system-on-chip and the architecture it implements are both called Morello.

Despite impressive results so far, there remain various outstanding research questions that must be addressed to facilitate robust memory safety and real-world vulnerability mitigation with CHERI. In the following chapters, I identify some of these gaps and work towards closing them.

#### **1.1** Contributions

In this dissertation, I make a number of contributions related to analyzing and extending the security properties that C/C++ applications can achieve with CHERI-supported memory safety:

Security analysis I develop the novel memory-operations framework (MOF) for reasoning about memory-safety mitigations and the types of attacks that they prevent. Using the MOF, I systematize the security properties of CheriABI [32], which has not previously been done. I further use the framework to analyze exploits that were carried out against devices running Apple's iOS in the wild to determine how CheriABI memory-safety protections would fare against contemporary real-world attacks. Based on this analysis, I identify important gaps in current research on memory safety with CHERI; namely, support for CHERI in programming-language interpreters and temporal safety for userspace heaps.

- **Programming-language interpreters** I perform a feasibility study to determine how CHERI memory-safety protections can be applied to harden contemporary interpreters that feature just-in-time compilation. Such interpreters have different characteristics from typical applications, and they have not been investigated in previous work on CHERI-supported memory safety. I adapt JavaScriptCore, the JavaScript interpreter in Apple's WebKit browser framework, to compile as pure-capability code, i.e. so that all pointers are implemented as CHERI capabilities. This adaptation includes a just-in-time compiler targeting the Morello platform. I determine that it is indeed possible to perform such an adaptation without affecting the interpreter's functionality, and that the source-code compatibility burden of doing so is comparable to that of adapting similar types of software. Applying the MOF, I determine that, unlike typical applications, language interpreters do not automatically gain all CheriABI security properties when adapted to support pure-capability compilation. However, I discover that straightforward changes to their memory allocators, JIT compilers, and build systems can bring their security properties up to par.

- Userspace heap temporal safety I propose, implement, and evaluate novel techniques and software components that constitute a fully elaborated system for CHERIbased userspace heap temporal safety. I introduce Cornucopia [122], a novel kernel subsystem of the CheriBSD operating system that userspace heap allocators can utilize to guarantee temporal safety. Cornucopia performs sweeping capability revocation for userspace processes. It can be configured to use the previously published CHERIvoke algorithm [127], which has never before been implemented on real CHERI hardware, as well as two novel algorithms with improved performance characteristics. These novel algorithms are inspired by past work on garbage collection and use Morello's architectural features to implement store-side or load-side barriers that allow sweeping capability revocation to be performed concurrently with the running application.

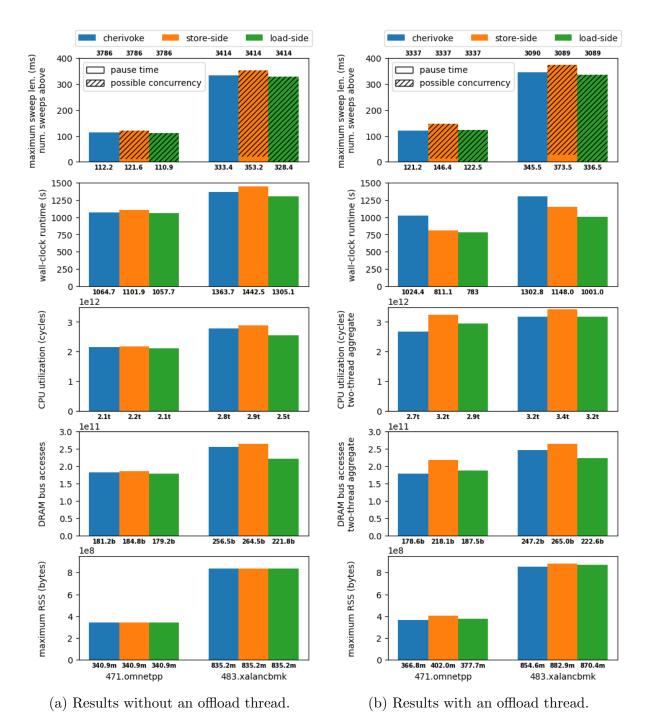

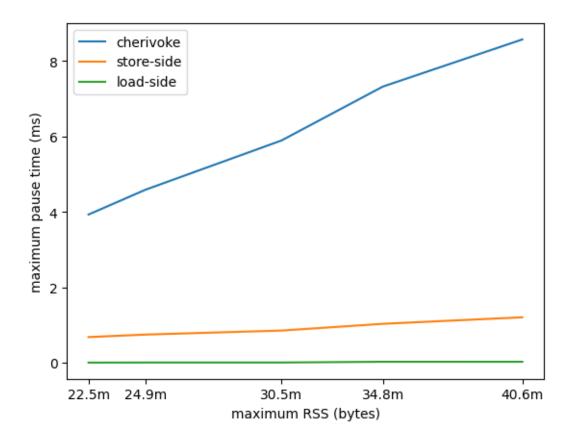

I evaluate these algorithms on Morello, producing the first performance results from a superscalar ASIC-based CHERI capability machine to be published. I determine that, relative to the CHERIvoke baseline, the novel algorithms reduce application runtimes by up to 23.5% and pause times by up to 11,000x. For the load-side barrier algorithm, application pause times are constant and do not scale with memory footprint; this feature potentially makes sweeping capability revocation feasible for large, real-world workloads.

I systematize a set of requirements that userspace heap allocators must meet in order to leverage the Cornucopia kernel subsystem to provide heap temporal safety, and I describe techniques for meeting them. I evaluate the effectiveness of heap temporal safety with Cornucopia and determine that it is possible to implement sweeping capability revocation on real CHERI hardware to mitigate heap temporal safety vulnerabilities in practice.

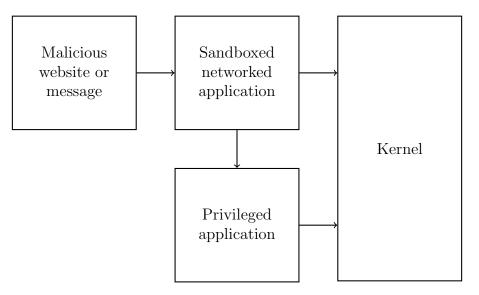

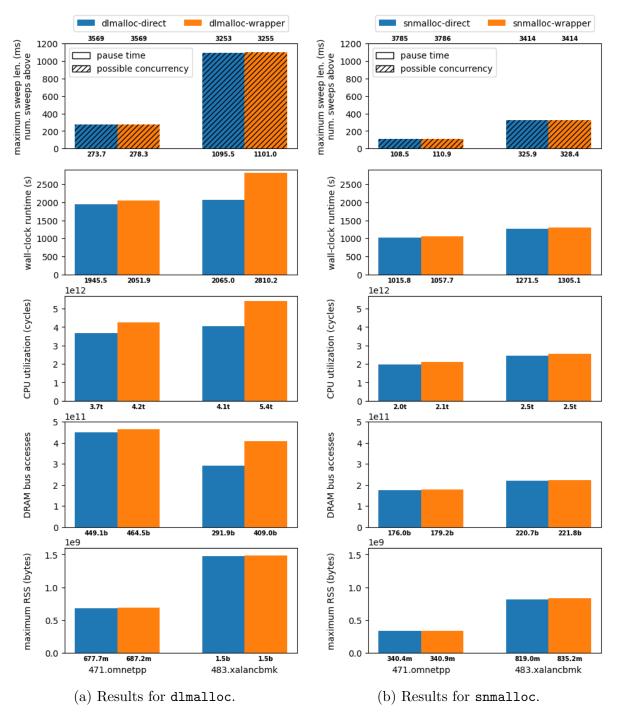

I also introduce a generic wrapper library that allows allocators to implement heap temporal safety with Cornucopia at a low source-code compatibility cost. This library demonstrates the unexpected result that it is possible to encapsulate temporal-safety logic without access to an allocator's internal data structures and synchronization primitives. Relative to modifying a contemporary memory allocator to integrate with Cornucopia directly, using this library can require fewer than 1% of the source-code changes and incur a performance cost of less than 5% in terms of runtime, CPU utilization, and DRAM traffic.

#### 1.2 Publications

During my PhD, I co-authored and delivered the following papers and presentations:

#### Peer-reviewed conference papers

- Nathaniel Wesley Filardo, Brett F. Gutstein, et al. Cornucopia: Temporal safety for CHERI heaps. In the 2020 IEEE Symposium on Security and Privacy (SP).

- A. Theodore Markettos, Colin Rothwell, Brett F. Gutstein, et al. Thunderclap: Exploring vulnerabilities in operating system IOMMU protection via DMA from untrustworthy peripherals. In Proceedings of the 2019 Network and Distributed System Security Symposium (NDSS).

#### Invited papers

- Brett F. Gutstein *et al. The ECATS project: Developments in the CHERI security architecture.* In Government Microcircuit Applications and Critical Technology Conference (GOMACTech) 2021.

- Brett F. Gutstein *et al. The ECATS project: CHERI and Thunderclap.* In Government Microcircuit Applications and Critical Technology Conference (GOMACTech) 2020.

#### Peer-reviewed presentations

• Brett F. Gutstein. *Challenges in system security evaluation*. At UK Systems Research Challenges Workshop 2019, Northumberland, UK.

#### Invited keynote presentations

• Brett F. Gutstein. *Thunderclap: a novel threat from malicious peripheral devices.* At NASK Secure Early Bird 2019, Warsaw, Poland.

#### Reports

- Peter G. Neumann and Brett F. Gutstein. *CHERI's mitigation of security vulnera-bilities.* Produced as part of the DARPA SSITH ECATS project.

- Nathaniel Wesley Filardo, Brett F. Gutstein, et al. Achelous: whence a better Cornucopia?. Technical report, in preparation.

## **1.3** Infrastructural contributions

I also made a number of scientific and engineering contributions to infrastructure that will support further CHERI-related research.

- I contributed to validation of the Arm Morello platform. I identified and reported issues in the Morello specification and carried out numerous tests on a high-fidelity FPGA implementation of the Morello hardware. One of these tests uncovered a hardware issue related to tag memory aliasing that was able to be worked around in firmware.

- I assisted in bringing up the CheriBSD operating system on Morello. I contributed kernel modifications for capability-aware boot, context switching, signal handling, and process startup. I also added initial runtime linker support for dynamically linked CheriABI binaries and modified a number of userspace applications to build correctly for Morello. I fixed multiple bugs in the hwpmc performance monitoring framework and added support for profiling position-independent executables.

- I adapted the JavaScriptCore JavaScript runtime, which is part of the WebKit framework that powers browsers including Apple's Safari and Mobile Safari, to Morello. This adaptation included support for multiple tiers of JavaScript execution, including the baseline JIT compiler, which was adapted in collaboration with Arm Limited.

- I adapted machine-dependent parts of CheriBSD's capability-revocation kernel subsystem to Morello.

- I designed and implemented a generic wrapper for userspace allocators that allows them to make use of sweeping capability revocation with minimal source code modification.

## 1.4 Work performed in collaboration with others

The CHERI project is a large and highly collaborative effort that comprises over a decade of work by dozens of team members. The work in this dissertation builds indirectly and directly on past contributions by others. I performed all of the experiments described, and, unless explicitly stated otherwise, I developed the ideas and systems under test, except for the following work performed by and in collaboration with others:

• Wes Filardo led development of the load-side and store-side barrier algorithms for concurrent sweeping capability revocation. I reviewed the store-side algorithm and helped to design the load-side algorithm. The evaluation of these algorithms in this dissertation is novel and solely my work.

Wes implemented the machine-independent, MIPS, and RISC-V components of the Cornucopia kernel subsystem for sweeping revocation in CheriBSD. I reviewed and made fixes to these components. I added a machine-dependent component for Morello, which leveraged features including hardware capability-dirty-bit tracking that are not present in other architectures. Wes added direct integration with Cornucopia to the snmalloc memory allocator. This allocator configuration is one of many that I use in my performance evaluation.

- Khilan Gudka and Alex Richardson initially adapted QtWebkit, including the C++ backend of JavaScriptCore's Low Level Interpreter, to support CHERI. Ruben Aryapetyan later extended their work to support JavaScriptCore up to the Baseline JIT compiler, targeting a precursor of Morello. I adapted the extension to target Morello, added features, and made a number of fixes and cleanups. Jacob Bramley helped to shepherd the Morello adaptation for public release.

- Brooks Davis and Hongyan Xia added direct integration with Cornucopia to the dlmalloc memory allocator. This allocator configuration is one of many that I use in my performance evaluation.

### 1.5 Outline

The rest of this dissertation is structured as follows. Chapter 2 covers background information that sets the stage for later chapters. In Chapter 3, I develop the memory-operations framework, as previously described in Section 1.1. I apply the MOF to analyze CheriABI and real-world exploits carried out against systems running iOS. Based on this analysis, I identify gaps in current CheriABI protections. These gaps include programming-language interpreters and temporal safety, as previously described in Section 1.1, and they motivate my contributions in Chapters 4 and 5. Chapter 4 investigates how contemporary language interpreters can be adapted to support CHERI. Chapter 5 covers novel sweeping capability revocation algorithms, the fully elaborated Cornucopia kernel subsystem for capability revocation, and the generic userspace library that allows heap allocators to offer temporal safety with little source code modification. Chapter 6 concludes the dissertation.

# Chapter 2

# Background

In this chapter, I cover background information and related work relevant to the rest of the dissertation. I first introduce the concept of memory safety in languages like C and C++, explain how memory safety bugs can be exploited, and summarize past memory safety attack techniques and mitigations. I then describe CHERI in detail, with a specific focus on Arm's Morello platform. I highlight CHERI properties that can help address problems related to memory safety, and I review previous work on C/C++ memory safety with CHERI. I then discuss virtual-machine language interpreters, operating-system virtual memory, and garbage collectors, which are relevant to work described in later chapters.

## 2.1 C/C++ memory safety

Generally speaking, memory safety is a property of individual programs. It describes whether or not a program allows the integrity of its memory objects to be violated during execution.

Memory objects are memory-backed constructs such as data structures and primitive data types. Their exact size and layout is determined by the program's compiler, and they might be allocated on the stack, in the heap, or as globals. Memory objects have abstract bounds that are determined by their size and location in memory as well as abstract lifetimes that are determined by their storage class.

Memory safety can be divided into three aspects:

- **Spatial safety** A program is spatially safe if it guarantees the integrity of memory object bounds. This means that a reference to a memory object cannot be used to access memory outside of that object, e.g. by over-running a buffer contained in the memory object.

- **Temporal safety** A program is temporally safe if it guarantees the integrity of memory object lifetimes. This means that memory used to store one memory object cannot be used simultaneously to store another memory object, e.g. as a result of dangling pointers to the heap.

- **Type safety** A program is type safe if it guarantees the integrity of memory object types. This means that a memory object referenced as one type cannot simultaneously be referenced as a memory object of an incompatible type, e.g. via a C-style union or type cast.

Some programming languages, such as Java and OCaml, produce programs that are memory-safe by construction. They do not allow the programmer to express operations that would violate the integrity of memory objects.

On the other hand, languages like C and C++ give programmers significant control over data representation and pointer use. This control makes C and C++ well suited to systems programming, but it also allows for the creation of programs that are not memory safe.

Features of a program that allow for the integrity of memory objects to be violated are known as memory-safety bugs. Memory-safety bugs can be related to spatial safety, temporal safety, or type safety. For example, if a program allocates a buffer and allows for writing past the end of it, then the program contains a spatial-safety bug. Similarly, if a program allows for a heap memory object to be accessed after it has been freed, then it contains a temporal-safety bug.

The C standard does specify the representations (Section 6.2.6), lifetimes (Section 6.2.4), and compatible types (Section 6.2.7) of memory objects [95]. However, corresponding violations of memory object bounds, lifetimes, and types are left as undefined behavior. This means that a C program is allowed to take any action in the presence of a memory-safety bug. Furthermore, recent work on C semantics by Memarian *et al.* identified areas related to memory-safety bugs in which the standard's current specification is unclear or inadequate [81].

In practice, mainstream compilers handle memory-safety bugs in ways that can make C/C++ programs susceptible to attack. When memory-safety bugs make a program susceptible to attack, they can also be called memory-safety vulnerabilities. For example, the infamous 1988 Morris worm leveraged a buffer overflow spatial-safety vulnerability in the **fingerd** program to increase its privilege on targeted hosts [107]. The behavior of mainstream compilers constitutes a murky, unpublished *de facto* standard that developers have grown to depend on for program functionality [82].

It is theoretically possible to write C/C++ programs that are memory-safe when built by any compiler that conforms to the published standards [95, 126]. Specifically, C/C++ programs that do not contain any kind of memory-safety bug or other undefined behavior are memory safe by definition. Unfortunately, however, the continued prevalence of security incidents caused by memory-unsafe C/C++ programs [22, 23] suggests that producing memory-safe C/C++ programs is exceedingly difficult.

In the early 2000s, Morrisett *et al.* created a research memory-safe dialect of C called Cyclone [83]. It modifies the C-language syntax and semantics in order to make some kinds of memory-safety bugs impossible to express. Other kinds are prevented by dynamic checks. This means that they are not exploitable, i.e. they are not memory-safety vulnerabilities.

It is also possible to specify a syntactically and semantically compatible memory-safe version of C/C++ that refines aspects of the current standards' undefined behavior such that all memory-safety bugs must not be exploitable. The recently developed CHERI C [81], which specifies that a program should trap when certain aspects of memory-safety are violated at runtime, makes significant progress in this direction. Such a language could be implemented on current mainstream hardware by augmenting a C/C++ compiler to emit instrumentation and dynamic checks. To date, however, no mainstream implementation of C/C++ has been made memory-safe, likely because the performance cost of enforcing memory safety with existing hardware is prohibitive [106]. Capability hardware like CHERI is a promising potential solution to this problem, but, until it is suitable for widespread

deployment, a huge quantity of C/C++ programs will remain susceptible to memory-safety attacks.

#### 2.1.1 Attacks and limited mitigations

In a memory-safety attack, also known as a memory-safety exploit, an attacker leverages a memory-safety vulnerability in some program to gain privilege that they were not intended to have. The usual goal of this privilege escalation is to execute arbitrary code in the target process, but other goals, such as the exfiltration of sensitive data, are also common. Memory-safety attacks have been prevalent, and extremely costly, throughout the history of computing, and a large number of mitigations has been developed in an attempt to stop them. A memory-safety mitigation alters the execution environment of a program to make one or more memory-safety attacks unsuccessful. Mitigations can aim to prevent specific kinds of attacks from succeeding, or, more powerfully, to render entire classes of memory-safety vulnerability unexploitable.

Here I present a brief history of widely deployed memory-safety attacks and mitigations. It highlights the whack-a-mole nature of mitigations in the real world to date. When a new attack becomes popular, a mitigation for the attack is developed and deployed. However, the mitigation fails to address the attack's underlying vulnerability, so a variant of the attack that bypasses the mitigation pops up, and the process repeats.

Strictly speaking, a memory-safety attack or exploit is a particular sequence of actions carried out by an attacker to take advantage of a memory-safety vulnerability in a particular program. However, in the following discussion, I refer abstractly to groups of similar memory-safety attacks.

Attack: code injection Perhaps one of the earliest known memory-safety attack techniques involves exploiting buffer overflows on the stack to inject and execute attacker-supplied code [90]. A programmer might, for example, allocate a buffer on the stack to hold some string argument provided by the user of a program. If the user-provided string argument is larger than the allocated buffer, and if the programmer uses a function like strcpy(), which copies the argument until it reaches a null terminator, then the argument will be copied past the bounds of the buffer. A malicious user could exploit such a program with a code-injection attack by supplying a specially formatted string. The string might contain a block of arbitrary code and a carefully positioned pointer, which overwrites the current function's return address on the stack with the address of the code block. Then when the function returns, the arbitrary attacker-supplied code is run.

Mitigation: write xor execute A widely employed mitigation that prevents the above type of stack-smashing attack is write xor execute  $(W \oplus X)$  protection, also known as data execution prevention (DEP) [96]. This mitigation enforces the invariant that pages of a process' memory can be mapped with either write permission or execute permission, but not both, except in special circumstances. The effect of  $W \oplus X$  protection is that, in general, an attacker cannot inject arbitrary code and then induce the process to run it. Some exceptions exist for programs like just-in-time (JIT) compilers, which write code that later becomes executable as part of their normal operation.

Attack: code reuse Not easily deterred, attackers developed new techniques to bypass  $W \oplus X$  protection: code-reuse attacks. The idea behind these attacks is to chain together snippets of existing library code, called gadgets, in a way that ultimately grants the attacker arbitrary code execution. The most widely known code reuse technique is return-oriented programming (ROP) [100], in which gadgets typically end with a return instruction, but other variants are possible [12, 20]. In the example above, a ROP attacker would use the buffer overflow to carefully place data and ROP gadget addresses on the stack, so that they appear to be function arguments and return addresses. The current function's return address would be overwritten with the known address of the initial ROP gadget. Then, when the function returns, the ROP gadget chain created on the stack is executed, which allows the attacker to execute arbitrary code.

Mitigations: stack canaries and shadow stacks Stack canaries and shadow stacks were developed to make it more difficult to overwrite a return address stored on the stack [31]. In a stack canary scheme, a value known as the canary is stored as part of stack frames, between local storage and the function's return address. All function epilogues check that the canary's value matches what was initially stored there before returning. Assuming the canary's value is unknown to the attacker, this mitigation prevents contiguous stack buffer overflows with high probability. However, stack canaries fail to mitigate bugs that allow targeted memory writes on the stack; these targeted writes could overwrite a return address without touching the canary.

Shadow stack schemes involve maintaining a second stack onto which function prologues store return addresses. Function epilogues then compare the shadow stack return address with that of the main stack, detecting an attack if the two do not match. These schemes protect against all attacks that overwrite stack-based return addresses. However, they do not mitigate bugs that allow for the corruption of other code pointers, such as virtual function table pointers in C++ objects.

Attack: beyond the stack With a number of mitigations deployed to make stack exploitation more difficult, attackers found other sources of vulnerabilities. In particular, memory objects on the heap often contain code pointers, which can be overwritten to carry out code-reuse attacks using special gadgets that pivot the stack to memory that the attacker controls. A spatial vulnerability related to the field of some heap memory object can allow attackers to overwrite code pointers in other objects on the heap, or even within another field of the same object. Similarly, temporal safety vulnerabilities related to a heap memory object can allow attackers to overwrite code pointers in another aliased memory object.

Mitigation: Address space layout randomization Address space layout randomization (ASLR) is a widely deployed mitigation against code-reuse attacks. It involves randomizing process memory layouts so that attackers overwriting a code pointer cannot reliably target specific gadgets. However, the probabilistic protection provided by ASLR can be bypassed in a number of ways, including via leaks that reveal the process' memory layout and via system side-channels [46, 60].

Mitigation: Control-flow integrity Some mitigation techniques are designed to prevent code-reuse attacks by protecting a program's control-flow integrity (CFI) [1, 24].

They aim to ensure that branches taken at runtime match a predetermined control-flow graph for the program, or do not violate static type information, usually by performing software instrumentation. However, these kinds of mitigation often provide provide coarse-grained or incomplete protection that can be bypassed easily.

Attack: Data-oriented programming Attention has also turned to data-oriented programming (DOP) attacks, which involve exploiting memory safety bugs without overwriting any pointers. Hu *et al.* demonstrated that, corrupting only data fields, it is theoretically possible to construct expressive, even Turing-complete, exploits against a wide variety of programs [51]. Proposed mitigations for these attacks include enforcing data-flow integrity [19], which is analogous to CFI for data, and detecting the effects of DOP on control-flow tracing [21].

#### 2.1.2 More robust mitigations

Here I describe past research efforts to add more robust memory-safety mitigations to C/C++ implementations. The limited mitigations described above, which generally aim to prevent a single type of exploit, have been sidestepped by attackers relatively easily. These mitigations, on the other hand, attempt to eliminate entire classes of vulnerability, i.e. spatial-safety, temporal-safety, or type-safety vulnerabilities, that facilitate memory safety attacks. For the most part, they have failed to achieve widespread deployment because of performance and compatibility overheads, or because they fail to provide complete protection in practice.

#### 2.1.2.1 Spatial safety

Some past projects have focused on providing spatial safety for C/C++:

- **Bounded-object approaches** Some approaches for spatially safe C have involved software instrumentation that tracks bounds information for each memory object [35, 58, 101]. However, these approaches require that all pointers to a particular object share the same bounds, and they have difficulty enforcing sub-object bounds completely [84].

- Fat-pointer approaches A more effective approach is to track bounds information for each pointer rather than each memory object. Pointers with associated bounds information are known as fat pointers. SoftBound [84] is a source-code compatible and effective fat-pointer mitigation based on software instrumentation. It stores bounds information for pointers disjointly in tables that are checked before each pointer dereference. However, SoftBound's spatial safety comes with a prohibitive average runtime overhead of 67%. Other similar software techniques have attempted to trade off mitigation effectiveness for improved performance [50].

Some past work has also proposed hardware support for bounding pointers to provide spatial safety. The M-Machine [18], SAFE low-fat pointers [62], and HardBound [34] feature pointers whose bounds are maintained and tagged by hardware. Hardware support facilitates a reduced performance overhead, but novel hardware comes with significant production and adoption costs.

#### 2.1.2.2 Heap temporal safety

Various past projects provide temporal safety for the C/C++ heap:

- Lock-and-key instrumentation One approach for providing heap temporal safety is to maintain a unique identifier for each heap memory object. When a heap pointer is created, it is associated with the identifier of its corresponding heap object. Then, when it is dereferenced, the system checks whether the pointer's identifier still matches that of the referenced memory. This technique is known as lock-andkey mitigation. CETS [85] is a mitigation that uses compiler instrumentation to implement lock-and-key checking. It comes with a runtime overhead of 48% on average. When combined with a spatial safety mitigation, which is a prerequisite for temporal safety with CETS, this overhead jumps to 116%.

- Garbage collectors Another approach for heap temporal safety is to use a garbagecollected heap rather than relying on manual calls to free(). The Boehm-Demers-Weiser garbage collector [14] is a conservative mark-and-sweep garbage collector for C and C++. MarkUs [2] offers improved security properties by only collecting garbage that has been explicitly freed by the programmer. CRCount [105] is a reference-counting garbage collector that uses static analysis and instrumentation of pointer-related operations to identify pointers to objects in the heap; it associates a reference count with each heap object that gets modified as pointers are created and destroyed. I discuss garbage collectors in more detail in Section 2.8.

- **Pointer nullification** It is also possible to provide heap temporal safety by rendering pointers to freed heap memory unusable. This is known as pointer nullification or invalidation. DANGNULL [64] is a pointer nullification system that uses software instrumentation and runtime data structures to track the pointers that reference heap memory objects. When a heap memory object is freed, pointers referencing it are set to null. DangSan [61] and pSweeper [76] are higher-performance invalidation systems that support concurrency.

- Virtual memory protection Electric Fence [41], Dhurjati and Adve [36], and more recently the Oscar system [30], use virtual memory to provide heap temporal safety in a way that does not require software instrumentation to identify pointers: each allocated memory object is placed in a separate virtual page that is rendered inaccessible by MMU hardware once the object is freed. However, this kind of technique can result in memory fragmentation and TLB pressure. I discuss virtual memory further in Section 2.7.

There are also some software-based techniques that reduce the possibility of exploiting a heap temporal-safety vulnerability but do not eliminate it. DieHard [11] provides probabilistic protection by randomizing the location of objects on the heap. Cling [3] is a memory allocator that restricts memory reuse to objects of a similar layout, which makes attacks that exploit heap temporal safety vulnerabilities harder to carry out but not impossible.

#### 2.1.2.3 Complete memory safety

Other projects aim to provide spatial, temporal, and type safety for C/C++:

- C dialects Some approaches have attempted to offer complete memory safety without hardware support by making changes to the C language. Cyclone [83] is a dialect of C that supports fat-pointer spatial safety and heap temporal safety. CCured [86, 87] is a software transformation system for C programs that similarly supports spatial and temporal safety. It also employs static analysis to identify pointer use that does not require runtime validation. However, these kinds of systems require significant changes to existing C source code, which limits their potential for adoption.

- Sanitizers A sanitizer is another kind of system that can offer complete memory safety. Sanitizers maintain metadata and perform expensive instrumentation to detect and report a number of undesirable program behaviors at runtime. They are usually implemented in software but can benefit from hardware acceleration. The downside of these systems is their significant performance overhead; for this reason, they are often used as offline debugging tools rather than mitigations that can be enabled in production [106]. Address Sanitizer [104] and Valgrind [116] are perhaps the most widely known sanitizers.

#### 2.1.3 Commodity hardware support

Relatively recently, various commodity architectures have added extensions that can be used to support memory safety mitigations. This trend indicates a willingness among commercial hardware designers and vendors to adopt changes that support improved security. To date, these extensions have not been successful in facilitating robust memory safety at a low performance cost; however, their adoption is encouraging for technologies like CHERI.

Intel's Memory Protection Extensions (MPX) [17] were developed to accelerate softwarebased bounds checking for spatial safety. A detailed analysis of MPX found that, while the technology is promising, it currently does not deliver the desired performance improvements and suffers from a number of issues related to its immaturity [89].

Arm has developed a number of extensions to facilitate security. One of these is Pointer Authentication Codes (PAC) [67, 103], which adds support for cryptographically signing pointers and validating that pointers have been signed before they are dereferenced. Using PAC to prevent pointer injection in this way is technically a probabilistic mitigation. Apple has adopted PAC on some of its platforms, but it has been successfully bypassed [10, 49, 97].

Another Arm security extension is Branch Target Identification (BTI) [74]. It adds a special no-operation instruction that is used to indicate valid indirect branch targets, and indirect branches to all other instructions result in a trap. BTI facilitates mitigating certain types of pointer injection rather than a class of memory safety vulnerability.

Extensions for tagging memory, such as Arm's Memory Tagging Extension (MTE) [47] and SPARC M7's Application Data Integrity (ADI) [91], have also been developed. These extensions provide hardware support for schemes similar to software lock-and-key instrumentation. They assign a tag, a few bits in length, to every pointer and every memory region of a particular size. Pointer tags are stored in unused upper address bits, and memory tags are stored in an auxiliary tag memory. When a pointer is dereferenced, its tag must match that of the referenced memory region, or the access will result in a trap. Because of the small number of possible tags, and the fact that pointer and memory tags can be modified by unprivileged code, these memory tagging extensions facilitate

| 63 0                 |  |                      |                            |  |  |  |  |  |  |

|----------------------|--|----------------------|----------------------------|--|--|--|--|--|--|

| permissions: 16 bits |  | object type: 18 bits | compressed bounds: 27 bits |  |  |  |  |  |  |

| address: 64 bits     |  |                      |                            |  |  |  |  |  |  |

Figure 2.1: 128-bit CHERI capability format, adapted from CHERI ISAv8 [118]

only weak probabilistic protection. Considered alone, they are more useful for sanitizers or debugging aids rather than security mitigations.

## 2.2 The CHERI architecture

CHERI (Capability Hardware Enhanced RISC Instructions) [118, 120, 125] is an architectural extension for RISC ISAs that composes the capability-system model with current hardware and software stacks. In a capability system, resources are only accessed via capabilities, which are unforgeable tokens of authority that can be transferred between system components. Such a model makes it natural and efficient to implement two important security design principles: the principle of least privilege, which dictates that software should run with the minimum privilege necessary to perform its function; and the principle of intentional use, which dictates that software must explicitly select which privileges to exercise for each action it takes. These principles limit the scope and spread of damage caused by software flaws.

CHERI's security model hybridizes cleanly with contemporary RISC ISAs, CPU designs, MMU-based operating systems, and existing C/C++ software. It de-conflates memory virtualization and protection, allowing the MMU to handle virtualization while CHERI features provide protection. CHERI's security features can be adopted incrementally by software, and existing binaries can run unmodified on CHERI processors. CHERI also aims to have a low compatibility overhead: codebases that use C-style pointers in a standards-conforming way require minimal to no changes to re-compile with support for CHERI features.

CHERI introduces the architectural capability, a form of hardware-checked fat pointer that is used instead of an integer pointer to access memory. On 64-bit processors, architectural capabilities are 128-bit values that encode a virtual address, compressed bounds [124], permissions, and an object type. They are associated with an out-ofband one-bit tag that distinguishes valid from invalid capabilities. Figure 2.1 illustrates the 128-bit CHERI capability format. Architectural capabilities are implemented via microarchitectural additions to the CPU and SoC that support new capability instructions and registers as well as tagged memory for hardware-enforced capability integrity.

An important aspect of CHERI is that capabilities themselves represent the authority to access memory and can propagate freely throughout the system. No additional indirection or synchronous table lookups are required to authorize memory access. This design avoids adding significant microarchitectural performance overheads.

CHERI capabilities can be used to implement a number of powerful security primitives, including compartmentalization [120], but this dissertation is primarily focused on memory safety. The main properties of CHERI capabilities that software can use to facilitate robust memory safety are as follows:

Tags On a CHERI-enabled system, each 128-bit region of memory is tagged to indicate

whether it contains a valid capability or not. Attempting to access memory via an untagged capability results in an exception. Capability transformations by legitimate capability instructions preserve tags, but other modifications, such as corrupting capability bounds via a raw memory write, automatically clear the capability's tag, rendering it unusable. These properties guarantee architecturally that capabilities are unforgeable, and in particular valid pointers cannot be derived from ordinary data.

- **Bounds and permissions** CHERI capabilities contain fine-grained bounds and permissions, which provide architectural guarantees that a capability cannot be used to access memory regions outside of its bounds or, for example, to write memory when it has only read permissions. Informally, the bounds of a CHERI capability can be described in terms of the capability's base, or inclusive lower bound, and its length, or number of bytes between the lower bound and exclusive upper bound.

- **Monotonicity** All valid capability instructions monotonically decrease capability rights. In other words, bounds and permissions can never be expanded once they have been narrowed.

- Sentry capabilities Sentry capabilities are immutable code capabilities that only allow control flow transfer [99]. Their target addresses cannot be modified, and they cannot be used to derive other capabilities. They are useful for implementing code pointers that should not be changed after they are initialized, such as global offset table entries and function return addresses. Sentry capabilities are identified by a specific value in their object type field. Software can *seal* a valid code capability to create a sentry, and the architecture can be configured so that function call and return instructions generate sentry capabilities for return addresses automatically [118].

#### 2.3 Software use of CHERI

For CHERI to provide security benefits to application programs, software must take advantage of its architectural features, which support a wide range of potential uses. CHERI capabilities can represent abstract capabilities, i.e. non-forgeable tokens of authority, and be used as pointers to regions of virtual memory. They can facilitate fine-grained compartmentalization [120] as well as memory safety.

#### 2.3.1 Spatial safety with CheriABI

Currently, the most sophisticated scheme for CHERI-supported memory safety is CheriABI. CheriABI is an execution environment for C/C++ applications that guarantees spatial safety [32, 99]. It is a feature of the CheriBSD operating system, which is a fork of FreeBSD that has been adapted to support CHERI features [25]. Its spatial safety guarantee stems from the facts that all memory accesses are made via valid capabilities and that capability bounds are shrunk to match the bounds of memory objects. These properties are enforced by the CHERI-LLVM compiler, which emits pure-capability code that only uses capability instructions to access memory, and other system components such as the kernel, the runtime linker, and C standard library, which work together to ensure that capability bounds are refined to match those of abstract memory objects. CheriABI also offers

attractive compatibility and performance overheads relative to similar past mitigations [32]. I further describe and analyze CheriABI in Section 3.3.

#### 2.3.2 Pure-capability linkage

The loading and linking of pure-capability code is broadly similar to conventional linkage, with some important differences. Pure-capability code means that all pointers are implemented as CHERI capabilities: both those visible at the C and C++ language level, such as a pointer to some region of heap memory, and *sub-language-level pointers*, such as pointers in the global offset table (GOT) or return addresses saved on the stack. Sub-language-level pointers play a large role in linkage, and using capabilities to implement them means that some techniques from conventional linkage no longer work. However, pure-capability linkage also allows for improved security through greater application of the principle of least privilege.

**Process initialization** One immediate consequence of having a GOT full of capabilities, otherwise known as a captable, is that those capabilities must be initialized. Valid capabilities cannot be initialized statically; they must be derived via legitimate transformations from other valid capabilities. In other words, a binary file cannot contain capabilities that will automatically have valid tags when the binary is loaded. In pure-capability linkage, the system's runtime linker performs the required initialization of the captable.

Each entry in the application binary's captable initially holds a capability relocation, which tells the runtime linker the location and size of the global that the capability in that entry is supposed to reference. The runtime linker runs immediately after a process is created, before the application program. It has access to privileged capabilities that are present in a process' register file when it is created, and the runtime linker uses them to derive valid capabilities that correspond to the application binary's capability relocations. It overwrites the capability relocations with the valid capabilities. Before transferring control to the application, it also refines the bounds and permissions of the privileged capabilities that were initially present in the process' register file, such as the stack pointer capability and the program counter capability (PCC), to limit the privilege of the running application.

This capability refinement and captable initialization process is a is a crucial part of enforcing spatial safety in CheriABI. Note that it is not an automatic effect of running code on a CHERI-capable processor. It requires adaptation of both the compiler and the runtime linker, which work together to implement it. This process must take place for all pure-capability applications, even when they are position-dependent binaries and do not reference any external dynamic shared objects (DSOs).

Linkage ABI Pure-capability code also facilitates the principle of least privilege in the linkage ABI for accessing global values and functions. Here I describe the PCC-relative ABI, which is used by default in the CHERI-LLVM compiler, but other designs are possible [99]. In this ABI, the PCC has only read and execute permissions. Its bounds span the current DSO's text segment and captable. The captable is located at a statically known offset relative to the text segment, and the runtime linker populates it when it loads the DSO.

In the PCC-relative ABI, global variables are accessed by indexing into the current DSO's captable. Note that even globals within the same DSO must be accessed via the captable. In conventional linkage, such globals might be accessed directly via a known offset from the program counter. However, in pure-capability code, an analogous type of access would violate the principle of least privilege. It would require the PCC to have write permission and access to the DSO's data segment.

With the PCC-relative ABI, functions in the same DSO can be accessed via a jump instruction, and functions in a different DSO are called via the procedure linkage table (PLT). The captable entries for global function pointers, which are used by the PLT, contain sentry capabilities whose addresses reference the target function and whose bounds correspond to the target function's DSO.

The PCC-relative ABI enforces bounds for globals, which is important for spatial safety. It also limits the bounds of PCC to the current DSO, and restricts access to globals on a DSO level. This design results in a form of inter-DSO compartmentalization that protects the internal components of one DSO from being accessed by other DSOs. Even if an attacker managed to gain arbitrary code execution within some DSO, they would be able to access only code and data within the DSO and globals from outside of the DSO that have been exposed to it specifically. The attacker would be able to call functions outside of the DSO that have been linked. However, because the capabilities granting access to those functions are sentries, their entry points cannot be changed; the attacker could control only the arguments that the functions receive. Note that this form of compartmentalization also relies on the kernel to configure the architecture to implement return addresses as sentry capabilities. Otherwise, return address capabilities could be used to access private data in the DSO being returned to.

The isolation provided by the PCC-relative ABI means that control over machine state, including memory and code execution, in one DSO is not sufficient to compromise private information in another. This property is particularly appealing in the context of security-critical libraries used by potentially buggy application code. A memory safety bug in an application, for example, would not be sufficient to expose a key in some cryptography library or a memory allocator's privileged capability to the heap. However, the PCC-relative ABI does not fully enforce the principle of least privilege, because it uses a single captable for all functions in a DSO, and so each function has access to all globals in the DSO. The PLT ABI [99] restricts captables to the function level, facilitating greater isolation at the cost of complexity and performance.

#### 2.4 Morello

CHERI initially extended the MIPS architecture, and later added support for RISC-V [118]. More recently, an extension to the ARMv8-A architecture known as Morello was developed in collaboration with Arm [69, 70]. It is a superset of ARMv8.2-A and implements the complete set of CHERI features with minor platform-specific adaptations.

Morello is the subject of the £187M UKRI Digital Security by Design program [113]. As part of this program, Arm produced an industrial-quality Morello demonstrator board, which was released in early 2022. The board, fabricated in a 7nm process, is based on the Arm Neoverse N1 System Development Platform [72]. It includes two CPU clusters, each with two superscalar out-of-order cores clocked at 2.5 GHz. Each core has a 64 KiB private L1 data cache, a 64 KiB private L1 instruction cache, and a 1 MiB private L2

unified cache. Each cluster has a 1 MiB shared L3 unified cache. The SoC's interconnect is clocked between 1.6 and 1.8 GHz. It has two DDR4 controllers, each of which supports an RDIMM up to DDR4-2667 speed (2667 MHz). The board can be configured to store capability tag bits in a carved-out memory region [56] or in RAM error-correcting-code bits.

Morello supports two instruction sets: A64 is the standard Armv8.2-A instruction set extended with instructions to interact with capabilities in a limited way, and C64 is a variant that supports a richer set of instructions for interacting with capabilities at the expense of instructions that use 64-bit integers to access memory [69]. Specifically, instructions are encoded in the same way across the two instruction sets, but instructions that use 64-bit operands in A64 use capability operands in C64, and vice versa. The active instruction set is determined by a bit in the processor state register (PSR). On a capability branch, this PSR bit is automatically saved into the least significant bit of the capability link register; its value is then updated to the least significant bit of the branch target's address. The PSR bit can also be toggled using the special **bx #4** instruction. This technique of using a branch target's least significant bit to switch between instruction sets has previously been used to support Arm's Thumb compressed instruction set [73].

#### 2.4.1 Platform limitations

A preliminary but fully featured Morello adaptation of the complete CHERI software stack, including the CHERI-LLVM compiler and CheriBSD operating system, has been completed. However, Morello is the first high-fidelity superscalar capability machine ever to be built. Because of its novelty and limited project timeline, it currently has a number of known platform limitations. They include the following:

- There are some features of the Morello SoC microarchitecture that result in nonessential penalties for pure-capability code. These penalties affect capability jumps, loads, and stores, and they inflate the overhead of pure-capability compilation. Attempts to fully diagnose and work around the penalties, including a benchmarking ABI that sacrifices some of CheriABI's security properties to simulate more realistic performance, are in progress. These non-essential penalties are expected to be eliminated in future microarchitectures as techniques for building high-performance CHERI-enabled processors are better understood. They will be documented in a future technical report, which has not yet been made public at the time of writing.

- Capability-related optimizations present for other CHERI architectures have not been added to the Morello backend of the CHERI-LLVM compiler.

- Specialized Arm assembly routines for byte-string operations like memcpy() and memset() in the CheriBSD standard library have not been ported to work with capabilities, so pure-capability binaries on Morello use slower C routines.

- The thread-local storage specification for Morello is still undergoing changes, so pure-capability binaries use emulated thread-local storage.

Additionally, current understanding of the general performance effects of capability use in superscalar capability machines is relatively limited.

These limitations mean that it is currently challenging to measure performance differences between normal 64-bit Arm code and pure-capability code. Similar challenges exist for measuring the performance effects of adding new pure-capability code paths, because the added code may be affected differently by current microarchitectural penalties than the existing body of code.

Despite these challenges, the work in this dissertation targets Morello because it will ultimately determine the feasibility of widespread CHERI adoption. I designed my experiments and hypotheses to be robust in the face of microarchitectural and toolchain-related changes that will take place as general understanding improves and the above limitations are addressed. Chapter 5 contains the first performance measurements from the Morello board to be reported.

#### 2.5 Virtual-machine language interpreters

Higher-level languages like JavaScript, Java, and C# play a large role in modern computing infrastructure. They power mobile applications, cross-platform client and server programs, and the user-facing dynamic components of websites. Unlike lower-level languages, which are typically compiled directly to machine code for a target architecture, higher-level languages are often executed by a program known as an interpreter.

Interpreters themselves are generally written in lower-level languages and compiled for a specific architecture. They must meet a significant challenge: to facilitate safe and highperformance execution of the interpreted language. In other words, an interpreter must efficiently implement the interpreted language's high-level features while also protecting its own code and data structures from interference by arbitrary interpreted code.

While an interpreter might implement spatial safety and a temporally-safe garbagecollected heap for the language being interpreted, the lower-level language that implements the interpreter, e.g. C or C++, likely lacks such security properties. In this case, the interpreter's implementation can contain memory-safety vulnerabilities that allow interpreted code to interfere with the interpreter's internal data structures. These bugs can be difficult to detect by inspecting the source. Features such as just-in-time compilation, discussed further below, which improve the performance of interpreters but greatly increase their implementation complexity, make it easy to introduce subtle bugs.

In the presence of such memory-safety vulnerabilities, a carefully crafted input program can leverage them to turn arbitrary *constrained* execution in the high-level interpreted language into arbitrary *unconstrained* code execution in the interpreter's process. This scenario is particularly dangerous in the context of web browsers, which we use regularly to download and interpret JavaScript code from untrusted, potentially malicious sources. Mitigating memory-safety vulnerabilities in language interpreters is thus crucially important for security.

A common design pattern for modern interpreters is to make use of a virtual machine [75]. A virtual-machine language interpreter implements the interface of an abstract computer, typically one that is stack-based or register-based. It operates on a set of values that occupy its virtual register file and memory regions. To interpret an input program, it first compiles the program into bytecode that specifies virtual machine operations. Each bytecode instruction in program order is then dispatched to a function in the interpreter's implementation that performs the operation and modifies the virtual machine's state accordingly.

#### 2.5.1 Just-in-time compilation