Number 96

# Models and logic of MOS circuits Lectures for the Marktoberdorf Summerschool, August 1986

Glynn Winskel

October 1986

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

# © 1986 Glynn Winskel

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Models and logic of MOS circuits Lectures for the Marktoberdorf Summerschool, August 1986

by

Glynn Winskel

University of Cambridge,

Computer Laboratory,

Corn Exchange Street,

Cambridge CB2 3QG.

#### Abstract

Various models of hardware have been proposed though virtually all of them do not model circuits adequately enough to support and provide a formal basis for many of the informal arguments used by designers of MOS circuits. Such arguments use rather crude discrete notions of strength—designers cannot be too finicky about precise resistances and capacitances when building a chip—as well as subtle derived notions of information flow between points in the circuit. One model, that of R.E.Bryant, tackles such issues in reasonable generality and has been used as the basis of several hardware simulators. However Bryant's model is not compositional. These lectures introduce Bryant's ideas and present a compositional model for the behaviour of MOS circuits when the input is steady, show how this leads to a logic, and indicate the difficulties in providing a full and accurate treatment for circuits with changing inputs.

# Models and logic of MOS circuits

by

Glynn Winskel

University of Cambridge,

Computer Laboratory,

Corn Exchange Street,

Cambridge CB2 3QG.

#### Abstract

Various models of hardware have been proposed though virtually all of them do not model circuits adequately enough to support and provide a formal basis for many of the informal arguments used by designers of MOS circuits. Such arguments use rather crude discrete notions of strength—designers cannot be too finicky about precise resistances and capacitances when building a chip—as well as subtle derived notions of information flow between points in the circuit. One model, that of R.E.Bryant, tackles such issues in reasonable generality and has been used as the basis of several hardware simulators. However Bryant's model is not compositional. These lectures introduce Bryant's ideas and present a compositional model for the behaviour of MOS circuits when the input is steady, show how this leads to a logic, and indicate the difficulties in providing a full and accurate treatment for circuits with changing inputs.

#### 0. Introduction.

There are some tricky issues in the verification of hardware. We all know that verification of any device can only be done in terms of a model for its behaviour. However it is very easy to forget that verification depends crucially on the accuracy of the model. The verification of hardware has been very successful when the model assumes there are basic trusted functional devices out of which all other devices are built (see e.g. [Gorl. She, Mos] and the classical work on implementing Boolean functions). mathematics of functions and functional programs is well-understood so it makes good sense to translate hardware into functions; they can be reasoned about or even run as functional programs to simulate the behaviour of the hardware. Fortunately this kind of model is often appropriate and proofs of properties of hardware amount to large but essentially trivial manipulations of expressions for functions or relations. Sometimes, however, the physical nature of the device intrudes. Designers, generally indifferent to slick proofs of correctness, use their knowledge of the physics of devices to improve performance or layout. Designers in metal oxide semiconductor (MOS) technology can use a variety of techniques. They exploit bidirectionality and the fact that signals do not have uniform strengths to improve their designs. Most approaches model such designs in an ad hoc way; directionality is often imposed, rather than derived, and effects due to signal strength are fudged. In what sense can a verification, based on such a model be trusted? After all directions can only be assigned correctly when the circuit behaviour is understood thoroughly and an incorrect assignment can easily lead to an incorrect prediction about the circuit's behaviour. As a last resort there are the precise models of physics but, even aside from whether these are tractable or not, they are often far too detailed. A designer cannot be finicky about the precise resistance or capacitance to be realised in a VLSI chip; designs should be fairly robust in order to tolerate variations in manufacture. There is a need for a model and proof system for circuits which while close to the logical behaviour of hardware devices also captures the effects used by designers.

In these lectures we shall look at the most striking problems with many of the models in use and attempt to remedy their faults. In addressing these problems we shall make use of the ideas in R.E.Bryant's model of MOS circuits. Bryant's ideas have been developed chiefly with the aim of accurate simulation in mind and they are not directly suitable as a basis for a proof system for circuits. We shall work towards achieving this. Firstly, we illustrate some of the problems that arise in other approaches to modelling circuits.

# 1. Relational models and their problems.

Modelling circuits as functions can often impose an unnatural directionality and lead to inaccurate models which predict the wrong behaviour. Instead we might try to model circuits as some form of relation. This is the course followed in [Gor] and less explicitly in [Mos]. It should be mentioned that although we base our criticism on the work [Gor] this is largely because it is there the problems are shown-up clearly, in their basic form. Essentially the same difficulties arise in the treatments [Mos, Mij. Incidentally, all the approaches [Gor, Mi, Mos, Sh] seem to cope well at higher levels of abstraction.

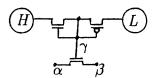

Consider a CMOS inverter:

H Power

The effect of the inverter is to output at  $\beta$  the inverse of the value input at  $\gamma$ . We illustrate for this simple example how one expresses and argues in the framework of [Gor 2,3] that the circuit drawn meets this specification.

The circuit is built out of two kinds of transistors. A p-type transistor  $ptran(\alpha, \beta, \gamma)$ , generally drawn as

is a device which, when the voltage value at the gate is low, i.e.  $V\gamma = L$ , connects  $\alpha$  and  $\beta$ , so  $V\alpha = V\beta$ . When the value at  $\gamma$  is high,  $V\gamma = H$ , the points  $\alpha$  and  $\beta$  are disconnected so we cannot say what the relation is between  $\alpha$  and  $\beta$ —it all depends

on what they are connected to. The other kind of transistor, an n-type transistor  $ntran(\beta, \delta, \gamma)$ , drawn

behaves in a converse fashion; when  $V\gamma = H$ ,  $\beta$  and  $\delta$  are connected and  $V\beta = V\delta$ , and when  $V\gamma = L$  they are disconnected. In approaches like [Gor2,3, Mos] a circuit (and hardware in general) is modelled by a relation between values at the significant points of the circuit. This is expressed as an assertion. So in the work [Gor2,3] the assertions associated with the two transistors are

$$ptran(\alpha, \beta, \gamma) \equiv (V\gamma = L \rightarrow V\alpha = V\beta),$$

$$ntran(\beta, \delta, \gamma) \equiv (V\gamma = H \rightarrow V\beta = V\delta).$$

(We use  $\equiv$  to mean definitional equality; the left-hand side stands for the right-hand side.)

Two kinds of sources are used in the CMOS inverter. Power connected at  $\alpha$  is regarded as maintaining the voltage value as high at  $\alpha$  and ground (or earth) at  $\delta$  maintains the value at low. The corresponding assertions are:

Pow

$$\alpha \equiv (V \alpha = H)$$

,

Gnd  $\delta \equiv (V \delta = L)$ .

So each component is described by an assertion about values at the points with which it is associated. Their composition, got by joining points in common, meets all the relations of the components, and so satisfies the conjunction:

$$ptran(\alpha, \beta, \gamma) \wedge ntran(\beta, \delta, \gamma) \wedge Pow \alpha \wedge Gnd \delta$$

For the inverter we wish to hide the points  $\alpha$  and  $\delta$  from the environment. This is achieved by existential quantification to give the following assertion for the CMOS inverter:

$$\operatorname{Inv}(\gamma,\beta) \equiv \exists V \alpha \exists V \delta. \ \operatorname{ptran}(\alpha,\beta,\gamma) \wedge \operatorname{ntran}(\beta,\delta,\gamma) \wedge \operatorname{Pow} \alpha \wedge \operatorname{Gnd} \delta$$

The CMOS inverter is intended to implement the specification:

$$\operatorname{Spec}(\gamma,\beta) \equiv (V\gamma = H - V\beta = L) \wedge (V\gamma = L - V\beta = H)$$

A simple proof using well-known rules of logic shows

$$\operatorname{Inv}(\gamma,\beta) \to \operatorname{Spec}(\gamma,\beta).$$

We can prove the assertion  $\operatorname{Inv}(\gamma,\beta)$  implies  $\operatorname{Spec}(\gamma,\beta)$ . In this sense we can prove  $\operatorname{Inv}(\gamma,\beta)$  implements  $\operatorname{Spec}(\gamma,\beta)$ . To recap: We have described the behaviour of circuits by assertions, their composition by conjunction, hiding of points by existential quantification and taken implementation as implication between the assertions for the circuit and its specification.

This general scheme can be followed equally well for dynamically changing circuits subject to voltages which change over time [Gor2, 3]. The only change is to model a

circuit as a relation between histories of voltage values at the points of interest (histories are functions from time  $0, 1, \dots, t, \dots$  to  $\{H, L\}$ ) taking e.g. the assertion for a p-type transistor to be

$$ptran(\alpha, \beta, \gamma) \equiv \forall t. \ V(\gamma, t) = L \rightarrow V(\alpha, t) = V(\beta, t).$$

The approach is noteworthy because it does not impose an unrealistic directionality on devices as would for example be forced in the approach [Sh] were it to tackle such low-level circuits. The model and logic are also compositional; one can reason about the behaviour of circuits in terms of the behaviour of their components. A similar scheme is followed in [Mosi, but there assertions in a temporal logic are used instead.

Unfortunately, there is a major deficiency in this approach—natural and useful as it is in many examples. According to this scheme a "short circuit" implements any specification! A short circuit, achieved most simply, by joining power and ground together at a point  $\alpha$  is described by the assertion

Pow

$$\alpha \wedge Gnd \alpha$$

But  $Pow \ \alpha \land Gnd \ \alpha$  is equivalent to  $V\alpha = H \land V\alpha = L$ , and because H and L are assumed unequal, this is equivalent to ff, the logical value false. Thus  $Pow \ \alpha \land Gnd \ \alpha$ , like ff, implies every assertion and so "implements" any specification whatsoever.

Several ways have been suggested to get around this undesirable situation. Sticking with the above method of modelling circuits by assertions, the only course is to use some other notion of implementation. In some contexts it appears reasonable to say a circuit implements a specification if the associated assertions are equivalent (see [Gor2]). But following that line would, in general, lead to unnecessarily detailed specifications. Another suggestion, discussed in [CGM], is to say a circuit  $circ(\iota, o)$  with input values  $V\iota$  and output values  $V\iota$ , correctly implements a specification spec $(\iota, o)$  iff

$$(\forall V\iota, Vo. \operatorname{circ}(\iota, o) \to \operatorname{spec}(\iota, o)) \land (\forall V\iota \exists Vo. \operatorname{circ}(\iota, o)).$$

A circuit meeting such a requirement cannot be equivalent to ff for any particular input value. But this solution depends on having clearly defined input and output points. It is hard to see, if this were so at every stage in constructing a design, how the method of construction could allow short-circuits to be formed, and any method which bans short-circuits outright is too restrictive to provide a general model. Another possibility, suggested in [F], is to use the power of higher order logic and make specifications of higher type than circuit behaviours. This proposal has promise but has not yet led a calculus for reasoning about circuits. Most significant of all, each of these suggestions fails to face the fact that voltage values other than high and low can appear in designs, often quite innocently, without trivialising their behaviour.

We look for a model of circuits which can handle voltage values other than just high and low, and in particular treat short circuits. When a source of power and ground are connected together they give rise to a voltage which has an indeterminate effect when applied to the gates of transistors. We can take a voltage to have value X when it lies

in a region between those corresponding to H and L. Similarly we can take a voltage at a point to have a value  $\emptyset$  when the point is not connected to any significant sources of charge. It will be useful to order the values  $H, L, X, \emptyset$  as

(Note this order is not directly related to the underlying order on voltages, measured as reals.) A point connected just to power takes the value H, just to ground the value L, to both the value X and to no sources the value  $\emptyset$ . Can our earlier ideas be adapted to cope with these extra values? For the composition of assertions to be conjunction we now require

Pow

$$\alpha \equiv V \alpha \geq H$$

,

Gnd  $\alpha \equiv V \alpha > L$ .

In this way we allow for the effect of the environment on the value at  $\alpha$ . Then the conjunction  $Pow \ \alpha \land Gnd \ \alpha$  is equivalent to  $V\alpha = X$ , as required, and not to ff. Unfortunately hiding can no longer be treated as simple  $\exists$ -quantification. For example, connecting and hiding a power source to the gate  $\gamma$  of an n-type transistor  $ntran(\alpha, \beta, \gamma)$  should yield a circuit equivalent in behaviour to a wire between  $\alpha$  and  $\beta$ . However  $ntran(\alpha, \beta, \gamma)$  is still described by

$$ntran(\beta, \delta, \gamma) \equiv (V\gamma = H \rightarrow V\beta = V\delta),$$

for the same reasons as before, so using 3-quantification to hide we obtain

$$\exists V \gamma. \ Pow \ \gamma \land ntran(\alpha, \beta, \gamma)$$

which is

$$\exists V\gamma.\ V\gamma \geq H \wedge (V\gamma = H \rightarrow V\alpha = V\beta).$$

This does not imply  $V\alpha = V\beta$ , the assertion we would like, because of the possibility that  $V\gamma = X$ .

The above example might suggest that when we hide a node the value associated with the node should be the least possible—to rule out the possibility that  $V\gamma = X$  in the example above. However, there are examples where this does not work. Consider hiding  $\gamma$  in the following circuit:

It is unclear whether we should hide  $\gamma$  with  $V\gamma$  taking the value H,L,X or  $\emptyset$ —all are possible.

One way to manage the new value X and still treat hiding by  $\exists$ -quantification is to impose enough directionality on devices so they can be modelled as functions. Again, this suffers the drawback of leading to an unrealistic model. There is no easy fix without complicating the relational model. We need somehow to express the fact that the values associated with a hidden point are precisely those which are maintained by connections to sources. We shall address this problem and the related one of providing a model which deals correctly with signal strengths.

#### 2. Signal strengths.

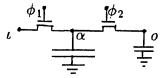

In NMOS technology p-type transitors are not available so inverters are constructed in a different way. An NMOS inverter has the following design

The design uses a strong resistance

$$\beta$$

$\delta$

connected to power. In NMOS this is implemented as a pull-up transistor. The behaviour of the inverter is remarkably subtle for its size (see [MC, MD]). In those environments where the point  $\beta$  is not connected to any other sources, the inverse of the value  $V\gamma$ , input at  $\gamma$ , is output as  $V\beta$  at  $\beta$ , so as a makeshift description of its behaviour we can take:

$$V\gamma = L \rightarrow V\beta = H \wedge V\gamma = H \rightarrow V\beta = L.$$

Later in section 4, after we have given the semantics of circuits and enriched the class of assertions, we can provide a complete description of its behaviour and, in particular, see what value  $V\beta$  takes for input  $V\gamma = X$ . The informal English description of how the inverter works is sometimes given as follows:

When  $\gamma$  is low the *n*-type transistor disconnects so the only voltage contribution to  $\beta$  is from the power source so  $\beta$  is high.

When  $\gamma$  is high the transistor connects so there is a voltage contribution of low from ground and a voltage contribution of high from power, weakened however by the large resistor, so the contribution from ground dominates and the net effect is to make  $\beta$  low.

Though this argument is perhaps not convincing at first, it can be justified by a simple application of Ohm's law. Suppose  $\gamma$  is high. Then  $\alpha$  and  $\beta$  are connected with a very small resistance r relative to the large resistance R between  $\beta$  and  $\delta$ . Let  $v_{\alpha}, v_{\beta}, v_{\delta}$  be the voltage values (real numbers) at the corresponding points. By Ohm's law we see

$$\frac{v_{\beta} - v_{\alpha}}{v_{\delta} - v_{\beta}} = \frac{Ir}{IR} = \frac{r}{R}$$

which we have assumed is very small. Because  $v_{\alpha}$  is safely inside the half-open interval qualifying as high, taking R large enough ensures  $v_{\beta}$  is high too.

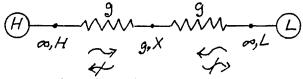

It is often convenient to use the inverse notion of conductance instead of resistance. In the literature (e.g. [B, Hay]), sources are pictured as transmitting signals to points of a circuit. The signals not only have a value— $H, L, X, \emptyset$ —but also a strength depending on the conductance strength of the path along which the signal has travelled. These ideas generalise when signals from capacitance, another source of charge, are considered.

The NMOS inverter illustrates a principle used in circuit design:

A signal from power or ground via a strong conductance overrides a signal via a relatively weak conductance.

It is not unusual for designs to use three ranks of conductance strengths, a signal via a conductance in one rank is overridden by a signal via a conductance in a rank strictly above it.

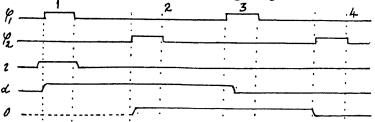

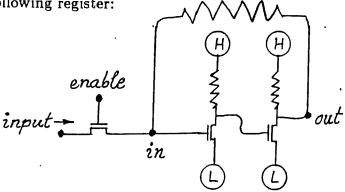

Extra signal strengths arise from capacitance. A simple dynamic register takes the form

in which use is made of the high capacitance  $cap^{\alpha}$  at the node  $\alpha$ . The points  $\phi_1$  and  $\phi_2$  are connected to clocks which alternately send pulses of high and low voltage. They are out of phase as shown in the timing diagram below. If a signal, say from power, is present at a pulse of  $\phi_1$ , then the left transistor connects and the right transistor disconnects and whatever charge was stored at  $cap^{\alpha}$  is overridden by the current supplied from  $\iota$ . This assumes the clock pulse of  $\phi_1$  is long enough for the opposite charge stored in  $cap^{\alpha}$  to drain away. Then when  $\phi_1$  goes low both transistors are disconnecting and  $cap^{\alpha}$  stores a high voltage. This is delivered at o at the next rise of the clock  $\phi_2$ . Assuming node  $\alpha$  has a very high capacitance relative to o, the net effect is to produce a high voltage at o. This is illustrated in the timing diagram.

More succinctly we can describe the behaviour by

$$\forall t. \ V(o,t+1) = V(\iota,t)$$

where we take a discrete model of time with the high pulses of  $\phi_1$  and  $\phi_2$  corresponding to alternate numbers.

We used two principles to explain the behaviour of the dynamic register:

A signal from power or ground overrides a signal from a capacitance.

A signal from a large capacitance overrides a signal from a relatively weak capacitance.

A circuit design may involve a range of signal strengths which give a discrete measure of the current driving capability in the analogue circuit. The strength order is derived from a deliberately crude ranking of resistances and capacitances. Two resistances R and R' are assigned conductance strengths g, g' respectively, with g < g', if the ratio R/R' is very large. Then, arguing by Ohm's law, as we did before, if two resistances R and R' of strength g and g' are connected in series the resulting resistance R + R' should be assigned conductance strength  $g \cdot g'$ , the minimum of g and g'. This is because, for example, if R/R' is very large then so is (R+R')/R'. Connected in parallel their resulting resistance, RR'/(R+R'), should be assigned strength g+g', the maximum of g and g'. We would like to conclude that whenever we encounter a chain of resistances, of strengths  $g_1, g_2, \ldots, g_n$ , in series then we can regard it as equivalent to a single resistance of strength  $\Pi\{g_1,\ldots,g_n\}$ , the minimum strength along the chain. We cannot quite do this because "very large" is a vague concept; even though R/R' is very large R/nR' need not be. The point is that with respect to a particular design a very large number L can be chosen (to stand for "very large") so that the number of times resistances are placed in series or parallel in the design has no significant effect. Still, we should bear in mind that such problems can arise through our choosing to work with an abstract strength order, and that without care they can lead to inaccuracies in the model.

In a similar way capacitances are ranked in a total order of capacitance strengths. The signal stored by a capacitance of strength k is overridden by one from a capacitance of strength k' with k < k'. As we have observed, signals from sources override those due to capacitance so we arrive at the concept of a strength order as consisting of two finite sets  $K = \{k_1, \ldots, k_m\}$  and and  $G = \{g_1, \ldots, g_n\}$  in a total order

$$0 < k_1 < \cdots < k_m < g_1 < \cdots < g_n < \infty.$$

We use 0, zero strength, to stand for a strength of a negligible signal, from zero capacitance or a non-conductance, and  $\infty$  to be the strength of a signal from a source via a perfect conductance. The restriction  $\mathbf{K} = (K \cup \{0\}, \leq)$ , is called the capacitance order and its elements are called capacitance strengths. The restriction  $\mathbf{G} = (G \cup \{0, \infty\}, \leq)$  is called the conductance order, with elements called conductance strengths. Often we shall write a strength order as  $\mathbf{S}$ , and sometimes, when we wish to emphasise the conductance and capacitance strengths as  $\mathbf{S}_{K,G}$ . We shall use  $s \cdot s'$  for the minimum and

s + s' for the maximum of two strengths s and s'. We can write the minimum of a set of strengths A as  $\Pi A$  and their maximum as  $\Sigma A$ .

Recall the lattice of values:

The value  $\emptyset$  is associated with points which are at 0 strength so they are not connected to any significant sources of current or charge. Sometimes it is said that such points "float" because they adopt, or float to, the value of whatever they are connected to. We can call the  $\emptyset$  value floating, though sometimes we use it in contexts where the intuition suggesting this name is not appropriate. Values now form a finite lattice. We use U+U' for the join (or least upper bound) of two values  $U,U',U\cdot U'$  for their meet. and  $\Sigma A$ , and  $\Pi A$ , for the join, respectively meet, of a set of values A. (Our notation is thus consistent with that for the strength order considered as a lattice.)

Consider how signals are transmitted through a resistance between  $\alpha$  and  $\beta$  of strength g. Suppose a signal of strength g', a conductance strength, and value  $V \in \{H, L\}$  is applied to one end  $\alpha$  of the resistance. By our earlier observation concerning resistances in series, the resulting signal at  $\beta$  has strength  $g \cdot g'$  and value V.

$$(V) \xrightarrow{g'} \alpha \qquad g \xrightarrow{g} g \cdot g', V$$

If instead a signal of strength k, a capacitance strength, and value V is applied at  $\alpha$ , assuming the resistance has negligible capacitance, the resulting signal at  $\beta$  is the same, with strength still k and value V.

In both situations a signal of strength s and value V, applied at  $\alpha$  gives rise to a signal of strength  $s \cdot g$  and value V at  $\beta$ . A signal of strength s > g is cut-down to a signal of strength g while a signal of strength  $s \leq g$  is unchanged.

Notice that these assumptions are dependent on connections lasting long enough for the charges in capacitances to reach stable levels. We shall have cause to examine this assumption more carefully later in the conclusion.

We have said that directionality in circuits should be derived rather than imposed. Where is this directionality to come from? It comes from the effects of resistance. Consider a resistance of conductance strength g between points  $\alpha$  and  $\beta$  in some environment in which the strength of the signal at  $\alpha$  is  $S\alpha$  and that at  $\beta$  is  $S\beta$ . Assume too

that the associated values are  $V\alpha$  and  $V\beta$  in  $\{H, L, X, \emptyset\}$ . We know from the behaviour of resistances, considering the transmission of signals from  $\alpha$  to  $\beta$  that

$$S\alpha \cdot g \leq S\beta$$

(and similarly that  $S\beta \cdot g \leq S\alpha$ ).

In the case when  $S\alpha \cdot g < S\beta$  the signal from  $\alpha$  is overridden and so has no effect on that at  $\beta$ . On the other hand, if  $S\alpha \cdot g = S\beta$  then the signal from  $\alpha$  is not overridden and has an effect on that at  $\beta$ . Values "flow" from  $\alpha$  to  $\beta$  and so  $V\alpha \leq V\beta$ . In particular if  $V\alpha = H$  then  $V\beta = H$ , or X if  $\beta$  happens also to be connected to ground. There is a connection, possibly one-way, between  $\alpha$  and  $\beta$ , and we can write this suggestively as  $\alpha \leadsto \beta$ . We have  $\beta \leadsto \alpha$  as well only if  $S\beta \cdot g = S\alpha$ . It is easy to check that elements of this "flow relation" compose, so if  $\alpha \leadsto \beta$  and  $\beta \leadsto \gamma$  then  $\alpha \leadsto \gamma$ . For this more general understanding of the flow relation we still have

$$\alpha \Rightarrow \beta \rightarrow V\alpha < V\beta$$

.

It is helpful to think of the strength function S as giving a "height" of each point, and indeed

$$\alpha \rightsquigarrow \beta \rightarrow S\beta < S\alpha$$

so flow is never "uphill". This understanding accounts for the following assignment of flows, strengths and values:

It is the flow relation, rather than the graph of conductances, which plays the central control in analysing the behaviour of circuits.

This exposition has been based largely on Bryant's work (see [B]). The paper [Hay] deals with similar ideas but the model it presents seems only to apply in situations where the components can be understood as functions with definite input and output ports. Our "flow relation" corresponds to Bryant's idea of "unblocked path" in a steady state. Note our subsequent presentation will be markedly different than Bryant's. This is because we shall develop a compositional model, one on which we can base a proof system structured by the way circuits are built-up.

# 3. States of circuits—static configurations.

Assume a particular strength order  $S = S_{K,G}$ .

We explain the intuition behind the definition of static configuration. Imagine a circuit connected to some environment via points  $\Lambda$ . Assume that in this environment the circuit has settled into a steady state. The definition of static configuration is intended to formalise this notion, picking out those features essential for the compositional account of circuit behaviour that follows. Note here we ignore the possibility that a circuit may never settle into a steady state in an environment. This model of circuits can be seen as analogous to those models of programs which only capture their partial correctness.

In a static configuration each point of a circuit is associated with a signal with a certain strength and value. So each point  $\alpha$  is associated with with a strength  $S\alpha \in S$  and a resultant value  $V\alpha \in V$ . Some of this signal may be contributed by sources inside the circuit; the internal contribution at  $\alpha$  can be recorded by a value  $I\alpha \in V$ .

Of course points are connected to each other according to the state of transistors and the connections have certain conductance strengths. This gives rise to a flow relation  $\rightarrow$  between points, though in the rather indirect way we saw in the last section. It is this relation, derived from the more basic and detailed conductance relation between points, which plays the central role in our model of the behaviour of circuits. Intuitively, the relation  $\rightarrow$  captures the flow of information in a circuit; it expresses how the values of signals flow (or are transmitted) from points at high strength to points at lower or equal strength along flows of conductance.

3.1 Definition. Let  $\Lambda$  be a set of points. A static configuration of sort  $\Lambda$  is a 4-tuple

$$\langle S, V, I, \leadsto \rangle$$

where

$S: \Lambda \to \mathbf{S}$  (the strength function),  $V: \Lambda \to \mathbf{V}$  (the value function),

$I: \Lambda \to \mathbf{V}$  (the internal value function) and

$\Rightarrow$  is a reflexive, transitive relation on  $\Lambda$  (the flow relation),

which satisfy

- (i)  $\alpha \rightsquigarrow \beta \rightarrow S\alpha \geq S\beta$ ,

- (ii)  $\alpha \rightsquigarrow \beta \land S\alpha = S\beta \rightarrow \beta \rightsquigarrow \alpha$ ,

- (iii)  $\alpha \rightsquigarrow \beta \land S\beta \in K \rightarrow S\alpha = S\beta$ ,

- (iv)  $S\alpha = 0 \leftrightarrow V\alpha = \emptyset$ ,

- (v)  $I\alpha \leq V\alpha$ ,

- (vi)  $\alpha \rightsquigarrow \beta \rightarrow I\alpha \leq I\beta \land V\alpha \leq V\beta$ .

Write  $sort(\sigma)$  for the sort of a configuration  $\sigma$ . Write  $Sta_S[\Lambda]$  for the set of static configurations of sort  $\Lambda$ . We say a static configuration is finite when it has finite sort.

Property (i) says a signal cannot flow from a point at weaker strength to a point at stronger strength. Property (ii) expresses the fact that if  $\alpha \rightsquigarrow \beta$ , so information can

flow from  $\alpha$  to  $\beta$ , and  $\alpha$  and  $\beta$  are at the same strength then  $\beta \leadsto \alpha$ , so information can flow in the other direction too. To justify (ii) assume that  $\alpha \leadsto \beta$  and  $S\alpha = S\beta$ . Then, according to the last section,  $\alpha \leadsto \beta$  arises iff there is a conductance, of strength g say, between  $\alpha$  and  $\beta$  so that  $S\alpha \cdot g = S\beta$ . Hence  $S\beta \cdot g = S\alpha$  too making  $\beta \leadsto \alpha$ . Property (iii) states that if  $\alpha \leadsto \beta$  and  $S\beta$  is a capacitance strength then  $S\alpha$  is the same strength. This follows capacitance strengths are always ranked below those of conductance in the strength order. Assume  $\alpha \leadsto \beta$  and  $S\beta \in K$ . Then  $S\alpha \cdot g = S\beta$  for some conductance strength g for which  $S\beta \le g$ . This can only occur with  $S\alpha = S\beta$ . Property (iv) says a signal of no strength has no content and vice versa. Naturally the internal contribution cannot exceed the resultant value—property (v). The final property (vi) formalises the intention that  $\leadsto$  should represent the direction in which information is transmitted through the circuit.

The strength and value functions are used later to specify when two static configurations can sensibly be linked together in parallel. It is necessary to keep track of the internal contribution to the value function and flow relation to give a satisfactory treatment of hiding. They determine when a point may be insulated from the environment without changing its resultant signal.

To make these somewhat abstract ideas a little clearer we present some static configurations of basic devices.

#### 3.2 Example. A source:

A source  $Pow^{\alpha}$  supplies an internal contribution of strength  $\infty$  and value H to a point  $\alpha$  which may well receive a contribution of L from the environment to yield a resultant value  $V\alpha = X$ .

$$S\alpha = \infty \wedge V\alpha = X \wedge I\alpha = H$$

#### 3.3 Example. A wire:

A resistance of perfect conductance  $res_{\infty}^{\alpha,\beta}$  can be regarded as a wire between  $\alpha$  and  $\beta$  in which signals flow unimpaired between the two points. There are no internal sources.

$$S\alpha = S\beta = s \wedge V\alpha = V\beta = U \wedge I\alpha = I\beta = \emptyset \wedge \alpha \leadsto \beta \wedge \beta \leadsto \alpha$$

# 3.4 Example. A resistance:

A resistance of strength g contains no internal sources. If (in the environment) power and no other source is applied at  $\alpha$  and  $\beta$  is connected to ground via conductance g then the static configuration shown would result.

$$\alpha \qquad \qquad \beta \qquad \qquad \alpha \qquad \qquad \beta \qquad \qquad \beta \qquad \qquad \alpha \qquad \qquad \alpha \qquad \qquad \beta \qquad \qquad \alpha \qquad \alpha \qquad \qquad$$

# 3.5 Example. A transistor:

134.

If an n-type transistor  $ntran^{\alpha,\beta,\gamma}$  is placed in an environment in which positive charge is applied to the gate  $\gamma$  then  $\alpha$  and  $\beta$  are connected and behave like a wire.

In a static configuration, two points  $\alpha$  and  $\beta$  may be both in the relation  $\alpha \rightsquigarrow \beta$  and  $\beta \rightsquigarrow \alpha$ . In this case the points  $\alpha$  and  $\beta$  receive the same signals both in value and strength. Sometimes neither  $\alpha \rightsquigarrow \beta$  nor  $\beta \rightsquigarrow \alpha$ —the two points are incomparable—with respect to the flow relation  $\rightsquigarrow$ . Intuitively this means that the signal at one point does not affect the signal at the other. We introduce notation to describe these circumstances.

**3.6 Definition.** Let  $\sigma = \langle S, V, I, \leadsto \rangle$  be a static configuration of sort  $\Lambda$ . For  $\alpha, \beta \in \Lambda$  define

$$\alpha \sim \beta \equiv \alpha \leadsto \beta \land \beta \leadsto \alpha$$

$$\alpha \parallel \beta \equiv \neg(\alpha \leadsto \beta) \land \neg(\beta \leadsto \alpha).$$

In the special case where the effects of resistance are negligible there is only one positive conductance strength  $\infty$ , corresponding to perfect conductance, the flow

relation  $\sim$  coincides with the equivalence relation  $\sim$ . The proof is a little exercise in using the axioms which define a static configuration.

**3.7 Proposition.** Assume there are only the two conductance strengths  $0 < \infty$ . Then for any static configuration  $\sigma$  the relation  $\rightarrow$  is symmetric and so an equivalence relation on points with  $x \rightarrow y$  iff  $x \sim y$  for all points x, y of  $\sigma$ .

*Proof.* Suppose  $\alpha \rightsquigarrow \beta$ .

Assume  $S\beta = 0$ . Then  $S\alpha = 0$  by (iv) and (vi). Assume  $S\beta \in K$ . Then  $S\alpha = S\beta$  by (iii). Assume the remaining case that  $S\beta = \infty$ . Then  $S\alpha = \infty$  by (i). Therefore, as in all cases  $S\alpha = S\beta$ , we see  $\beta \leadsto \alpha$  by (ii).

Thus  $\alpha \rightsquigarrow \beta$  implies  $\beta \rightsquigarrow \alpha$ , making  $\rightsquigarrow$  symmetric. By definition  $\rightsquigarrow$  is reflexive and transitive, so  $\rightsquigarrow$  is an equivalence relation. Hence the relations  $\rightsquigarrow$  and  $\sim$  are equal.

Proposition 3.7 may increase our level of confidence in the axioms proposed for a static configuration. Still there are sufficiently many axioms, and the idea of static configuration sufficiently complicated, to raise the question of their completeness. We have used arguments from physics for the soundness of the axioms. To show completeness we need an argument showing that there are no properties shared by all static configurations of real (or buildable) circuits which do not follow from those written down in the definition? Afterall, axiom (ii) does not spring to mind immediately from idea of static configuration or the examples we have considered. Later in proposition 4.4 we shall show that every structure  $\langle S, V, I, \rightsquigarrow \rangle$  on a finite set of points which satisfies all the axioms of 3.1 can be realised as the static configuration of a circuit built-up from resistances and sources connected to those points. Then any property of structures  $\langle S, V, I, \rightsquigarrow \rangle$  which holds of all static configurations of circuits must also hold of all finite structures in 3.1.

We make the static configurations with sorts  $\Lambda$  a subset of some universe of points  $\Pi$  into a partial algebra with operations associated with composition and hiding.

**3.8 Notation.** Let L be a complete lattice ordered by  $\leq$  with binary join + and arbitrary join  $\Sigma$ . Let M and  $\Lambda$  be sets. Let  $f: M \to L$  and  $g: \Lambda \to L$  be functions to the lattice. We define their join  $f+g: M \cup \Lambda \to L$  by

$$(f+g)(x) = \left\{ egin{array}{ll} f(x) & ext{if } x \in M \setminus \Lambda \ g(x) & ext{if } x \in \Lambda \setminus M \ f(x) + g(x) & ext{if } x \in M \cap \Lambda. \end{array}

ight.$$

for  $x \in M \cup \Lambda$ .

If  $f: M \to L$  we write  $f[\Lambda]$  for the restriction of f to the subset  $M \cap \Lambda$ . If R is a binary relation on M we write  $R[\Lambda] = R \cap (\Lambda \times \Lambda)$  for its restriction.

Let R be a binary relation on M. Let  $f: \Lambda \to L$  be a function from  $\Lambda \subseteq M$  to the lattice L. Define the application of relation R to f to be the function  $(R \cdot f): M \to L$  given by

$$(R \cdot f)(x) = \Sigma \{ f(z) \mid z \in \Lambda \& (z, x) \in R \}.$$

We shall use this operation to transmit the values at a subset of points in a static configuration to other points in accord with the flow relation  $\rightarrow$ .

Assume  $\sigma_0$  is a static configuration of a circuit  $c_0$  and  $\sigma_1$  is a static configuration of a circuit  $c_1$ . When can  $\sigma_0$  and  $\sigma_1$  be composed to give a static configuration of  $c_0$  and  $c_1$ ? When their strengths and values agree at common points; only then do  $\sigma_0$  and  $\sigma_1$  make consistent assumptions about the environment. Then the resulting flow relation should be the transitive closure of the flow relations in the components and the internal contribution should be spread out accordingly.

**3.9 Definition.** Let  $\sigma_0 = \langle S_0, V_0, I_0, \leadsto_0 \rangle$  be a static configuration of sort  $\Lambda_0$  and  $\sigma_1 = \langle S_1, V_1, I_1, \leadsto_1 \rangle$  be a static configuration of sort  $\Lambda_1$ . Define their composition to be

$$\sigma_0 \bullet \sigma_1 = \left\{ egin{array}{ll} \langle S, V, I,

ightharpoonup

angle & ext{if } S_0 \centsize \Lambda_1 = S_1 \centsize \Lambda_0 \text{ and} \ & V_0 \centsize \Lambda_1 = V_1 \centsize \Lambda_0 \text{ and} \ & ext{undefined} & ext{otherwise} \end{array}

ight.$$

where

$$S = S_0 + S_1,$$

$V = V_0 + V_1,$

$\Rightarrow = (\Rightarrow_0 \cup \Rightarrow_1)^*$  and

$I = \Rightarrow_- (I_0 + I_1).$

Suppose  $\sigma$  is a static configuration of a circuit c. When does  $\sigma$  restrict to a configuration of a circuit like c but in which all points but those in  $\Lambda$  are hidden? When all the points to be hidden have values (and strengths) which result from the combined effect of internal sources and the contribution from unhidden points  $\Lambda$ . More precisely when for all points  $\alpha$  to be hidden we have  $V\alpha = I\alpha + (\sim V \cap \Lambda)\alpha$ . Then the hiding of points not in  $\Lambda$  will make no difference.

**3.10 Definition.** Let  $\sigma = \langle S, V, I, \leadsto \rangle$  be a static configuration of sort M and  $\Lambda$  a set of points. Define the restriction of  $\sigma$  to  $\Lambda$  to be

$$\sigma \lceil \Lambda = \begin{cases} \langle S \lceil \Lambda, V \rceil \Lambda, I \lceil \Lambda, \rightsquigarrow \lceil \Lambda \rangle & \text{if } V = I + (\rightsquigarrow V \lceil \Lambda) \\ \text{undefined} & \text{otherwise.} \end{cases}$$

**3.11 Notation.** We indicate  $\sigma_0 \bullet \sigma_1$  and  $\sigma \lceil \Lambda$  are defined by writing  $\sigma_0 \bullet \sigma_1 \downarrow$  and  $\sigma \lceil \Lambda \downarrow$ .

#### 4. The semantics of static circuits.

Assume the strength order is  $S = S_{K,G}$ . Also assume a countably infinite set of point names  $\Pi$ .

#### 4.1 Definition. A little language for static circuits—circ.

The syntax of circ is given by:

$$c ::= Pow \ \alpha \mid Gnd \ \alpha \mid cap_{kU}\alpha \mid res_g(\alpha,\beta) \mid ntran(\alpha,\beta,\gamma) \mid ptran(\alpha,\beta,\gamma) \mid c \bullet c \mid c \lceil \Lambda$$

where  $k \in K$ ,  $\emptyset \neq U \in \mathbf{V}$ ,  $g \in G \cup \{\infty\}$  and  $\alpha, \beta, \gamma$  are distinct point names in  $\Pi$  and  $\Lambda \subseteq \Pi$ .

The constant terms  $Pow \alpha$  and  $Gnd \alpha$  stand for sources providing a signal of strength  $\infty$  at point  $\alpha$  with values H and L respectively. Another kind of source arises through charge storage, when the strength s is an element of K. A term  $cap_{kU}\alpha$  represents a capacitance of strength k, charged up with value U. The constant term  $res_g(\alpha,\beta)$  stands for a resistance connecting points  $\alpha$  and  $\beta$  with conductance  $g \in G$ . The constant  $ntran(\alpha,\beta,\gamma)$  stands for an n-type transistor with a gate  $\gamma$  which when it is high connects points  $\alpha$  and  $\beta$  with perfect conductance. The constant term  $ptran(\alpha,\beta,\gamma)$  stands for a p-type transistor with a gate  $\gamma$  which connects points  $\alpha$  and  $\beta$ , again with perfect conductance, when the gate  $\gamma$  is low. Of course, should the effect of resistance be significant we can insert a suitable resistance between  $\alpha$  and  $\beta$ .

We take the behaviour of a circuit in circ to be the set of possible static configurations it can settle into in some static environment. For compactness, in the following definition we assume that a static configuration  $\sigma$  is  $\langle S, V, I, \rightsquigarrow \rangle$ .

# 4.2 Definition. The semantics of circ.

Let Sta =  $\bigcup_{\Lambda \subseteq \Pi} \operatorname{Sta}[\Lambda]$ , the set of static configurations with sorts which are subsets of  $\Pi$ .

Define the semantic function  $[\![\ ]\!]:\mathbf{circ}\to P(\operatorname{Sta})$  to be the map defined by the structural induction

$$[\![ Pow \ \alpha ]\!] = \{ \sigma \in \operatorname{Sta}[\alpha] \mid S\alpha = \infty \land I\alpha = \operatorname{H} \}$$

$$[\![ Gnd \ \alpha ]\!] = \{ \sigma \in \operatorname{Sta}[\alpha] \mid S\alpha = \infty \land I\alpha = \operatorname{L} \}$$

$$\llbracket cap_{kU}\alpha

rbracket = \{\sigma\in\operatorname{Sta}[lpha]\mid Slpha\geq k\land \ (Slpha=k

ightarrow Ilpha=U)\land (Slpha>k

ightarrow Ilpha=\emptyset)\}.$$

$$\lceil res_{g}(\alpha,\beta) \rceil = \{ \sigma \in \operatorname{Sta}[\alpha,\beta] \mid I\alpha = \emptyset \land I\beta = \emptyset \land \\ S\alpha \cdot g \leq S\beta \land S\beta \cdot g \leq S\alpha \land \\ (S\alpha \cdot g = S\beta \leftrightarrow \alpha \leadsto \beta) \land (S\beta \cdot g = S\alpha \leftrightarrow \beta \leadsto \alpha) \}$$

$$\lceil ntran(\alpha,\beta,\gamma) \rceil = \{ \sigma \in \operatorname{Sta}[\alpha,\beta,\gamma] \mid I\alpha = \emptyset \land I\beta = \emptyset \land I\gamma = \emptyset \land \\ \gamma \mid\mid \alpha \land \gamma \mid\mid \beta \land (\alpha \mid\mid \beta \lor \alpha \leadsto \beta) \land \\ (V\gamma = H \to \alpha \leadsto \beta) \land (V\gamma = L \to \alpha \mid\mid \beta) \}$$

$$\lceil ptran(\alpha,\beta,\gamma) \rceil = \{ \sigma \in \operatorname{Sta}[\alpha,\beta,\gamma] \mid I\alpha = \emptyset \land I\beta = \emptyset \land I\gamma = \emptyset \land \\ \gamma \mid\mid \alpha \land \gamma \mid\mid \beta \land (\alpha \mid\mid \beta \lor \alpha \leadsto \beta) \land \\ (V\gamma = L \to \alpha \leadsto \beta) \land (V\gamma = H \to \alpha \mid\mid \beta) \}$$

$$\lceil c \bullet d \rceil = \{ \sigma \bullet \rho \mid \sigma \in \llbracket c \rrbracket \& \sigma \cap \Lambda \downarrow \}.$$

$$\lceil c \cap A \rceil = \{ \sigma \cap A \mid \sigma \in \llbracket c \rrbracket \& \sigma \cap A \downarrow \}.$$

Further terms can be defined. For example, we can define a wire  $wre(\alpha, \beta)$  between  $\alpha$  and  $\beta$ , with denotation

$$\llbracket \mathit{wre}(\alpha,\beta) \rrbracket = \{ \sigma \in \mathrm{Sta}[\alpha,\beta] \mid I\alpha = \emptyset \land I\beta = \emptyset \land \alpha \sim \beta \},$$

which can be realised by a resistance with perfect conductance, i.e.

$$\llbracket wre(\alpha,\beta) \rrbracket = \llbracket res_{\infty}(\alpha,\beta) \rrbracket.$$

More interestingly, We can define a general source  $sce_{sU}\alpha$ , at  $\alpha$ , of strength s and value  $U \in \mathbf{V}$ , to have denotation

$$\llbracket sce_{sU}\alpha \rrbracket = \{\sigma \in \operatorname{Sta}[\alpha] \mid S\alpha \geq s \land \\ (S\alpha = s \to I\alpha = U) \land (S\alpha > s \to I\alpha = \emptyset) \}$$

Such a source only makes a contribution at  $\alpha$  if the strength of  $\alpha$  is exactly s. We only consider sources  $sce_{sU}\alpha$  for which  $s=0 \Leftrightarrow U=\emptyset$ —any others could have no static configurations. If s is a capacitance strength k then such a weakened source can be realised by the charged capacitance  $cap_{kU}^{\alpha}$ . If s is a conductance strength g it can be realised by passing signals from ground or power through a resistance of strength g. For example, if U=H, we have

$$\llbracket sce_{qH} \alpha \rrbracket = \llbracket (Pow \beta \bullet res_q(\beta, \alpha)) \lceil \alpha \rrbracket.$$

The one remaining case,  $sce_{00}\alpha$  can be realised as a single connection point standing alone, and this can be made by hiding one end of a resistance, i.e.

$$\llbracket sce_{00}\alpha \rrbracket = \llbracket res_g(\alpha,\beta) \lceil \alpha \rrbracket.$$

It is helpful to explain the ways sources combine using an ordering between pairs sU, where  $s \in S$  and  $U \in V$  and s = 0 iff  $U = \emptyset$ . On such pairs define

$$sU \le s'U'$$

iff  $s < s'$  or  $(s = s' \& U \le U')$ .

This forms a finite distributive lattice (meet · and join +), mentioned in [B1] and [Hay], which may be drawn as:

Now we can list some basic equivalences between circuit terms, which can be proved from the denotational semantics.

# 4.3 Proposition. Some equivalences on circuits

Write c = c' iff [c] = [c'], for circuit terms c, c'.

Realising sources: If k is a capacitance strength and g a conductance strength then

$$sce_{00}\alpha = res_g(\alpha, \beta)\lceil \alpha,$$

$sce_{kU}\alpha = cap_{kU}\alpha,$

$sce_{gH}\alpha = (Pow \beta \bullet res_g(\beta, \alpha))\lceil \alpha,$

$sce_{gL}\alpha = (Gnd \beta \bullet res_g(\beta, \alpha))\lceil \alpha,$

$sce_{gX}\alpha = sce_{gH}\alpha \bullet sce_{gL}\alpha.$

Composing sources:  $sce_{sU}\alpha \bullet sce_{s'U'}\alpha = sce_{sU+s'U'}\alpha$ . Resistances in series and parallel:

$$(res_g(\alpha,\beta) \bullet res_{g'}(\beta,\gamma)) \lceil \{\alpha,\gamma\} = res_{g,g'}(\alpha,\gamma).$$

$(res_g(\alpha,\beta) \bullet res_{g'}(\alpha,\beta)) = res_{g+g'}(\alpha,\beta).$

Wires, resistances and transistors:

$$wre(\alpha, \beta) = res_{\infty}(\alpha, \beta)$$

$$= (Pow \ \alpha \bullet ntran(\alpha, \beta, \gamma)) \lceil \{\alpha, \beta\} \rceil$$

$$= (Gnd \ \alpha \bullet ptran(\alpha, \beta, \gamma)) \lceil \{\alpha, \beta\} \rceil.$$

Earlier we pointed out the problem of knowing whether or not we had written down sufficient axioms for static configurations. From the remarks in the last section it is sufficient to show every finite static configuration can be realised as a static configuration of a circuit term. This is established in the following proposition.

**4.4 Proposition.** Any static configuration  $\sigma$  of sort  $\Lambda$  a finite subset of  $\Pi$  is the static configuration of some circuit c i.e.  $\sigma \in [c]$ .

*Proof.* We sketch the proof. Given  $\sigma$ , we define the required circuit to be the composition of the following finite set of components:

$$\{sce_{S\alpha U}\alpha \mid \alpha \in \Lambda \ \& \ I\alpha = U \neq \emptyset\} \cup \\ \{res_g(\alpha,\beta) \mid \alpha \not\sim \beta \ \& \ g \text{ is the minimum conductance strength s.t. } S\alpha \cdot S\beta \leq g\}.$$

This uses our knowledge of how to build all sources  $sce_{sU}\alpha$  as circuits. From the definition of sources, resistances and composition, it can be seen  $\sigma \in [c]$ .

Now we can see how to give a more accurate specification of the NMOS inverter of section. 2. Its circuit is constructed by the term

$$c \equiv (ntran(\alpha, \beta, \gamma) \bullet res_g(\beta, \delta) \bullet Pow \ \delta \bullet Gnd \ \alpha) [\{\gamma, \beta\}.$$

Informally, its output  $\beta$  behaves like a direct connection to ground when its input  $\gamma$  is high and like a weakened power source when  $\gamma$  is low. Formally, if we define

$$Sce_{sU}x \equiv Sx \geq s \land$$

$Sx = s \rightarrow Ix = U \land$

$Sx = s \rightarrow Ix = U.$

then we can say c satisfies the assertion

$$V \Upsilon = H \rightarrow Sce_{\infty L} \beta \wedge V \Upsilon = L \rightarrow Sce_{gH} \beta.$$

This illustrates how the model is closely associated with assertions for specifying the behaviour of circuits. Of course we should give a more rigorous treatment of their syntax and semantics. This is done in the next section where a complete proof system is presented for proving a circuit satisfies an assertion.

Technically, it will be simpler to work with more basic predicates than Vx and Ix. Say  $\sigma$  satisfies  $H\alpha$  if  $H \leq V\alpha$ , meaning  $\alpha$  is connected to a source of positive charge (either in the environment or internal). Similarly, say  $\sigma$  satisfies  $L\alpha$  if  $L \leq V\alpha$ . The assertion  $V\alpha = H$  can then be expressed equivalently by  $H\alpha \wedge \neg L\alpha$ , while  $V\alpha = X$  is equivalent to  $H\alpha \wedge L\alpha$ . For internal signals say  $\sigma$  satisfies  $h\alpha$  if  $H \leq I\alpha$  and  $l\alpha$  if  $L \leq V\alpha$ . Then, for instance,  $\sigma$  satisfies  $h\alpha$  if  $\alpha$  is connected to an internal source of positive charge.

To conclude this section, we note we have not completely eliminated the kind of problems raised in the section 1. Certainly we now have an adequate treatment of short circuits. In particular

$$[\![Pow \ \alpha \bullet \ Gnd \ \alpha]\!] \neq \emptyset,$$

and so, when we come to the logic, the circuit  $Pow \alpha \bullet Gnd \alpha$  will not satisfy ff. However, there are other circuit terms which do denote  $\emptyset$  and so will satisfy ff. Roughly speaking,

these are terms which represent circuits whose only possible behaviour is to oscillate. For example the term

$$\bullet \equiv (ntran(\alpha, \beta, \gamma) \bullet res_g(\beta, \delta) \bullet Pow \ \delta \bullet Gnd \ \alpha \bullet wre(\gamma, \beta)) [\emptyset,$$

with g a conductance strength strictly between 0 and  $\infty$ , "ties-back" the output of an NMOS inverter to its input, and then insulates all points from the environment. It can be drawn as:

The circuit c denotes the emptyset,  $[c] = \emptyset$ . (The circuit is a little peculiar in that it has an empty sort. A trivial modification—connecting the wire to the gate of another transistor—produces a term with nonempty sort and empty denotation.) The logic of circuits will thus be akin to the logic of partial correctness assertions (Hoare logic); a purely oscillating circuit will satisfy any assertion just as a diverging program satisfies all partial correctness assertions.

### 5. A proof system.

We show how to construct a proof system for circuits. In this section we highlight its main features, and refer to the appendix for the full syntax, semantics and proof rules. The proof system consists of a complete set of rules to prove formally that a circuit, described by a term c, satisfies a property described by an assertion A. It is compositional in that proving an assertion holds of a compound circuit of the form  $c \lceil \Lambda$  or  $c_0 \bullet c_1$  reduces to proving assertions about the components, c of  $c \lceil \Lambda$ , and  $c_0$ and  $c_1$  of  $c_0 \cdot c_1$ . Assertions describe the possible static configurations the circuit can settle into. We have seen several examples where a static configuration satisfies some particular logical assertion. Of course, an assertion determines all those configurations which satisfy it, and in the formal treatment we take the meaning, or denotation, of an assertion A, written [A], to be the set of all those static configurations which satisfy it. Thus we seek a way to prove relations  $[c] \subseteq [A]$ , which we write as  $c \models A$ , hold between circuit terms c and assertions A. In order to establish such relations it is useful to treat circuit terms as just another kind of assertion in our semantics and proof rules. We write  $\sigma \models c$  to mean  $\sigma$  is a static configuration of the circuit c, just as we do for more usual assertions. We make use of relations  $\Gamma \models A$  between a set  $\Gamma$  and A where  $\Gamma$  and A are circuit-assertions (see L.1 in the appendix) which may include, or be built out of circuit terms. The relation  $\Gamma \models A$  means any static configuration  $\sigma$  which satisfies all of  $\Gamma$  satisfies A too. Such relations have their syntactic counterpart in the proof system. The proof rules are written in a natural-deduction style, keeping track of the assumptions in sequents of the form  $\Gamma \vdash A$ .

We settle on a countably infinite set of point names  $\Pi$ , with typical members  $\alpha, \beta, \cdots$ , and a fixed strength order S. It is simplest to assume that point names are in 1-1 correspondence with points, so two distinct names cannot be associated with the same point (we shall axiomatise the equality relation between points accordingly). Our previous work suggests the form assertions should take. A static configuration  $\sigma$ , with sort  $\Lambda \subseteq \Pi$ , is a structure  $\langle S, V, I, \rightsquigarrow \rangle$  over individuals  $\Lambda$ . We could treat  $\sigma$  as a structure for a first order logic with function symbols S,V,I and relation symbols ightsquigarand =. We do not quite follow this course. There is first of all the problem that the sorts are not all the same, and in particular we allow the trivial empty static configuration—a source of trouble should we follow a traditional treatment where it is usual to ban empty structures. We could use a family of logics, one for each sort, but instead it is much more convenient and much less messy to use a free logic in which it is not necessary that terms are defined, or denote existing things. In the free logic a static configuration  $\sigma$  satisfies  $\forall x.A$  when  $A[\alpha/x]$  holds for all points  $\alpha$  in sort( $\sigma$ ), and similarly  $\sigma$  satisfies  $\exists x.A$  if for some  $\alpha$  in sort( $\sigma$ ) the assertion  $A[\alpha/x]$  is satisfied by  $\sigma$ ; quantification is only taken to be over existing, or defined, elements. On the other hand, all variables are understood to range over all potential individuals II. Our style of free logic is based on [S] and includes an existence predicate E;  $E\alpha$  holds in a static configuration precisely when  $\alpha \in \operatorname{sort}(\sigma)$ . We have constant symbols from  $\Pi$ , a function symbol S, as well as relations  $\rightarrow$  and = in the logical language. Instead of using functions V and I we use the predicates Hx, Lx and hx, lx mentioned in the last section 4.

The point relations, prel, have the form

$$H\pi \mid L\pi \mid h\pi \mid l\pi \mid \pi_0 = \pi_1 \mid \pi_0 \rightsquigarrow \pi_1 \mid E\pi$$

where  $\pi, \pi_0, \pi_1$  range over points and variables.

To reason formally about strengths we need strength expressions of the form

$$s \mid S\pi \mid e_0 \cdot e_1 \mid e_0 + e_1$$

where  $s \in S$ ,  $\pi$  is a point or variable and  $e_0, e_1$  are strength expressions. Note we need an existence predicate for strength expressions as well as points. This is because  $S\alpha$  only makes sense, with respect to a static configuration  $\sigma$ , if  $\alpha \in \text{sort}(\sigma)$ . Define the strength relations, srel, to have the form

$$Ee \mid e_0 \leq e_1 \mid e_0 = e_1$$

where e,  $e_0$  and  $e_1$  are strength expressions.

Now the first order assertions of our free logic are:

$$A ::= prel \mid srel \mid tt \mid ff \mid A \wedge A \mid A \vee A \mid A \rightarrow A \mid \exists x.A \mid \forall x.A$$

with atoms which are point and strength relations. The full semantics and proof system can be seen in the appendix (for the moment ignore the second order assertions and rules). Notable, special to a free logic, are the quantifier rules which must take account of existence and the rule (refl) the axiom for existence—the equality  $\alpha = \alpha$  only holds of an existing point  $\alpha$ . The paper [S] gives an excellent discussion of the axioms and rules.

**5.1 Theorem.** A first-order assertion is provable using the proof system in the appendix iff it is satisfied by all static configurations.

Proof. The proof is omitted. Unfortunately, I do not know an adequate reference for a completeness result in the form we want it, though completeness can be proved rather indirectly from results in [FS] and [Gr]. More direct proofs can be got by following the lines of Henkin's completeness proof for the predicate calculus.

It is as well to get a basic fact about strength relations out of the way. It will be useful to observe that any strength relation can be reduced to ones of a special form. described in the following.

**5.2 Proposition.** Let R be a strength relation. There is a propositional assertion A which includes strength assertions solely of the form  $S\pi = s$  such that  $\vdash R \leftrightarrow A$ .

Proof.

By structural induction,

$$- Ee \leftrightarrow M_{\pi \ in \ e} E\pi$$

for any strength expression e, where  $\pi$  ranges over the variables or points mentioned in e. This establishes the proposition for strength relations of the form Ee.

By structural induction,

$$\vdash Ee \leftrightarrow \bigvee_{s \in S} e = s$$

for any strength expression e. It follows from the axioms that

$$\vdash e_{0} \cdot e_{1} = s \leftrightarrow \bigvee_{s_{0}, s_{1} \in S} (e_{0} = s_{0} \land e_{1} = s_{1} \land s_{0} \cdot s_{1} = s)

\vdash e_{0} + e_{1} = s \leftrightarrow \bigvee_{s_{0}, s_{1} \in S} (e_{0} = s_{0} \land e_{1} = s_{1} \land s_{0} + s_{1} = s)

\vdash e_{0} \leq e_{1} \leftrightarrow \bigvee_{s_{0}, s_{1} \in S} (e_{0} = s_{0} \land e_{1} = s_{1} \land s_{0} \leq s_{1})

\vdash e_{0} = e_{1} \leftrightarrow \bigvee_{s_{0}, s_{1} \in S} (e_{0} = s_{0} \land e_{1} = s_{1} \land s_{0} = s_{1}).$$

Whence, by structural induction on expressions, any strength relation of the form  $e_0 \le e_1$  or  $e_0 = e_1$  is provably equivalent to a propositional assertion of the required form.

We are still left with the major problem of how to incorporate rules for reasoning about circuit terms in the logic. As mentioned we can include them in the logic, treating them much the same way as assertions. They are built-up using restrictions  $\lceil \Lambda \rceil$  and composition • from atoms like  $Pow \alpha$  and  $ntran(\alpha, \beta, \gamma)$ . It is a simple matter to incorporate atoms. For example, the rules (L.10) include an elimination rule of the form

$$(Pow \ E) \qquad Pow \ \alpha \vdash S\alpha = \infty \land h\alpha \land \neg l\alpha \land \forall x.x = \alpha$$

whose role is to replace proving a property of a power source  $Pow\ \alpha$  to proving a consequence of an assertion expressing its behaviour. But how are we to treat compound terms? Our approach is to associate modal operations, analogous to weakest liberal preconditions, with the operators  $\lceil \Lambda$  and  $\bullet$ . This line was inspired by the general treatment in  $\lceil \Lambda \rceil$ , though, of course, their specific use in the semantics of imperative programming language is well known, largely due to  $\lceil D \rceil$ . We also extend the logic to include second—order quantifiers, to obtain the following syntactic category of second—order assertions:

$$A ::= prel \mid srel \mid tt \mid ff \mid A \land A \mid A \lor A \mid A \rightarrow A \mid \exists x.A \mid \forall x.A \mid \{x : A\}\pi \mid P\pi \mid \exists P.A \mid \forall P.A \mid$$

Though the reason for this will not become clear until we deal with the preconditions for composition.

The treatment of the restriction operator  $\lceil \Lambda \rceil$ , for a finite subset  $\Lambda$  of  $\Pi$ , is easier to explain first. The use of preconditions arises naturally from the requirement that the proof system be compositional. The requirement of compositionality begs the question:

What has to be true of a circuit c in order to be guaranteed that  $c \cap \Lambda$  satisfies an assertion A?

And this question amounts to:

What must be true of a static configuration  $\sigma$  so that if  $\sigma \upharpoonright \Lambda$  is defined then  $\sigma \upharpoonright \Lambda$  satisfies A?

Rather tautologously, we can answer that  $\sigma$  must satisfy the  $\Lambda$ -precondition of A, written  $^{\Lambda}A$ , which has the denotation

$$\llbracket^{\Lambda} A \rrbracket = \{ \sigma \mid \sigma \lceil \Lambda \downarrow \Rightarrow \sigma \lceil \Lambda \models A \}.$$

We might instead of  $^{\Lambda}A$  write  $[\![\Lambda]A$  because  $[\![^{\Lambda}A]\!]$  could have been written equally well as

$$\{\sigma \mid \forall \sigma'. \ \sigma[\Lambda = \sigma' \Rightarrow \sigma' \models A\},\$$

making the precondition look even more like a modal operator of the kind used in dynamic logic [Ha]. This precondition is analogous to weakest liberal preconditions because if  $\sigma[\Lambda]$  is undefined then  $\sigma$  satisfies  $\Lambda$ . We could have worked instead with the analogue of weakest precondition. We temporarily introduce it as  $\langle \Lambda \rangle A$  with the meaning

$$\llbracket \langle \lceil \Lambda \rangle A \rrbracket = \{ \sigma \mid \exists \sigma'. \ \sigma \lceil \Lambda = \sigma' \ \& \ \sigma' \models A \},\$$

but do not make any further use of it. It turns out to be definable in terms of  $^{\Lambda}A$ , and is not quite as directly useful. For  $^{\Lambda}A$  we have the following fact:

#### 5.3 Proposition.

Let c be a circuit term and A a second-order assertion. Then

$$c \lceil \Lambda \models A \text{ iff } c \models^{\Lambda} A.$$

Proof.

$$c\lceil \Lambda \models A \text{ iff } \llbracket c\lceil \Lambda \rrbracket \subseteq \llbracket A \rrbracket$$

$$\text{iff } \forall \sigma'. \ \sigma' \models c\lceil \Lambda \Rightarrow \sigma' \models A$$

$$\text{iff } \forall \sigma. \ (\sigma \models c \& \sigma\lceil \Lambda \downarrow) \Rightarrow \sigma\lceil \Lambda \models A$$

$$\text{iff } \forall \sigma. \ \sigma \models c \Rightarrow (\sigma\lceil \Lambda \downarrow \Rightarrow \sigma\lceil \Lambda \models A)$$

$$\text{iff } \forall \sigma. \ \sigma \models c \Rightarrow \sigma \models^{\Lambda} A$$

$$\text{iff } \llbracket c \rrbracket \subseteq \llbracket^{\Lambda} A \rrbracket$$

$$\text{iff } c \models^{\Lambda} A.$$

We extend the second-order assertions by preconditions and call the resulting syntactic category simply assertions. Proposition 5.3 suggests an obvious elimination rule for preconditions:

$$\frac{c \vdash^{\Lambda} A}{c \lceil \Lambda \vdash A}$$

in which the semantic relation of satisfaction has been replaced by the syntactic one of entailment in a sequent calculus. Standing alone this proof rule would not get us very far. True we can eliminate an occurrence of the restriction operator, but only at the expense of introducing a precondition. Fortunately it is a purely mechanical process, captured mainly in the distribution laws for  $^{\Lambda}($ ), listed in L.6, to eliminate all occurrences of  $[\Lambda$ -preconditions; an assertion containing them can be proved equivalent to an assertion without any.

We explain the rules for  $^{\Lambda}($ ), leaving the detailed proofs of soundness to the reader. Regarding preconditions as modal operators suggests the introduction rule

$$\frac{\vdash A}{\vdash {}^{\Lambda}A}$$

familiar from proof systems with modal operators. The other introduction rule for such preconditions accompanies the fact that if  $\sigma[\Lambda]$  is undefined then  $\sigma \models {}^{\Lambda}A$ . Take

$$G \equiv orall x. \

eg \Lambda x

ightarrow [\operatorname{H} x

ightarrow h x \lor (\exists y : \Lambda. \ \operatorname{H} y \land y

ightharpoonup x)] \land [\operatorname{L} x

ightharpoonup l x \lor (\exists y : \Lambda. \ \operatorname{L} y \land y

ightharpoonup x)].$$

The assertion G expresses definedness in the sense that

$$\sigma = G \text{ iff } \sigma[\Lambda \downarrow .$$

The other introduction rule for preconditions is

$$\neg G \vdash {}^{\Lambda}A.$$

The remaining  $^{\Lambda}($ ) rules say how the operator distributes over logical operators. Their role is to enable preconditions to be pushed through and finally eliminated from assertions. Using them we can for instance derive the rule

$$\frac{\Gamma \vdash A}{^{\Lambda}\Gamma \vdash ^{\Lambda}A}$$

where by  ${}^{\Lambda}\Gamma$  we mean  $\{{}^{\Lambda}B \mid B \in \Gamma\}$ , for a finite set of assumptions  $\Gamma$ . From  $\Gamma \vdash A$  we derive  $\vdash \bigwedge \Gamma \to A$  and hence  $\vdash {}^{\Lambda}(\bigwedge \Gamma \to A)$ . Using the distribution rules we deduce  $G \vdash \bigwedge {}^{\Lambda}\Gamma \to {}^{\Lambda}A$ . This gives  $G, \bigwedge {}^{\Lambda}\Gamma \vdash {}^{\Lambda}A$  which combined with  $\neg G \vdash {}^{\Lambda}A$  yields  $\bigwedge {}^{\Lambda}\Gamma \vdash {}^{\Lambda}A$ , and finally  ${}^{\Lambda}\Gamma \vdash {}^{\Lambda}A$ . In particular using this we can for instance show  $\vdash {}^{\Lambda}A \leftrightarrow {}^{\Lambda}B$  if  $\vdash A \leftrightarrow B$ ; equivalent assertions have equivalent preconditions. This means that preconditions of strength relations can be replaced by preconditions of assertions of the form given in proposition 5.2 from which all preconditions can be eliminated using the distribution rules.

#### 5.4 Theorem.

: \\.

Let A be an assertion, which may include restriction preconditions. There is an assertion B, which does not contain any preconditions, such that  $\vdash A \leftrightarrow B$ .

Proof. By the remarks above, using the distribution laws, we obtain

$$G \vdash {}^{\Lambda}A \leftrightarrow C$$

where C contains no preconditions. But  $\neg G \vdash {}^{\Lambda}A$ . Therefore  $\vdash {}^{\Lambda}A \leftrightarrow (G \to C)$ , with  $B \equiv (G \to C)$  an assertion of the required form.

Proving c

cap A reduces to proving c

cap A which, by the metatheorem and modus ponens, reduces to proving c

cap B where B contains no preconditions—and this

can be done formally in the proof system. We have reduced the problem of proving an assertion A holds of  $c \mid \Lambda$  to proving an assertion B holds of c. We have achieved compositionality for restriction.

The term c may well contain compositions using  $\bullet$ . For our proof system to be compositional we must "decompose" the proof that an assertion A is satisfied by a composition  $c_0 \bullet c_1$  to proofs that assertions  $A_0$  and  $A_1$ , are satisfied by the components  $c_0$  and  $c_1$ , respectively. Problems like this have received a great deal of attention recently (see e.g. [deR, OH, St, W]) and our approach throws some light on the problem of obtaining compositional proof systems for parallel processes, and even suggests a general approach. Again the use of a modal operator plays a central role, this time associated with composition. Composition  $\bullet$  is a binary operator so the  $\bullet$ -precondition of an assertion A is satisfied by those pairs of static configurations  $(\sigma, \rho)$  whose composition  $\sigma \bullet \rho$ , when defined, satisfies A, i.e.

$$\llbracket {}^{\bullet}A \rrbracket = \{ (\sigma, \rho) \mid \sigma \bullet \rho \downarrow \Rightarrow \sigma \bullet \rho \models A \}.$$

Thus the assertion  ${}^{\bullet}A$  is of a different type than those we have encountered previously. It is satisfied by pairs of static configurations. To emphasise that it has a different type we call it, and other assertions satisfied by pairs of configurations, product assertions. It is useful to define another operator for forming atomic product assertions. For assertions A and B, take  $A \times B$  to be satisfied by those pairs  $(\sigma, \rho)$  where  $\sigma$  satisfies A and  $\rho$  satisfies B, i.e. so

$$\llbracket A \times B \rrbracket = \llbracket A \rrbracket \times \llbracket B \rrbracket.$$

The full syntactic category of product assertions is:

$$D ::= A \times B \mid {}^{\bullet}A \mid E\pi \mid \pi_0 = \pi_1$$

$$\text{tt} \mid \text{ff} \mid D_0 \wedge D_1 \mid D_0 \vee D_1 \mid D_0 \rightarrow D_1 \mid \exists x.D \mid \forall x.D \mid$$

$$\{x : D\}\pi \mid \exists P.D \mid \forall P.D$$

which includes the apparatus of first and second order free logic with equality.

We can treat circuit terms similarly, and with the obvious definition of |= between product assertions, obtain the following proposition relating the •-precondition to composition.

#### 5.5 Proposition.

Let co and co be circuit terms and A an assertion. Then

$$c_0 \bullet c_1 \models A \text{ iff } c_0 \times c_1 \models {}^{\bullet}A.$$

Proof.

$$c_{0} \bullet c_{1} \models A \text{ iff } \llbracket c_{0} \bullet c_{1} \rrbracket \subseteq \llbracket A \rrbracket$$

$$\text{iff } \forall \sigma'. \ \sigma' \models c_{0} \bullet c_{1} \Rightarrow \sigma' \models A$$

$$\text{iff } \forall \sigma, \rho. \ (\sigma \models c_{0} \& \ \rho \models c_{1} \& \ \sigma \bullet \rho \downarrow) \Rightarrow \sigma \bullet \rho \models A$$

$$\text{iff } \forall \sigma, \rho. \ \sigma \models c_{0} \& \ \rho \models c_{1} \Rightarrow (\sigma \bullet \rho \downarrow \Rightarrow \sigma \bullet \rho \models A)$$

$$\text{iff } \forall \sigma, \rho. \ (\sigma, \rho) \models c_{0} \times c_{1} \Rightarrow (\sigma, \rho) \models {}^{\bullet}A$$

$$\text{iff } \llbracket c_{0} \times c_{1} \rrbracket \subseteq \llbracket {}^{\bullet}A \rrbracket$$

$$\text{iff } c_{0} \times c_{1} \models {}^{\bullet}A. \quad \blacksquare$$

The proposition asserts the soundness of the elimination rule for composition:

$$\frac{c_0 \times c_1 \vdash {}^{\bullet}A}{c_0 \bullet c_1 \vdash A}$$

We want the proof of  $c_0 \times c_1 \models {}^{\bullet}A$  to "factor" into proving

$$c_0 \models A_0 \& c_1 \models A_1 \& A_0 \times A_1 \models {}^{\bullet}A.$$

The key to a compositional proof system for  $\bullet$  is to obtain such assertions so that we can prove formally the relation between assertions, that  $A_0 \times A_1 \vdash {}^{\bullet}A$ . Then we have reduced proving a property holds of a composition  $c_0 \bullet c_1$  to proving properties hold of its components  $c_0$  and  $c_1$ : If there are such assertions then by the rules  $(\times \vdash)$  and (tran), and provided  $c_0 \vdash A_0$  and  $c_1 \vdash A_1$ , we can deduce  $c_0 \times c_1 \vdash {}^{\bullet}A$  and so  $c_0 \bullet c_1 \vdash A$ . Obtaining suitable assertions  $A_0$  and  $A_1$  is quite involved.

The rules for  $\bullet$ -preconditions are like those for  $\lceil \Lambda$ -preconditions and are presented in L.9. There are two introduction rules, one of which makes use of a definedness assertion D, with

$$D \equiv \forall x. \ ([Ex imes t] \land [tt imes Ex])

ightharpoonup ([Hx imes tt] \leftrightarrow [tt imes Hx] \land [Lx imes tt] \leftrightarrow [tt imes Lx] \land \ igwedge_{s \in S} [Sx = s imes Sx = s]),$$

so  $(\sigma, \rho) \models D$  iff  $\sigma \bullet \rho \downarrow$ . This is where the cost of making assertions second-order paysoff. Because we can quantify over subsets (or properties), we can reduce  ${}^{\bullet}A$  to a provably equivalent product assertion which contains no preconditions. The quantification over sets is used to express the fact that the flow relation in a composition  $\sigma \bullet \rho$ , assumed defined, is the transitive closure of the flow relations contributed by the components  $\sigma$  and  $\rho$ . This is the role of axiom  $(d^{\bullet} \leadsto)$ . Suppose  $\sigma \bullet \rho$  is defined. Then  $(\sigma, \rho) \models (\alpha \leadsto \beta)$  means simply that  $\sigma \bullet \rho \models \alpha \leadsto \beta$  for  $\alpha, \beta \in \operatorname{sort}(\sigma \bullet \rho)$ . Let  $\Lambda \subseteq \operatorname{sort}(\sigma \bullet \rho)$ . Note we can represent the set  $\Lambda$  as the term  $\Lambda$  which is  $\{x : \bigvee_{\lambda \in \Lambda} x = \lambda\}$  in the logic. Say  $\Lambda$  is closed, with respect to  $\sigma, \rho$ , if

$$\sigma \bullet \rho \models \Lambda \gamma \ \& \ (\sigma \models \gamma \leadsto \delta \ \text{or} \ \rho \models \gamma \leadsto \delta) \Rightarrow \sigma \bullet \rho \models \Lambda \delta$$

for all  $\gamma, \delta \in \text{sort}(\sigma \bullet \rho)$ . Now, the flow relation in  $\sigma \bullet \rho$  is characterised as being the transitive closure of the flow relations of the components, and this is expressed by the property that

$$\Lambda \alpha \& \Lambda \text{ is closed } \Rightarrow \Lambda \beta$$

for all  $\alpha, \beta \in \text{sort}(\sigma \bullet \rho)$  and for any  $\Lambda$ . This gives the gist of axiom  $(d^{\bullet} \rightsquigarrow)$ . Notice it depends on quantifying over subsets. Once we have gone second-order, the distribution axioms for  $\bullet$ () enable us to eliminate occurrences of  $\bullet$ -preconditions from product assertions.

#### 5.6 Theorem.

Let A be a product assertion which may include composition preconditions. There is a product assertion B, which does not contain any preconditions such that  $\vdash A \leftrightarrow B$ .

Proof. The proof follows the same lines as for restriction preconditions.

But, of course, this was at the expense of making our logic second-order and it is well-known that there is no complete effective axiomatisation of second-order logic. Fortunately we can use the fact that circuits are finite to get around this difficulty. In contexts where it is assumed that all points lie within some finite set we can reduce second-order assertions to provably equivalent first-order or even propositional assertions. (An assertion is propositional if it contains no quantifiers or preconditions.)

It is easy to define the sort of circuit term by structural induction:

$$\operatorname{sort}(Pow \ \alpha) = \operatorname{sort}(Gnd \ \alpha) = \{\alpha\}$$

$\operatorname{sort}(res_g(\alpha, \beta)) = \{\alpha, \beta\}$

$\operatorname{sort}(ntran(\alpha, \beta, \gamma)) = \operatorname{sort}(ptran(\alpha, \beta, \gamma)) = \{\alpha, \beta, \gamma\}$

$\operatorname{sort}(c \bullet d) = \operatorname{sort}(c) \cup \operatorname{sort}(d)$

$\operatorname{sort}(c[\Lambda) = \operatorname{sort}(c) \cap \Lambda.$

In the logic, the fact that a circuit term c has sort  $\Lambda$ , a finite set, is expressed by

$$c \models \bigwedge_{\lambda \in \Lambda} E\lambda \wedge \forall x.\Lambda x$$

where  $\Lambda x$  abbreviates  $\{y: \bigvee_{\lambda \in \Lambda} y = \lambda\} x$  and so is equivalent to  $\bigvee_{\lambda \in \Lambda} x = \lambda$ . This can be proved in the formal system, though all we need to show completeness is the following.

#### 5.7 Proposition.

- (i) Let c be a circuit term of sort  $\Lambda$ . Then  $c \vdash \forall x. \Lambda x$ .

- (ii) Let  $c_0, c_1$  be circuit terms of sort  $\Lambda_0$  and  $\Lambda_1$  respectively. Then  $c_0 \times c_1 \vdash \forall x. (\Lambda_0 \cup \Lambda_1)x.$

*Proof.* The proof of (i) is by structural induction on circuit terms.

For basic components like transistors the sorts are specified in their associated assertions so for a basic component c we have  $c \vdash \forall x$ . (sort(c))x.