Number 955

# Capability memory protection for embedded systems

Hongyan Xia

February 2021

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

#### © 2021 Hongyan Xia

This technical report is based on a dissertation submitted May 2019 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Hughes Hall.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

#### **Declaration**

This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration except as declared in the Preface and specified in the text. It is not substantially the same as any that I have submitted, or, is being concurrently submitted for a degree or diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. I further state that no substantial part of my dissertation has already been submitted, or, is being concurrently submitted for any such degree, diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. It does not exceed the prescribed limit of 60,000 words.

Hongyan Xia

#### Capability Memory Protection for Embedded Systems

Hongyan Xia

#### Abstract:

This dissertation explores the use of capability security hardware and software in real-time and latency-sensitive embedded systems, to address existing memory safety and task isolation problems as well as providing new means to design a secure and scalable real-time system. In addition, this dissertation looks into how practical and high-performance temporal memory safety can be achieved under a capability architecture.

State-of-the-art memory protection schemes for embedded systems typically present limited and inflexible solutions to memory protection and isolation, and fail to scale as embedded devices become more capable and ubiquitous. I investigate whether a capability architecture is able to provide new angles to address memory safety issues in an embedded scenario. Previous CHERI capability research focuses on 64-bit architectures in UNIX operating systems, which does not translate to typical 32-bit embedded processors with low-latency and real-time requirements. I propose and implement the CHERI CC-64 encoding and the CHERI-64 coprocessor to construct a feasible capability-enabled 32-bit CPU. In addition, I implement a real-time kernel for embedded systems atop CHERI-64. On this hardware and software platform, I focus on exploring scalable task isolation and fine-grained memory protection enabled by capabilities in a single flat physical address space, which are otherwise difficult or impossible to achieve via state-of-the-art approaches. Later, I present the evaluation of the hardware implementation and the software run-time overhead and real-time performance.

Even with capability support, CHERI-64 as well as other CHERI processors still expose major attack surfaces through temporal vulnerabilities like use-after-free. A naïve approach that sweeps memory to invalidate stale capabilities is inefficient and incurs significant cycle overhead and DRAM traffic. To make sweeping revocation feasible, I introduce new architectural mechanisms and micro-architectural optimisations to substantially reduce the cost of memory sweeping and capability revocation. Another factor of the cost is the frequency of memory sweeping. I explore tradeoffs of memory allocator designs that use quarantine buffers and shadow space tags to prevent frequent unnecessary sweeping. The evaluation shows that the optimisations and new allocator designs reduce the cost of capability sweeping revocation by orders of magnitude, making it already practical for most applications to adopt temporal safety under CHERI.

#### Acknowledgements

First, I would like to thank my supervisor, Professor Simon Moore, for his patience, technical expertise and great guidance throughout my PhD. I never imagined that I could accomplish what I have actually achieved in the past years. Looking back, I am sincerely grateful to Simon whose supervision makes the entire process exciting, rewarding, challenging, and most of all, enjoyable.

I would also like to thank Robert Watson for his insights in software, kernels and operating systems. With his supervision, I have been exposed to the art of software-hardware co-design, which successfully transformed some of my work from what I could only call engineering effort, into comprehensive and more sophisticated research topics.

I am also grateful to Jonathan Woodruff, who shows great wisdom in CPU architecture and design. He also shows unparalleled patience compared with most human beings I have seen. I often feel guilty that a lot of his time was spent on sitting beside me helping me understand CHERI concepts and CPU micro-architecture instead of having biscuits and tea or on other meaningful activities. Hopefully, I am now repaying his kindness with my own contributions to the project.

I also need to thank Alexandre Joannou for his knowledge and help on various fronts and his work style. Particularly, he is an interesting colleague to work with, and his obsession with high-level abstractions often sparks long and meaningful discussions. Sometimes his design philosophy is something I would be thankful for several months later when I see the code evolve into a modular, configurable entity instead of being filled with ugly hacks and hardcoded values. Working with him in the past years has always been a pleasure.

I need to thank other members in the team, including David Chisnall, Robert Norton, Theo Markettos, Robert Kovacsics, Marno van der Maas, Lucian Paul-Trifu, Nathaniel Filardo, Lawrence Esswood, Peter Rugg and so forth, for all the help and collaboration in multiple areas and projects. It always reminds me of how wonderful it is to work within an active, open-minded, innovative and motivated research team.

Outside my research, I have been enjoying my time with Yimai Fang, Fengyuan Shi, Ruoyu Zhou, Menglin Xia, Dongwei Wang, Jiaming Liang, Meng Zhang, Zheng Yuan... in countless punting trips, excursions, Nintendo Switch nights, festival celebrations, formal hall dinners, which gave me some of the best memories I have had.

I thank my parents for their support for my PhD and for everything. Frankly, it is not possible to express my eternal gratitude here with just words. What I do know is that whenever I am lost, you are there, strong and steady. Wish you guys health, sincerely.

Finally, I must thank Xizi Wei for just being in my life. You are a food innovator, a good listener, a healthy lifestyle enforcer, a cat lover, a Machine Learning expert, a perfectionist, a bookworm, and above all, a wonderful human being. I hope I can achieve this many positive labels in your mind, and I will try.

# Contents

| Li | List of Figures 13 List of Tables 15 |                                                         |    |  |  |

|----|--------------------------------------|---------------------------------------------------------|----|--|--|

| Li |                                      |                                                         |    |  |  |

| 1  | Inti                                 | roduction                                               | 17 |  |  |

|    | 1.1                                  | Contributions                                           | 18 |  |  |

|    | 1.2                                  | Publications                                            | 19 |  |  |

|    | 1.3                                  | Dissertation overview                                   | 20 |  |  |

| 2  | Bac                                  | kground                                                 | 21 |  |  |

|    | 2.1                                  | Introduction to embedded systems                        | 21 |  |  |

|    | 2.2                                  | The need for memory safety                              | 23 |  |  |

|    | 2.3                                  | State-of-the-art memory protection                      | 24 |  |  |

|    | 2.4                                  | Case studies                                            | 27 |  |  |

|    | 2.5                                  | Requirements                                            | 30 |  |  |

|    | 2.6                                  | Introduction of capability models and CHERI             |    |  |  |

|    | 2.7                                  | Summary                                                 | 40 |  |  |

| 3  | A 6                                  | 4-bit compressed capability scheme for embedded systems | 41 |  |  |

| 3.1  | CHERI for a 32-bit machine                                                                                                                                                                                                                               | 1                                         |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 3.2  | Existing capability encodings       42         3.2.1 CHERI-256       42         3.2.2 M-Machine       42         3.2.3 Low-fat       43         3.2.4 Project Aries       47         3.2.5 CHERI-128 Candidate 1       48         3.2.6 Summary       48 | $\frac{3}{3}$ $\frac{3}{5}$ $\frac{8}{8}$ |

| 3.3  | The CHERI Concentrate (CC) and 64-bit capability encoding                                                                                                                                                                                                | 9<br>5<br>8                               |

| 3.4  | Summary of compressed capability schemes                                                                                                                                                                                                                 | 2                                         |

| 3.5  | A CC-64 hardware implementation                                                                                                                                                                                                                          | 3<br>5                                    |

| 3.6  | Summary                                                                                                                                                                                                                                                  | 7                                         |

| 4 Ch | eriRTOS 69                                                                                                                                                                                                                                               | 9                                         |

| 4.1  | A CHERI-based RTOS                                                                                                                                                                                                                                       | 9                                         |

| 4.2  | Real-time operating systems                                                                                                                                                                                                                              | 0                                         |

| 4.3  | Prerequisites       73         4.3.1 The MIPS-n32 ABI       73         4.3.2 Enabling CHERI-64 in Clang/LLVM       73         4.3.3 A baseline RTOS       73                                                                                             | 2<br>3                                    |

| 4.4  | CheriRTOS       74         4.4.1 Overview       75         4.4.2 OType space       76         4.4.3 Non-PIC dynamic task loading       77         4.4.4 Context switch       77                                                                          | 5<br>6<br>7                               |

|   |     | 4.4.5  | CCallFast                                                          |

|---|-----|--------|--------------------------------------------------------------------|

|   |     | 4.4.6  | Return and real-time guarantees                                    |

|   |     | 4.4.7  | Secure centralised heap management                                 |

|   | 4.5 | Evalua | ation                                                              |

|   |     | 4.5.1  | The MiBench benchmark suite                                        |

|   |     | 4.5.2  | Non-PIC and compartmentalisation                                   |

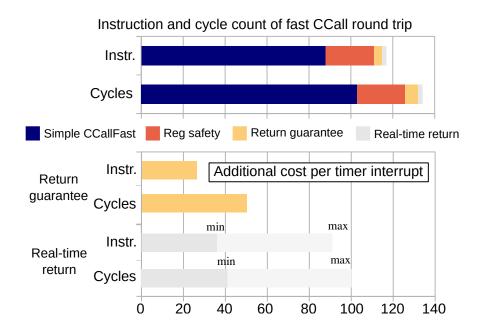

|   |     | 4.5.3  | Fast and direct domain crossing                                    |

|   |     | 4.5.4  | Register safety, return and real-time guarantees 91                |

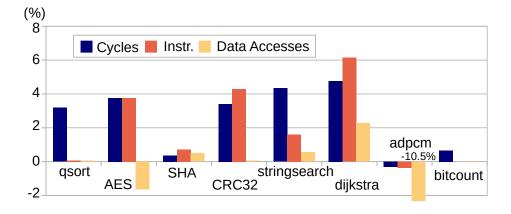

|   |     | 4.5.5  | Overall system performance                                         |

|   | 4.6 | Cheril | RTOS vs. state-of-the-art                                          |

|   | 4.7 | Summ   | nary                                                               |

|   |     | 4.7.1  | The problem of temporal memory safety                              |

| 5 | Ten | nporal | safety under the CHERI architecture 97                             |

|   | 5.1 | Backg  | round                                                              |

|   | 5.2 | Oppoi  | tunities of CHERI temporal safety                                  |

|   |     | 5.2.1  | Deterministic temporal memory safety                               |

|   |     | 5.2.2  | Spatial and temporal safety combined                               |

|   |     | 5.2.3  | Possible but inefficient                                           |

|   | 5.3 | Optim  | nising for efficient sweeping revocation                           |

|   | 5.4 | Archit | sectural/microarchitectural proposals and implementations for fast |

|   |     | sweep  | ing                                                                |

|   |     | 5.4.1  | CLoadTags                                                          |

|   |     | 5.4.2  | Page table cap-dirty bit                                           |

|   |     | 5.4.3  | Core dump study                                                    |

|   |     | 5.4.4  | Performance of fast sweeping                                       |

|   |     | 5.4.5  | Pointer concentration                                              |

|   | 5.5 | New a  | allocator design for reduced sweeping frequency                    |

|   |     | 5.5.1  | Brief overview of dlmalloc()                                       |

|   |     | 5.5.2  | Implementation of dlmalloc_nonreuse()                              |

|   |     | 5.5.3  | Experimental setup                                                 |

|   |     | 5.5.4  | Overall overheads of dlmalloc_nonreuse()                           |

|              |       | 5.5.5<br>5.5.6           | Breakdown of overheads                                                                                                                                                                                                                                                                         |                            |                                                    |

|--------------|-------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------|

|              | 5.6   | Altern<br>5.6.1<br>5.6.2 | Subset testing revocation                                                                                                                                                                                                                                                                      | 12                         | 22<br>22                                           |

|              | 5.7   | Summ                     | ary                                                                                                                                                                                                                                                                                            | 12                         | 23                                                 |

| 6            | Con   | clusio                   | n                                                                                                                                                                                                                                                                                              | 12                         | 25                                                 |

|              | 6.1   | 6.1.1<br>6.1.2<br>6.1.3  | A capability format for 32-bit cores CheriRTOS CHERI temporal memory safety  work CHERI-64 CheriRTOS CHERI temporal memory safety  CHERI temporal memory safety  Adopting capability protection in future embedded devices Extrapolating to non-CHERI systems  Adversarial security evaluation | 12 12 12 12 12 12 12 12 13 | 26<br>26<br>27<br>28<br>28<br>28<br>28<br>29<br>30 |

| $\mathbf{A}$ | CH    | ERI C                    | oncentrate bounds and region arithmetic                                                                                                                                                                                                                                                        | 13                         | 31                                                 |

|              | A.1   | Encod                    | ing the bounds                                                                                                                                                                                                                                                                                 | 13                         | 31                                                 |

|              | A.2   | Decod                    | ing the bounds                                                                                                                                                                                                                                                                                 | 13                         | 33                                                 |

|              | A.3   | Fast re                  | epresentable limit checking                                                                                                                                                                                                                                                                    | 13                         | 36                                                 |

| Re           | efere | nces                     |                                                                                                                                                                                                                                                                                                | 13                         | 39                                                 |

# List of Figures

| 2.1  | Memory accesses controlled by MPU                                                          | 25 |

|------|--------------------------------------------------------------------------------------------|----|

| 2.2  | Escalations towards a successful control flow hijack. size (brown) and                     |    |

|      | pointer to next/unused (green) are allocator metadata fields. data                         |    |

|      | (blue) is the actual allocated memory. Red indicates contaminated fields. $\boldsymbol{.}$ | 27 |

| 2.3  | The capability coprocessor                                                                 | 36 |

| 2.4  | 256-bit memory representation of a capability                                              | 38 |

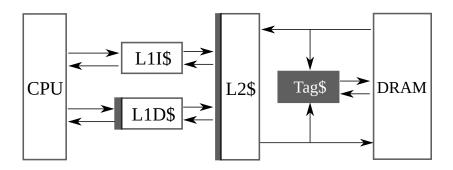

| 2.5  | Memory hierarchy and the tag cache                                                         | 39 |

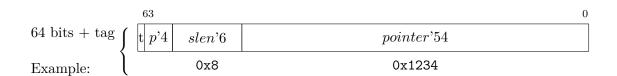

| 3.1  | M-Machine capability encoding with example values                                          | 43 |

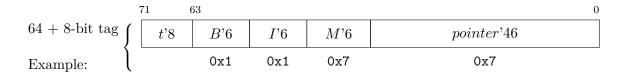

| 3.2  | Low-fat capability encoding with example values                                            | 45 |

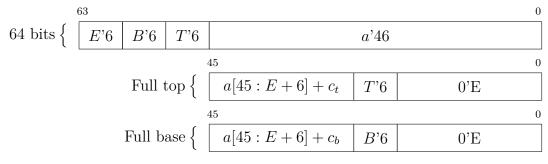

| 3.3  | Low-fat bounds decompression                                                               | 46 |

| 3.4  | Aries capability encoding                                                                  | 48 |

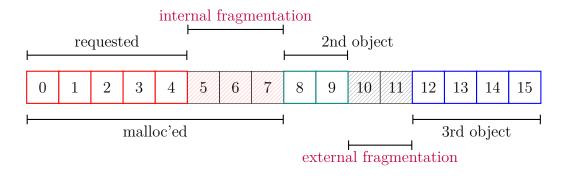

| 3.5  | Internal vs. external fragmentation                                                        | 50 |

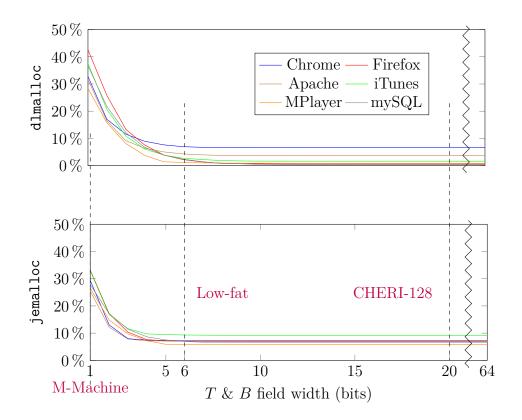

| 3.6  | Heap internal fragmentation                                                                | 53 |

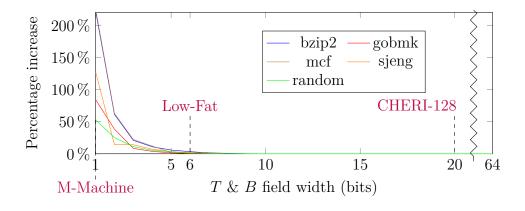

| 3.7  | Percentage increase in peak size of total stack allocations (SPEC CPU                      |    |

|      | 2006 experimental builds)                                                                  | 53 |

| 3.8  | Improved Low-fat Encoding with Embedded Exponent and Implied $T_8$                         | 57 |

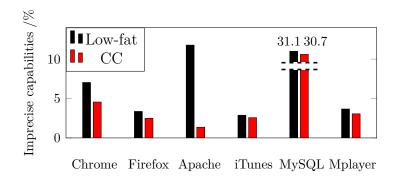

| 3.9  | The percentage of allocations that cannot be precisely represented in a                    |    |

|      | capability. Lower is better                                                                | 58 |

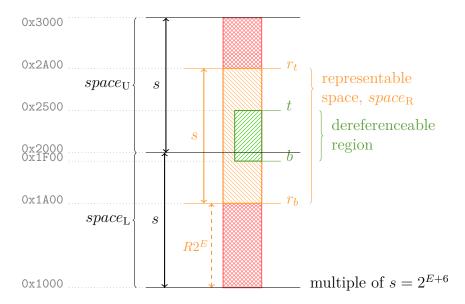

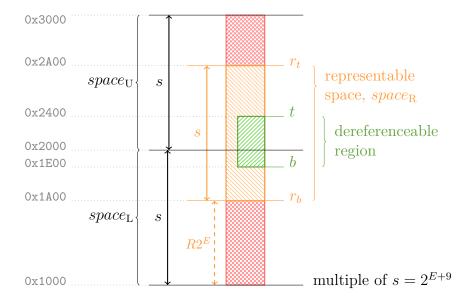

| 3.10 | CHERI Concentrate bounds in an address space. Addresses increase up-                       |    |

|      | wards. The example shows a $0x600\text{-byte}$ object based at $0x1F00.\ \dots\ \dots$     | 60 |

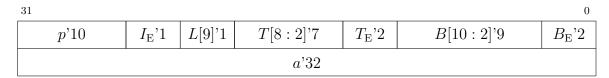

| 3.11 | 64-bit CHERI Concentrate                                                                   | 62 |

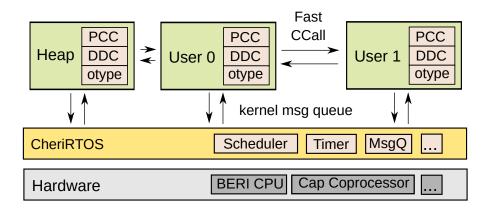

| 4.1  | Overall structure                                                                          | 75 |

| 4.2  | Example of memory access instructions under CHERI. "\$" denotes reg-                       |    |

|      | isters. Loading a word at address $\$s0 + 8$ (relative to the base of the                  |    |

|      | capability) into \$t0, either implicitly or via an explicit capability register.           | 76 |

| 4.3  | Increment two variables at 0x800 and 0x900. Binary compiled for 0x0 now                    |    |

|      | loaded at 0x11000. Red indicates patching                                                  | 78 |

| 4.4  | CCallFast sequence                                                                         | 79 |

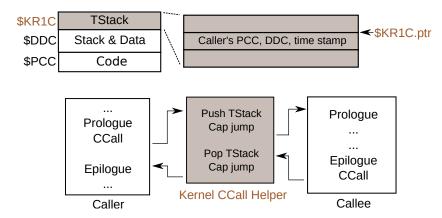

| 4.5  | Trusted stack and CCallFast round trip. Dark indicates kernel-only ob-                     |    |

|      | jects. The pointer field of \$KR1C points to the top of the trusted stack                  | 83 |

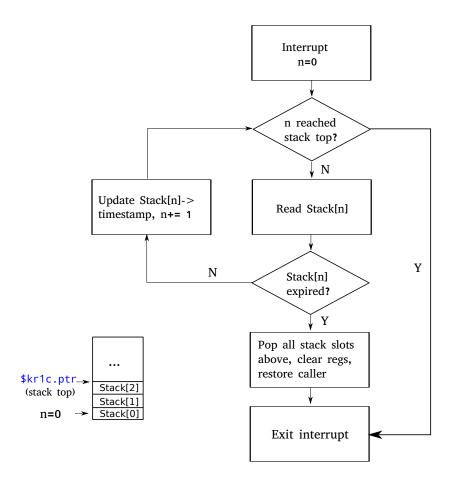

| 4.6  | Interrupt routine to check for expired CCalls                                                |

|------|----------------------------------------------------------------------------------------------|

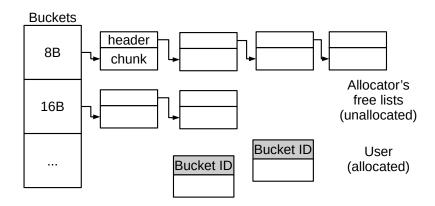

| 4.7  | Memory allocator structure (gray boxes indicate that the bucket ID is                        |

|      | sealed inside a sealed capability)                                                           |

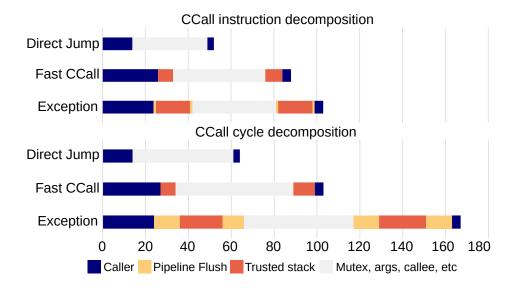

| 4.8  | Instruction and cycle counts for a round trip: direct jump vs. capability                    |

|      | jump (fast CCall) vs. exception based CCalls                                                 |

| 4.9  | Overhead of different protection levels                                                      |

| 4.10 | Overall overhead across benchmarks                                                           |

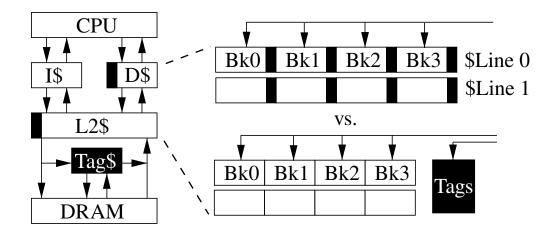

| 5.1  | Tags in the CHERI memory hierarchy and the refactoring of caches 103                         |

| 5.2  | CLoad<br>Tags. Assuming 128-byte cache lines and 64-bit capabilities.<br>$104$               |

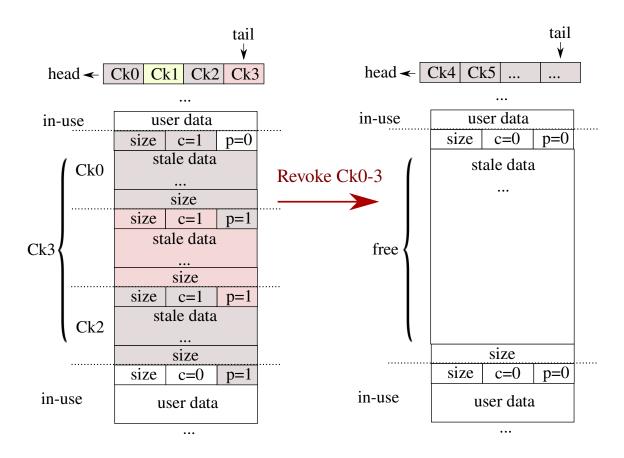

| 5.3  | ${f c}$ and ${f p}$ represent ${f cdirty}$ and ${f pdrity}$ bits. At the end Ck0 and Ck2 are |

|      | unlinked from the queue and the newly freed chunk (in the middle) will                       |

|      | be coalesced with Ck0 and Ck2 into Ck3 and inserted at the tail of the                       |

|      | queue. After a revocation, Ck3 is returned to the free lists to be reused $114$              |

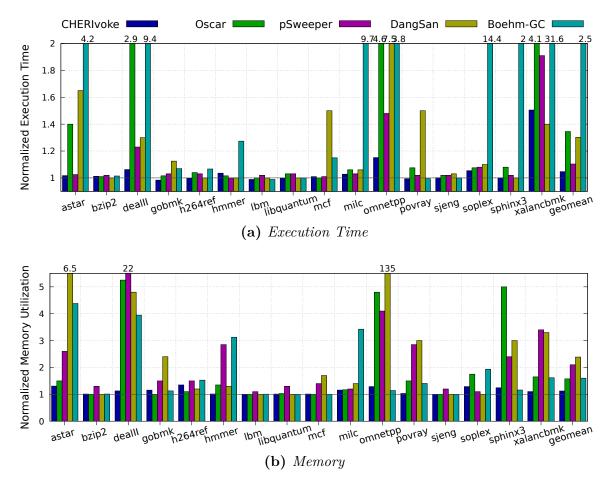

| 5.4  | Overheads compared with results reported by other state-of-the-art tech-                     |

|      | niques. CHERIvoke represents the new dlmalloc                                                |

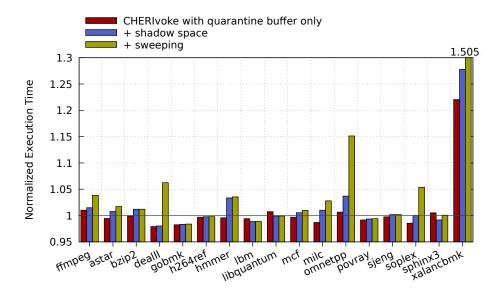

| 5.5  | Run-time overhead decomposition for the constituent parts, with the de-                      |

|      | fault 25% heap overhead                                                                      |

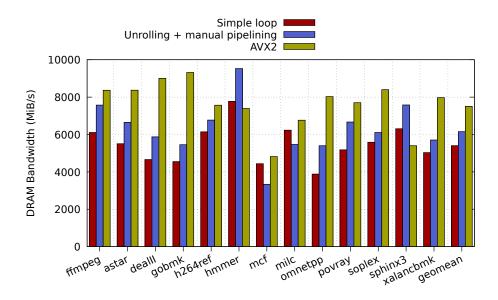

| 5.6  | Memory bandwidth achieved for the sweep loop with different optimisa-                        |

|      | tions. The system's full bandwidth is $19405 \text{MiB/s}.$                                  |

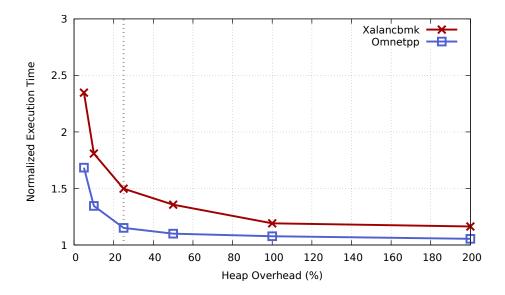

| 5.7  | Normalised execution time for the two workloads with highest overheads,                      |

|      | at varying heap overhead. Default setup shown by dotted line                                 |

| A.1  | CHERI Concentrate bounds in an address space. Addresses increase up-                         |

|      | wards. To the left are example values for a $0x600$ -byte object based at                    |

|      | 0x1E00                                                                                       |

# List of Tables

| 2.1        | Example CHERI instruction-set extensions                                                                                                                                                                                                      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1<br>3.2 | Comparison of capability encodings                                                                                                                                                                                                            |

| 4.1<br>4.2 | MiBench: non-PIC vs. PIC (all numbers in billions)                                                                                                                                                                                            |

| 5.1        | Sweeping performance of sample applications. The percentages in the last four columns indicate relative <b>reduction</b> compared with the baseline.  Negative means <b>overhead</b> instead of reduction. Tildes indicate negligible numbers |

|            | Humbers                                                                                                                                                                                                                                       |

# Chapter 1

### Introduction

Today, embedded systems are deployed ubiquitously among various sectors, including automotive, medical, robotics and avionics. As these systems become increasingly connected, their attack surfaces increase dramatically to a much more sophisticated level, invalidating previous assumptions that such devices are susceptible only to direct physical attack. Also, the end of Moore's Law for single core and the continuing increase in transistor count drive manufacturers to pair large performance cores with smaller dedicated embedded cores for I/O and other peripherals on System-on-Chips (SoCs). As a result, securing the system without securing the embedded side of the chip still exposes attack vectors. For example, the Broadcom WiFi stack exploit enables the attacker to hijack the control flow via the Wi-Fi chip in nearly all iPhones and many Android phones [5]; the CAN bus in self-driving cars can be updated with malicious firmware to remotely control its motion by an attacker driving in parallel [14]. Even though many published vulnerabilities are well-known and well understood, it remains a challenge to build a comprehensive memory security framework around deeply embedded processors. Such systems with very small CPU cores typically impose tight constraints on the extra hardware logic, memory overhead and additional latency of any protection mechanisms deployed. Moreover, the lack of virtual memory only exacerbates the problem of memory protection, since all tasks reside within a single physical address space without isolation.

In this thesis, I work on many fronts of Capability Hardware Enhanced RISC Instructions (CHERI), a capability architecture developed by the University of Cambridge and SRI International. The CHERI Instruction Set Architecture (ISA) provides

direct processor support for fine-grained memory protection and scalable compartmentalisation on top of paged virtual memory. More importantly, CHERI hardware and software support for fast domain crossing has been proven to be much more efficient than conventional process-based isolation [67]. I hypothesise that the CHERI platform provides a novel angle towards low-overhead and scalable memory security for embedded devices, since the fine-grained memory protection, the scalable domain isolation and fast domain crossing within a flat address space are the desired properties in an embedded CPU, none of which is achievable via state-of-the-art solutions. However, challenges remain since existing CHERI implementations focus on a UNIX-based operating system (FreeBSD) on 64-bit processors and optimise for performance, whereas embedded processors are typically 32-bit, operate on bare-metal or on a Real-Time Operating System (RTOS) and optimise for low latency and real-time guarantees. Therefore, my research investigates how CHERI capabilities can be adapted to 32-bit embedded CPUs without violating the real-time constraints, and how a capabilitybased RTOS offers fine-grained memory protection and efficient, scalable task isolation/communication in a physical address space.

Further, I look into the possibility of practical temporal memory safety (e.g., against use-after-free attacks) under CHERI. I hypothesise that the separation between pointers and data and capability unforgeability fundamentally guarantee full temporal safety as opposed to probabilistic defenses on conventional architectures. Even so, the high cost of frequently sweeping memory to invalidate stale capabilities means that currently CHERI temporal safety is only possible, but not feasible. To address this, I explore hardware optimisations and new memory allocator designs to significantly reduce the cycle overhead and DRAM traffic for capability sweeping revocation, making it practical for most applications to adopt CHERI temporal memory safety.

#### 1.1 Contributions

Contribution to various capability compression schemes especially the CHERI

Concentrate (CC) format. CC-128 compresses 256-bit capabilities into 128 bits.

It halves the memory footprint of capabilities, improves encoding efficiency,

maintains compatibility with legacy C code and addresses pipelining issues.

- Restructuring BERI with 32-bit addressing and implementing CHERI-64, a compressed 64-bit capability scheme and a 64-bit capability coprocessor for the 32-bit CPU.

- Various fixes and patches to upstream LLVM to enable 32-bit addressing for MIPS in the compiler. Adding support for CHERI-64 on top of the MIPS 32bit compiler in Clang/LLVM.

- A real-time kernel, CheriRTOS, which enforces fine-grained memory protection and efficient task isolation via capabilities.

- CHERI temporal memory safety study. I introduce new instructions and microarchitectural optimisations for fast memory sweeping, and implement a nonreuse memory allocator for reduced memory sweeping.

#### 1.2 Publications

- Xia, H., Woodruff, J., Ainsworth, S., Filardo, N. W., Roe, M., Richardson, A., Rugg, P., Neumann, P. G., Moore, S. W., Watson, R. N. M. and Jones, T. M. 'CHERIvoke: Characterising Pointer Revocation Using CHERI Capabilities for Temporal Memory Safety'. In: Proceedings of the 52Nd Annual IEEE/ACM International Symposium on Microarchitecture. MICRO '52. Columbus, OH, USA: ACM, 2019, pp. 545–557.

- Woodruff, J., Joannou, A., Xia, H., Fox, A., Norton, R., Chisnall, D., Davis, B., Gudka, K., Filardo, N. W., Markettos, A. T., Roe, M., Neumann, P. G., Watson, R. N. M. and Moore, S. W. 'CHERI Concentrate: Practical Compressed Capabilities'. In: *IEEE Transactions on Computers* (2019)

- Xia, H., Woodruff, J., Barral, H., Esswood, L., Joannou, A., Kovacsics, R., Chisnall, D., Roe, M., Davis, B., Napierala, E., Baldwin, J., Gudka, K., Neumann, P. G., Richardson, A., Moore, S. W. and Watson, R. N. M. 'CheriRTOS: A Capability Model for Embedded Devices'. In: 2018 IEEE 36th International Conference on Computer Design (ICCD). 2018, pp. 92–99

- Joannou, A., Woodruff, J., Kovacsics, R., Moore, S. W., Bradbury, A., Xia, H., Watson, R. N. M., Chisnall, D., Roe, M., Davis, B., Napierala, E., Baldwin, J., Gudka, K., Neumann, P. G., Mazzinghi, A., Richardson, A., Son, S. and Markettos, A. T. 'Efficient Tagged Memory'. In: 2017 IEEE International Conference on Computer Design (ICCD). Nov. 2017, pp. 641–648

#### 1.3 Dissertation overview

In Chapter 2, I present a short survey of the current processors used in embedded devices. Then, I present the growing problem of security and memory safety in such systems, accompanied by case studies on the typical attack vectors. The next section introduces and describes the state-of-the-art memory security schemes and techniques, followed by comparison and analysis on the effectiveness and shortcomings of said approaches. From the analysis I extract the fundamental requirements of memory safety for embedded systems.

Chapter 3 describes the work I have done to investigate a new compressed capability format for embedded processors. The study consists of the design and implementation of the 64-bit CHERI Concentrate encoding. I evaluate the memory overhead due to low precision and the hardware implementation complexity compared with other state-of-the-art security components, drawing the conclusion that a 64-bit compressed capability machine for 32-bit embedded devices is feasible.

Chapter 4 presents my work on a proof-of-concept RTOS kernel, CheriRTOS, using CHERI as the only memory protection and isolation mechanism atop CHERI-64. The evaluation shows that a capability-aware RTOS can be implemented without violating the constraints of typical embedded systems.

Chapter 5 visits the topic of enforcing temporal memory safety under the CHERI architecture. I propose, investigate and implement new ISA and micro-architectural changes to significantly accelerate sweeping revocation for capabilities. Further, I implement a non-reuse version of the dlmalloc memory allocator which avoids the reuse of memory allocations and reduces the rate required for sweeping. Combined, the proposed changes bring the cost of sweeping revocation down by orders of magnitude, making it feasible to apply CHERI temporal safety to many applications.

Chapter 6 draws conclusions.

# Chapter 2

# **Background**

One major focus of this thesis is bringing capability-based protection to the 32-bit embedded space. I begin by defining what it means to operate in the embedded space. Next, I describe the situation of memory safety for such systems, presenting literature review and case studies to illustrate the status quo of memory protection for embedded devices. Based on the advantages and shortcomings of state-of-the-art memory safety schemes, I identify and summarise the requirements of a secure design. Finally, I present background knowledge of CHERI.

#### 2.1 Introduction to embedded systems

Embedded systems and processors are deployed among various sectors, which typically include devices ranging from tiny chips like in video cables, keyboard controllers and sensors, to small ones like Wi-Fi and security chips in mobile phones, to even larger systems like routers. They differ vastly from normal desktop and server systems in that they do not perform general purpose computing, instead they are heavily adapted to domain-specific areas and custom designs, performing only a handful of dedicated tasks. Moreover, software running on top of it does not commonly involve general purpose operating systems with a full stack of capabilities (e.g., the abstraction of files, processes, networking, etc.). Instead, code either runs on bare-metal (no OS) or under a Real-Time Operating System (RTOS), providing limited abstractions and interfaces for dedicated computations. In terms of computing instances, an RTOS

creates and runs lightweight tasks in a shared flat address space, an analogous but simpler model to processes in UNIX operating systems.

Another major difference are the primary requirements. A PostgreSQL database server running under Linux, for example, focuses on high processing power, high throughput and multi-processing to resolve the large number of requests from clients. On the contrary, the goal of embedded applications is typically low-latency, determinism and deadline guarantees. For example, a self-driving vehicle has to respond promptly in the steering and brake system when a danger arises. The system ensures that it responds to real-time events within a pre-determined delay. Failing to guarantee real-timeness and determinism may put the user into critical danger, whereas the raw performance of such processors may not be of primary concern. In addition, these devices are commonly used in highly constrained scenarios including low-cost and low-power applications. As a result, they often come with a limited amount of RAM and ROM and are not clocked at high frequencies, and commonly have a very simple cache hierarchy or no caches at all. This leads to many important design decisions like minimising code size, the support for low-power programming and deep sleep modes.

Although the above describes the typical characteristics of embedded systems, many devices today are labelled "embedded", covering a wide range of different specifications. From the very low end, we have a keyboard controller that is an 8-bit processor operating at only a couple of megahertz, to an Amazon Fire TV stick with a quad-core Snapdragon 8064 and 2GiB RAM, and an Android-based operating system. As the scope may be too broad and some "embedded systems" already deviate a lot from the requirements above, I would like to narrow down the definition so that the target of this thesis is unambiguous.

The specifications of the embedded systems discussed throughout this thesis should be:

- Used in low-cost and low-power scenarios.

- Limited memory (typically under 1MiB), very simple or no cache hierarchy.

- Short in-order processor pipeline.

- Flat physical address space. No address translation, virtual memory or Memory Management Unit (MMU).

- Code runs on bare-metal or an RTOS.

- Focuses on determinism and real-time constraints in addition to performance.

- Priority-based or deadline-driven task scheduling for multitasking.

- Connected to other systems, either wired or wireless, i.e., direct physical attacks

are not the only possible vulnerability.

#### 2.2 The need for memory safety

The rapid growth of the market of embedded systems and the increase of connections across devices pose new threats and challenges. Today, even the smallest embedded products (e.g., smart watches and earphones) are connected to various other devices via connections like Wi-Fi or bluetooth. The increased connectivity quickly invalidates our previous assumption that these devices are susceptible primarily to physical attacks, and exposes a whole new variety of attack surfaces.

Recently, new attack vectors targeting memory safety have been disclosed, either exposing a crucial vulnerability for a specific device, or in terms of systematic surveys of attack surfaces. For instance, the Broadcom Wi-Fi vulnerability disclosed in 2017 [5] allows arbitrary code execution in the Wi-Fi chip of many mobile phones. Costin, A. et al. conduct a large-scale survey of a total of 32,356 firmware images of common embedded devices, extracting RSA keys, password hashes as well as identifying backdoors. The study concludes that an even broader analysis is necessary to systematically understand the vulnerabilities in embedded firmware [17]. These vulnerabilities are only a tip of the iceberg of all the possible attacks discovered in recent years, and with the rapid growth of Internet of Things (IoTs), we can only be prepared for further disclosure of even more sophisticated attacks. In fact, papers and articles from academia and industry (e.g., [65, 42, 24]) have already warned us of the difficult situation and other challenges of enforcing security in embedded and IoT devices. With more than 200 billion IoT devices in total to be shipped by 2021 [24], and several security platforms only starting to emerge now, we do not anticipate the security aspect to be effectively addressed in the near future.

#### 2.3 State-of-the-art memory protection

#### 2.3.1 Desktop systems

Memory corruption bugs and attacks have been well studied in past decades with countless projects and papers on multiple fronts. In summary, we are able to categorise these bugs into two major categories, that is, spatial or temporal memory safety violations. The paper Eternal War on Memory offers a good summary and overview of a wide range of memory bugs, attacks and potential mitigations [62], which describes how such small bugs can be leveraged and quickly escalate into severe system vulnerabilities, including code injection, control flow hijack, data attacks and information leak. Besides the exposure of memory corruptions, defense and mitigation techniques have been proposed and implemented to counteract the damage, which include both hardware and software approaches, for example: virtual memory for address space isolation and page-level protection, AddressSanitizer [56] to detect out-of-bounds, use-after-free, use-after-return access, memory tagging (SPARC Silicon Secure Memory (SSM) [50] and AArch64 Hardware ASan (HWASAN)) for temporal safety violation detection, StackGuard [18] to guard against stack overflows by inserting canaries, Control Flow Integrity (CFI) schemes [12] to defend against Jump-Oriented-Programming (JOP) and Return-Oriented-Programming (ROP) attacks, fat-pointers [46, 49] to bounds check on a per-pointer level, and so forth. Many of the defense techniques have already been used in production with reasonable strength and performance.

#### 2.3.2 Searching for novel solutions for embedded systems

Unfortunately, memory safety for desktop computers mentioned above can exhibit high overhead. AddressSanitizer, for example, incurs more than  $2 \times$  slowdown and memory overhead for memory intensive workloads [56]. To make matters worse, determinism is a common requirement for low-latency use cases which is overlooked in the aforementioned studies. MMUs, for example, introduce non-determinism due to Translation Lookaside Buffer (TLB) misses and page table walks, even though the TLB hardware is not too expensive to incorporate. Therefore, virtual memory is typically absent from embedded systems.

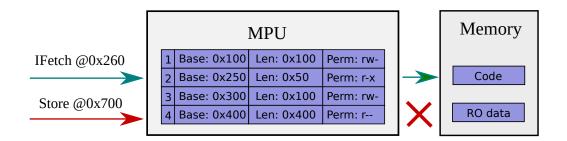

Figure 2.1: Memory accesses controlled by MPU

These limitations mean well-studied solutions rarely scale down, and novel solutions are developed and specifically tailored to these devices. The Memory Protection Unit (MPU) is commonly adopted in embedded processors to mark memory regions with security attributes [2] to prevent arbitrary physical memory access (Figure 2.1). The intention is to protect crucial code and data from buggy or malicious user space tasks. Although widely used in industry, MPUs have several inherent drawbacks. First, an MPU is implemented as a kernel space device and each register takes several cycles to configure, and some memory mapped implementations have even higher latencies through the memory hierarchy. As a result, they are normally configured only globally at system start-up, which makes per-task memory access control difficult, and user space cannot adopt it for intra-task protection. Second, the number of MPU entries is limited. With only 8 MPU regions in most implementations [2], only security critical memory partitions are protected, e.g., the kernel, encryption keys, code sections, etc., thus any fine-grained memory protection with MPUs is a challenge. Third, MPU lookups involve associative searches of all entries. Each cycle can potentially require up to 32 (accounting for both instruction fetch and data) comparisons with 8 MPU entries. This means that MPUs could inherently be inefficient in terms of power and die area. To compare CHERI with the MPU model in this thesis, I implement the RISC-V Physical Memory Protection (PMP) unit, which is a state-of-the art MPU component. The RISC-V PMP has an open-source specification [66] that can be followed easily.

In addition to MPUs which generally provide system-wide memory protection for critical regions, TrustZone<sup>®</sup> partitions memory into secure and non-secure worlds [64] with constrained control flow. Non-secure code can only jump to valid entry points on the secure side, and secure code calls non-secure functions after clearing registers and pushing the return address on the secure stack to prevent data leak and to protect

the return address. Nevertheless, TrustZone is likely to encounter scalability issues. For example, further isolation within a world is not possible, still enabling attacks in the same world. A task from one user is visible (and potentially modifiable) from another, and buggy drivers in the secure world can have access to secrets and secure keys which are stored in the secure space as well.

Besides commercial implementations, research projects also tackle the problem of embedded system memory safety. TrustLite [37] and TyTAN [9] extend the MPU and kernel to provide data isolation, trusted inter-task communication, secure peripherals, run-time configurability, etc. The Execution-Aware MPU (EA-MPU) links data and code entries and tags them with task identifiers. Therefore, only the entries of the active task are enabled, providing per-task protection. However, an MPU-based approach inherits several flaws described above, the most significant being that the number of protected regions is still severely limited by the number of MPU entries. If the kernel attempts to support more tasks and regions than MPU entries, then expensive system calls have to be made to swap MPU registers when the desired one is not present. TrustLite argues that this bottleneck may not be a problem as the number of simultaneous tasks in embedded systems is low. However, as the market rapidly grows, I would like to see scalable and future-proof solutions in case this assumption cannot be safely made in the near future.

For control flow robustness and defense against Return-Oriented Programming (ROP) attacks, architectures have been developed for embedded systems [21, 20] by using dedicated instructions for function calls, exposing only valid entry points, hiding return addresses in protected spaces and so forth in a similar approach to TrustZone. On the other hand, Sanctus [48, 61] builds tasks into Self-Protecting Modules (SPMs) to restrict access and enforce control flow with a minimum Trust Computing Base (TCB). However, it sacrifices software flexibility and incurs a high hardware cost by implementing SPM loading, measurement and runtime identification in the trusted CPU.

We have also seen research projects tackle the memory protection problem on a programming language level for embedded devices. nesCheck [45] modifies the language and compiler to perform stronger type safety, type validation, static analysis and run-time checks, carrying additional metadata to remove or detect unsafe memory access. Others develop new compiler frameworks to address stack, array and pointer

safety, and implement new heap allocation techniques to address heap safety without introducing garbage collection [25]. These language- and compiler- based schemes have shown good results within reasonable overhead and without substantial hardware changes. However, a software approach protects code written or compiled under specific language variants or toolchain. If a task is compromised or is itself malicious, it may directly execute or inject low-level code that circumvents any language level invariants. Similar to other software schemes for desktop systems, this type of memory protection is most useful for debugging existing codebase rather than offering systemwide security guarantees.

#### 2.4 Case studies

#### 2.4.1 The Broadcom Wi-Fi attack

The Broadcom's Wi-Fi chipset is widely deployed in smartphones including the Nexus series, Samsung products and all iPhones since iPhone4. A successful exploit was recently discovered and published in such a system [5]. The Wi-Fi chipset, BCM4339, is a Cortex-R4 based SoC running firmware from a 640KiB ROM and processing data from a 768KiB RAM.

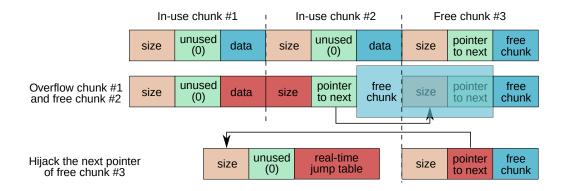

Figure 2.2: Escalations towards a successful control flow hijack. size (brown) and pointer to next/unused (green) are allocator metadata fields. data (blue) is the actual allocated memory. Red indicates contaminated fields.

Figure 2.2 illustrates how a slight buffer overflow is exploited which escalates to a complete control flow hijack. To summarise:

- 1. Reverse engineering reveals a slight overflow in a heap allocation (chunk #1). which is sufficiently large to overwrite the size field of an adjacent in-use allocation (#2).

- 2. Chunk #2 is deallocated when the Wi-Fi connection closes. It is linked into the free-list before chunk #3 with a hijacked size field.

- 3. The attacker carefully crafts a request that fits into the hijacked size and is allocated to chunk #2, which now overlaps with #3.

- 4. The next-pointer field of #3 is under the control of the attacker. It is overwritten with a value that points to a kernel allocation storing the real-time jump table. Now the in-use allocation containing the kernel jump table is exposed in the free-list.

- 5. The attacker sends another crafted request that gets allocated to the jump-table memory chunk and overwrites them with pointers to malicious code.

- 6. A real-time event fires. The kernel fetches the hijacked pointer in the jump table and jumps to malicious code.

Again, this is another typical example of a minor buffer overflow leading to arbitrary code execution. After dissecting the firmware, the reverse-engineered code shows that the programmer actually has memory safety in mind. For example:

The code checks for an overflow before copying data. Both the difficulty and the run-time overhead forbid the programmer to add manual bounds checks to every potential overflow, leaving several of them still hidden and exploitable. One may argue that the proper use of MPU could prevent such attacks, and in fact the Cortex-R4 CPU of the Wi-Fi chip implements it. However, we also imagine the difficulty of adapting it to this use case. Heap allocations require fine-grained protection on every memory chunk, which unfortunately cannot be achieved with the coarse-grained MPU with limited regions. At best, a programmer could segregate the heap into a kernel and a user pool and dedicate two MPU entries, which still does not stop memory attacks between users or between the kernel and buggy drivers in the kernel space.

The problem of centralised heap management. The Wi-Fi attack shows a fundamental problem of memory allocation. In typical embedded systems with a small flat physical address space, dynamic memory allocations are commonly done in a centralised heap for all user tasks (or even including the kernel). Although many dynamic heap allocators actually have low and relatively deterministic latencies and are widely used among multiple systems including mbedOS, FreeRTOS [4] and TinyOS [45], the security issues caused by dynamically allocated and shared memory pool have never been properly addressed. Without bounded access, allocations from a user can easily overflow into other allocations or even the heap metadata to attack other users or the heap allocator itself. To hide and protect heap metadata, many allocators including jemalloc [28] used in FreeBSD organise the metadata in separate data structures. However, embedded systems still prefer to attach metadata directly beside each allocated chunk and use "free-lists" like dlmalloc [40] in mbedOS for lower latency. The organisation of such allocators demands low-latency fine-grained memory protection for effective isolation, which unfortunately is difficult to achieve with current software-hardware platforms, and inherently creates the tension between flexibility and security. Many designs simply revert to pre-determined static allocations for each task to avoid this problem, losing all flexibility of a dynamic heap.

#### 2.4.2 The QSEE privilege escalation vulnerability

The Qualcomm's Secure Execution Environment (QSEE) uses TrustZone technology to contain trusted applications (trustlets) in the secure world beside a normal embedded OS. Trustlets perform privileged operations like key storage and Digital Rights Management (DRM). Only few applications in the normal world are able to load and communicate with the trustlets in a controlled manner, and the MPU is set to protect the regions of trustlets against data attacks and code injection. Recently, an attack has been found to exploit one of the trustlets to execute arbitrary code

in the secure domain [6]. The attack starts in a similar way to the Broadcom WiFi attack by uncovering a crucial buffer overflow. The details are more complex and will not be listed here.

The author of [6] observes that all trustlets reside in the secure world and Trust-Zone only offers a uni-directional trust relationship. Two key properties arise from this observation. One, a successful exploit on a single trustlet can expose all other trustlets in the secure world. Two, the secure world has strictly higher privileges, which is able to read, write and execute any memory in the normal world as well. In this example, part of the gadgets is simply injected to the normal world and is executed by the indirected trustlet, which in turn attacks the embedded OS and other parts of the system.

In addition to memory protection, this attack exposes the insufficient level of isolation and scalability provided by TrustZone. Having only two worlds forces all trustlets to live in a single domain, exposing them to possible attacks from one another. Also, TrustZone employs a traditional hierarchical and uni-directional approach which fails to guarantee mutual distrust. In the attack, it is questionable to run the embedded OS in the normal world while the trustlets live in the secure world. This design suggests that trustlets have strictly higher privileges than the OS, which is not true. The embedded OS can be attacked from the secure side even though it contains no vulnerabilities itself. A desirable design should allow mutual distrust domains, where they are parallel instead of being a superset or subset of each other.

#### 2.5 Requirements

Although the case studies are just two data points, most security vulnerabilities originate from similar memory safety issues. In fact, Microsoft security engineers have confirmed that around 70% of all the vulnerabilities in Microsoft products addressed through a security update each year are memory safety issues [63]. From the common attack surface in security vulnerabilities, the survey of state-of-the-art solutions, the shortcomings of existing protection schemes and the properties and growth of embedded systems themselves, I identify the following requirements that are essential to a secure design.

Task isolation. In a flat physical address space, it is essential to separate multiple tasks from different users or vendors into different domains. Unconstrained access means a malicious task can easily compromise other critical components in the system. In addition, I would like to include mutual distrust as part of the definition, as the case study demonstrates that a uni-directional trust model is insufficient.

Fine-grained memory protection. So far, memory protection in embedded systems controls access to large segments of code and data. Protecting finer granularities often require explicit checks from the compiler or programmer at a cost of run-time slowdown [25, 45], and can be error-prone or incomplete [5]. An architecture should provide a generic mechanism for low-cost and fine-grained memory protection.

Fast and secure domain crossing and inter-task communication. A system with multitasking often requires communication among components, either in terms of message passing and memory sharing, or in cross-domain function calls. Strong task isolation should not prohibit efficient and secure domain crossing and communication.

**Secure centralised heap management.** As discussed in Section 2.4.1, existing protection schemes often fail to guarantee that memory management in embedded systems is both flexible and secure. A system with fine-grained memory protection enables a secure shared-heap allocator by restricting any user of allocations from reaching metadata or any other allocations.

**Real-time guarantees.** No security architecture should violate real-time constraints. Cached memory translation (like virtual memory with MMU), for example, directly violate the low-latency and deterministic properties of embedded systems and therefore should not be used for protection.

**Scalability.** We have seen the rapid growth of the embedded market in recent years and a scalable solution is desirable. MPU-based approaches described above suffer from scalability issues and may not meet the security needs as these systems become more capable and dynamic.

A generic solution for security. Embedded chips often implement multiple components to enforce safety. ARM solutions typically provide an MPU, a Security Attribution Unit (SAU), TrustZone® and even an Implementation Defined Attribu-

tion Unit (IDAU) for security. Together, these components are able to defend against common attacks if configured correctly. However, orchestrating many security mechanisms is non-trivial, and we have seen in practice that vendors often revert to manual assertions and explicit checks, leaving these security layers largely unused. An ideal solution should be generic enough to ease the effort of orchestration and deployment.

#### 2.6 Introduction of capability models and CHERI

#### 2.6.1 Historical capability machines

In 1966, Dennis and Van Horn formally described a memory protection framework in which each process possessed a list of keys (capabilities) that granted access to objects within the system [23]. A capability is an unforgeable token, which when presented can be taken as incontestable proof that the presenter is authorized to have access to the object named in the token [54]. Capability systems are one of the architectural protection models among segmented memory, MMU protection, access control lists, etc. Capability systems have been implemented on various machines including IBM System/38, which created a unique ID for each capability and used a tagged architecture to avoid malicious capability manipulation [41], and the Cambridge CAP computer, which had a centralised capability table that also facilitated secure procedure calls [47]. Other than a hardware approach, a software capability system, Hydra, implemented an object-based OS with internal bit vectors for permissions, in which a set bit indicated a granted permission. AND only operations on bit vectors ensured that only a subset of permissions could be derived from given capabilities [76]. However, capability schemes in that era were not widely adopted due to the high overhead which at that time was not justified given the security provided, and have been overshadowed by coarse-grained yet low-overhead solutions like paged memory and MMUs.

Due to the rapid growth in available transistor resources and the increasingly sophisticated attacks on memory safety, capability machines have been revisited recently as a complementary or an alternative approach. Recent software capability models include Capsicum, which takes an incremental approach and serves as an extension for UNIX, providing new kernel primitives and userspace sandbox API via

capabilities [68]. The formally verified seL4 uses capabilities for memory management, authorisation, etc. [36]. To extend the Trusted Computing Base (TCB) to hardware and for a better performance, many architectural proposals have emerged, including the M-Machine [13] and the Low-Fat Pointer scheme [39], which provide hardware bounds checking and novel domain crossing mechanisms.

# 2.6.2 Overview of Capability Hardware Enhanced RISC Instructions, CHERI

CHERI, developed by SRI International and the University of Cambridge, revisited capability systems by extending the Bluespec Extensible RISC Implementation (BERI) platform and adding security extensions for the 64-bit MIPS Instruction Set Architecture (ISA) [70, 75]. The CHERI ISA provides direct processor support for fine-grained memory protection and scalable compartmentalisation on top of paged memory. Unlike previous capability implementations, CHERI maintains both a mixed model (traditional code mixed with capabilities) and the purecap-ABI (pure capabilities) to offer fine-grained protection while being backward compatible, therefore it is able to run a range of software including FreeBSD/CheriBSD and other user-space applications. BERI/CHERI is written in Bluespec System Verilog (BSV), a high-level functional HDL language, and the existence of other higher level implementations and simulation platforms (QEMU, L3) allow further extensions and rapid explorations.

#### CHERI capabilities

CHERI architecturally distinguishes capabilities from normal data. All memory accesses (including instruction fetch and data load and store) in CHERI must be done via capabilities. An access fails if the capability does not allow such an operation, either due to out of bounds or insufficient permission. To enforce integrity and unforgeability, each capability is tagged with a **tag** bit set, without which a capability is not valid to be used. In addition to bounded memory access with memory capabilities, sealed capabilities (**s** bit set) can be used for compartmentalisation and fast domain crossing. Sealed capabilities are created with another capability as a key. After the sealing operation, the capability is immutable and non-dereferenceable, and is given an Object Type (otype) from the key. CHERI restricts that capabilities can only be unsealed in two ways. First, the original key or another key with suffi-

| Mnemonic                                   | Description                                                                                                                                                                                  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CGetBase<br>CGetLen<br>CGetTag<br>CGetPerm | Move base to a GPR Move length to a GPR Move tag bit to a GPR Move permissions to a GPR                                                                                                      |

| CSetBounds<br>CClearTag<br>CAndPerm        | Set (reduce) bounds on a capability Invalidate a capability register Restrict permissions                                                                                                    |

| CLC<br>CSC<br>CL[BHWD][U]<br>CS[BHWD]      | Load capability register Store capability register Load byte, half-word, word or double via capability register, (zero-extend) Store byte, half-word, word or double via capability register |

| CToPtr<br>CFromPtr                         | Generate DDC-based integer pointer from a capability<br>CIncBase with support for NULL casts                                                                                                 |

| CBTU<br>CBTS                               | Branch if capability tag is unset<br>Branch if capability tag is set                                                                                                                         |

| CJR<br>CJALR                               | Jump capability register Jump and link capability register                                                                                                                                   |

| CCall                                      | Perform a capability call                                                                                                                                                                    |

Table 2.1: Example CHERI instruction-set extensions

cient rights can perform unsealing. Second, the Capability Call (CCall) mechanism takes a pair of sealed code and data capabilities with matching otypes and sufficient permissions. Upon a successful CCall, both the code and the data capability are unsealed and installed, transferring control to the new domain with the callee's code and data. CCall is the fundamental method to perform an atomic domain crossing across compartments under CHERI.

#### The CHERI ISA

The current CHERI ISA extends MIPS with capability instructions. It includes capability inspection (CGetBase, CGetTag...), manipulation (CSetBounds, CClearTag, CAndPerm), control flow (CBTU, CBTS, CJR, CJALR, CCall...) and memory instructions (CLC, CSC, CL[BHWD]...).

The example instructions (Table 2.1) demonstrate the important monotonicity property of CHERI, that is, the ISA only permits capability operations that do not increase rights. Any capability manipulations only decrease bounds, reduce permissions or clear tags but never vice versa. Also, storing non-capability data to a location containing a capability will invalidate the tag to forbid overwriting an existing one to change its interpretation, which combined with monotonicity guarantees unforgeability. Such restrictions ensure that a program is never able to fabricate arbitrary memory references; therefore, its ability to reference memory is strictly limited by the unforgeable capabilities it receives from the system, and a protection domain is defined by the transitive closure of memory capabilities reachable from its capability register set.

In address-space sandboxing and compartmentalisation: The fact that a domain is defined by its reachable capabilities facilitates CHERI-based compartmentalisation. The ISA defines a CCall operation that atomically switches the set of root capabilities (including code and data), transferring control and reachability to the callee. The CCall mechanism allows scalable construction and transition of compartments within a process. Compared with multi-process sandboxing that switches between processes and address spaces, CCall is orders of magnitude cheaper and achieves the same magnitude of overhead as direct function calls. For example, the CHERI-enabled FreeBSD OS presents at least three mechanisms to transfer data to another isolated domain: pipe, which transfers to a sandbox process via a UNIX pipe; shmem, which transfers to a sandbox process through shared memory using a semaphore for synchronisation; CHERI domain crossing, which transfers to a inprocess sandbox via a CHERI capability and CCall. A round trip on a tiny dataset (caller prepares data; callee calls memcpy to copy from a shared buffer to its own domain, which for this dataset takes only 150 cycles in a plain function call) takes >17,000 cycles under multi-process isolation (pipe, shmem), whereas a CHERI call/return round trip gives a fixed overhead of around 250 cycles [67]. In this simple case, CHERI overhead comes from clearing registers as well as preparing and validating callee capabilities, unlike multi-process isolation which exhibits high overhead from system calls and OS synchronisation. For large datasets, the fixed overhead of 250 cycles from CHERI becomes negligible, showing the same magnitude of performance to plain function calls, whereas the cost of cache and TLB flushes still dominates the data transfer under multi-process isolation. The pipe case performs additional data copies and converges to about 6 times more expensive than function calls and CHERI.

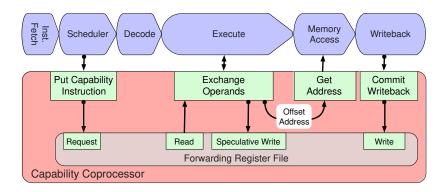

**Figure 2.3:** The capability coprocessor

CHERI compartmentalisation enables intra-process isolation, which avoids the costs incurred from inter-process communication, like kernel synchronisation, data copying, cache flushes, TLB maintenance, etc..

#### Hardware implementation

The current CHERI processor is implemented in Bluespec SystemVerilog [7] as a modularised extension to the MIPS R4000 CPU. As with the MIPS R4000, our base processor (Bluespec Extensible RISC Implementation (BERI)) is single-issue and in-order, with a throughput approaching one instruction per cycle. BERI has a branch predictor and uses limited register renaming for robust forwarding in its 6-stage pipeline. BERI runs at 100MHz on an Altera Stratix IV FPGA and is capable of running the stock FreeBSD 10 operating system and associated applications.

The CHERI processor adds capability extensions to BERI and is fully backward compatible, facilitating side-by-side comparisons. CHERI capability extensions are implemented as a MIPS coprocessor, CP2. Similar to the MIPS floating-point coprocessor, CP1, the capability coprocessor holds a new register file and logic to access and update it. The MIPS pipeline feeds instructions into the capability coprocessor, exchange operands with it, and receive exceptions from it (Figure 2.3). The capability coprocessor also transforms and limits memory requests from instruction fetch and MIPS load and store instructions. [75]

Although one may choose to understand the capability coprocessor by comparing it to a normal MIPS coprocessor, the former is far more integrated with the main pipeline and memory hierarchy than the latter. For example, capability bounds and

permission checks have altered the exception behaviour of jumps and branches; several system registers like the Program Counter (PC) have been replaced by bounded capabilities which affect the execution of the main pipeline; the main CPU and all cache hierarchies require significant change to natively understand memory tags and capabilities. In summary, the capability coprocessor affects and cooperates with the main CPU in ways that a normal MIPS coprocessor cannot, and care is needed to make direct comparisons.

The current CHERI CPU implementation adds a separate register file for capabilities, similar to a MIPS floating point coprocessor holding floating point registers. A design space worth exploring is the choice between a *split* and *merged* register file. A merged register file extends existing general purpose registers in the main CPU to also hold capabilities. The two designs have been discussed extensively in the architecture document [69] and are being further investigated. The major distinctions include:

- The coprocessor interface. A coprocessor design holding a separate register file fits nicely into the existing CPU structure and is easily configurable as an extension, whereas a merged register file needs a deep restructure of the CPU pipeline.

- Context switches. The split design introduces 32 capability registers as well as extra capability system and control registers, at least doubling the context size and increasing the latency of context switches. Such a large context is typically unacceptable in embedded and latency-sensitive systems.

- Opcode space. Dedicated opcodes are required to perform capability operations

in the capability register file. In contrast, a merged design can reuse the same

opcodes for capability manipulations. Whether the opcode is interpreted as

a capability instruction can depend on the mode of the CPU or whether the

register has a valid capability tag.

- Intentionality. It is impossible to misuse a capability register as an integer or vice

versa in the split design, since the instruction explicitly specifies the intended

register file. With integers and capabilities merged, such confusions can happen,

and explicit instructions with dedicated opcodes might still be required when

necessary.

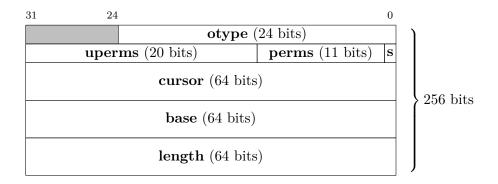

Figure 2.4: 256-bit memory representation of a capability

Compiler complexity. A merged register file can choose to extend all or part of

the general purpose registers to accommodate capabilities. Since a capability

doubles the size of an integer register, only allowing a subset for capabilities

avoids doubling the register context size. This comes at a cost of additional

compiler register allocation and ABI complexity. Therefore, this design is not

being actively explored.

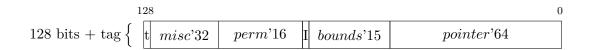

CHERI-256 encoding. Figure 2.4 shows the encoding of the 256-bit capability format. The format quadruples the pointer size by adding otype, perms, base, length fields. For memory capabilities, each dereference is checked against the bounds and permissions, and for sealed capabilities, they can only be unsealed by other capabilities that are able to unseal this otype. The otype field is also checked when performing a CCall. A CCall takes a pair of code and data capabilities, checking both otypes match before installing the unsealed capability pair of the new domain. otype matching guarantees that the new domain does not take an arbitrary sealed data capability.

The tag cache. To enforce unforgeability, the processor pipeline is modified so that each capability is extended with a tag bit in the register file and caches. However, it is much more difficult to manufacture a custom DRAM to accommodate tags. Instead, the CHERI processor uses existing off-the-shelf DRAM and partitions it into data and tags. Each memory request that reaches DRAM accesses data and its tag from the two partitions, which could potentially double the number of DRAM transactions.

Figure 2.5: Memory hierarchy and the tag cache

The current implementation addresses this issue by adding a tag cache before the DRAM (Figure 2.5). The data request is sent to DRAM while its tag is looked up in the tag cache in parallel. Upon a hit, the tag response waits for the DRAM response before being combined and returned to the L2 cache. As the data transaction and the tag cache lookup happen in parallel, such an operation has the same latency of a single DRAM transaction.

Introducing a tag cache helps avoid another problem as well, which is the aliasing effect in DRAM. Without a tag cache, the two transactions for tags and data may conflict in DRAM if, for example, they occupy different rows in the same bank. For a small DRAM array which is capable of opening only a limited number of concurrent rows, such an effect further deteriorates performance. By introducing a tag cache, most tag operations will hit in the cache and will not require a second DRAM transaction, significantly alleviating the impact of DRAM aliasing.

Of course, the effectiveness depends on the tag cache hit rate, because a miss or an evict makes it no better than issuing two transactions to DRAM. Joannou, A. et al. proposes a design [34] that compresses tags in multiple hierarchies. The compression increases the effective capacity by exploiting the sparsity of tags in memory. By exploring the design space, the author chooses an optimised configuration that reduces the DRAM overhead by up to 99% for many non-pointer-heavy applications. For the aliasing effect, a DRAM overhead reduction of 99% means only 1 in 100 tagged memory transactions will actually issue two transactions to DRAM, while 99 hit the tag cache and therefore issue a single DRAM transaction. This greatly minimises the chance of aliasing even under limited row concurrency.

## 2.7 Summary

This chapter described the embedded systems that are in scope of this dissertation. I explained the different specifications and requirements between desktop and embedded systems and why this could lead to fundamental difficulties in enforcing memory safety for the latter. The state-of-the-art and literature review presented solutions from academia and industry towards solving the problem. Nevertheless, they still face issues including weak security guarantees, inability to scale and the coarse granularity of protection.

Two case studies demonstrated that said commercial memory safety solutions in many cases failed to guarantee the desired protection level. We saw that programmers either did not use them or were forced into a non-optimal design. From the review of state-of-the-art and the case studies, I extracted the key requirements that should be satisfied by a secure design.

As this dissertation later explores the possibility of adapting CHERI to embedded systems, I presented the background, basics and other fundamentals of capability systems and CHERI. The next chapter will explore the design of efficient compressed capability encodings and implementations for embedded space.

## Chapter 3

# A 64-bit compressed capability scheme for embedded systems