Technical Report

Number 931

**Computer Laboratory**

## A Performance-efficient and practical processor error recovery framework

Jyothish Soman

January 2019

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

#### © 2019 Jyothish Soman

This technical report is based on a dissertation submitted July 2017 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Wolfson College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

#### Abstract

Continued reduction in the size of a transistor has affected the reliability of processors built using them. This is primarily due to factors such as inaccuracies while manufacturing, as well as non-ideal operating conditions, causing transistors to slow down consistently, eventually leading to permanent breakdown and erroneous operation of the processor. Permanent transistor breakdown, or faults, can occur at any point in time in the processor's lifetime. Errors are the discrepancies in the output of faulty circuits. This dissertation shows that the components containing faults can continue operating if the errors caused by them are within certain bounds. Further, the lifetime of a processor can be increased by adding supportive structures that start working once the processor develops these hard errors.

This dissertation has three major contributions, namely REPAIR, FaultSim and Pre-Fix. REPAIR is a fault tolerant system with minimal changes to the processor design. It uses an external Instruction Re-execution Unit (IRU) to perform operations, which the faulty processor might have erroneously executed. Instructions that are found to use faulty hardware are then re-executed on the IRU. REPAIR shows that the performance overhead of such targeted re-execution is low for a limited number of faults.

FaultSim is a fast fault-simulator capable of simulating large circuits at the transistor level. It is developed in this dissertation to understand the effect of faults on different circuits. It performs digital logic based simulations, trading off analogue accuracy with speed, while still being able to support most fault models. A 32-bit addition takes under 15 micro-seconds, while simulating more than 1500 transistors. It can also be integrated into an architectural simulator, which added a performance overhead of 10 to 26 percent to a simulation. The results obtained show that single faults cause an error in an adder in less than 10 percent of the inputs.

PreFix brings together the fault models created using FaultSim and the design directions found using REPAIR. PreFix performs re-execution of instructions on a remote core, which pick up instructions to execute using a global instruction buffer. Error prediction and detection are used to reduce the number of re-executed instructions. PreFix has an area overhead of 3.5 percent in the setup used, and the performance overhead is within 5 percent of a fault-free case. This dissertation shows that faults in processors can be tolerated without explicitly switching off any component, and minimal redundancy is sufficient to achieve the same.

#### Acknowledgements

This thesis could not have come together without the guidance and support of many people, and especially many of my friends. I would like to thank my supervisor Dr Timothy Jones for being the source of inspiration and guidance for this work. His focus on the larger goals while pursuing short-term goals has been a revelation. Wolfson College has been a great source of support for me, especially my tutor, Dr. Kevin Greenbank, who provided me with the necessary help whenever needed, and gave me opportunities that have proved quite educational.

I would like to dedicate this thesis to my beloved friend, Negar, who is no longer with us. You were a source of strength and support during my thesis. My wife cannot go without mention in this thesis for her unending patience throughout my PhD. Finally, I would like to dedicate this thesis to my parents. Without their constant and continuing sacrifices and dedication towards my education, I would not have reached this point in life.

## Contents

| 1 | Intr | oducti | ion                                   | 11   |

|---|------|--------|---------------------------------------|------|

|   | 1.1  | Hypot  | hesis of this dissertation            | . 12 |

|   | 1.2  | Contri | ibutions of this dissertation         | . 13 |

|   | 1.3  | Disser | tation framework                      | . 14 |

| 2 | Bac  | kgrou  | nd                                    | 15   |

|   | 2.1  | Types  | of faults                             | . 15 |

|   |      | 2.1.1  | Transient faults                      | . 15 |

|   |      | 2.1.2  | Hard faults                           | . 16 |

|   |      | 2.1.3  | Physical causes of hard faults        | . 16 |

|   |      | 2.1.4  | Goldilocks Errors                     | . 18 |

|   | 2.2  | Comp   | arison of Hard and Soft faults        | . 18 |

|   | 2.3  | Overv  | iew of Fault tolerance strategies     | . 19 |

|   | 2.4  | Cost r | metrics of Fault Tolerance            | . 21 |

|   | 2.5  | Proces | ssor architecture and Fault-tolerance | . 21 |

|   |      | 2.5.1  | Fault tolerance for processors        | . 21 |

|   | 2.6  | Summ   | nary                                  | . 22 |

| 3 | RE   | PAIR:  | Accelerator based fault tolerance     | 23   |

|   | 3.1  | Motiva | $\operatorname{ation}$                | . 24 |

|   | 3.2  | Relate | ed work                               | . 24 |

|   | 3.3  | REPA   | IR                                    | . 26 |

|   |      | 3.3.1  | Overview of the REPAIR architecture   | . 27 |

|   |      | 3.3.2  | The REPAIR Re-Execution unit          | . 27 |

|   |      | 3.3.3  | Source operands                       | . 29 |

|   |      | 3.3.4  | Memory instructions                   | . 29 |

|   |      | 3.3.5  | Summary                               | . 30 |

|   | 3.4  | Integr | ation with standard cores             | . 30 |

|   |      | 3.4.1  | Fault coverage                        | . 31 |

|   |      | 3.4.2  | Identifying faulty instructions       | . 31 |

|   |      | 3.4.3  | Dispatch checking                     | . 32 |

|   |     | 3.4.4   | Commit checking                                                                                                                              | 33        |

|---|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   |     | 3.4.5   | Example instruction re-execution                                                                                                             | 34        |

|   |     | 3.4.6   | Rename map errors                                                                                                                            | 34        |

|   |     | 3.4.7   | Summary                                                                                                                                      | 35        |

|   | 3.5 | Experi  | imental setup                                                                                                                                | 35        |

|   | 3.6 | Result  | ·S                                                                                                                                           | 37        |

|   |     | 3.6.1   | Single-core REPAIR                                                                                                                           | 38        |

|   |     |         | Analysis                                                                                                                                     | 39        |

|   |     |         | Differences between arrays                                                                                                                   | 40        |

|   |     |         | Communication latency                                                                                                                        | 42        |

|   |     |         | Number of errors                                                                                                                             | 43        |

|   |     | 3.6.2   | Multicore REPAIR                                                                                                                             | 43        |

|   |     | 3.6.3   | Hardware overhead                                                                                                                            | 46        |

|   | 3.7 | Conclu  | usions                                                                                                                                       | 46        |

| 4 | Fau | ltSim:  | An online fault-simulator                                                                                                                    | 47        |

|   | 4.1 | Relate  | d Work                                                                                                                                       | 47        |

|   | 4.2 | Metho   | $\mathbf{d}$                                                                                                                                 | 49        |

|   |     | 4.2.1   | Circuit modelling                                                                                                                            | 49        |

|   |     | 4.2.2   | Circuit simulation                                                                                                                           | 50        |

|   |     |         | Initialisation                                                                                                                               | 50        |

|   |     |         | Circuit simulation                                                                                                                           | 52        |

|   |     |         | Higher level models                                                                                                                          | 52        |

|   |     | 4.2.3   | Fault models and fault injection                                                                                                             | 53        |

|   |     | 4.2.4   | Integration with Gem5                                                                                                                        |           |

|   | 4.3 | Knowl   | les Adders                                                                                                                                   | 54        |

|   | 4.4 | Experi  | imental Setup                                                                                                                                | 55        |

|   | 4.5 | Result  | 8                                                                                                                                            | 56        |

|   |     | 4.5.1   | FaultSim performance                                                                                                                         | 57        |

|   |     | 4.5.2   | FaultSim-Gem5 performance                                                                                                                    | 58        |

|   |     | 4.5.3   | Comparison with other fault simulators                                                                                                       | 59        |

|   | 4.6 | Conclu  | usions                                                                                                                                       | 61        |

| 5 | Pre | Fix: Fa | ault Tolerance using predictive remote re-execution                                                                                          | <b>62</b> |

|   | 5.1 |         | $ation \ldots \ldots$ | 63        |

|   |     | 5.1.1   | Related Work                                                                                                                                 | 64        |

|   |     | 5.1.2   | Justification for PreFix                                                                                                                     |           |

|   | 5.2 | PreFix  | ζ                                                                                                                                            | 65        |

|   |     | 5.2.1   | Instruction Flow                                                                                                                             | 66        |

|     | 5.2.2    | $2  \text{Pre-Decoder}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                            |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------|

|     | 5.2.3    | 3 PreFix Frontend                                                                                                                   |

|     |          | PreFix Predictor                                                                                                                    |

|     |          | Fault Trees    68                                                                                                                   |

|     |          | Duplicate Execution                                                                                                                 |

|     | 5.2.4    | 4 PreFix Backend                                                                                                                    |

|     |          | PreFix Fault Detector                                                                                                               |

|     |          | Corrector Unit                                                                                                                      |

|     | 5.2.     | 5 Parameter Dependence                                                                                                              |

| 5   | .3 Exp   | $erimental setup \dots \dots$ |

| 5   | .4 Res   | $ults \ldots \ldots$              |

|     | 5.4.     | 1 PreFix performance                                                                                                                |

|     | 5.4.2    | 2 Impact of prediction                                                                                                              |

|     | 5.4.     | 3 Area and power overhead                                                                                                           |

| 5   | .5 Con   | clusions                                                                                                                            |

| 6 ( | Conclus  | ions 77                                                                                                                             |

| 6   | .1 Con   | tributions $\ldots \ldots .$ 77                 |

|     | 6.1.     | 1 REPAIR                                                                                                                            |

|     | 6.1.2    | 2 FaultSim $\ldots \ldots $              |

|     | 6.1.     | 3 PreFix                                                                                                                            |

| 6   | .2 Con   | nparison between PreFix and REPAIR                                                                                                  |

| 6   | .3 Usa   | ge scenario of REPAIR and PreFix 80                                                                                                 |

| 6   | .4 Lim   | itations and drawbacks                                                                                                              |

| 6   | .5 Futi  | ure work                                                                                                                            |

| 7 0 | Guide to | o McPat usage 82                                                                                                                    |

| 7   | .1 McI   | Pat Architecture                                                                                                                    |

| 7   | .2 Usir  | ng McPAT                                                                                                                            |

| 7   | .3 Cod   | le observations                                                                                                                     |

## List of Figures

| 1.1  | Overview of dissertation structure                                            | 13 |

|------|-------------------------------------------------------------------------------|----|

| 3.1  | REPAIR overview.                                                              | 27 |

| 3.2  | Overview of the IRU                                                           | 28 |

| 3.3  | Detection stages within a core                                                | 30 |

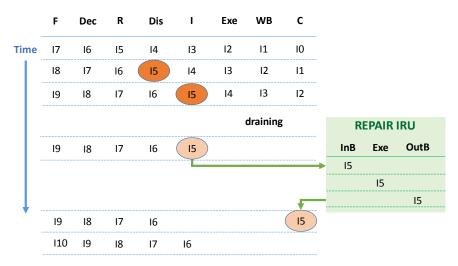

| 3.4  | Example rerun of an instruction using REPAIR                                  | 34 |

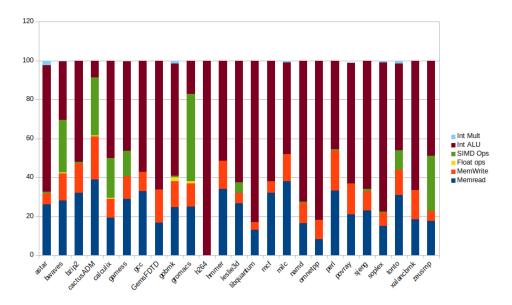

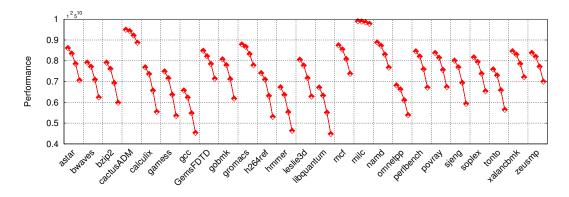

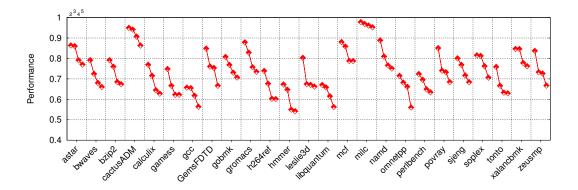

| 3.5  | The spread of instructions in the different benchmarks                        | 38 |

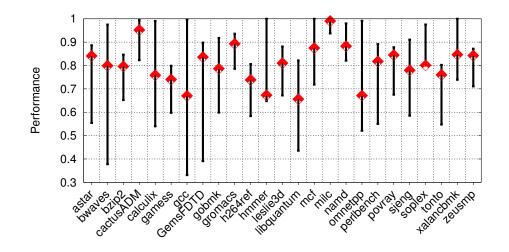

| 3.6  | Performance of REPAIR across single-core systems, each with a single error.   | 39 |

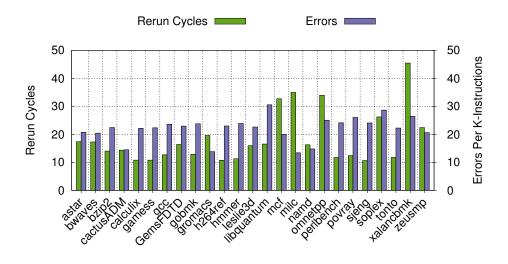

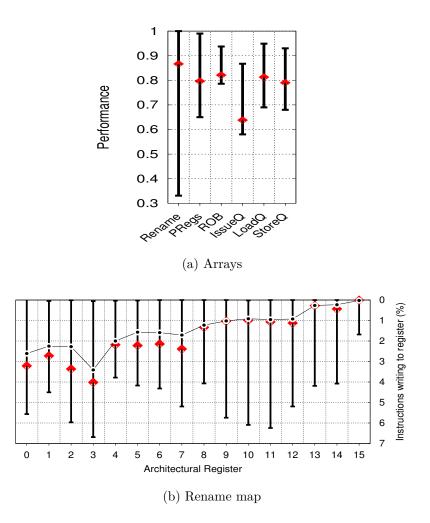

| 3.7  | Cycles taken for re-execution and number of errors per kilo-instruction       | 40 |

| 3.8  | Performance across different architectural arrays and within the rename       |    |

|      | map; also the fraction of instructions committed using each architectural     |    |

|      | register as a destination.                                                    | 41 |

| 3.9  | Performance on a single core with the addition of extra communication         |    |

|      | cycles between the core and IRU.                                              | 42 |

| 3.10 | Performance on a single core as the number of errors increases                | 42 |

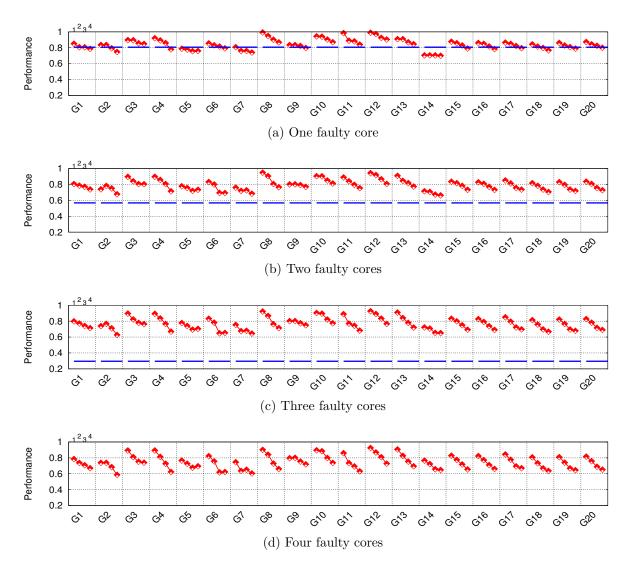

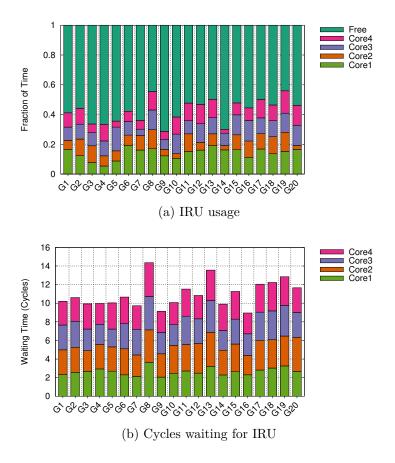

| 3.11 | Performance on a 4-core system as the number of errors per core increases.    |    |

|      | Also shown is a comparison scheduler.                                         | 44 |

| 3.12 | IRU usage and core waiting time on 4 cores, each with 4 errors                | 45 |

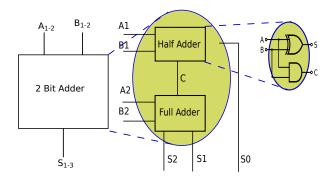

| 4.1  | A heirarchical model of a 2-bit adder                                         | 50 |

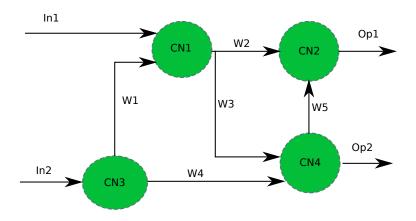

| 4.2  | Path delay modelling example                                                  | 51 |

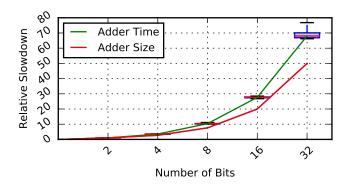

| 4.3  | Scaling of FaultSim with increasing circuit complexity. Relative increase     |    |

|      | in time and size compared to a 2 bit Knowles adder is shown. $\ldots$ .       | 57 |

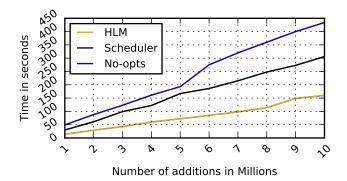

| 4.4  | Performance comparison of different optimisations                             | 57 |

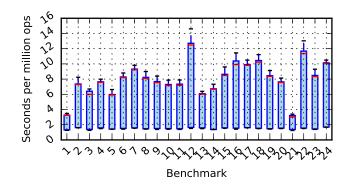

| 4.5  | Time in seconds per million $32$ bit addition operations using FaultSim using |    |

|      | SPEC2006 benchmarks.                                                          | 59 |

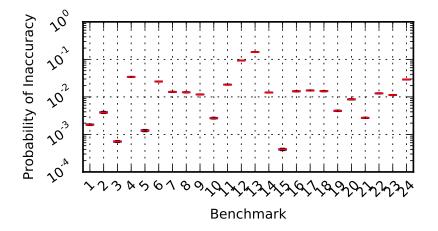

| 4.6  | Probability of error for single faults across different benchmarks            | 60 |

| 5.1  | Performance degradation caused by preventing instructions that would in-      |    |

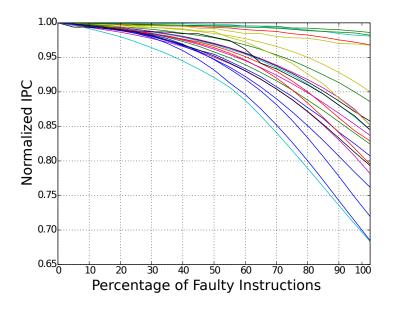

|      | cur errors from passing through a partially faulty ALU                        | 65 |

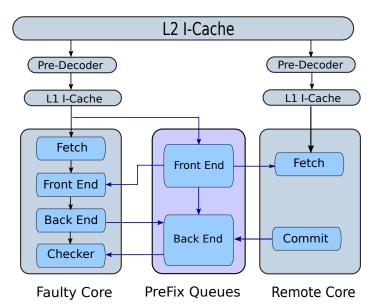

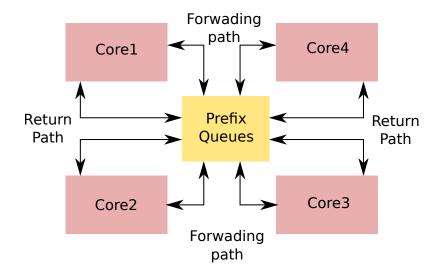

| 5.2  | PreFix overview showing CPU pipeline integration.                             | 66 |

| 5.3  | PreFix overview showing a multi-CPU configuration.                            | 67 |

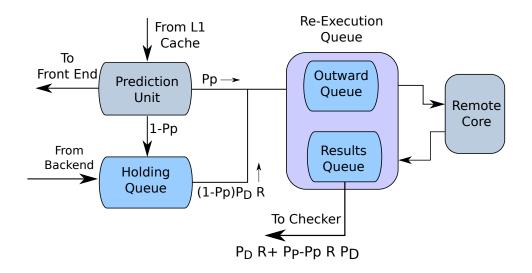

| 5.4 | PreFix front end showing predictor and the queues. Further the probabil-   |    |  |

|-----|----------------------------------------------------------------------------|----|--|

|     | ities through each section are shown.                                      | 69 |  |

| 5.5 | PreFix detection logic. Each component has a related detector and any      |    |  |

|     | trigger causes a re-execution                                              | 71 |  |

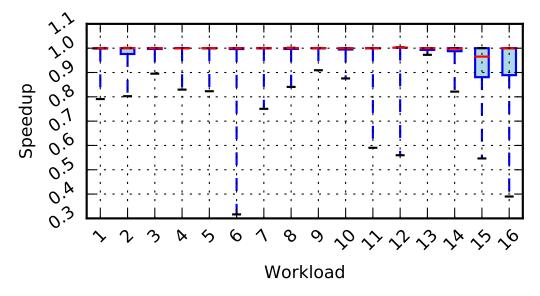

| 5.6 | Results with full PreFix. Frequent errors cause significant slowdowns, but |    |  |

|     | median performance shows little impact.                                    | 74 |  |

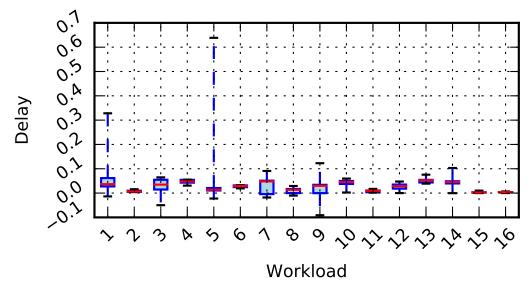

| 5.7 | Delay per re-executed instruction                                          | 75 |  |

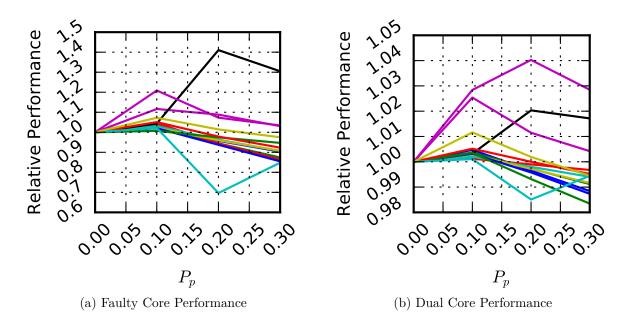

| 5.8 | Effect of varying the prediction rate on a 2-core system                   | 76 |  |

|     |                                                                            |    |  |

## List of Tables

| 3.1 | Experimental setup for cores and memory.                                           | 36 |

|-----|------------------------------------------------------------------------------------|----|

| 3.2 | Benchmark groupings for 4-core workloads                                           | 37 |

| 3.3 | Correlation between different application statistics and the performance of REPAIR | 39 |

| 4.1 | Benchmarks and their ids                                                           | 58 |

| 4.2 | Relative runtime of gem5-FaultSim as compared to a gem5 only run $\ . \ . \ .$     | 60 |

| 5.1 | Randomly-selected pairs of benchmarks studied                                      | 73 |

| 6.1 | Comparison of REPAIR and PreFix.                                                   | 79 |

## Chapter 1

## Introduction

Transistor manufacturing has been steadily improving over time. One benefit from this is the scaling down of the transistor size by  $2 \times$  nearly every four years. Moore's law [1] provides a rough guideline for this scaling. Chip fabrication since the 90s has followed Moore's Law with an error margin of  $\pm 1$  years. Until the current technology node of 14nm, despite the difficult manufacturing process, transistor scaling has just managed to stay true to the law.

This scaling down brings expectations of proportional high performance, power and area improvements for the designs. Dennard scaling [2] provided estimates for voltage, power, delay and area for a transistor as its dimensions scale. Dennard suggested that the per-transistor delay, current and voltage will scale in direct proportion to the transistor scaling. Given that  $Power \propto Voltage \times Current$ , power consumed per transistor, would scale at a quadratic rate compared to the size. As the number of transistors for a given area also increases quadratically, the power density and total power for a given chip dimensions would be constant. Dennard postulated that as the technology scales, the delay and voltage would reduce, but the power density would remain the same, leading to faster, smaller processors which are power efficient as well. However, leakage current of transistors has started gaining relevance lately, which was not considered by Dennard. Leakage current increases the power dissipation of each transistor. Voltage scaling has not been achieved in the current technology nodes, especially threshold voltage has not reduced proportionally, leading to a higher power density. As the power dissipation of the chip increases, the temperature increases as well. Warmer chips age faster [3] and such an aggresive ageing would lead to fault forming earlier.

The scaling down of transistor sizes have hence caused a renewed interest and focus on reliability. Reliability is also becoming an issue due to the molecular scale sizes of the transistors. Currently, the size of a transistor is close to 40 atoms in width [4]. As mentioned earlier, operating voltage of a transistor has not scaled at the same rate as transistor dimensions. So there is a higher electric field across narrower widths which greatly increases both the energy requirements and the possibility of leakage of charges caused by parasitic resistances. This leads to the eventual breakdown of the transistor.

Another factor affecting reliability is the variability in the properties of various transistors within a chip. This is caused by the inability of the production environments to guarantee consistency, especially across multiple chips and also within a single chip. This has made current and upcoming generations of processors very susceptible to the occurrence of faults. Given the lowering dimensions, increasing electric fields and variation within the already small dimensions, the chances of a transistor breaking are substantially increased. Due to such effects, a variety of faults are formed during operation of a system.

The slowing down of processor voltage has been accompanied by a slowing down of the frequency of the processors as well. Since 2004, processor frequencies have found a ceiling of 5 Ghz. Most processors available now have their peak frequency below 4 Ghz. This clear throttling of application speeds on current and future generations of processors has to led to a situation where the current generation of processors can achieve acceptable levels of performance across multiple generations of processors. For example, the singlethreaded performance of a processor released in 2010 (Intel Core i7–2700k) [5] is within 10–15% performance margin of a processor released in 2015 (Intel Core i7–6700), and within 22% of a processor released in 2017 (Intel Core i7–7700k). Moore's law would have suggested a 10X performance difference between the processors. Similarly, the top two processors on the single thread performance list are the Core i7–7700 and Core i7–4790, both having comparable performance despite the fact that they were released 3 years apart.

Despite the issues with reducing performance gains, the situation also presents an opportunity for cost savings to the end customer. A fault tolerant processor has a longer lifetime, reducing the cost of ownership for the end user. Manufacturers have clear advantages in terms of increased fabrication output, allowing immediate financial gains. Hence, a processor with fault tolerance and a longer lifetime has clear benefits.

#### 1.1 Hypothesis of this dissertation

This dissertation shows work done to handle hard faults in processors. Logic blocks internal to the Processor are the primary targets in this work. Processor peripherals or the memory system is not considered in this work. The methods are suited for hard faults but are useful for handling soft faults as well.

**Hypothesis:** Given an out-of-order superscalar processor with hard faults in the logic components, a method can be developed, which can tolerate errors generated by these faults without switching off any faulty components.

Definitions: In the above statement and rest of this dissertation, faults refer to actual

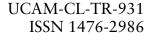

Figure 1.1: Overview of dissertation structure

hardware deterioration, *faulty component* refers to a circuit having a fault in it, and an *error* is a variation in the output of a faulty component from a fault-free case given the input. As can be inferred, the presence of a fault does not mean the occurrence of an error every time the faulty component is used.

#### **1.2** Contributions of this dissertation

Given the hypothesis of this dissertation, this work presents REPAIR, FaultSim and PreFix as the three major contributions towards achieving it.

The first contribution is a fault-tolerant architectural design named REPAIR, where the faults are tolerated by re-executing instructions which use faulty components on a remote accelerator. REPAIR allows instructions to be executed on the faulty component, and updates the result if the faults occur. The comparison is done post execution, the pipeline operations are halted pending the re-execution. On the availability of the results, the necessary registers are updated and the regular operation of the processor pipeline continues. REPAIR shows good performance in the presence of multiple faults especially in large structures. Further, it was seen that the performance of re-execution based fault tolerance is within acceptable levels.

FaultSim is the next contribution of this dissertation, which is a fast fault simulator capable of up to 300,000 32-bit addition operations per minute. FaultSim is also able to simulate numerous fault models. It is able to do so while providing transistor level simulations. FaultSim provides a simple interface for designing components, allowing easy simulation as well. Due to its simple interface, it can be easily integrated into architectural simulators.

PreFix is the final contribution of the dissertation; it has a conservative re-execution policy and the does not halt the pipeline. Both are clear improvements as compared to REPAIR. The performance is also significant, with median slowdown less than 5% compared to the fault-free case. Prediction, detection and permissive re-execution are used to handle faults. It is shown that even a conservative prediction of faults can reduce the overheads significantly. An interesting observation of the above mentioned fault tolerance systems is that, for multicores, on specific benchmark combinations, the performance of a fault tolerant system is better than a fault-free system.

This dissertation brings together three methods, which are inter-related. Figure 1.1 presents an overview of the relationship between the three. REPAIR is the foundational work, the results from which are used to create further sub-problems related to a fault acceptive methodology. Some of these were analysed using FaultSim and the results were used by PreFix to create a fault-tolerant system.

#### **1.3** Dissertation framework

In Chapter 1, the different concepts relevant to later discussion are briefly introduced, such as faults and processor types. Then Chapter 3 presents REPAIR, which is a preliminary work on profile based re-execution of erroneous instructions. Results which clearly show the advantage of having an external re-execution based system is shown. Next, FaultSim Chapter 4 is presented, which is a fast fault simulator. It is the fastest Gem5 integrateable fault simulator available. Chapter 4 further presents the characterisation of faults and its effects on the output for a set of circuits. Chapter 5 discusses PreFix, which explicitly uses both prediction and detection to speed up the handling of hard faults and handling it as if it is a soft fault. The results clearly show that the results are faster than switching off the component. Chapter 6 concludes the discussion and presents a short discussion on the attempted solutions for the hypothesis of this dissertation.

### Chapter 2

## Background

Handling faults in processors is the central theme of this dissertation and this chapter gives a brief introduction to them and to the various solutions for this problem available in the literature. The discussion on the solutions is detailed using the different processor architectures they target. The next section details the different type of faults that can be found in a processor.

#### 2.1 Types of faults

Faults in this context are any permanent or temporary variation from the expected behaviour of the circuit, caused by either electrical or structural anomalies in the circuit. The presence of such non-ideal variations can lead to errors in the output of that component. Faults in the internals of a processor can affect the larger system it is part of, if the errors generated permeate through to the next stages, which can lead to cascading failures. Hence, the understanding of both the types of faults and their effect on the system is of interest. The types of faults that can be present in a processor include transient errors, permanent errors and inconsistently occurring permanent errors, also known as Goldilocks errors [4].

#### 2.1.1 Transient faults

Transient faults, also called as soft faults are temporary and are triggered by an event external to the point of effect [6]. They are generally caused by radiation as well as system internal events such as coupling and supply noise. Transient faults are temporary and do not cause any permanent damage to the system. Despite the short-term nature of the faults, the possibility of one being caused at any point of time (temporal spread) and at any place on the circuit (spatial spread) causes substantial difficulty in dealing with them. Due to the unpredictability of the temporal and spatial spread of the fault, faulttolerance using historical data is not a practical solution. Predictive methods are hence not a possibility, transient faults are handled post detection. Once the errors are detected, they are handled by correcting any side effects it would have caused. In processor-based systems, errors manifest as incorrect value in the affected component or the buffer that gets the value from the component. Fixing these errors involves data redundancy or execution redundancy either spatially or temporally.

#### 2.1.2 Hard faults

Hard faults, on the other hand are permanent. Hard faults are caused by fabrication issues and usage related deterioration. They affect the output of the system from the Time of Formation (ToF). ToF is either the time of fabrication of the chip or later in the lifetime of the processor. Fabrication time issues are caused by imperfections in the fabrication process. Typically, the faulty chip will have substantial faults and portions of it are switched off if possible to deliver a working processor. In the case of minor fabrication issues such as process variation, the produced chips have transistors and other circuit elements with non-uniform electrical properties. This leads to the different parts of the chip deteriorating at a different rate and some will age much faster than the rest of the chip. Along with lifetime degradation issues, this can create hot-spot points, which quickly age and hard faults form.

In contrast to the probabilistic nature of transient faults, hard faults are deterministic and are caused by degradation over time. With sufficient early detection methods, hard faults can be predicted ahead of time if needed.

Another issue with hard faults is irreversibility. The formed faults will persist across the remaining lifetime of the processor. Despite this, hard faults are not terminal to the processor. Formation of error would depend on the location of the fault, usage of the faulty component and the set of inputs to the faulty component. Hence, every input would not lead to an error.

Compared to transient faults, hard faults have received less attention, largely due to the perception that hard faults are a start of life and end of life event and the operation time cost of hard faults is negligible. If the number of chips that are marked as not fit for purpose post-fabrication are considered, a better economic sense of the issue can be developed. For example, a study [7] presented that 40 to 60% of chips on average are fabricated faulty. The large numbers as such point to economic losses for both the chip manufacturers and the processor companies. Fabrication related faults could be handled by increasing the inherent hard fault tolerance in the processor designs.

#### 2.1.3 Physical causes of hard faults

Hard faults are mainly caused by one of the following causes:

- 1. Process variation and manufacturing defects: During the manufacturing process of processor chips, the possibility of significant variations in the fabrication process can lead to non-uniform chips being manufactured. This causes variation in circuit parameters including channel length, threshold voltage and wire spacing [8]. Such a variation in one extreme means that a very large portion of chips would be immediately made useless, while a large portion would have weak frequency and voltage responses indicating a short lifetime, and these would typically fail quality checks. The eventually available processors would have assymetry w.r.t. electrical properties across the chip. Hence, the time to failure of various parts of the processor would be different from the onset itself.

- 2. Negative Bias temprature instability (NBTI): When PMOS transistors are placed under the effect of negative bias, causing gate oxide breakdown [9]. This causes an increase in the threshold voltage and decreases the drain current.

- 3. Hot Carrier Injection (HCI): When electrons gain sufficient energy, they inject themselves into the dielectric region of a transistor, causing damage to the oxide [9]. This can lead to the degradation of electric properties, and is quite similar to radiation damage that is experienced in deep-space.

- 4. Time dependent dielectric breakdown (TDDB): The application of a low electric field over time causes the gate oxide of a transistor to break down causing a conducting path to form. This causes the transistor be stuck at the same logic level [10].

- 5. Electromigration: The movement of material due to the movement of charged particles through a medium causes electromigration. This affects the channels through which electrons move. Though this is an important phenomenon, it is considered a lesser issue than NBTI and HCI [10].

NBTI, HCI and TDDB cause the transistor parameters such as mobility and threshold voltage to change. This effectively increases the circuit level parameters, especially the delay and increases the threshold voltage. The increase in delay reduces the maximum frequency of operation. To keep an aged transistor active, the voltage would also need to be increased, or the frequency needs to be reduced. Both have processor-wide effects as each processor will be within a frequency and voltage island [11], and hence any changes to voltage or frequency would be applicable to every element on that island. Hence, the frequency of the processor and its voltage requirements would be driven by such aged transistors.

#### 2.1.4 Goldilocks Errors

An intermediate state between hard faults and soft faults happens when the operating conditions are not suitable for the circuit due to manufacturing issues [4]. The hardware would be seen as capable of accurate operation under certain constraints, but would fail otherwise. It is notable that the process of aging can also cause similar faults when the circuit begins to reach its end of life.

#### 2.2 Comparison of Hard and Soft faults

Hard faults are caused by the wearout of the circuit due to usage, whereas soft faults are caused by environmental reasons. Assuming that the environmental events are random and are spread uniformly in space, the probability of a soft fault,  $p_{sf} \propto Area$ . The environmental conditions are independent of the operation of the processor, hence the probability of a soft fault is independent of the past state of the processor. The probability of error being caused by a fault is also independent of any previous faults. Errors may propagate through the system, but faults act as independent events. Soft faults are hence spatially and temporally independent. This is useful for n-modular redundancy schemes where single-event-upset [12] has a low probability of affecting a majority of the redundant components. Additionally, soft faults gained importance from technology node of 90nm [13]. At this size, the energy of a 1.5MeV alpha particle is less than the inverter switching energy. An alpha particle strike would not change the value held in an inverter built at that technology node. All technology nodes smaller than 90nm have the possibility of the value changing due to an alpha particle strike.

Hard faults on the contrary are dependent on the time of operation of the processor, and hence cannot be treated as independent events. Using the NBTI and HCI equations, the deterioration of a component is  $\propto f(\sqrt{T})$  [9], where T is the duration of usage of a component. Any two components with similar usages will develop faults at times close to one another. Additionally, such faults are permanent. Hard faults hence have temporal dependency. N-modular redundancy schemes that are active for the same duration of time would have similar chances of hard-faults manifesting in them. In a perfectly symmetrical system, where the initial state of the system (electrical and physical properties) are identical and the same application is run on the replicas with the same operating conditions would lead to the same flaws occurring in the replicas, and hence the faults would not cause the behaviour of the replicas to deviate. This would allow errors to pass through as the replicas would give out the same erroneous result. Hard faults are hence dependent on the usage of a given component, and if two identical components have run the same application, they will, with very high probability, form hard faults at matching locations. Given that usage can be correlated in both space and time for any given pair of components, hard faults are neither spatially nor temporally independent. Hence, solutions for soft faults which are built on the premise of spatial and temporal independence of faults would not be an immediate fit for handling hard faults.

The direct consequence of this is on voting based schemes such as Triple Modular Redundancy (TMR). TMR relies on spatial and temporal independences, given that the errors caused by hard faults are dependent, active fault tolerance methods are not always ideal solutions for handling hard faults. A similar critique can be made for always active hardware redundancy schemes such as DIVA, where the possibility of fault formation increases over time quite similarly to the ones in the processor. Cold sparing is hence a more feasible mechanism for hard fault tolerance. REPAIR is one such strategy, where a cold spare in a separate location on the chip is provided that is used only when needed. Also, two processors running different workloads over time would develop different kind of faults, hence coupling processors can lead to better fault tolerance solutions. One such method is explored in PreFix. REPAIR presents a way of using minimal spares, whereas PreFix focusses on reusing faulty processors. In summary, soft-fault tolerant solutions focus on reducing the window of space and time in which a transient fault can cause an error in the processor. On the contrary, hard fault tolerance focusses on providing viable spares or by reusing faulty components.

#### 2.3 Overview of Fault tolerance strategies

Fault tolerance is not restricted to hardware-level solutions. It is a well studied problem in scales varying from large clusters, distributed systems and software, to processors. The error causing mechanisms and the semantics of their effect on the system are varied, but the fundamental methods of tolerating the faults have several common features. In this section, the various generic strategies devised to handle faults are discussed.

Fault-tolerance strategies can either be built for a hardware system or a software system. Hardware systems are either a cluster of multiple machines or a single machine with multiple or a single processor. Software systems have an analogy to the hardware systems, wherein, they are either a multi-machine software or a single-system software.

The solutions that will be discussed below target a system whose size or granularity would be either that of a multi-machine cluster, or of a single machine at its various software/hardware hierarchy of Operating system, application-level, compiler or multiprocessor level or at a single processor level. Any solution which addresses all the above would be called a full-closure method. Though both hardware and software fault-tolerance systems take care of multiple points of failure such as network, power distribution network, storage etc. In this discussion, we would focus only on faults in the processor and the methods used to handle them. A detailed discussion on this is available in [14]. A short summary of the methods follow here:

- Redundancy: Redundancy has different implementations for hardware and software. Hardware redundancy [15, 16] is either Dual or Triple redundancy, the generalisation of which is N-number of component redundancy. Software redundancy on the other hand is replication of operation and verification of the results. The support for such can be from the user-level, compiler level or the Operating-system level [17].

- Recovery: Recovery is the process of dealing with an error once it occurs. There are two methods of doing so, namely checkpoint recovery or by using forward error correction. Checkpoints are either micro-checkpoints at the level of process registers, or at process level, where the checkpoints reflect the status of the process at a time. The largest checkpointing mechanism is a system level checkpoint, where the entire state of the system is stored. Micro-checkpoints are characteristic of processor-level fault tolerance systems, whereas process level checkpointing needs software-level interference at either one of OS, compiler or application level. System-level checkpointing [18] has the highest requirements in terms of complexity and storage requirements. Typically, it is present in systems where clear system snapshoting is possible. Though typically not used for running-systems due to various complexities, system-level checkpointing can be found in architectural simulator like Gem5 [19] or any database [20].

- Migration: Migration is the process of shifting operation of a running system from a faulty system to a currently functional system. For clusters, this means shifting the responsibilities of a machine to another one in the cluster, and in multi-processor systems, this means switching a task from one processor to another one. In either scenarios, the migration policy would be triggered on the event of a failure or the future possibility of one. For a multi-processor machine, a workload which would not accurately run on a faulty machine can be migrated to one in which it can run failure free; or a newly faulty processor is retired by migrating tasks away from it. Migration is a pre-emptive action on a running node. Hence, the node will be active while migration is taking place.

- Failure Masking: Failure-masking allows failures to happen and the system would then react to the event and re-configures to hide the effects of the failure. Failure masking is a reactive method, operating after a failure occurs. This method requires clear indications that the failure has occurred requiring error detection. One of the common application scenarios is when the failure is fatal and the failed machine cannot recover from it. In large scale systems, this is supported by repeating the tasks running on the failed machine, on a different machine. An example can be found in Hadoop clusters, where individual tasks are provided to a single machine

and on failure, other machines take up tasks assigned to the failed machine and complete it. Compared to recovery, failure-masking assumes a system that cannot be immediately brought back into full functionality without intervention.

#### 2.4 Cost metrics of Fault Tolerance

The cost metrics of fault-tolerance are: reliability, area, power, performance and price. Reliability is measured by calculating the Mean time to failure (MTTF). MTTF is the expected time for a system to fail in the first instance. Once a failure happens, reliability is defined by Mean time between failures (MTBF). Given that this work focusses on handling hard faults, hence we focus on the MTBF of a processor. The overhead in terms of area covers both the area on chip and any additional resources that need to be added. For example, in system level checkpointing, the space needed to store the checkpoints can be significantly large and would likely be stored on a hard-disk drive. This adds an area overhead which may not be accounted for in a chip-level area computation. Power relates to the additional electric power required by the system to perform its functions. Power consumption increases the running cost of the system. Performance quantifies the increase in the time taken by a program running on the hardware. In this dissertation, it is measured as the percentile increase compared to a fault-free system. The monetary price of fault-tolerance consists of both design costs and run-time costs. Due to design costs being driven by market factors and run-time costs being driven by the operating environment, a discussion on costs will be beyond the scope of this thesis.

#### 2.5 Processor architecture and Fault-tolerance

Fault-tolerance as discussed earlier presents a higher level view of the strategies that are usable for fault-tolerance. A discussion on the different fault-tolerance strategies based on the type of processor architecture is discussed in this section.

#### **2.5.1** Fault tolerance for processors

Hard-fault tolerance strategies greatly vary depending on the different sections of the processor and for different processor types. From a performance perspective, the best suited method for fault-tolerance is the availability of spares. Such redundancies can either be inter-core (spare is present in the core) or cross-core (spare is either shared across cores or is available on another core). Spares can be hot-spares (already active, and can be switched off when faulty) or cold spares (activated when an active components turn faulty). The recovery mechanism in the presence of faults depends on the redundancy available. Typically, once a fault is found, the faulty component is switched off and the

redundancy is used. The mechanism of usage depends on the spare is intra-core or crosscore. PreFix presents a cross-core design, where the faulty component is not switched off. This is contrary to the fault tolerance schemes currently available.

For systems where spares are not possible, different mechanisms for handling faults are employed. One situation is when a processor is running an application and a component in it develops an error. In such a situation, just the presence of cold-spares (and the absence of an aggresive fault detection mechanism) would not protect the system from having errors forming in it. Aggresive fault detection is also critical in such cases. Safetycritical devices such as medical devices, autonomous vehicles, navigational and guidance systems cannot tolerate such errors. Another scenario is when the area overheads are critical, in such cases, explicit spares would increase the total area, this is true especially in embedded and low power systems. In either of these scenarios, the provision of explicit spares would not be either beneficial or sufficient.

For registers, the ease of substitution is high, as local provision of spare registers with multiplexors to redirect reads and writes allow cheap sparing. For functional units such as an ALU or FPU, the space taken by an individual unit is a non-trivial portion of an individual core. In situations where the space taken by spares is of concern, the ALU and the FPU are shared across processors if needed. This work takes a similar approach, where REPAIR has a common pool of resources shared across different processors. In PreFix, similarly, the resources of a different chip are shared between processors.

It can be noted from this discussion that fault detection is an essential part of faulttolerance. Additionally, NBT and HCI induced ageing and degradation consistently reduces the performance of the processor. Eventually, the number of faults created due to ageing would be significantly higher than the maximum performance guaranteed by any fault-tolerance scheme. At this point, the processor would need to be retired. Hard fault handling methods focusses on providing some performance guarantees between the first hard fault and the time of retirement. Specific solutions for hard fault-tolerance are discussed in the later chapters.

#### 2.6 Summary

Faults of different types affect processors. The strategies to handle them are dependent on the application, processor design and costs involved. In the coming chapters, methods to deal with hard faults in out-of-order super-scalar processors are presented. These methods are also useful in handling faults in in-order processors. The effect of speculation and memory operations on these methods are also discussed.

## Chapter 3

# **REPAIR:** Accelerator based fault tolerance

This chapter presents REPAIR, a system that tackles faults in the processor core without the need for explicit spares. REPAIR is a minimal re-execution framework which will allow faulty components to do some amount of meaningful work without explicit duplication. REPAIR allows for remote re-execution using shared cold-spare components. Cold-sparing allows better protection from hard faults as the spare components have longer life left from the time of first fault as compared to hot spares [21]. Further, REPAIR also acts as a base from which key components are identified in the pipeline, faults in which can be catastrophic. The rest of the dissertation understands as well as mitigate effects of faults on the processor. Hence, REPAIR is the first building block, in tackling hard faults in hardware, of this dissertation.

Traditionally, methods to handle faults involved explicitly switching off components, or keeping them away from the critical aspects of the processor's functioning. REPAIR takes a different approach. Instead of swapping out faulty parts of the hardware, or keeping it running only to provide hints to other cores, the faulty cores are kept running and performing work. To do this the system is augmented with a small amount of logic containing only functional units and buffers that is termed here as an Instruction Reexecution Unit (IRU). Additionally, each core has a fault map, which store the fault state of all the tracked components (e.g., registers or ROB entries). It is either initialized by power-on self-test or periodic built-in self-test, to record faulty components within the core. REPAIR needs a dynamic periodic testing mechanism to deal with evolving faults as REPAIR cannot perform fault detection. Also, faults are generated at an exponential rate in the later phases of a processor's lifecycle [22]. Each instruction is monitored as it traverses through the core's pipeline and whenever it touches a component marked as faulty, its execution is aborted, re-executed on the IRU, and the results passed back to the original core. This requires minimal modification to a standard out-of-order super-scalar pipeline and, additionally, imposes no performance penalty unless and until a hard error

occurs. In this way multiple errors are tolerated in different components within each faulty core and the core generates correct results. This technique is named as REPAIR because it provides "Recovery from Errors in Processors by Allowing Instruction Re-execution".

REPAIR is evaluated as an addition to a single-core system, and as a shared resource within a multicore chip, showing that the expected performance for a single core is  $0.81 \times$  peak performance and for multicore with four errors in every core is  $0.68 \times$ .

The rest of this chapter is organized as follows. Section 3.2 discusses related work from the literature. Section 3.3 gives an overview of REPAIR and presents the IRU for re-executing instructions; how it can take a group of instructions whose execution faulted on the main core and re-execute them. Section 3.4 explains how the IRU is connected to the main processor cores, explaining our specific use case which integrates the IRU with an out-of-order super-scalar pipeline with checking for faults at both the dispatch and commit stages. Section 3.5 details our experimental setup before Section 3.6 presents the results from single core and multicore deployments of REPAIR.

#### 3.1 Motivation

As discussed in Chapter 2, hard-fault tolerance is necessary for processors operating in circumstances where reliability is necessary. Also, there is a need to provide spares which would have a higher lifetime compared to the processor it is protecting. Cold-spares is one such method, where the lifetime of the spare is significantly higher than that of the processor it supports. Additionally, there exist use cases where providing extensive spares is not possible. In all such cases, the processor would need to have in-built fault-tolerance mechanisms which are light-weight in both area and power. Given that the cold spares are not active in a fault-free scenario, they do not incur any faults during that phase. Hence, any additional steps to protect them from faults, such as increasing their geometry is needed. To protect REPAIR from fabrication faults, it would be useful to fabricate it in a higher geometry, but not necessary. REPAIR is designed to provide graceful end of life for a processor without the addition of substantial area or performance overheads.

#### 3.2 Related work

Significant work has addressed hard faults and methods for continuing to use erroneous components despite their errors. The first issue to focus on is that of fault detection. DIVA [23] provides a solution for dynamic detection of errors by incorporating a functional checker at the commit stage of a superscalar pipeline. Results from computations on the main core are sent to the DIVA checker for comparison with the values generated there, and differences flagged up as an exception that can be handled by flushing and restarting. Although similar in some aspects to REPAIR, DIVA requires full execution of

all instructions to detect and correct errors, whereas REPAIR only re-execute instructions that may have incurred an error, meaning there is no performance impact for correct instructions.

BlackJack [24] is an architectural scheme to detect hard errors by running redundant threads on a single SMT core. By providing duplicate execution of a program, application state can be compared at key points and differences discovered. In contrast Rescue [25] presents a micro-architecture that identifies and avoids hard errors. Using scan chains and automated test pattern generation, a Rescue core can be quickly locate faulty components which are then isolated and mapped out from the core, exploiting the natural redundancy available. Finally, Constantinides et al. [26] extend the ISA with new instructions that leverage the scan chains to probe any microarchitectural component, thereby isolating faulty structures that are usually unavailable to the software. These schemes do not directly approach fault tolerance, but REPAIR can use these approaches to periodically probe for errors and fill in the fault maps that are used to identify whenever an instruction requires re-execution.

Once errors have been detected they must be corrected, usually through the use of redundancy. Srinivasan et al. [15] add extra redundant resources for key microarchitectural structures which can be used in the event of a fault in original. Graceful performance degradation makes use of the pre-existing spares in other logic to turn off parts of a structure that have errors, maintaining functionality at the expense of performance. Architectural core salvaging [27] uses the natural redundancy across cores to avoid structures with defects. When an error occurs, the executing thread can be migrated to a new core or swapped with a thread that will not make use of the buggy hardware. Architectural redundancy is used in StageNet [28] and StageWeb [16] by providing a network of pipeline stages. The network can be configured to work around faulty stages, creating logical cores that are distributed about the chip. Similarly Romanescu and Sorin [29] present a scheme to cannibalize cores at pipeline granularity, arranging cores into groups so that the cannibalized cores can donate spare pipeline stages to nearby cores. Cobra [30] has a distributed execution model where instructions are batched and executed based on resource availability. All these schemes rely on turning off parts of the core or chip that are faulty. REPAIR, in contrast, allows continued use of the faulty hardware but re-executes instructions that have touched these faulty resources.

Necromancer [31] uses faulty cores to enhance the performance of others by providing hints to another animator core. Although the animator has a lower specification to the other cores, by using hints from the faulty core its performance can be close to that of the fully functioning cores.

ReCycle is a method for tolerating process variation within the processor's pipeline [32] via cycle time stealing and the addition of donor pipeline stages. With these alterations the pipeline can be clocked with a period close to the average stage delay, rather than

being dictated by the slowest stage. There has also been research to take advantage of micro-architectural redundancy to improve the performance average yield [33].

Other schemes have used software to avoid hard errors. A coprocessor was presented by Rajendiran et al. [34] to execute instructions that cannot be run correctly on the main core. Hard faults on the base processor are known by the compiler and appropriate calls are placed in the software to execute those instructions on the co-processor. Detouring [35] is a compiler method to translate software so that it doesn't use faulty components. ALU operations can be converted to logical counterparts and errors in the register file, bypass network and instruction cache can also be dealt with. Rosy [17] uses the operating system to execute software on unreliable cores. Thread relocation [36] uses a hypervisor-based system to handle errors by mapping software to appropriate cores for execution. REPAIR, on the other hand, focuses on providing hard error tolerance in hardware only, avoiding the need to recompile software for a faulty core.

A performance analysis of different architectural and non-architectural arrays in the presence of errors across different technology nodes has been presented by Hardy et al. [37]. Their analytical model considers the performance impact of faulty cache cells being turned off, reducing capacity and leading to additional misses, and faulty predictor entries causing increased mis-predictions. They show that at 22nm the impact of SRAM cell failures are low, but that performance degrades noticeably at lower technology nodes. A discussion on performance-based reliability measures for computing systems has also been presented by Beaudry [38].

Finally recent work has considered approximate compute where errors are allowed to occur and tolerated rather than corrected [39, 40, 41]. Although this is suitable for a certain class of application, the majority of programs require exact computation and cannot survive errors in the underlying fabric. REPAIR is a general technique that provides error recovery for a processor, and is not targeted towards any class of applications.

#### 3.3 REPAIR

The REPAIR architecture <sup>1</sup> allows a faulty core to continue correct execution by rerunning potentially-erroneous instructions on a new, specialized instruction re-execution unit (IRU). This unit provides external redundancy for instruction execution and can be shared by a number of cores in the system. Compared to existing methods, which rely on either forcing internal redundancy or using the faulty core to provide hints to the error-free cores, our approach focuses on getting useful work done on the faulty core, assisted by external logic. The design of IRU is discussed in this section; Section 3.4 describes how the instructions that need to be re-executed are identified.

<sup>&</sup>lt;sup>1</sup>This work has been published at DFTS 2015 [42]

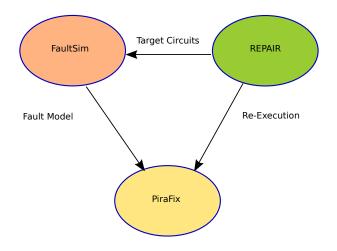

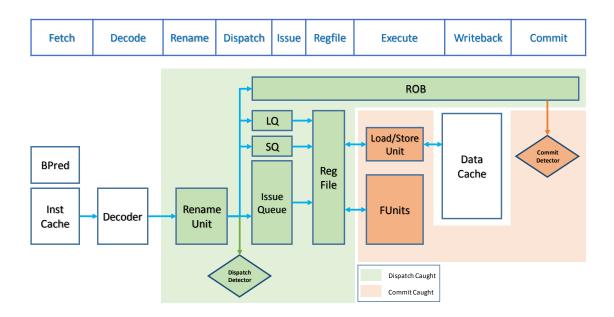

Figure 3.1: REPAIR overview.

#### 3.3.1 Overview of the REPAIR architecture

The REPAIR architecture consists of standard cores, with minor extra logic to support REPAIR, and an IRU, which is used to rerun instructions that are faulty. It contains a mechanism to identify instructions that have, or may have, used erroneous hardware and transfer them to the IRU, writing the results back to the faulty core afterward. The IRU sits alongside the core that it supports, and in a multicore system can be shared between a number of cores. An overview is shown in Figure 3.1.

The REPAIR interface to the cores can be split into two parts: one for fault detection and the other for re-execution. The first part monitors instructions within the pipeline, checking each one to ensure that no logic with hard errors has been used while processing. The instruction resource usage are tracked at two points within a superscalar pipeline (dispatch and commit) to quickly catch instructions using faulty hardware with minimal intrusion into a core's internal logic. The second part re-executes an instruction that has used a faulty structure by squashing it and all subsequent instructions (if necessary), then passing it on to the IRU. Once the result is returned, execution continues with the first instruction after the fault.

It is important to note that REPAIR doesn't solely intercept instructions that definitely have an error, but in fact replays all instructions that *may* have an error. This keeps our monitoring circuitry simple, yet still guarantees that all faulty instructions will be caught.

#### 3.3.2 The REPAIR Re-Execution unit

The instruction re-execution unit used in REPAIR is a simple circuit that executes one instruction, or a group of consecutive instructions from the same core, using operands and data read from that core. The IRU does not need all the components of a standard

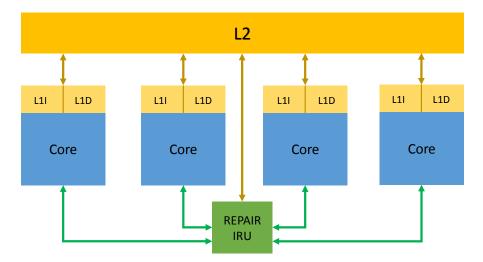

Figure 3.2: Overview of the IRU.

processor; in fact it only requires buffers to hold instructions and their results, along with functional units to execute them. The basic IRU is shown in Figure 3.2 and consists of an interface to the main cores, input and output buffers, execution units, an operand manager, to deal with dependences between instructions, and a memory manager, to perform loads and stores.

The core interface is responsible for managing groups of instructions coming from the main cores. The IRU only executes instructions from a single core at any point of time; where more than one core wishes to use the IRU, the core interface arbitrates for access in a round-robin fashion.

Once a core has been chosen to use the IRU, it starts streaming the instructions and data to be operated on (i.e., register values) into the IRU where they are placed in the input buffer. Instructions wait here until execution units are available to execute them, and can start while further instructions continue to be streamed in. Instructions are executed from the input buffer in order and their results are placed in the output buffer, along with the destination architectural register ID. The output buffer keeps a mapping between architectural registers and the values that are generated within the IRU, coalescing multiple writes to a single register to reduce the data that needs to be sent back to the core. The execute unit of the IRU contains one copy of each type of functional unit appearing in a standard core. Although the IRU can execute any number of instructions from a core, REPAIR only uses it with sequences of micro-ops from a single macro-instruction at any one time. Accordingly, the IRU contains a simple pipeline and operand manager to handle such cases and avoid round-trips between the core and the IRU for each instruction within a group from the same core.

REPAIR also maintains precise exceptions by marking any instruction that causes an exception within the output buffer. Once this instruction has been transferred back to the core, exception handling deals with the issue as normal.

#### 3.3.3 Source operands

Sitting alongside the execution units and buffers is the operand manager. Its job is to identify the location of the input operands for the execution units. The majority of data values are sent over with each instruction from the core. However, for a group of instructions there are two other sources. First is the bypass network between the functional units, which is included to provide back-to-back execution of dependent instructions. Secondly, input values may have already been generated by an earlier instruction and reside within the IRU output buffer.

The operand manager handles dependences between a group of instructions executing on the IRU by scanning the source operands of the oldest instruction and providing the most recent value of each to the execution units. It first chooses to source values from the bypass network, then the output buffer, and finally the input buffer if the register has not yet been generated by the IRU.

Figure 3.2 shows an example of how the operand manager works. In this example, a load instruction has already executed and generated the value of register r1, whose result is in the output buffer and marked as such in the operand manager. In execution is an add instruction which will generate the value of r0, which is marked as being available for bypass in the operand manager. It reads r2 which has not been generated locally by the IRU (marked invalid within the operand manager), so it uses the value for r2 that was sent over by the core. Finally, there is a compare instruction in the input buffer, which will compare the values of r0 and r1 with each other. When the compare instruction moves to the execution units the operand manager will provide r0 from the bypass network and r1 from the output buffer, ignoring the values of r0 and r1 that were sent from the core.

#### **3.3.4** Memory instructions

The memory manager of the IRU is responsible for handling memory operations that need re-execution. It performs address translation using the core interface as well as directly accessing the L2 cache either to read data or to write it.

The IRU does not contain a TLB, therefore virtual-to-physical address translation is handled by the original core's TLB through the core interface. Providing a TLB within the IRU would add significant complexity with little benefit. This complexity would arise from servicing TLB misses and ensuring that only the pages available to the core could be accessed by the IRU. Either the OS would have to be made aware of the IRU and the core it was currently executing instructions for, or the IRU would have to present itself to the OS as this core. In addition, since it is expected that the IRU is going to be used infrequently, there would be little temporal or spatial locality between the memory pages that would be accessed by the re-executed instructions.

After performing address translation, the IRU directly accesses the L2 cache. Again,

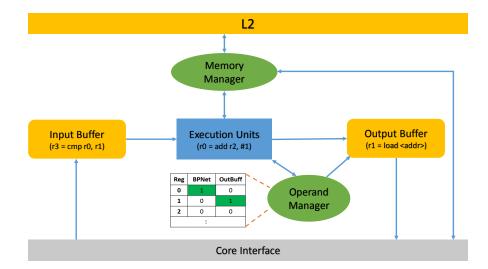

Figure 3.3: Detection stages within a core.

due to the infrequent nature of instruction re-execution, significant locality between memory addresses accessed by the IRU would not be expected. Providing an L1 cache would also mean an extra cache for the coherence protocol to consider (if a shared L2) or would mean introducing coherence between the IRU L1 and the core's L1 (where there is a single IRU for each core and a private L2). Hence the IRU has a connection to the shared lastlevel cache. Our method makes a strong requirement about the cache-coherency protocol accepting the shared last-level cache as a valid level for storing modified data.

#### 3.3.5 Summary

REPAIR works by identifying instructions that may have used faulty hardware within the main core and sending them to a re-execution unit to be executed again. This unit can be shared by multiple cores, but handles groups of instructions from a single core at a time. It contains buffers for holding instructions that are waiting to execute, as well as an operand manager for handling dependences between instructions. After execution of the whole group, results are written back to the core, the IRU is reset and normal execution can continue. The next section describes how REPAIR interfaces with the cores to actually identify faulty instructions and prepare them for re-execution.

#### **3.4** Integration with standard cores

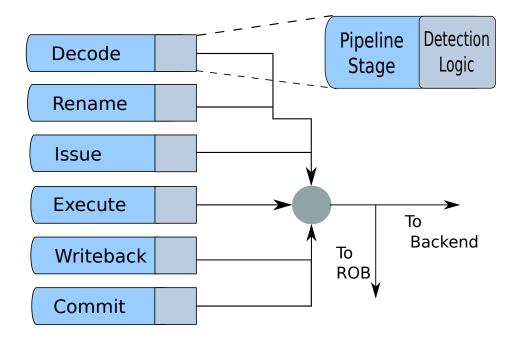

REPAIR is designed to require minimal integration into a standard out-of-order superscalar pipeline. It detects the use of faulty components at instruction dispatch and commit and takes advantage of existing branch mis-prediction logic to squash dependents of faulty instructions if necessary. This section first describes how instructions with potential errors are recognized, then discusses the core's operation in the presence of faults. Figure 3.3 gives an overview of how REPAIR is integrated into a superscalar pipeline.

#### 3.4.1 Fault coverage

REPAIR protects the SRAM cells within the architectural arrays <sup>2</sup> used to provide outof-order execution within a superscalar processor's pipeline, as shown in Figure 3.3. It deals with stuck-at faults in the rename table, register files, register scoreboard, re-order buffer, issue queue, load queue, store queue and functional units. Non-architectural arrays (e.g., branch prediction logic) where errors only affect performance and not correctness are not monitored as the aim is to preserve correctness rather than performance on hard errors. Other logic and structures within the core are assumed to be error-free. Therefore REPAIR expects valid, decoded instructions to be presented to the rename stage of the pipeline, from which it can take over, detecting faults at dispatch and commit.

Should there be errors in other parts of the core, a variety of alternate schemes can be used to continue correct execution, which are orthogonal to REPAIR. Caches nowadays are augmented with error detection or error correction codes [43]. Similarly, pipeline lanes can be turned off for errors in the fetch queue or decoders. In the extreme case, a core can simply be marked as faulty and powered down [44].

Faults can also occur in the hardware required for REPAIR. In this case, for correctness, it is simply assumed that the IRU does not work and cannot be used. Therefore a core can continue to run whilst it is error-free, but as soon as it develops a single error it must be marked as faulty. However, for the rest of this chapter, it is assumed that each core is fault-free in all the logic and circuits that are not covered by REPAIR and that there are no faults in any of REPAIR's hardware.

#### **3.4.2** Identifying faulty instructions

REPAIR identifies instructions that have used faulty processor structures through the use of fault maps at the dispatch and commit pipeline stages. The fault maps indicate the processor structures that have been detected to have hard errors within them and REPAIR compares this information with resources actually used. The fault maps themselves are periodically populated using built-in self-test [26]. As the faults increase with time, the frequency of testing for faults has to increase accordingly. BIST incurs performance loss for the system, and if the frequency of testing is significantly large, then the performance of the system would suffer. It is recommended to decrease the clock-frequency if the total performance of REPAIR lags below the frequency scaled value, and refill the fault maps accordingly.

A fault map is a simple array of bits for each structure where each bit represents the presence of fault in one entry of that component. For example, in our processor described

<sup>&</sup>lt;sup>2</sup>Arrays holding architectural state whose corruption could cause incorrect execution.

in Table 3.1 there are 32 entries in the issue queue, therefore the fault map for the issue queue contains 32 bits, each of which represents the presence or absence of an error in the corresponding entry.

The detector keeps a fault map for each structure that REPAIR covers within the core, and at every clock cycle checks instructions at the dispatch and commit stages to see if they have used, or will use, any faulty components. If so, they are marked for re-execution by the IRU. Since checking for errors at the dispatch and at commit stages are subtly different, their operations are described in the next two subsections.

#### 3.4.3 Dispatch checking

At dispatch REPAIR checks for errors in the ROB, IQ, LSQ, register scoreboard, rename map and physical registers. Instructions are checked for faults as they are dispatched into the reorder buffer and instruction queues. If there is an error in any of the entries that they are being dispatched into, then the corresponding instruction is marked as faulty and requiring re-execution. However, at this point, there is a problem with the validity of the instruction's bits that have been written. Since REPAIR makes the error checks at dispatch and does not find out until the end of the cycle that the instruction is using faulty hardware, the instruction bits in the previous pipeline latches would have already been overwritten. Yet the instruction bits that have been written into the queues cannot be used, since they may be erroneous. To solve this, a small buffer is provided that is the same width as dispatch (three instructions in our core) within the detector, called the dispatch-fault buffer. As the instructions dispatch, a copy of the instructions is also written into this buffer to allow access to valid instruction bits in the event that an error is found.

Once an instruction has been identified as faulting, its entries in the reorder buffer and other queues (and those of any younger instructions that have dispatched in the same cycle) are annulled to avoid them being executed erroneously. It is then held in the detector's buffer until the pipeline has drained as all older instructions commit, when it can be sent to the re-execution unit to be executed correctly. During this time an older instruction may flush the pipeline due to a branch misprediction or an error caught at commit. In this situation the instructions held in the dispatch-fault buffer are flushed too, meaning that they will not be sent needlessly to the IRU.