Number 870

# Accelerating control-flow intensive code in spatial hardware

Ali Mustafa Zaidi

May 2015

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 http://www.cl.cam.ac.uk/

## © 2015 Ali Mustafa Zaidi

This technical report is based on a dissertation submitted February 2014 by the author for the degree of Doctor of Philosophy to the University of Cambridge, St. Edmund's College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Abstract

Designers are increasingly utilizing spatial (e.g. custom and reconfigurable) architectures to improve both efficiency and performance in increasingly heterogeneous systems-on-chip. Unfortunately, while such architectures can provide orders of magnitude better efficiency and performance on numeric applications, they exhibit poor performance when implementing sequential, control-flow intensive code. This thesis studies the problem of improving sequential code performance in spatial hardware without sacrificing its inherent efficiency advantage.

I propose (a) switching from a statically scheduled to a dynamically scheduled, dataflow execution model, and (b) utilizing a newly developed compiler intermediate representation (IR) designed to expose ILP in spatial hardware, even in the presence of complex control flow. I describe this new IR – the Value State Flow Graph (VSFG) – and how it statically exposes ILP from control-flow intensive code by enabling control-dependence analysis, execution along multiple flows of control, as well as aggressive control-flow speculation. I also present a High-Level Synthesis (HLS) toolchain, that compiles unmodified high-level language code to dataflow custom hardware, via the LLVM compiler infrastructure.

I show that for control-flow intensive code, VSFG-based custom hardware performance approaches, or even exceeds the performance of a complex superscalar processor, while consuming only  $1/4\times$  the energy of an efficient in-order processor, and  $1/8\times$  that of a complex out-of-order processor. I also present a discussion of compile-time optimizations that may be attempted to further improve both efficiency and performance for VSFG-based hardware, including using alias analysis to statically partition and parallelize memory operations.

This work demonstrates that it is possible to use custom and/or reconfigurable hardware in heterogeneous systems to improve the efficiency of frequently executed sequential code, without compromising performance relative to an energy inefficient out-of-order superscalar processor.

# ACKNOWLEDGEMENTS

First and foremost, my sincerest thanks to my supervisor, David Greaves, for his careful and invaluable guidance during my PhD, especially for challenging me to explore new and unfamiliar topics and broaden my perspective. My heartfelt thanks also to Professor Alan Mycroft for his advice and encouragement as my second advisor, as well as for his enthusiasm for my work. I would also like to acknowledge Robert Mullins for his encouragement, many insightful conversations, and especially for running the CompArch reading group. Sincere thanks also to Professor Simon Moore, for seeding the novel and exciting Communication-centric Computer Design project, and for making me a part of his amazing team.

I would also like to acknowledge my colleagues for making the Computer Laboratory a fun and engaging workplace, and especially for all of the illuminating discussions on diverse topics, ranging from computer architecture, to the Fermi paradox, to the tractability of magic roundabouts. In particular, I would like to thank Daniel Bates, Alex Bradbury, Andreas Koltes, Alan Mujumdar, Matt Naylor, Robert Norton, Milos Puzovic, Charlie Reams, and Jonathan Woodruff.

My gratitude is also due to my friends at St. Edmund's College, as well as around Cambridge, for helping me to occasionally escape from work to try something less stressful, like running a political discussion forum! In particular, my heartfelt thanks go the cofounders of the St. Edmund's Political Forum, as well as to my friends Parul Bhandari, Taylor Burns, Ali Khan, Tim Rademacher, and Mohammad Razai.

Last but not least, I am most grateful to my wife Zenab for her boundless patience and support during my PhD, to my son Mahdi for bringing both meaning and joy to the life of a humble student, and to my parents for their unwavering faith, encouragement and support.

# Contents

| 1 | $\mathbf{Intr}$ | $\operatorname{oducti}$ | ion                                              | 11 |

|---|-----------------|-------------------------|--------------------------------------------------|----|

|   | 1.1             | Thesis                  | Statement                                        | 13 |

|   | 1.2             | Contri                  | ibutions                                         | 14 |

|   | 1.3             | Public                  | eations and Awards                               | 15 |

| 2 | Tec             | hnical                  | Background                                       | 17 |

|   | 2.1             | The U                   | Iniprocessor Era                                 | 17 |

|   | 2.2             | The M                   | Iulticore Era                                    | 20 |

|   | 2.3             | The D                   | Oark Silicon Problem                             | 21 |

|   |                 | 2.3.1                   | Insufficient Explicit Parallelism                | 21 |

|   |                 | 2.3.2                   | The Utilization Wall                             | 23 |

|   |                 | 2.3.3                   | Implications of Dark Silicon                     | 24 |

|   | 2.4             | The $S$                 | patial Computation Model                         | 26 |

|   |                 | 2.4.1                   | Advantages of Spatial Computation                | 26 |

|   |                 | 2.4.2                   | Issues with Spatial Computation                  | 28 |

|   |                 | 2.4.3                   | A Brief Survey of Spatial Architecture Research  | 31 |

|   | 2.5             | Summ                    | ary                                              | 36 |

| 3 | Stat            | tically                 | Exposing ILP from Sequential Code                | 39 |

|   | 3.1             | The N                   | Tature of Imperative Code                        | 39 |

|   | 3.2             | Expos                   | ing ILP from Imperative Code                     | 42 |

|   |                 | 3.2.1                   | False or Name dependencies                       | 42 |

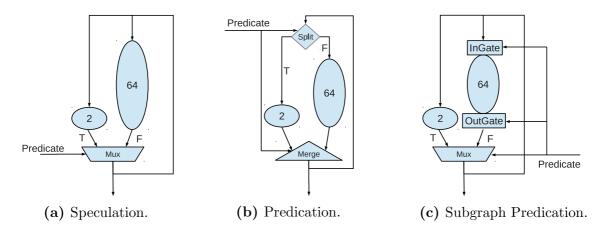

|   |                 | 3.2.2                   | Overcoming Control Flow                          | 44 |

|   |                 | 3.2.3                   | Pointer Arithmetic and Memory Disambiguation     | 46 |

|   | 3.3             | The S                   | uperscalar Performance Advantage                 | 47 |

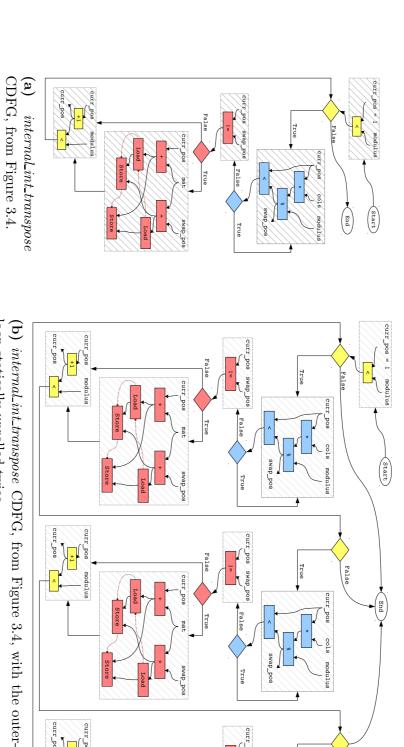

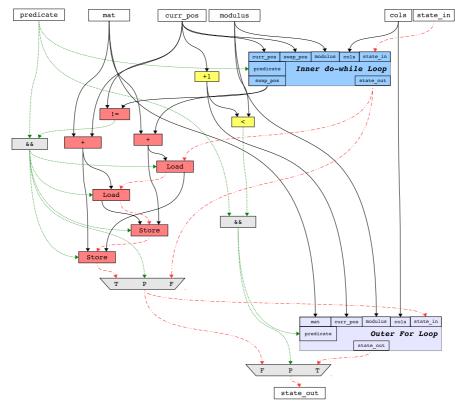

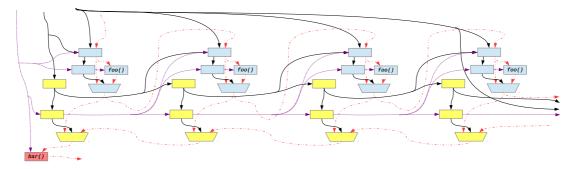

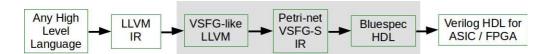

|   |                 | 3.3.1                   | Case Study 1: Outer-loop Pipelining              | 49 |

|   | 3.4             | Limita                  | ations of Superscalar Performance                | 52 |

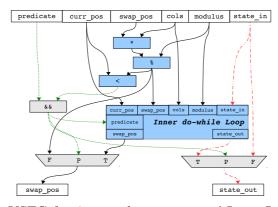

|   |                 | 3.4.1                   | Case Study 2: Multiple Flows of Control          | 52 |

|   | 3.5             | Impro                   | ving Sequential Performance for Spatial Hardware | 53 |

|   |                 | 3.5.1                   | Why the Static Dataflow Execution Model?         | 54 |

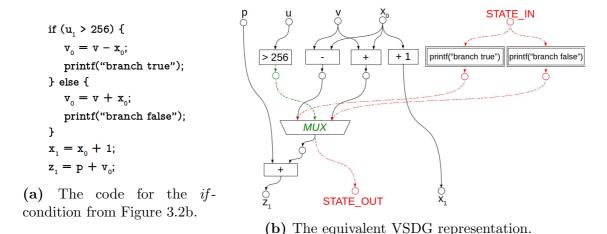

|   |                 | 3.5.2                   | Why a VSDG-based compiler IR?                    | 55 |

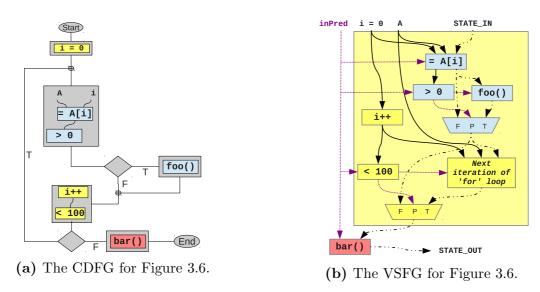

|   | 3.6             | Overce                  | oming Control-flow with the VSDG                 | 55 |

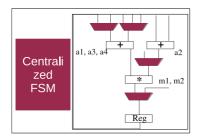

|   |                 | 3.6.1                   | Defining the VSDG                                | 55 |

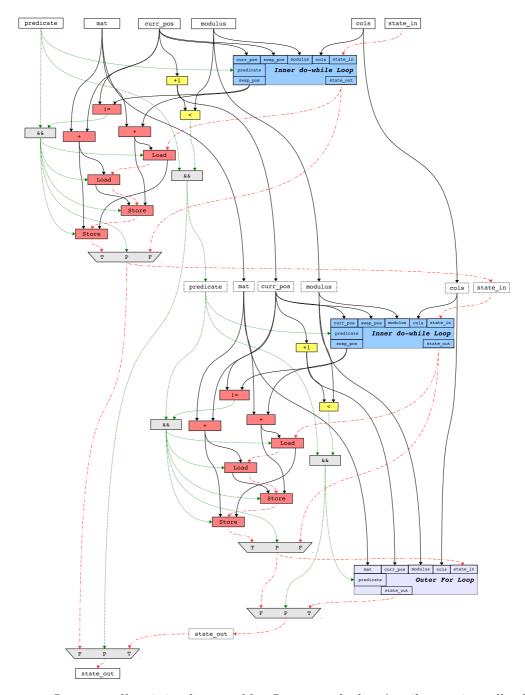

|   |                 | 3.6.2                   | Revisiting Case Studies 1 and 2                  | 64 |

|   | 3.7             | Relate                  | ed Work on Compiler IRs                          | 70 |

|   | 3.8             |                         | iary                                             | 72 |

| 4                              | Def   | inition            | and Semantics of the VSFG                       | <b>75</b> |  |

|--------------------------------|-------|--------------------|-------------------------------------------------|-----------|--|

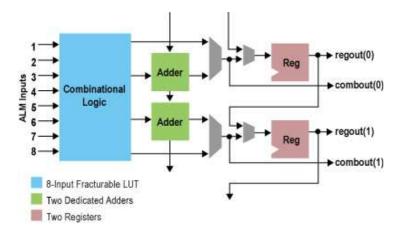

|                                | 4.1   | The V              | SFG as Custom Hardware                          | 75        |  |

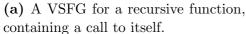

|                                |       |                    | ing Execution with Petri-Nets                   | 77        |  |

|                                |       | 4.2.1              | Well-behavendess in Dataflow Graphs             | 79        |  |

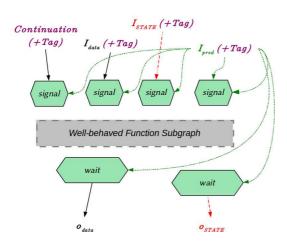

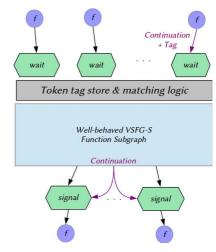

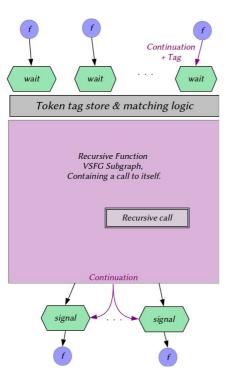

|                                | 4.3   |                    | tional Semantics for the $VSFG$ - $S$           |           |  |

|                                |       | $4.\overline{3.1}$ | Semantics for Basic Operations                  | 84        |  |

|                                |       | 4.3.2              | Compound Operations: Nested Acyclic Subgraphs   | 89        |  |

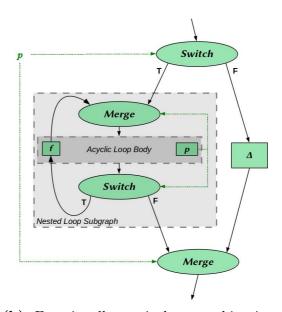

|                                |       | 4.3.3              | Compound Operations: Nested Loop Subgraphs      | 92        |  |

|                                | 4.4   | Compa              | arison with Existing Dataflow Models            | 100       |  |

|                                |       | 4.4.1              | Comparison with Pegasus                         | 100       |  |

|                                |       | 4.4.2              | Relation to Original Work on Dataflow Computing | 101       |  |

|                                | 4.5   | Limita             | ations of Static Dataflow Execution             |           |  |

|                                | 4.6   | Summ               | ary                                             | 107       |  |

| 5                              | A 3.  | SEC I              | Based High-Level Synthesis Toolchain            | 109       |  |

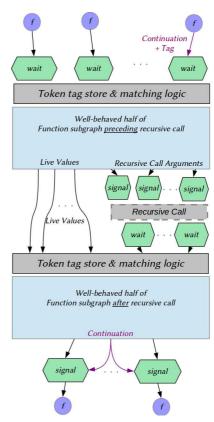

| 0                              | 5.1   |                    | oolchain                                        |           |  |

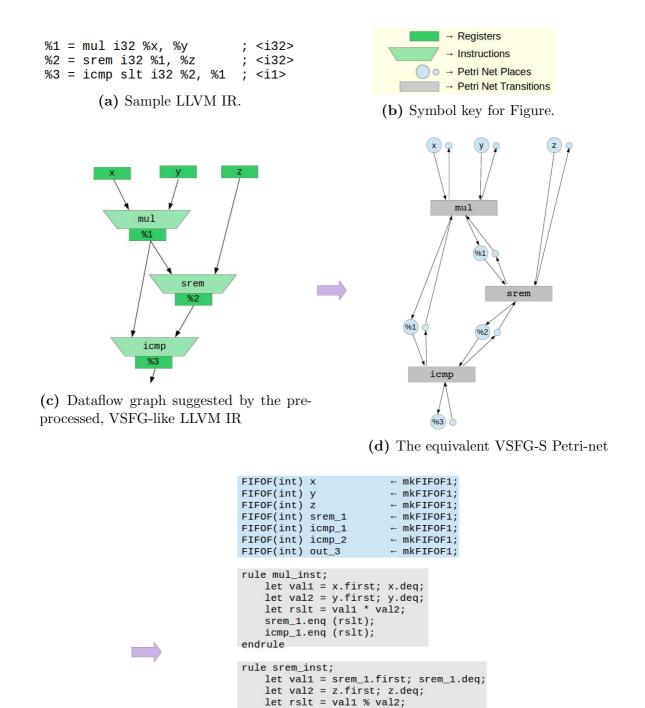

|                                | 5.2   |                    | rsion from LLVM to VSFG-S                       |           |  |

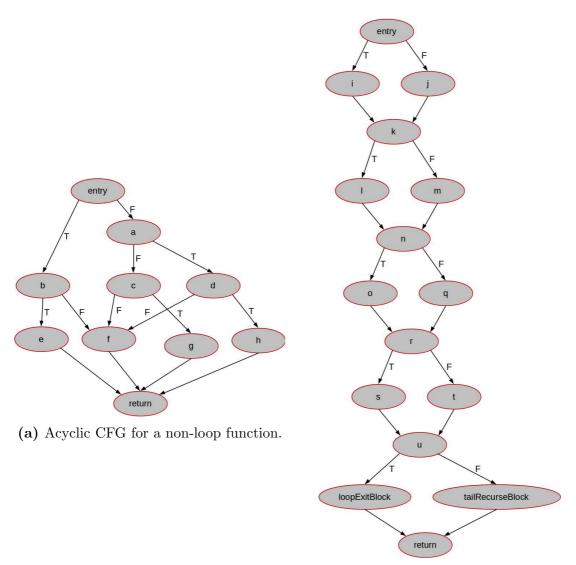

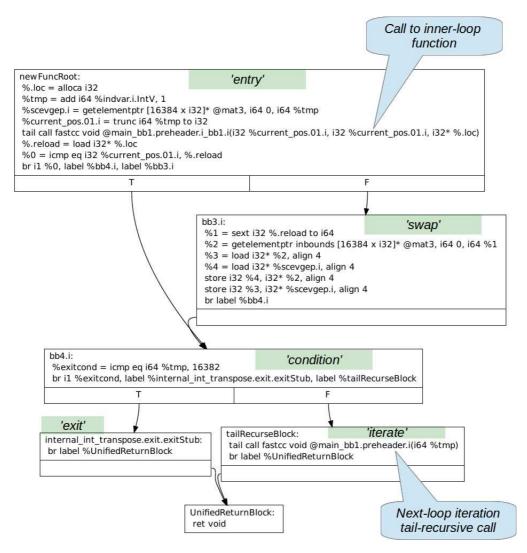

|                                | 9.2   | 5.2.1              | Convert Loops to Tail-Recursive Functions       |           |  |

|                                |       | 5.2.1              | Implement State-edges between State Operations  |           |  |

|                                |       | 5.2.2              | Generate Block Predicate Expressions            |           |  |

|                                |       | 5.2.4              | Replace each $\phi$ -node with a $MUX$          |           |  |

|                                |       | 5.2.5              | Construct the VSFG-S                            |           |  |

|                                | 5.3   |                    | rsion from VSFG-S to Bluespec                   |           |  |

|                                | 5.4   |                    | nt Limitations                                  |           |  |

|                                | 5.5   |                    | ary                                             |           |  |

|                                | _     |                    |                                                 |           |  |

| 6                              |       |                    | Methodology and Results                         | 125       |  |

|                                | 6.1   |                    | ation Methodology                               |           |  |

|                                |       | 6.1.1              | Comparison with an Existing HLS Tool            |           |  |

|                                |       | 6.1.2              | Comparison with Pegasus/CASH                    |           |  |

|                                |       | 6.1.3              | Comparison with Conventional Processors         |           |  |

|                                | 0.0   | 6.1.4              | Selected benchmarks:                            |           |  |

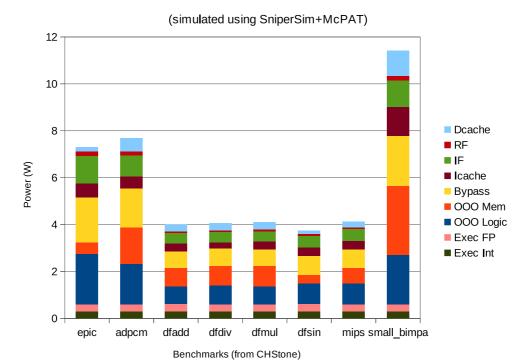

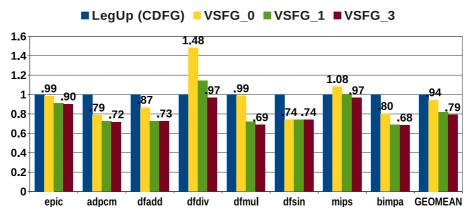

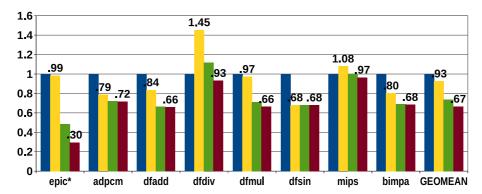

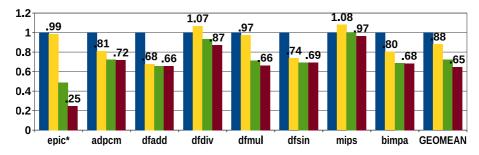

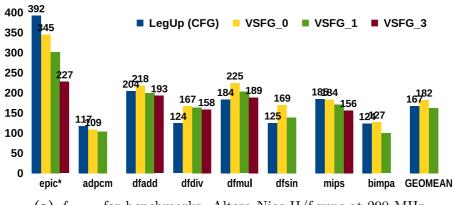

|                                | 6.2   |                    | S                                               |           |  |

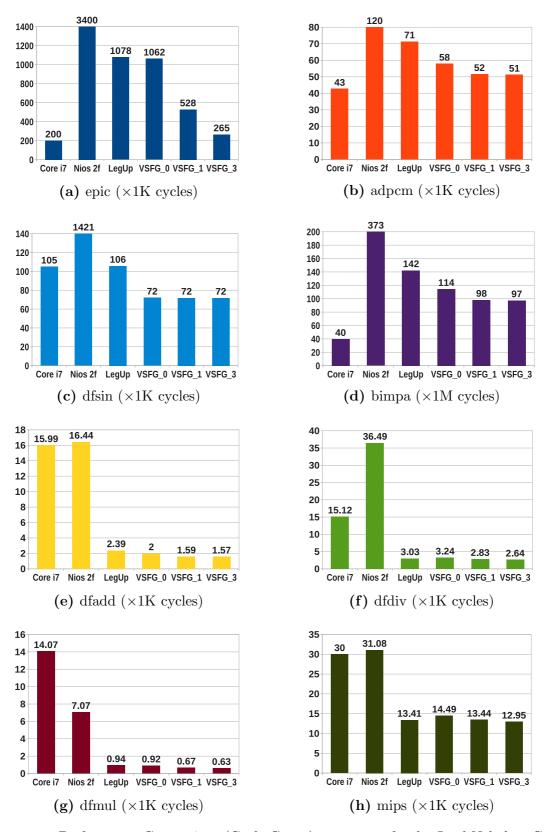

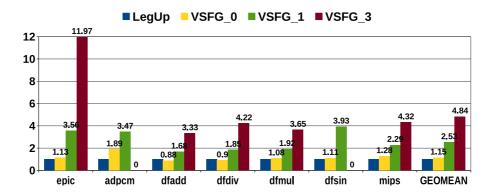

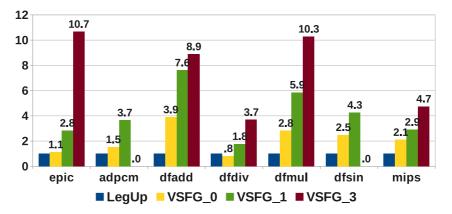

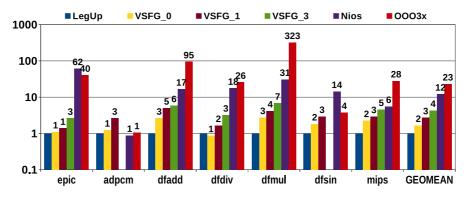

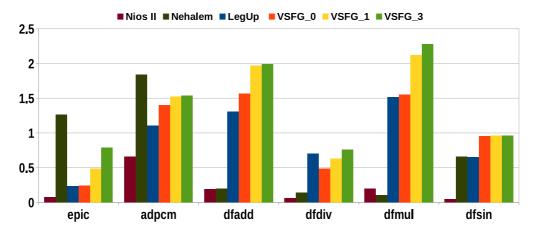

|                                |       | 6.2.1              | Cycle Counts                                    |           |  |

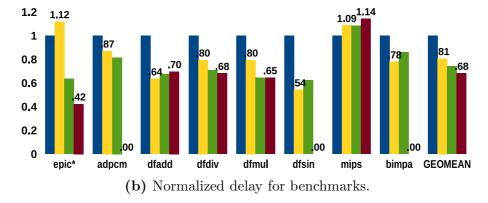

|                                |       | 6.2.2              | Frequency and Delay                             |           |  |

|                                |       | 6.2.3              | Resource Requirements                           |           |  |

|                                | c o   | 6.2.4              | Power and Energy                                |           |  |

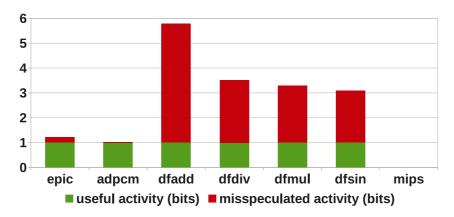

|                                | 6.3   |                    | ating ILP                                       |           |  |

|                                | 6.4   | Summ               | ary                                             | 151       |  |

| 7                              | Con   |                    | ns and Future Work                              | 153       |  |

|                                | 7.1   |                    | e Work                                          |           |  |

| 7.1.1 Incremental Enhancements |       |                    |                                                 |           |  |

|                                |       | 7.1.2              | Mitigating the Effects of Dark Silicon          | 154       |  |

| Bi                             | bliog | graphy             |                                                 | 170       |  |

# Introduction

Over the past two decades, pervasive, always-on computing services have become an integral part of our lives. Not only are we using increasingly portable devices like tablets and smartphones, there is also an increasing reliance on *cloud* computing: server-side computation and services, like web search, mail, and social media. On the client side, there is an ever growing demand for increased functionality and diversity of applications, as well as an expectation of continued performance scaling with every new technology generation.

Designers incorporate increasingly powerful processors and systems-on-chip into such devices to meet this demand. However, the key trade-off in employing high-performance processors is the high energy cost they incur [GA06]: for increasingly portable devices, in addition to the demand for ever higher performance, users have an expectation of a minimum time that their battery should last under normal use.

On the server-side, power dissipation and cooling infrastructure costs are growing, currently accounting for more than 40% of the running costs for datacenters [Ham08], and around 10% of the total lifetime cost [KBPS09]. To meet the growing demand for computational capacity in datacenters, computer architects are striving to develop processors capable of not only providing higher throughput and performance, but also achieving high energy efficiency.

Unfortunately, for the past decade, architects have had to struggle with several key issues that hinder their ability to continue scaling performance with Moore's Law, while also improving the energy efficiency of computation. Poor wire-scaling, together with the need to limit power dissipation and improve energy efficiency, have driven a push towards ever more decentralized, modular, multicore processors that rely on explicit parallelism for performance instead of frequency scaling and increasingly complex uniprocessor microarchitectures.

Instead of the dynamic, run-time effort of exposing and exploiting parallelism in increasingly complex processors, in the multicore era the responsibility of exposing further parallelism to scale performance rests primarily with the programmer. Nevertheless, despite the increased programming costs and complexity, performance has continued to scale for application domains that have abundant, easy-to-express parallelism, in particular for server-side applications such as web and database servers, scientific and high-performance computing, etc.

The Dark Silicon Problem: On the other hand, for client-side, general-purpose applications, performance scaling on explicitly parallel architectures has been severely limited due to Amdahl's Law, as such applications exhibit limited coarse-grained (data or task-level) parallelism that could be cost-effectively exposed by a programmer [BDMF10].

Furthermore, more recently, a new issue has been identified that limits performance scaling on multicore architectures, even for applications with abundant parallelism: due to the end of Dennard scaling [DGnY<sup>+</sup>74], on-chip power dissipation is growing in proportion to the number of on-chip transistors, meaning that for a fixed power budget, the proportion of on-chip resources that can be actively *utilized* at any given time decreases with each technology generation. This problem is known as the *Utilization Wall* [VSG<sup>+</sup>10].

Together, the utilization wall and Amdahl's law problems lead to the issue of Dark Silicon, where a growing fraction of on chip resources will have to remain switched off, either due to power dissipation constraints, or simply because of insufficient parallelism in the application itself. A recent study has shown that with future process generations, even as Moore's Law provides a  $32\times$  increase in on-chip resources, dark silicon will limit effective performance scaling to only about  $3-8\times$  [EBSA+11].

The Potential of Spatial Computation: To mitigate the effects of the utilization wall, it is essential to make the most efficient use of the fraction of transistors that can be active at any given time. Architects are doing exactly this as they build increasingly heterogeneous systems incorporating spatial computation hardware such as custom or reconfigurable logic<sup>1</sup>. Unlike conventional processors, spatial hardware relegates much of the effort of exposing and exploiting concurrency to the compiler or programmer. Spatial hardware is also highly specialized, tailored to the specific application being implemented, thereby providing orders-of-magnitude improvements in energy efficiency and performance [HQW<sup>+</sup>10].

Examples of such hardware include video codecs and image processing datapaths implemented as part of heterogeneous systems-on-chip commonly used in modern smartphones and tablets. By implementing specialized hardware designed for a small subset of tasks, architects essentially trade relatively inexpensive and abundant transistor resources for essential improvements in energy-efficiency.

Current Limitations of *Spatial* Computation: To mitigate the effects of Amdahl's Law and continue scaling performance with Moore's law, it is essential to also aggressively exploit implicit fine-grained parallelism from otherwise sequential code, and to do so with high energy efficiency to avoid running into the utilization wall. Recent work has attempted to implement sequential, general-purpose code using spatial hardware, in order to improve energy efficiency [VSG<sup>+</sup>10, BVCG04]. Unfortunately, sequential code exhibits poor performance in custom hardware, meaning that for performance scaling under Amdahl's Law, architects must employ conventional, complex, and energy-inefficient out-of-order processors [BAG05].

<sup>&</sup>lt;sup>1</sup>Unlike the *temporal* execution model of conventional processors, wherein intermediate operands are communicated between operations through a centralized memory abstraction such as a register file, *spatial* computation utilizes a point-to-point interconnect to communicate intermediate operands directly between producing and consuming processing elements. Consequently, unlike with conventional processors, *placement/mapping* of operations to processing elements must be determined before program execution. Spatial Computation is described in greater detail in Section 2.4.

Not only does this affect usability by reducing the battery life of portable devices, it also means that overall performance scaling would be further limited due to the utilization wall limiting the amount of parallel processing resources that can be activated within the remaining power budget. To overcome this Catch-22 situation, it is essential that new approaches be found to implement such sequential code with high performance, without incurring the energy costs of conventional processors.

This dissertation focuses on combining the high energy efficiency of spatial computation, with the high sequential-code performance of conventional superscalar processors. Success in this endeavour should have a significant positive impact on a diverse range of computational domains in different ways.

For instance, embedded systems would be able to sustain higher performance within a given power budget, potentially also reducing effort required to optimize code. For example, the primary energy consumption in a smartphone is typically not due to the application processor. Instead subsystems like high-resolution displays, or radio signalling and processing consume a majority of the power budget. As a result, even an order of magnitude improvement in computational efficiency would not significantly affect how frequently a user is expected to charge their phone. However, the increased efficiency could instead be utilized to undertake more complex computation within the same power budget, perhaps to provide a better user experience.

Conversely, cloud and datacenter infrastructure could directly take advantage of the increased efficiency to reduce energy costs. As the key reasons for the high energy cost in server-side systems are (a) power consumed by processors, and (b) the cooling infrastructure needed to dissipate this power, more efficient processing elements would simultaneously reduce the operating costs due to both of these factors without compromising computational capacity.

## 1.1 Thesis Statement

My main thesis is that by statically overcoming the limitations on fine-grained parallelism due to control-flow, the sequential code performance of energy-efficient spatial architectures can be improved to match or even exceed the performance of dynamic, out-of-order superscalar processors, without incurring the latters' energy cost.

To achieve this, this dissertation focuses on the development of a new compiler intermediate representation that accelerates control-intensive sequential code by enabling aggressive speculative execution, control-dependence analysis, and exploitation of multiple flows of control in spatial hardware. In order to demonstrate my thesis, this dissertation is structured as follows:

- Chapter 2: A brief overview of the energy and performance issues faced by computer architects is presented, followed by an introduction to *spatial* computation, along with a brief survey of existing spatial architectures, demonstrating the current issues with sequential code performance.

- Chapter 3: I study the key underlying reasons for the performance advantage of complex, out-of-order superscalar processors over spatial hardware when implementing general-purpose sequential code. The goal being to understand how to

overcome these limitations without compromising the inherent energy-efficiency of spatial hardware.

- Chapter 4: I then develop a new compiler intermediate representation called the Value State Flow Graph that simplifies the static exposition of fine-grained instruction level parallelism from control-flow intensive sequential code. The VSFG is designed so that it can be used as an intermediate representation for compiling to a wide variety of spatial architectures and substrates, including a direct implementation as application-specific custom hardware.

- Chapter 5: A high-level synthesis toolchain using the VSFG representation is developed that allows the compilation of high-level language code to high performance custom hardware.

- Chapter 6: Finally, results from benchmarks compiled using this toolchain demonstrate that in most cases, the performance of the generated custom hardware matches, or even exceeds the performance of a complex superscalar processor, while incurring a fraction of its energy cost. I highlight the fact that performing compile-time optimizations on the VSFG can easily improve both performance and energy-efficiency even further.

Chapter 7 concludes the dissertation, and highlights some areas for future research in the area of spatial architectures and compilers.

# 1.2 Contributions

This thesis makes the following contributions:

- A new low level compiler intermediate representation (IR), called the Value State Flow Graph (VSFG) is presented, that exposes ILP from sequential code even in the presence of complex control flow. It achieves this by enabling aggressive control-flow speculation, control dependence analysis, as well as execution along multiple flows of control. As conventional processors are typically unable to take advantage of the last two features, the VSFG can potentially expose far greater ILP from sequential code [LW92].

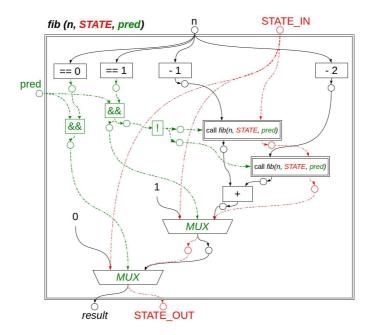

- The VSFG representation is also designed to be directly implementable as custom hardware, replacing the traditionally used CDFG (Control-Data Flow Graph) [NRE04]. The VSFG is defined formally, including the development of eager (dataflow) operational semantics. A discussion of how the VSFG compares to existing representations of dataflow computation is also presented.

- To test this new IR, a new high-level synthesis (HLS) tool-chain has been implemented, that compiles from the LLVM IR to the VSFG, then implements the latter as a hardware description in Bluespec SystemVerilog [Nik04]. Unlike the statically-scheduled execution model of traditional custom hardware [CM08], I employ a dynamically-scheduled static-dataflow execution model for our implementation [Bud03, BVCG04], allowing for better tolerance of variable latencies and statically unpredictable behaviour.

- Custom hardware generated by this new tool-chain is shown to achieve an average speedup of  $1.55\times$  (max  $4.05\times$ ) over equivalent hardware generated by LegUp, an established CDFG-based high-level synthesis tool [CCA+11]. Furthermore, VSFG-based hardware is able to approach (in some cases even improve upon) the cycle-counts of an Intel Nehalem Core i7 processor, on control-flow intensive benchmarks. While this performance incurs an average  $3\times$  higher energy cost than LegUp, the VSFG-based hardware's energy dissipation is still only  $1/4\times$  that of a highly optimized in-order Altera Nios II/f processor (and  $1/8\times$  that of a Core i7-like out-of-order processor).

- I provide recommendations for how both the energy efficiency and performance of our hardware may be further improved by implementing simple compiler optimizations, such as performing alias-analysis to partition and parallelize memory accesses, as well as how to reduce the energy overheads of speculation.

# 1.3 Publications and Awards

- Paper (to appear): Ali Mustafa Zaidi, David Greaves, "A New Dataflow Compiler IR for Accelerating Control-Intensive Code in Spatial Hardware", 21st Reconfigurable Architectures Workshop (RAW 2014), associated with the 28th Annual International Parallel and Distributed Processing Symposium (IPDPS 2014), May 2014, Phoenix, Arizona, USA.

- Poster: Ali Mustafa Zaidi, David Greaves, "Exposing ILP in Custom Hardware with a Dataflow Compiler IR", The 22nd International Conference on Parallel Architectures and Compilation Techniques (PACT 2013), September, 2013, Edinburgh, UK.

- Award: Awarded Gold Medal at the PACT 2013 ACM Student Research Competition.

- Paper: Ali Mustafa Zaidi, David Greaves, "Achieving Superscalar Performance without Superscalar Overheads A Dataflow Compiler IR for Custom Computing", The 2013 Imperial College Computing Students Workshop (ICCSW'13), September 2013, London, UK.

- Award: Qualcomm Innovation Fellowship 2012, Cambridge, UK. Awarded for research proposal titled: "Mitigating the Effects of Dark Silicon".

# TECHNICAL BACKGROUND

This chapter presents a brief history of computer architecture, highlighting the technical and design challenges architects have faced previously, as well as those that must be addressed today, such as dark silicon. I establish the need for achieving both high sequential performance, as well as much higher energy efficiency, in order to mitigate the effects of dark silicon. This chapter also presents a survey of prior work on spatial computation, establishing its scalability, efficiency and performance advantages for the numeric application domain, as well as its shortcomings with respect to implementing and accelerating sequential code. This dissertation attempts to overcome these shortcomings with the development of a new dataflow compiler intermediate representation which will be discussed in Chapter 3, and described formally in Chapter 4.

# 2.1 The Uniprocessor Era

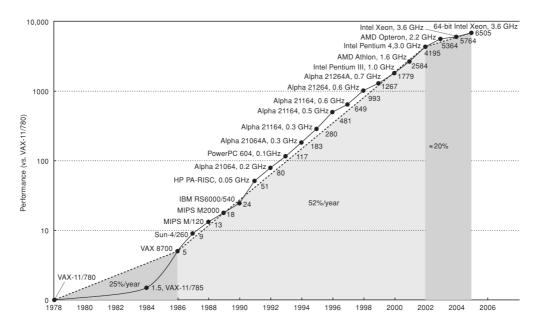

For over two decades, Moore's Law enabled exponential scaling of uniprocessor performance. Computer architects used the ever growing abundance of on-chip resources to build increasingly sophisticated uniprocessors that operated at very high frequencies. Starting in the mid 1980s, uniprocessor performance improved by three orders of magnitude, at approximately 52% per year (Figure 2.1, taken from [HP06]), until around 2004. Of this, two orders of magnitude can be attributed to improvements in fabrication technology leading to higher operating frequencies, while the remaining 10× improvement is attributed to microarchitectural enhancements for dynamically exposing and exploiting fine-grained instruction level parallelism (ILP), enabled by an abundant transistor budget [BC11].

Programmers would code using largely sequential programming models, while architects utilized ever more complex techniques to maximize ILP: incorporating deeper pipelining, superscalar as well as out-of-order execution to accelerate true dependences, register renaming to overcome false dependences, as well as aggressive branch prediction and misspeculation recovery mechanisms to overcome control dependences.

While the benefits of explicit parallel programming were known due to extensive work done in the high-performance and supercomputing domains [TDTD90, DD10], there was little incentive for programmers to utilize explicit parallelism in the general-purpose computing domain, since uniprocessor performance scaling effectively provided a 'free lunch': doubling observed performance every 18 months, with no effort required on the part of the

Figure 2.1: Uniprocessor Performance Scaling from 1978 to 2006. Figure taken from [HP06]

programmer [Sut05]. Thus all the 'heavy lifting' of exposing and exploiting concurrency was left to the microarchitecture level of abstraction, leading to increasingly complex mechanisms for instruction stream management at the microarchitecture level.

Utilizing the exponentially growing on-chip resources to develop evermore complicated uniprocessors ultimately proved to be unsustainable. Around 2004, this trend came to an end due to the confluence of several issues, commonly known as the ILP, Power, Memory, and Complexity Walls [OH05].

1. **The ILP Wall:** In the early 1990s, limit studies carried out by David Wall [Wal91] and Monica Lam [LW92] determined that, with the exception of *numeric* applications<sup>1</sup>, the amount of ILP that can be dynamically extracted from a sequential instruction stream by a uniprocessor is fundamentally limited to about 4-8 instructions per cycle (IPC).

Lam noted that this ILP Wall is not due to reaching the limit of available ILP in the code at runtime, but rather because control-flow remains a key performance bottleneck despite aggressive branch prediction, particularly as uniprocessors are limited to exploiting ILP by speculatively executing independent instructions from a single flow of control. By enabling the identification of multiple independent regions of code through control dependence analysis, and then allowing their concurrent execution (i.e. exploiting multiple flows of control), Lam observed that ILP could again be increased by as much as an order of magnitude in the limit [LW92].

2. The Memory Wall: As transistor dimensions shrank, both processor and DRAM clock rates improved exponentially, but the rate of improvement for processors far outpaced that for main memory. This meant that the cycle latency for accessing main memory grew exponentially [WM95]. This issue was mitigated to an extent through the use of larger last-level caches and deeper cache hierarchies, but at a

<sup>&</sup>lt;sup>1</sup>Applications with abundant data level parallelism, and often regular, predictable control-flow. Examples include signal processing, compression, and multimedia.

significant area cost: the fastest processors dedicated as much as half of total die area to caches. Despite this, it was expected that DRAM access latency would ultimately become the primary performance bottleneck to performance, given the historic reliance on ever higher clock rates for uniprocessor performance improvement.

3. The Complexity Wall: While transistor dimensions and performance have scaled with Moore's Law, the performance of wires has diminished as feature sizes shrink. This is partly due to the expectation that each process generation will enable higher frequency operation, so the distance that signals can propagate in a single clock cycle is reduced [AHKB00]. Furthermore, narrower, thinner and more tightly packed wires exhibit higher resistance (R) and capacitance (C) per unit length, and thus increased signaling delay [HMMH01].

Uniprocessors have heavily relied on monolithic, broadcast resource abstractions such as centralized register files, and broadcast buses, in their designs, primarily in order to maintain a unified program state and support precise exceptions. However, such resources scale poorly when increased performance is required [ZK98, TA03].

With poor wire scaling limiting clock rate improvements, together with the ILP wall limiting improvements in IPC, designers observed severely diminishing returns in overall performance, even as design complexity, costs and effort continued to grow [BMMR05, PJS97].

4. The Power Wall: With each process generation, Moore's law enables a quadratic growth in the number of transistors per unit area, as well as allowing these transistors to operate at higher clock rates. For a given die size, this represents a significant increase in the number of circuit elements that can switch per unit time, potentially increasing power dissipation proportionally. Thankfully, total power dissipation per unit area could be kept constant thanks to Dennard scaling [DGnY<sup>+</sup>74], which posits that both per-transistor load capacitance and supply voltage can be lowered each generation. (This is described in more detail in Section 2.3.2).

However, Dennard scaling did not take into account the increased complexity of newer processor designs, as well as the poor scaling of wires, both of which contributed to an overall increase in power dissipation. Furthermore, as transistor dimensions shrink and supply voltage (and therefore threshold voltage) are reduced, there is an exponential increase in leakage current, and therefore relative static power dissipation increases as well [BS00]. Until about 1999, static power remained a small fraction of total power dissipation, but was becoming increasingly more severe with each process generation [TPB98].

A combination of these factors has meant that the total power dissipation of uniprocessor designs continued to grow to such an extent that chip power densities began to approach those of nuclear reactor cores [Pol99].

Due to the ILP, Memory, Complexity, and Power Walls, further scaling of performance could no longer be achieved by simply relying on faster clock rates and increasingly complex uniprocessors. Ending frequency scaling became necessary to keep memory access latency and architectural complexity from worsening, as well as to compensate for power increases due to leakage, poor wire scaling, and growing microarchitectural complexity

with successive process generations. This meant that further performance scaling would have to rely solely on the increased exploitation of concurrency.

In order to overcome the ILP Wall and improve IPC, processors would need to exploit parallelism from multiple, independent regions of code. Exploitation of more coarse-grained and/or more explicit concurrency became essential, but must be achieved without further increasing design complexity. To address poor wire scaling and the complexity wall, decentralized, modular, highly scalable architectures must be devised, so that the worst-case wire lengths do not have to scale with the amount of resources available. Instead of relying on the simple unified abstraction provided by non-scalable centralized memory or broadcast interconnect structures, cross-chip communication must now be explicitly managed between modular components.

Since 2004, computer architecture has developed into two distinct directions. Multicore architectures are primarily utilized for the *general-purpose* computing domain, that includes desktop and server applications. Alternatively, *spatial* architectures, discussed in Section 2.4 are increasingly being utilized to accelerate numeric, data-intensive applications, particularly in situations where both high performance and/or high energy efficiency are required.

# 2.2 The Multicore Era

The need for modularity and explicit concurrency was answered with an evolutionary switch to multicore architectures. Instead of having increasingly complex uniprocessors, designers chose to implement multiple copies of conventional processors on the same die. In most cases, architects relied on the shared-memory programming model to enable programmers to write parallel code, as this model was seen as an extension of the Von-Neumann architecture that programmers were already familiar with.

Wire scaling and complexity issues were mitigated thanks to the modular nature of multicore design, while the memory wall was addressed by ending frequency scaling. The ILP Wall would be avoided by relying on explicitly parallel programming to identify and execute 'multiple flows of control' organised into threads, communicating and synchronizing via shared memory. Ideally, the Moore's Law effect of exponential growth in transistors would then be extended into an exponential growth in number of cores on chip.

Multicore processors are able to provide high performance scaling for *embarrasingly* parallel application domains that have abundant data or task level parallelism. This is often facilitated with the help of domain-specific programming models like MapReduce [RRP+07], that are used for web and database servers and other datacenter applications, or OpenCL [LPN+13], which is useful for accelerating highly numeric applications such as games, or multimedia and signal processing<sup>2</sup>.

However, for many non-numeric, consumer-side applications, performance scaling on multicore architectures has proven far more difficult. Such applications are characterized by low data or task parallelism, complex and often data-dependent control-flow, and irregular memory access patterns<sup>3</sup>. Previously, programmers had relied on the fine-grained

<sup>&</sup>lt;sup>2</sup>Graphics Processors or GPUs can be considered a highly specialized form of multicore processor, designed to accelerate such data-parallel applications.

<sup>&</sup>lt;sup>3</sup>In this thesis, I refer to such code as belonging to the *client-side*, *consumer*, or *general-purpose* application domains, or simply as *sequential* code.

ILP exploitation capabilities of out-of-order superscalar processors to achieve high performance on such code [SL05].

The shared memory programming model has proven to be very difficult for programmers to utilize in this domain, particularly when constrained to exploiting such fine-grained parallelism [HRU+07]. Programmers are required to not only explicitly expose concurrency in their code by partitioning it into threads, but also to manually manage communication and synchronization between threads at run-time. The shared-memory threaded programming model is also highly non-deterministic, since the programmer is largely unaware of the order in which concurrent threads will be scheduled, and hence alter shared state, at runtime. This non-determinism further increases the complexity of debugging such applications, as observed behavior may change with each run of the application [Lee06].

Thus, despite the decade-old push towards multicore architectures, the degree of threaded parallelism in consumer workloads remains very low. Blake et al. observed that over a period of 10 years, the number of concurrent threads in non-numeric applications has been limited to about two [BDMF10]. As a result, performance scaling for such applications remains far below what users have come to expect over the past decades. In part due to this insufficient explicit parallelism in applications, a new threat to continued performance scaling with Moore's Law has recently been identified, called Dark Silicon.

# 2.3 The Dark Silicon Problem

Despite ongoing exponential growth of on-chip resources with Moore's Law, the performance scalability of future designs will be increasingly restricted. This is because the total *usable* on-chip resources will be growing at a much slower rate. This problem is known as 'Dark Silicon', and is caused by two factors [EBSA<sup>+</sup>11]:

- 1. Amdahl's Law and performance saturation due to insufficient explicit parallelism, and

- 2. the end of Dennard Scaling, together with limited power budgets leading to the  $Utilization\ Wall.$

This section describes these issues in more detail, and discusses current strategies for addressing them.

# 2.3.1 Insufficient Explicit Parallelism

Amdahl's Law: As mentioned in the last section, the general-purpose, or consumer application domain exhibits low degrees of parallelism. Amdahl's Law [Amd67] governs the performance scaling of parallel applications by considering them composed of a parallel and a sequential fraction, and states that for applications with insufficient parallelism, achievable speedup will be strictly constrained by the performance of the sequential fraction.

$$Perf(f, n, S_{seq}, S_{par}) = \frac{1}{\frac{(1-f)}{S_{seq}} + \frac{(f)}{n \cdot S_{par}}}$$

(2.1)

A generalized form of Amdahl's Law for multicore processors is shown in equation 2.1 (adapted from [HM08]), where f is the fraction of code that is perfectly parallel, thus (1-f) is the fraction of sequential code.  $S_{seq}$  is the speedup that a particular architecture provides for the sequential portion of code, n is the number of parallel processors, and  $S_{par}$  is the speedup each parallel processor provides when executing a thread from the parallel region of code.

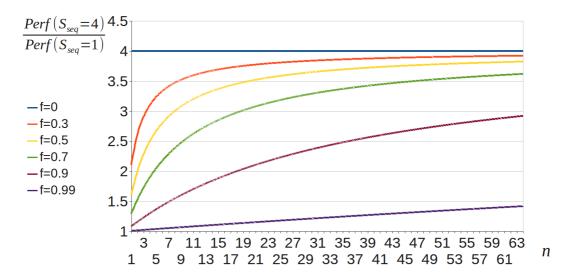

Figure 2.2 shows a plot of the relative speedup of a machine with high  $S_{seq}$ , versus a machine with low  $S_{seq}$ , as f and n are varied (assume  $S_{par}=1$  for both machines). The vertical axis is the ratio of speedup of a machine with  $S_{seq}=4$  to a machine with  $S_{seq}=1$ . Figure 2.2 shows that even with moderate amounts of parallelism  $(0.7 \le f \le 0.9)$ , overall speedup is highly dependent on the speedup of the sequential fraction of code even as the number of parallel threads is increased. Thus achieving high sequential performance through dynamic exploitation of implicit, instruction-level parallelism remains important for scaling performance with Moore's Law. However, this must be achieved without again running into the ILP, Complexity, Power and Memory Walls.

Figure 2.2: Plot showing the importance of sequential performance to overall speedup. The y-axis measures the ratio of performance between two machines, one with high sequential performance  $(S_{seq} = 4)$ , vs. one with low sequential performance  $(S_{seq} = 1)$ , with all other factors being identical.

A more comprehensive analysis of multicore speedups under Amdahl's Law is presented by Hill and Marty [HM08]. They consider various configurations of multicore processors given a fixed resource constraint: fewer coarse-grained cores, many fine-grained cores, as well as asymmetric and dynamic multicore processors. They find that while performance scaling is still limited by the sequential region, the best potential from speed-up arises from the dynamic multicore configuration, where many smaller cores may be combined into a larger core for accelerating sequential code, assuming minimal overheads for such reconfiguration. It is important to note that theirs is a highly optimistic analysis, as it assumes that sequential performance can be scaled indefinitely (proportional to  $\sqrt{n}$ , where n is the number of execution resources per complex processor), whereas Wall [Wal91] notes a limit to ILP scaling for conventional processors.

Esmaelzadeh et al. identifed insufficient parallelism in applications as the primary

source of dark silicon [EBSA<sup>+</sup>11]: with the sequential fraction of code limiting overall performance, most of the exponentially growing cores will remain unused unless the degree of parallelism can be dramatically increased.

Brawny Cores vs. Wimpy Cores: Even for server and datacenter applications that exhibit very high parallelism, and thus are less susceptible to being constrained by sequential performance, per-thread sequential performance remains essential [H10]. This is because of a variety of practical concerns not considered under Amdahl's Law – the explicit parallelization, communication, synchronization and runtime scheduling overheads of many fine-grained threads can often negate the area and efficiency advantages of wimpy, or energy-efficient cores. Consequently, it is often better for overall cost and performance to have fewer threads running on fewer brawny cores than to have a fine-grained manycore in most cases [LNC13].

Add to this the fact that a vast amount of legacy code remains largely sequential, we find that achieving high sequential performance will remain critical for performance scaling for the forseeable future. Unfortunately, currently the only means of achieving high performance on general-purpose sequential code is through the use of complex, energy inefficient out-of-order superscalar processors.

## 2.3.2 The Utilization Wall

The average power dissipation of CMOS circuits is given by equation 2.2, where n is the total number of transistors,  $\alpha$  is the average activity ratio for each transistor, C is the average load capacitance,  $V_{DD}$  is the supply voltage, and f is the operating frequency.  $P_{static}$  represents static, or leakage power dissipation that occurs independently of any switching activity, while  $I_{leakage}$  is the leakage current, and  $k_{design}$  is a constant factor. This model for  $P_{static}$  is taken from [BS00].

$$P_{total} = P_{dynamic} + P_{static} = n.\alpha.C.V_{DD}^2.f + n.V_{DD}.I_{leakage}.k_{design}$$

(2.2)

The effect of Moore's Law and Dennard Scaling on power dissipation is described as a first-order approximation in [Ven11], and is adapted and briefly summarized here:

If a new process generation allows transistor dimensions to be reduced by a scaling factor of S (i.e. transistor width and length are both reduced by 1/S, where S > 1), then the number of transistors on chip (n) grows by  $S^2$ , while operating frequency (f) also improves by S. This implies that the total switching activity per unit time should increase by  $S^3$ , for a fixed die size. However, chip power dissipation would also increase by  $S^3$ .

In 1974, Robert Dennard observed that not only does scaling transistor dimensions also scale its capacitance (C) by 1/S, but that it is also possible to scale  $V_{DD}$  by the same factor [DGnY<sup>+</sup>74]. This meant that  $P_{dynamic}$  could be kept largely constant, even as circuit performance per unit area improved by  $S^3$ !

However, as  $V_{DD}$  is lowered, the threshold voltage of transistors  $(V_{th})$  must be lowered as well, and this leads to an exponential increase in leakage current  $(I_{leakage})$  [BS00]. Although  $I_{leakage}$  was rising exponentially,  $P_{static}$  accounted

for a very small fraction of total power until about 1999, but has been increasingly significant since then [TPB98].

This has meant that Dennard scaling effectively ended with the 90nm process technology in about 2004, because if  $V_{DD}$  was lowered further,  $P_{static}$  would be a significant and exponentially increasing fraction of total power dissipation [TPB98]. Consequently, with only transistor capacitance scaling, chip power dissipation would increase by  $S^2$  each process generation if operated at full frequency.

This issue resulted in the Power Wall described in section 2.1. Switching to multicore and ending frequency scaling meant that power would now only scale with S. In addition, enhancements in fabrication technology such as FinFET/Tri-gate transistors and use of high-k dielectrics allowed designers to avoid this power wall at least temporarily [RM11,  $AAB^{+}12$ ,  $HLK^{+}99$ ].

Unfortunately, the end of Dennard scaling has another implication: for a fixed power budget, this means that with each process generation, only an ever decreasing fraction of on-chip resources may be active at any time, even if frequency scaling is ended. This problem is known as the *Utilization Wall*, and is exacerbated even further with the growing performance demands of increasingly portable yet functional devices like tablets, smartphones and smart-watches, that have evermore limited power budgets.

# 2.3.3 Implications of Dark Silicon

The issue of insufficient parallelism, together with the Utilization Wall means that despite ongoing exponential growth in transistors or cores on-chip with Moore's Law, a growing proportion of these resources must frequently remain un-utilized, or 'dark'. Firstly, performance scaling will primarily be limited due to poor sequential performance scaling in the consumer domain. Secondly, even for applications with abundant data or task level parallelism, such as in the server/datacenter or multimedia domains, the Utilization Wall limits the amount of parallelism that can be exploited in a given power budget.

A comprehensive analysis of these two factors by Esmaelzadeh et al. found that in 6 fabrication process generations, from 45nm to 8nm, while available on-chip resources grow by  $32\times$ , dark silicon will limit the ideal case performance scaling to only about  $7.9\times$  for highly parallel workloads, with a more realistic estimate being about  $3.7\times$ , or only 14% per year – well below the 52% we have been used to for most of the past three decades [EBSA+11]. This analysis assumed ideal per-benchmark multicore configurations from among those described by Hill and Marty [HM08], so actual performance scaling on a fixed, realistic architecture can be expected to be even lower.

Overcoming the effects of dark silicon would require addressing each of the constituent issues. Breakthroughs in auto-parallelisation or an industry-wide switch to novel programming models that can effectively expose fine-grained parallelism from sequential code would be required to effectively exploit available parallel resources. Overcoming the Utilization Wall, returning to Dennardian scaling, and re-enabling the full use of all on-chip resources would likely require a switch to a new post-CMOS fabrication technology that either avoids the leakage current issue, or is just inherently far more efficient overall [Tay12]. Barring such breakthroughs however, the best that architects can attempt is to mitigate the effects of each of these factors.

#### The Need to Accelerate Sequential Code

To accelerate sequential code, architects are currently developing heterogeneous multicore architectures, composed of different types of processor cores. One approach is to implement an Asymmetric Multicore processor, that combines a few complex out-of-order superscalar cores for accelerating sequential code, with many simpler in-order cores for running parallel code more efficiently [JSMP13]. Another is the Single-ISA Heterogeneous Multicore<sup>4</sup> approach, where cores of different performance and efficiency characteristics but implementing the same ISA, cooperate in the execution of a single thread – performance critical code can be run on the complex out-of-order processors, but during phases that do not require as much processing power (e.g. I/O intensive code), execution seamlessly switches over to the simpler core for efficiency [KFJ<sup>+</sup>03, KTR<sup>+</sup>04].

An example of such a design is ARM's big.LITTLE which is composed of two different processor types: large out-of-order superscalar Cortex-A15 cores, as well as a small and efficient Cortex-A7 cores [Gre11]. big.LITTLE can be operated either as an asymmetric multicore processor, with all cores active, or as a single-ISA heterogeneous multicore, where each Cortex-A15 core is paired with a Cortex-A7 in such a way that only one of them is active at a time, depending on the needs of the scheduled threads.

However, running sequential code faster on complex cores also inevitably means a decrease in energy efficiency, thus such architectures essentially trade-off between performance and energy by running non-critical regions of code at lower performance. Grochowski and Annavaram observed that after abstracting away implementation technology differences for Intel microprocessors, a linear increase in sequential performance leads to a power-law increase in power dissipation, given by the following equation [GA06]:

$$Pwr = Perf^{\alpha} \quad where \quad 1.75 \le \alpha \le 2.25. \tag{2.3}$$

This puts architects between a rock and a hard place – without utilizing complex processors, performance scaling is limited by Amdahl's Law, and practical concerns, but with such processors, their high power dissipation means that the Utilization Wall limits speedup by limiting the number of active parallel resources at one time. Esmaelzadeh et al note that in order to truly mitigate the effects of dark silicon: "Clearly, architectures that move well past the Pareto-optimal frontier of energy/performance of today's designs will be necessary" [EBSA<sup>+</sup>11].

#### The Need for High Energy Efficiency

To mitigate the effects of the Utilization Wall, it is essential to make the most efficient use possible of the fraction of on-chip resources that can be activated at any given time. Recently, architects have been increasingly relying on custom hardware and/or reconfigurable architectures, incorporated as part of heterogeneous systems-on-chip, in order to achieve

<sup>&</sup>lt;sup>4</sup>Although both involve combining fast cores with simple cores on the same multicore system-on-chip, a subtle distinction is made between *asymmetric* and *heterogeneous* multicores, primarily due to the different use cases these terms are associated with in the cited literature. The former expects sequential/low-parallelism fraction of an application to run on fewer large cores, with the scalable parallel code running on many smaller cores, as a direct response to Amdahl's Law, whereas the latter involves switching a single sequential thread from a small core to a large core in order to trade-off energy with sequential performance, as needed. Asymmetric multicores view all cores as available to a single parallel application, whereas the heterogeneous multicores approach typically makes different kinds of cores seamlessly available to a single sequential thread of execution.

high performance and high energy efficiency on computationally intensive operations such as video codecs or image processing. This trend has largely been driven by growing demand for highly portable (thus power limited) computing devices like smartphones and tablets, with strong multimedia capabilities. For such applications, custom hardware is able to provide as much as three orders of magnitude improvements in performance and energy efficiency  $[HQW^+10]$ .

Custom and reconfigurable hardware are types of *spatial* computing architectures. The next section describes spatial computation, and considers how its advantages may be utilized to mitigate the effects of dark silicon. I also describe the current limitations of spatial computation that need to be overcome in order to be truly useful for addressing the dark silicon problem, and how several research projects have attempted to do so.

# 2.4 The *Spatial* Computation Model

Conventional processors rely on an imperative programming and execution model, where communication of intermediate operands between instructions occurs via a centralized memory abstraction, such as a register file or addressed memory location. For such processors, the *spatial* locality between dependent instructions – i.e. *where* they execute in hardware relative to each other – is largely irrelevant. Instead, what matters is their correct *temporal* sequencing – *when* an instruction executes such that correct state can be maintained in the shared memory abstraction.

Custom and reconfigurable hardware on the other hand utilize a more dataflow-oriented, spatial execution model. Dataflow graphs of applications are mapped onto a collection of processing resources laid out in space, with intermediate operands directly communicated between producers and consumers using point-to-point wires, instead of through a centralized memory abstraction. As a result, where in space an operation is placed is crucial for achieving high efficiency and performance – dependent instructions are frequently placed close to each other in hardware in order to minimize wiring lengths in the spatial circuit.

# 2.4.1 Advantages of Spatial Computation

#### Scalability

As the number of operations that can execute in parallel is increased, the complexity of memory elements such as register files in conventional architectures grows quadratically [ZK98, TA03]. Instead of such structures, spatial architectures (a) rely on programmer-or compiler-directed placement of operations, making use of abundant locality information from the input program description to minimize spatial distances between communicating operations, and then (b) implement communication of operands between producers and consumers through short, point-to-point, possibly programmable wires.

While broadcast structures like register-files and crossbars are capable of supporting non-local, random-access, any-to-any communication patterns, recent work by Greenfield and Moore indicates that maintaining this level of flexibility is unnecessary. By analysing the dynamic-data-dependence graphs of many benchmark applications, they observe that the communication patterns of many applications demonstrate *Rentian* scaling in both temporal and spatial communication between dependent operations [GM08a, GM08b].

By making use of short, point-to-point wiring for communication, spatial computation is able to take advantage of the high locality implied by Rent's rule: instead of having the worst-case, quadratic complexity growth of a multi-ported register-file, the communication complexity of spatial architectures would be governed by the complexity of the communication graph for the algorithm/program it is implementing.

The communication-centric nature of spatial architectures is also beneficial in addressing the general issue of poor wire scaling. Ron Ho et al. observed that: "increased delays for global communication will drive architectures towards modular designs with explicit global latency mechanisms" [HMMH01]. The highly modular nature of spatial architectures, together with their exposure of communication resources and their management to higher levels of abstraction (i.e. the programmer and/or compiler) means that they are inherently more scalable than traditional uniprocessor architectures.

## Computational Density

In complex processor cores, only a small fraction of the die area is dedicated to execution resources that perform actual computation. Complex processors are designed to maximize the utilization of a small set of execution resources by overcoming false and control dependencies, and accelerating true dependence in an instruction stream. Consequently, the majority of core resources are utilized in structures for dynamically exposing concurrency from a sequential instruction stream: large instruction windows, register renaming logic, branch prediction, re-order buffers, multi-ported register files, etc.

Spatial architectures instead dedicate a much larger fraction of area to processing elements. Per unit area, this allows spatial architectures to achieve much higher computational densities than conventional superscalar processors [DeH96, DeH00]. Provided that applications can be mapped efficiently to spatial hardware such that the abundant computational elements can be effectively utilized, spatial architectures can achieve much greater performance per unit area. Given the fact that the proportion of usable on-chip resources is shrinking due to the Utilization Wall, the higher computational density offered by spatial architectures is an effective way of continuing to scale performance by making more efficient use of available transistors.

#### **Energy Efficiency**

Due to poor wire scaling, the energy cost of communication now far exceeds the energy cost of performing computation. Dally observes that transferring 32-bits of data across chip consumed the energy equivalent of 20 ALU operations in the 130nm CMOS process, which increased to about 57 ALU operations in the 45nm process, and is only expected to get worse [Dal02, MG08].

The communication-centric, modular, scalable, and decentralized nature of spatial architectures makes them well-suited to also addressing the energy efficiency challenges posed by poor wire scaling. Exploitation of spatial locality reduces the distances signals must travel, while reliance on decentralized point-to-point interconnect instead of multiported RAM and CAM (content-addressable memory) structures reduces the complexity of communication structures.

Programmable spatial architectures are able to reduce the energy cost of programmability in two more ways. First, instead of being broadcast from a central instruction store to execution units each cycle (such as the L1 instruction cache), 'instructions' are *config*- ured locally near each processing element, thereby reducing the cost of instruction stream distribution. Secondly, spatial architectures are able to amortize the cost of instruction fetch by fixing the functionality of processing elements for long durations – when executing loops, instructions describing the loop datapath can be fetched and spatially configured once, then reused as many times as the loop iterates. DeHon demonstrates in [DeH13], that due to these factors, programmable spatial architectures exhibit an asymptotic energy advantage over conventional temporal architectures.

A further energy efficiency advantage can be realised by removing programmability from spatial computation structures altogether. Instead of utilizing fine-grained programmable hardware like FPGAs, computation can be implemented as fixed-function custom hardware, eliminating the area, energy, and performance overheads associated with bit-level logic and interconnect programmability. For certain applications, this approach has been shown to provide as much as three orders of magnitude improvements in energy efficiency over conventional processors [HQW+10], and almost 40× better efficiency than a conventional FPGA, with its very fine-grained, bit-level programmable architecture [KR06]. While this improved efficiency (and often performance) comes at the cost of flexibility, given the ever-diminishing cost per transistor thanks to Moore's Law, incorporating fixed-function custom hardware is an increasingly attractive option for addressing the utilization wall problem by actively making use of dark silicon through hardware specialization.

Of course, a middle-ground does exist between highly-programmable but relatively inefficient FPGAs and inflexible but efficient custom hardware: researchers are increasingly developing coarse-grained reconfigurable arrays (CGRAs), that are optimized for specific application domains by limiting the degree and granularity of programmability in their designs. This is done for instance by having n-bit ALUs and buses, instead of bitwise programmable LUTs and wires. Examples of such architectures are discussed in Section 2.4.3.

However, there remain several issues with spatial architectures that must be addressed before they can be more pervasively utilized to mitigate the effects of dark silicon, particularly for the general-purpose computing domain.

# 2.4.2 Issues with Spatial Computation

Despite its considerable advantages, spatial computation has not found ubiquitous utilization in mainstream architectures, due to a variety of issues. Many of these issues are often specific to particular types of spatial architecture, and could be addressed by switching to a different type. For instance, FPGAs provide a high degree of flexibility, but incur high device costs due to their specialized, niche-market nature, as well as exorbitant compilation times due to their fine-grained nature. This makes it difficult to incorporate them into existing software engineering practices that rely on rapid recompilation and testing. FPGAs also incur considerable cost, area, performance, and efficiency penalties over custom hardware, limiting the scope of their applicability to application areas where their advantages outweigh their drawbacks [Sti11].

Some of the efficiency, performance and cost issues can be mitigated by utilizing fixed-function custom hardware, or domain-specific CGRAs, as suggested by several academic research projects [KNM<sup>+</sup>08, MCC<sup>+</sup>06, VSG<sup>+</sup>10]. However, there are two fundamental issues for spatial computation that must be addressed before such architectures can be

#### **Programmability**

Implementing computation on spatial hardware is considerably more difficult than writing code in a high level language. This is a direct consequence of the spatial nature of computation. Whereas conventional processors employ microarchitecture-level dynamic placement/allocation of operations to execution units, and rely on broadcast structures for routing of operands, spatial architectures instead relegate the responsibility of operation placement and operand routing to the higher levels of abstraction. The programmer and/or the compiler (and in some cases even the system runtime) are now responsible for explicitly orchestrating placement, routing, and execution/communication scheduling of individual operations and operands. This is analogous to the way that the shift to multicore meant that the the programmer was responsible for exposing concurrency, except that spatial computation makes this far more complex, as much more low-level hardware details must now be managed explicitly.

A related issue is that of hardware *virtualization*: for conventional processors, programmers remain unaware of the resource constraints of the underlying execution environment – for a given ISA, the hardware may implement a simple processor with fewer execution units, or a complex processor with more. The programmer need not be aware of this difference when writing code. On the other hand, the spatial nature of computation also exposes the hardware *capacity* constraints to higher levels of abstraction. The programmer must in most cases ensure that this developed spatial description satisfies all cost, resource or circuit-size constraints.

Historically, programmers relied on low-level hardware description languages (HDLs) such as Verilog and VHDL to precisely specify the hardware for the functionality that they wished to implement. More recently, design portability and programmer productivity have been improved thanks to sophisticated high-level synthesis (HLS) tools, that allow the programmer to define hardware functionality using a familiar high-level language (HLL). Many such tools support a subset of existing HLLs like C, C++, or Java [CLN<sup>+</sup>11, CCA<sup>+</sup>11], while some augment these languages with specialized extensions to simplify concurrent hardware specification in a sequential language [Pan01, PT05]. At the same time, common coding constructs that enhance productivity, such as recursion, dynamic-memory allocation and (until recently) object-oriented code are usually not permitted.

Furthermore, the quality of output from such tools is highly sensitive to the coding style used [Sti11, SSV08], thus requiring familiarity with low-level digital logic and design optimization in order to optimize the hardware for best results. Recent HLS tools manage to provide much better support for high-level languages [CLN+11, CCA+11], but nevertheless, the spatial hardware programming task remains one of describing the hardware implementation in a higher level language, instead of merely coding the algorithm to be implemented.

Due to the difficulty and cost of effectively programming spatial architectures, their use has largely been relegated to numeric application domains where the abundant parallelism is easier to express, and the order-of-magnitude performance, density and efficiency advantages of spatial computation far outweigh the costs of their programming and implementation.

#### Amenability

Conventional processors dedicate considerable core resources to managing the instruction stream, and identifying and overcoming name and control dependences between individual instructions to increase parallelism. On the other hand, spatial architectures dedicate very few resources to such dynamic discovery of concurrency, opting instead for high computational density by dedicating far more area to execution units and interconnect. In order to make full use of the available execution resources, discovering and overcoming dependences then becomes the responsibility of higher levels of abstraction.

Overcoming many statically (compile-time) known name dependences becomes trivial through use of point-to-point communication of intermediate values, since there is no centralized register file with a finite number of registers that must be reused for multiple values. Also, unlike the total order on instructions imposed by a sequential instruction stream, spatial architectures directly implement the data-flow graph of an application, which only specifies a partial order on instructions considering only memory and true dependences.

However, overcoming dependences that require dynamic (runtime) information becomes more difficult, as the statically-defined structure of a spatial implementation cannot be easily modified at run-time. Code with complex, data-dependent branching requires aggressive control-flow speculation to expose more concurrency. Based on code profiling, the compiler may be made aware of branch bias – i.e. which side of a branch is more likely to execute in general – but it cannot easily exploit knowledge of a branch's dynamic behavior to perform effective branch prediction, which tends to be significantly more accurate [MTZ13]. Similarly, code with pointers and irregular memory accesses introduces further name dependences that cannot be comprehensively overcome with only compile-time information (e.g. through alias-analysis).

Due to these issues, spatial architectures have thus far largely been utilized for application domains that have regular, predictable control-flow, and abundant data or task-level parallelism that can be easily discovered at compile-time. Conversely, for general-purpose code that contains complex, data-dependent control-flow, spatial architectures consistently exhibit poor performance.

#### Implications

For these reasons, spatial architecture utilization is restricted largely to numeric application domains such as multimedia, signal-processing, cryptography, and high-performance computing, where there is an abundance of data-parallelism, and often regular, predictable control-flow and memory access patterns. Due to an increasing demand for highly portable yet functional, multimedia oriented devices, custom hardware components are commonly included in many smartphone and tablet SOCs, particularly to accelerate video, radio-modem, and image processing codecs. Such custom hardware presents an effective utilization of dark silicon, since these components are only activated when implementing very specific tasks, and remain dark for the remainder of the time.

While FPGAs are unsuitable for the portable computing domain due to their high area and relatively higher energy cost, they are increasingly being utilized in high performance computing systems, again to accelerate data intensive tasks such as signal-processing for oil and gas exploration, financial analytics, and scientific computing [Tec12].

However, with growing expectations of improved performance scaling with future tech-

nology generations, as well as critical energy-efficiency concerns due to the utilization wall, it is becoming increasingly important to broaden the applicability, scope and flexibility of spatial architectures so they may be utilized to address these issues. Section 2.4.3 highlights several recent research projects that attempt to address the programmability and/or amenability issues with spatial computation. This brief survey shows that while considerable success has been achieved in addressing the programmability issue, addressing amenability (by improving sequential code performance) has proven more difficult, especially without compromising on energy efficiency.

# 2.4.3 A Brief Survey of Spatial Architecture Research

While there are many examples of research projects developing spatial architectures targeted at numeric application domains like multimedia, signal processing etc. [HW97, PPM09, PNBK02], this brief survey focuses on selected projects that attempt to address at least one, if not both of the key limitations of spatial architectures, namely programmability and amenability.

# RICA: The Reconfigurable Instruction Cell Array [KNM<sup>+</sup>08]

RICA is a coarse-grained reconfigurable architecture designed with the goal of achieving high energy efficiency and performance on digital signal processing applications. RICA is programmable using high-level languages like C, and executes such sequential code one basic-block at a time. To conserve energy, basic-blocks are 'depipelined', meaning that intermediate operands are only latched at basic-block boundaries, reducing the number of registers required in the design, but resulting in each basic block executing with a variable latency. To address this, execution of instructions in a block are scheduled statically, so that the total latency of each block is known at compile-time. This known clock latency is then used to *enable* the output latches from each basic block after the specified number of cycles.

RICA does not attempt to overcome control-flow dependences in any significant way. No support is provided for control-flow speculation, though the compiler does implement some optimizations such as loop unrolling and loop fusion that reduce some of the control-flow overheads. Though not mentioned, RICA might be able to implement some speculative execution through the use of compile-time techniques such as if-conversion [AKPW83] and hyperblock formation [MLC<sup>+</sup>92] to combine multiple basic blocks into larger blocks and expose more ILP across control-flow boundaries – such approaches are already used for generating statically scheduled VLIW code [ACPP05].

While RICA is able to address the issue of programmability to some degree, it still suffers from poor amenability, and as such is limited to accelerating DSP code with simple control-flow. RICA provides  $3\times$  higher throughput than a low power Texas Instruments TI C55x DSP processor, but with 2-6× lower power consumption. Compared to an 8-way VLIW processor (the TI 64X processor), RICA achieves similar performance on applications with simple control-flow, again with a 6× power advantage. However, for DSP applications with complex control-flow, RICA performs as much as 50% worse than the VLIW processor despite the numeric nature of the applications.

## The MIT RAW Architecture [TLM+04]

The RAW architecture was developed to address the problem of developing high throughput architectures that are also highly scalable. Unlike RICA's Coarse-Grained Reconfigurable Array, RAW is classified as a massively parallel processor array (MPPA), since each of its processing elements is not simply an ALU, but a full single-issue, in-order MIPS core, with its own program counter. Each such core executes its own thread of code, and also has an associated programmable router. The ISA of the cores is extended with instructions for explicit communication with neighbouring cores.

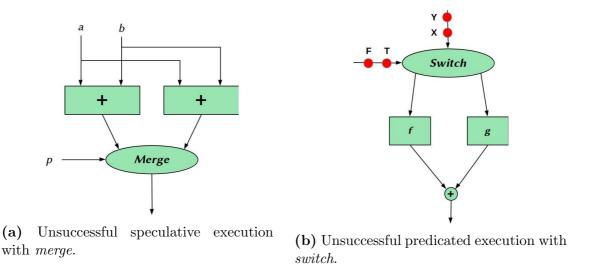

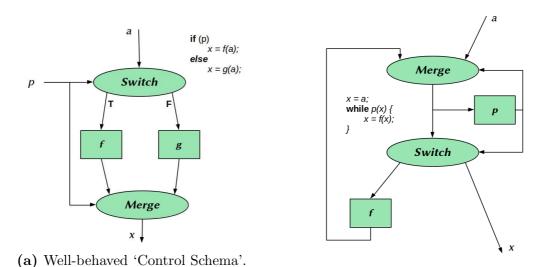

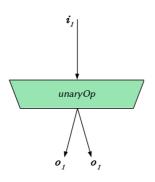

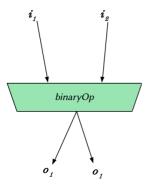

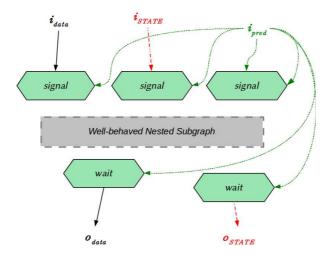

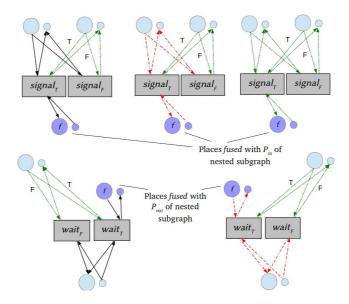

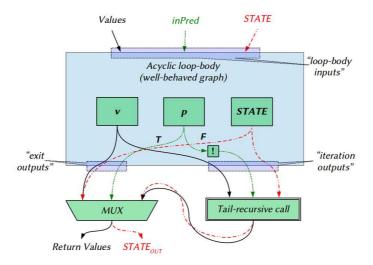

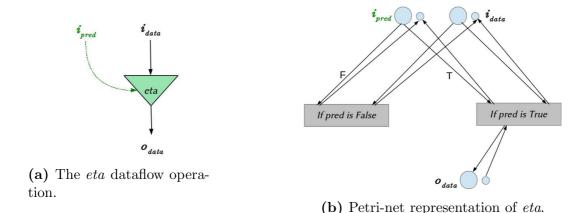

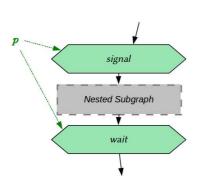

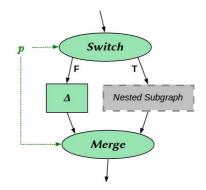

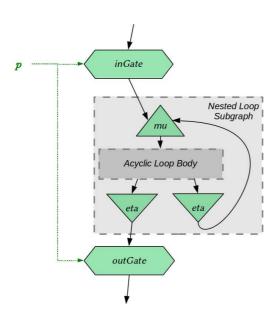

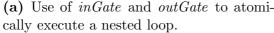

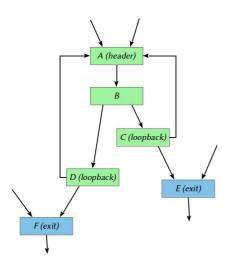

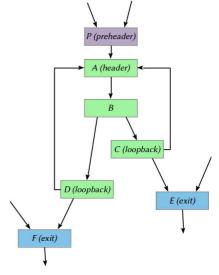

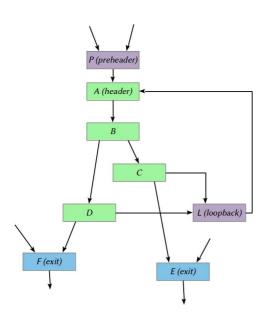

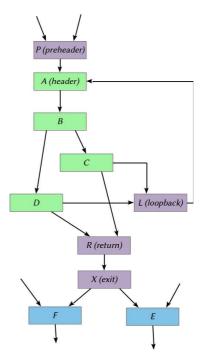

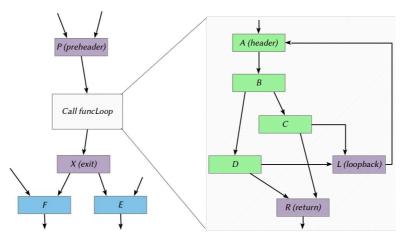

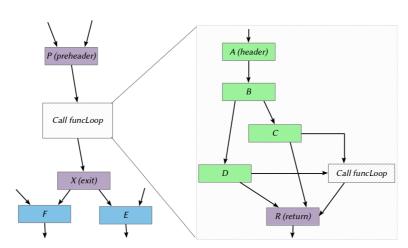

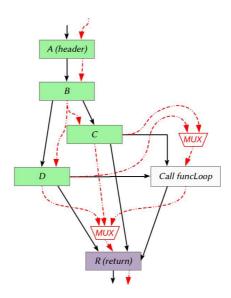

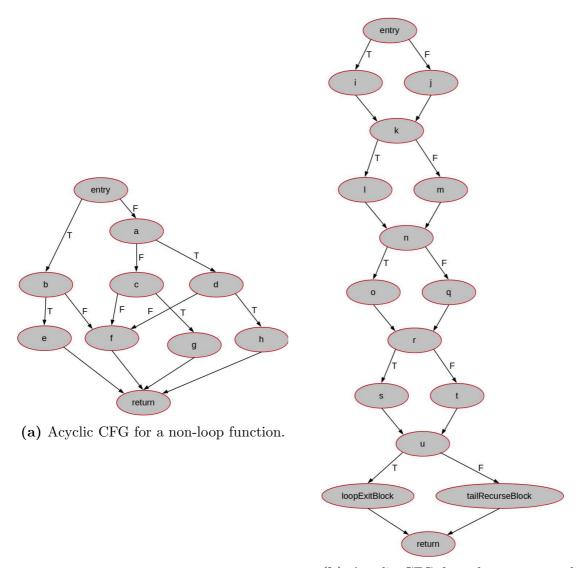

The RAW architecture supports the compilation of general-purpose applications through the use of the RAWCC compiler, which is responsible for partitioning code and data across the cores, as well as statically orchestrating communication between cores. Much like a VLIW architecture, the responsibility for exposing and exploiting ILP rests with the compiler.