Technical Report

Number 846

**Computer Laboratory**

# Exploiting tightly-coupled cores

Daniel Bates

January 2014

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

http://www.cl.cam.ac.uk/

#### © 2014 Daniel Bates

This technical report is based on a dissertation submitted July 2013 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Robinson College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

### Abstract

As we move steadily through the multicore era, and the number of processing cores on each chip continues to rise, parallel computation becomes increasingly important. However, parallelising an application is often difficult because of dependencies between different regions of code which require cores to communicate. Communication is usually slow compared to computation, and so restricts the opportunities for profitable parallelisation. In this work, I explore the opportunities provided when communication between cores has a very low latency and low energy cost. I observe that there are many different ways in which multiple cores can be used to execute a program, allowing more parallelism to be exploited in more situations, and also providing energy savings in some cases. Individual cores can be made very simple and efficient because they do not need to exploit parallelism internally. The communication patterns between cores can be updated frequently to reflect the parallelism available at the time, allowing better utilisation than specialised hardware which is used infrequently.

In this dissertation I introduce Loki: a homogeneous, tiled architecture made up of many simple, tightly-coupled cores. I demonstrate the benefits in both performance and energy consumption which can be achieved with this arrangement and observe that it is also likely to have lower design and validation costs and be easier to optimise. I then determine exactly where the performance bottlenecks of the design are, and where the energy is consumed, and look into some more-advanced optimisations which can make parallelism even more profitable.

#### ACKNOWLEDGEMENTS

First, I would like to thank my supervisor, Robert Mullins, without whose help, support and insight, this work would not have been possible.

I would also like to thank David Greaves and Steven Hand for their role in guiding me towards an achievable and worthwhile goal over the last few years.

The rest of Team Loki—Alex Bradbury, Andreas Koltes and George Sarbu—have provided countless interesting discussions, whether work-related or not, and I am indebted to them for their work on other parts of the Loki design and infrastructure. Other members of the Computer Architecture Group have also been quick to give advice and feedback when I needed it.

Thanks must go to the Raspberry Pi Foundation – I admire their aim of getting more people interested in Computer Science, and it has been a privilege to be as involved as I have been. I am also thankful for the opportunities they provided to take the occasional break from thesis-writing and meet some very interesting people.

My research was funded with a grant from the Engineering and Physical Sciences Research Council.

## CONTENTS

| 1 | Intr | oduction  | n                                                | 15   |

|---|------|-----------|--------------------------------------------------|------|

|   | 1.1  | Motiva    | ation                                            | . 15 |

|   | 1.2  | Contril   | butions                                          | . 17 |

|   | 1.3  | Publica   | ation                                            | . 18 |

| 2 | Bacl | kground   | 1                                                | 19   |

|   | 2.1  | History   | y                                                | . 19 |

|   | 2.2  | Classes   | s of architecture                                | . 21 |

|   |      | 2.2.1     | Multi-cores                                      | . 21 |

|   |      | 2.2.2     | Graphical processing units (GPUs)                | . 22 |

|   |      | 2.2.3     | Field-programmable gate arrays (FPGAs)           |      |

|   |      | 2.2.4     | Application-specific integrated circuits (ASICs) |      |

|   |      | 2.2.5     | Comparison with Loki                             |      |

|   | 2.3  | Related   | d work                                           |      |

|   |      | 2.3.1     | Network                                          |      |

|   |      | 2.3.2     | Instruction supply                               | . 26 |

|   |      | 2.3.3     | Reconfiguration                                  |      |

|   |      | 2.3.4     | Dynamic configuration                            |      |

|   |      | 2.3.5     | Miscellaneous                                    |      |

|   | 2.4  | Homog     | geneity vs. heterogeneity                        |      |

|   | 2.5  | -         | lation                                           |      |

|   | 2.6  | -         | developments                                     |      |

| 3 | Lok  | i archite | ecture                                           | 33   |

| • | 3.1  | Overvi    |                                                  |      |

|   | 3.2  |           | nicroarchitecture                                |      |

|   | 0.2  | 3.2.1     | Instruction fetch                                |      |

|   |      | 3.2.2     | Decode                                           |      |

|   |      | 3.2.3     | Execute                                          |      |

|   |      | 3.2.4     | Write back                                       |      |

|   |      | 3.2.5     | Network integration                              |      |

|   |      | 3.2.6     | Data supply                                      |      |

|   | 3.3  |           | ip network                                       |      |

|   | 5.5  | 3.3.1     | Intratile networks                               |      |

|   |      | 3.3.2     | Intertile network                                |      |

|   | 3.4  |           | ry hierarchy                                     |      |

|   | 3.5  |           | mming Loki                                       |      |

|   | 5.5  |           | Predicated execution                             | . 49 |

|   |      | 3.3.1     |                                                  |      |

|   |            | 3.5.2     | Remote execution                      | 50       |

|---|------------|-----------|---------------------------------------|----------|

|   |            | 3.5.3     | Parallelism                           | 50       |

|   |            | 3.5.4     | Loki-C                                | 51       |

|   | 3.6        | Limita    | ions                                  | 51       |

|   | 3.7        | Summa     | ury                                   | 52       |

|   |            |           |                                       |          |

| 4 |            |           |                                       | 53       |

|   | 4.1        |           | 8                                     | 53       |

|   | 4.2        | Compi     |                                       | 53       |

|   | 4.3        |           |                                       | 54       |

|   |            | 4.3.1     | <b>I</b>                              | 57       |

|   | 4.4        |           | 6                                     | 59       |

|   | 4.5        | Model     |                                       | 61       |

|   |            | 4.5.1     |                                       | 63       |

|   |            | 4.5.2     |                                       | 65       |

|   |            | 4.5.3     |                                       | 65       |

|   |            | 4.5.4     | Crossbar                              | 66       |

|   |            | 4.5.5     | FIFO buffer                           | 66       |

|   |            | 4.5.6     | Instruction decoder                   | 67       |

|   |            | 4.5.7     | Instruction packet cache              | 67       |

|   |            | 4.5.8     | -                                     | 69       |

|   |            | 4.5.9     |                                       | 70       |

|   |            | 4.5.10    |                                       | 70       |

|   |            | 4.5.11    |                                       | 71       |

|   |            | 4.5.12    | <b>I</b>                              | 71       |

|   |            | 4.5.12    |                                       | 71       |

|   |            |           | 8                                     | 71       |

|   |            |           |                                       | 73       |

|   | 4.6        |           | 1                                     | 73       |

|   | 4.0        | Summe     | пу                                    | 15       |

| 5 | Desi       | gn spac   | e exploration                         | 75       |

|   | 5.1        | Instruc   | tion supply                           | 75       |

|   |            | 5.1.1     | Instruction packet cache              | 76       |

|   |            | 5.1.2     | Instruction buffer                    | 78       |

|   |            | 5.1.3     | Cache pinning                         | 79       |

|   |            | 5.1.4     |                                       | 82       |

|   |            | 5.1.5     | 1 0                                   | 83       |

|   | 5.2        | Scratch   | 5                                     | 84       |

|   | 5.3        |           | L                                     | 87       |

|   | 5.4        |           |                                       | 90       |

|   | 5.5        |           | ,                                     | 90<br>94 |

|   | 5.5<br>5.6 | -         |                                       | 94<br>96 |

|   | 5.0        | Concit    | SIOII                                 | 90       |

| 6 | Exp        | loiting t | ghtly-coupled cores                   | 97       |

|   | 6.1        | MIMD      | · · · · · · · · · · · · · · · · · · · | 98       |

|   | 6.2        | Data-le   | vel parallelism                       | 98       |

|   |            | 6.2.1     | 1                                     | 00       |

|   |            | 6.2.2     | Evaluation                            |          |

|    |                                             | 6.2.3                                                                                                                     | Helper core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 03                                                                                                                   |

|----|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|    |                                             | 6.2.4                                                                                                                     | Instruction sharing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 04                                                                                                                   |

|    |                                             | 6.2.5                                                                                                                     | Worker farm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 08                                                                                                                   |

|    |                                             | 6.2.6                                                                                                                     | Parallelism extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12                                                                                                                   |

|    |                                             | 6.2.7                                                                                                                     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12                                                                                                                   |

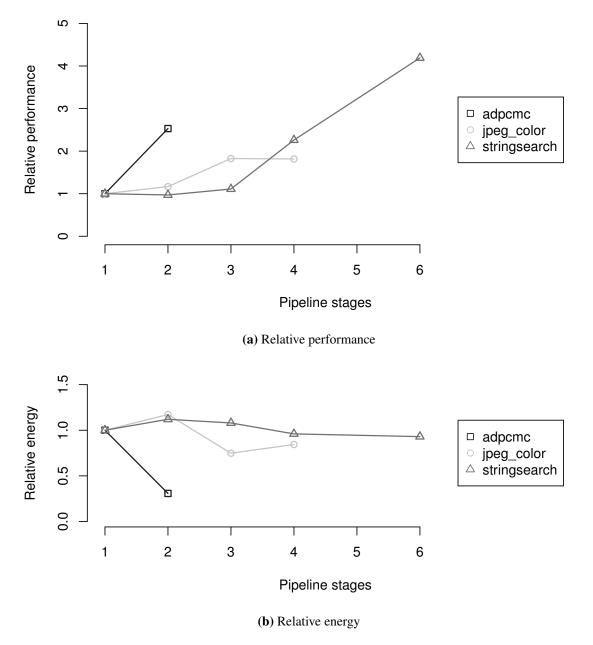

|    | 6.3                                         | Task-le                                                                                                                   | evel pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13                                                                                                                   |

|    |                                             | 6.3.1                                                                                                                     | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13                                                                                                                   |

|    |                                             | 6.3.2                                                                                                                     | Parallelism extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                                                                                                                   |

|    |                                             | 6.3.3                                                                                                                     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17                                                                                                                   |

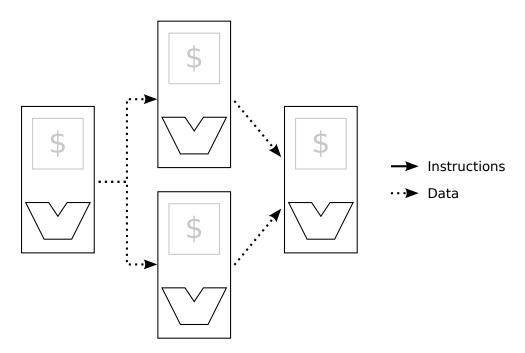

|    | 6.4                                         | Datafle                                                                                                                   | ow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17                                                                                                                   |

|    |                                             | 6.4.1                                                                                                                     | Power gating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19                                                                                                                   |

|    |                                             | 6.4.2                                                                                                                     | Case studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                                                                                   |

|    |                                             | 6.4.3                                                                                                                     | Dataflow within a core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24                                                                                                                   |

|    |                                             | 6.4.4                                                                                                                     | Reducing bottlenecks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26                                                                                                                   |

|    |                                             | 6.4.5                                                                                                                     | Reducing power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                                                                                   |

|    |                                             | 6.4.6                                                                                                                     | Reducing latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33                                                                                                                   |

|    |                                             | 6.4.7                                                                                                                     | Parallelism extraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34                                                                                                                   |

|    |                                             | 6.4.8                                                                                                                     | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35                                                                                                                   |

|    | 6.5                                         | Summa                                                                                                                     | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36                                                                                                                   |

|    |                                             |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      |

| 7  | Con                                         | elucion                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <i>A</i> 1                                                                                                           |

| 7  |                                             | clusion                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>41</b><br>42                                                                                                      |

| 7  | <b>Cono</b><br>7.1                          |                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>41</b><br>42                                                                                                      |

| -  |                                             | Future                                                                                                                    | work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |

| Bi | 7.1<br>bliogr                               | Future<br><b>aphy</b>                                                                                                     | work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42<br>52                                                                                                             |

| -  | 7.1<br>bliogr<br>Instr                      | Future<br>raphy<br>ruction                                                                                                | work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42<br>52<br>53                                                                                                       |

| Bi | 7.1<br>bliogr                               | Future<br>raphy<br>ruction<br>Datapa                                                                                      | work       1         1         set architecture       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1 | 42<br>52<br>53<br>53                                                                                                 |

| Bi | 7.1<br>bliogr<br>Instr                      | Future<br>raphy<br>ruction                                                                                                | work       1         set architecture       1         th       1         Registers       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42<br>52<br>53<br>53<br>53                                                                                           |

| Bi | 7.1<br>bliogr<br>Instr                      | Future<br>raphy<br>ruction<br>Datapa<br>A.1.1<br>A.1.2                                                                    | work       1         set architecture       1         th       1         Registers       1         Predicates       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42<br>52<br>53<br>53<br>53                                                                                           |

| Bi | 7.1<br>bliogr<br>Instr<br>A.1               | Future<br>raphy<br>ruction<br>Datapa<br>A.1.1<br>A.1.2<br>A.1.3                                                           | work       1         set architecture       1         th       1         Registers       1         Predicates       1         Channels       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42<br>52<br>53<br>53<br>53<br>53<br>53<br>54                                                                         |

| Bi | 7.1<br>bliogr<br>Instr<br>A.1<br>A.2        | Future<br>raphy<br>Datapa<br>A.1.1<br>A.1.2<br>A.1.3<br>Instruc                                                           | work       1         set architecture       1         th       1         Registers       1         Predicates       1         Channels       1         tion formats       1                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42<br>52<br>53<br>53<br>53<br>53<br>53<br>54<br>55                                                                   |

| Bi | 7.1<br>bliogr<br>Instr<br>A.1<br>A.2        | Future<br>raphy<br>cuction<br>Datapa<br>A.1.1<br>A.1.2<br>A.1.3<br>Instruc<br>Instruc                                     | work       1         set architecture       1         th       1         Registers       1         Predicates       1         Channels       1         tion formats       1         tion summary       1                                                                                                                                                                                                                                                                                                                                                                                                            | 42<br>52<br>53<br>53<br>53<br>53<br>53<br>54<br>55<br>56                                                             |

| Bi | 7.1<br>bliogr<br>Instr<br>A.1<br>A.2<br>A.3 | Future<br>raphy<br>cuction<br>Datapa<br>A.1.1<br>A.1.2<br>A.1.3<br>Instruc<br>Instruc                                     | work       1         set architecture       1         th       1         Registers       1         Predicates       1         Channels       1         tion formats       1         tion summary       1         tion reference       1                                                                                                                                                                                                                                                                                                                                                                             | 42<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>54<br>55<br>56<br>58                                                 |

| Bi | 7.1<br>bliogr<br>Instr<br>A.1<br>A.2<br>A.3 | Future<br>raphy<br>cuction<br>Datapa<br>A.1.1<br>A.1.2<br>A.1.3<br>Instruc<br>Instruc<br>Instruc                          | work       1         set architecture       1         th       1         Registers       1         Predicates       1         Channels       1         tion formats       1         tion reference       1         ALU       1                                                                                                                                                                                                                                                                                                                                                                                      | 42<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>54<br>55<br>56<br>58<br>58                               |

| Bi | 7.1<br>bliogr<br>Instr<br>A.1<br>A.2<br>A.3 | Future<br>raphy<br>Datapa<br>A.1.1<br>A.1.2<br>A.1.3<br>Instruc<br>Instruc<br>A.4.1                                       | work       1         set architecture       1         th       1         Registers       1         Predicates       1         Channels       1         tion formats       1         tion reference       1         ALU       1         Data       1                                                                                                                                                                                                                                                                                                                                                                 | 42<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>54<br>55<br>56<br>58<br>58                               |

| Bi | 7.1<br>bliogr<br>Instr<br>A.1<br>A.2<br>A.3 | Future<br>raphy<br>cuction<br>Datapa<br>A.1.1<br>A.1.2<br>A.1.3<br>Instruc<br>Instruc<br>A.4.1<br>A.4.2                   | work       1         set architecture       1         th       1         Registers       1         Predicates       1         Channels       1         tion formats       1         tion reference       1         ALU       1         Data       1         Instruction fetch       1                                                                                                                                                                                                                                                                                                                               | 42<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>55<br>56<br>58<br>58<br>58                         |

| Bi | 7.1<br>bliogr<br>Instr<br>A.1<br>A.2<br>A.3 | Future<br>raphy<br>Datapa<br>A.1.1<br>A.1.2<br>A.1.3<br>Instruc<br>Instruc<br>A.4.1<br>A.4.2<br>A.4.3                     | work       1         set architecture       1         th       1         Registers       1         Predicates       1         Channels       1         tion formats       1         tion reference       1         ALU       1         Data       1         Instruction fetch       1         Memory       1                                                                                                                                                                                                                                                                                                        | 42<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>54<br>55<br>56<br>58<br>58<br>58<br>58             |

| Bi | 7.1<br>bliogr<br>Instr<br>A.1<br>A.2<br>A.3 | Future<br>raphy<br>cuction<br>Datapa<br>A.1.1<br>A.1.2<br>A.1.3<br>Instruc<br>Instruc<br>A.4.1<br>A.4.2<br>A.4.3<br>A.4.4 | work       1         set architecture       1         th       1         Registers       1         Predicates       1         Channels       1         tion formats       1         tion reference       1         ALU       1         Data       1         Instruction fetch       1         Memory       1         Network       1                                                                                                                                                                                                                                                                                | 42<br>52<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>53<br>55<br>56<br>58<br>58<br>58<br>58<br>58<br>59<br>60 |

## LIST OF FIGURES

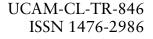

| 3.1  | High-level Loki architecture                           | 4             |

|------|--------------------------------------------------------|---------------|

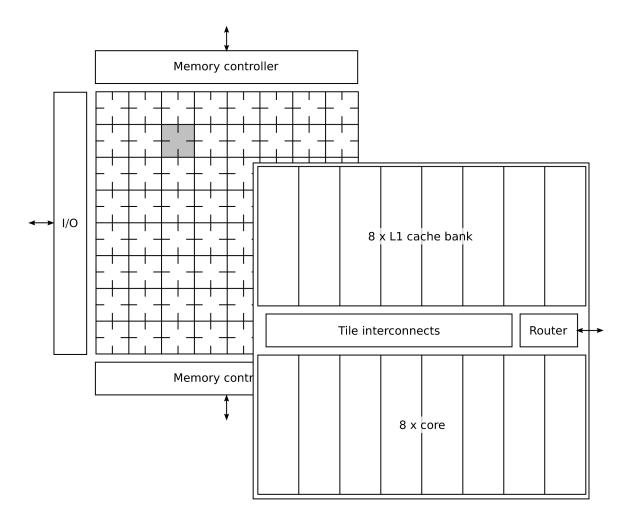

| 3.2  | Loki pipeline                                          | 6             |

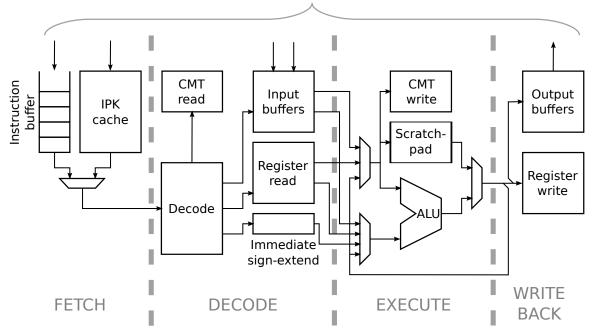

| 3.3  | Loki instruction sources                               | 8             |

| 3.4  | Loki instruction formats                               | -1            |

| 3.5  | Network assembly code                                  | 4             |

| 3.6  | Register file                                          | .5            |

| 3.7  | Loki assembly code demonstrating use of the scratchpad | .5            |

| 3.8  | Tile sub-networks                                      | .7            |

| 3.9  | Loki-C code sample                                     | 1             |

| 4.1  | Effects of hand-optimisation                           | 8             |

| 4.2  | 1                                                      | 52            |

| 7.2  |                                                        | 2             |

| 5.1  | Instruction packet cache implementations               | 7             |

| 5.2  | Behaviour of instruction buffer relative to L0 cache   | 9             |

| 5.3  | Instruction supply energy distribution                 | 0             |

| 5.4  | Effects of cache pinning 8                             | 31            |

| 5.5  | Buffer pinning                                         | 3             |

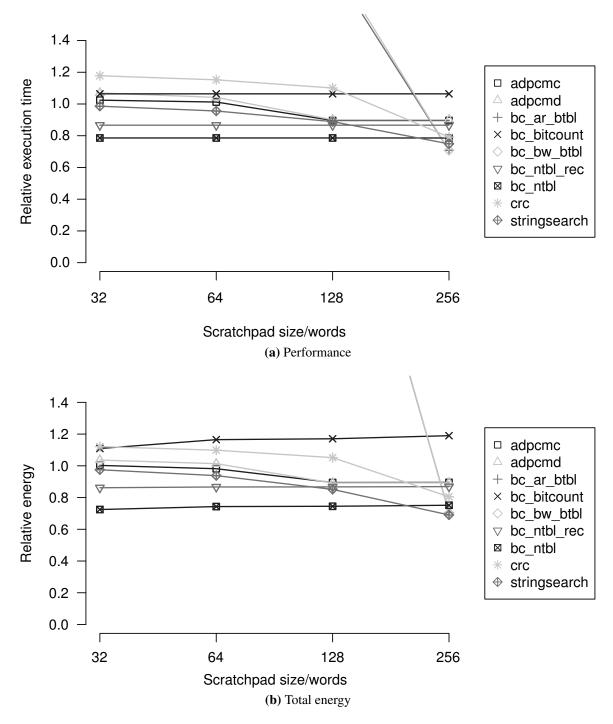

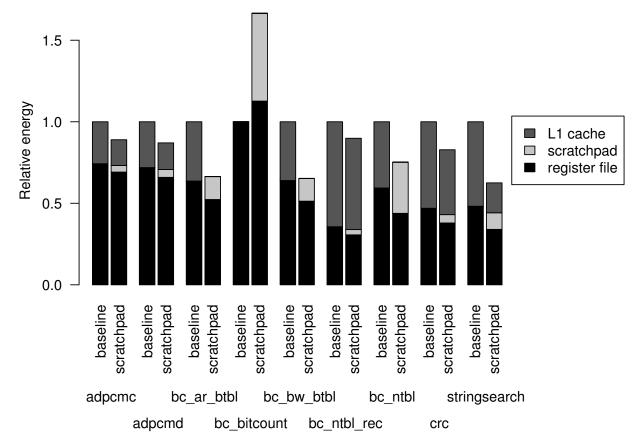

| 5.6  |                                                        | 5             |

| 5.7  |                                                        | 7             |

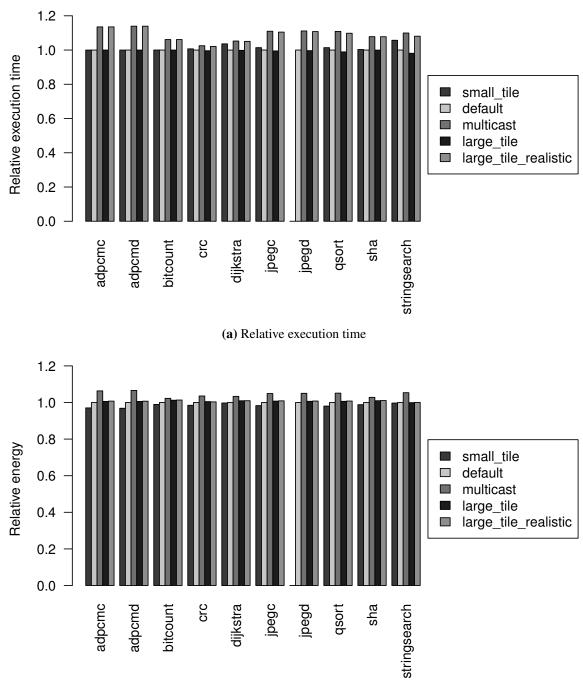

| 5.8  | Network comparison                                     | 9             |

| 5.9  |                                                        | 2             |

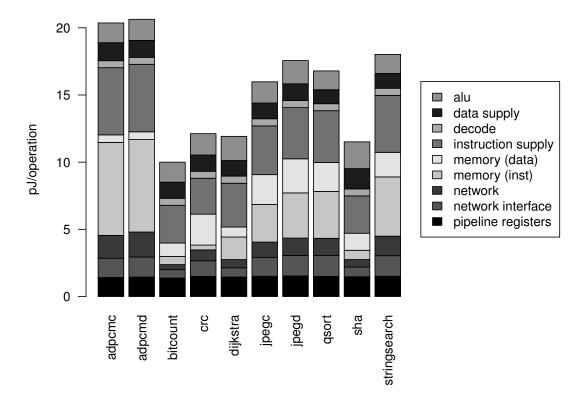

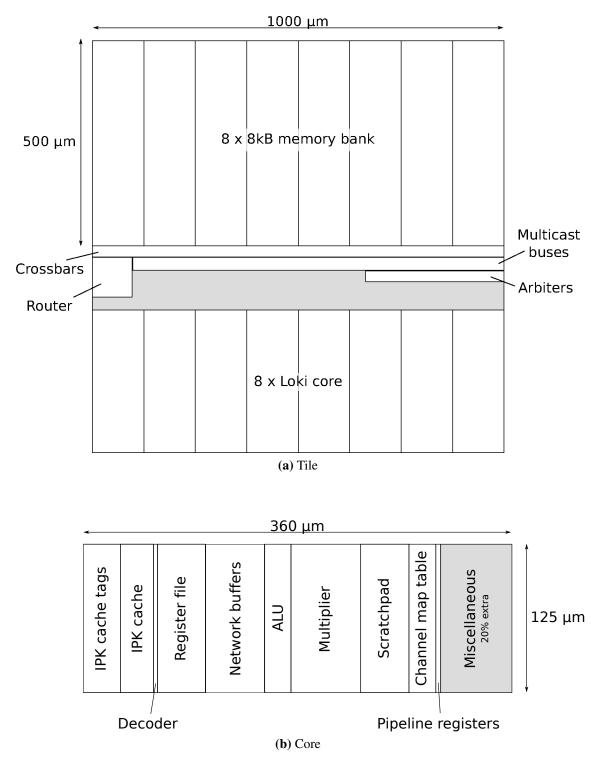

| 5.10 | Loki architecture floorplan                            | 3             |

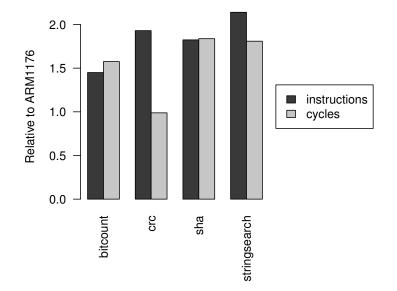

| 5.11 | Comparison with ARM1176                                | 95            |

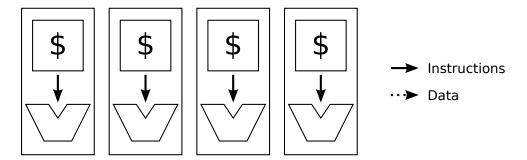

| 6.1  | MIMD execution pattern                                 | 8             |

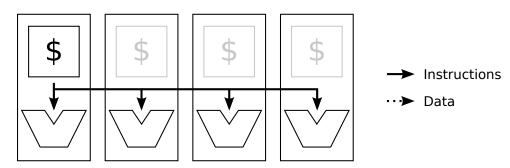

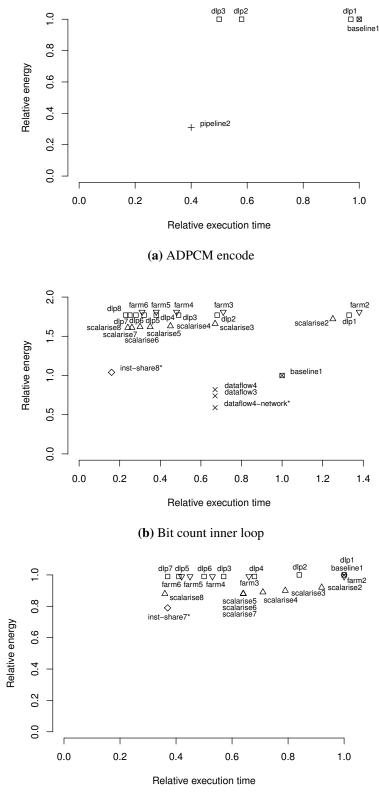

| 6.2  | DLP execution pattern                                  | -             |

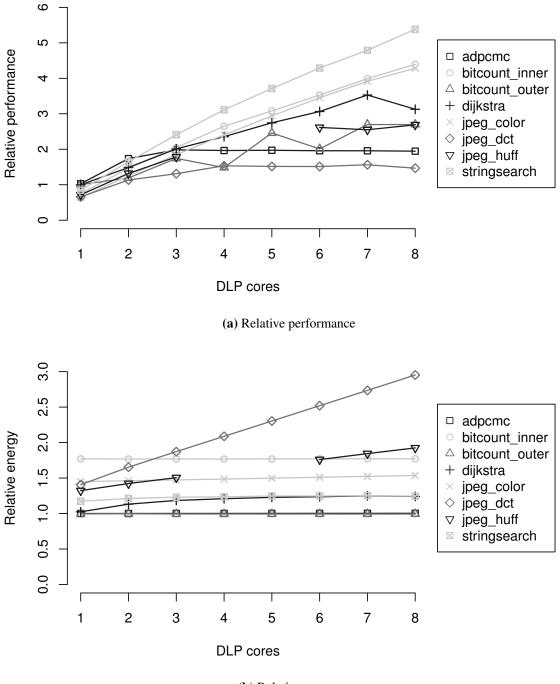

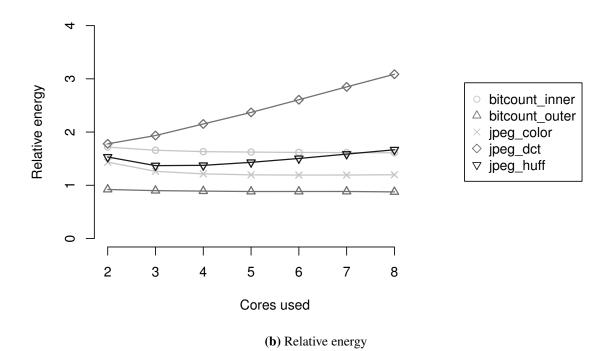

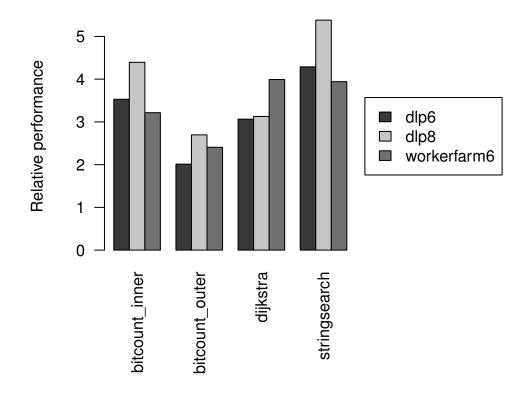

| 6.3  | Impact of DLP execution                                |               |

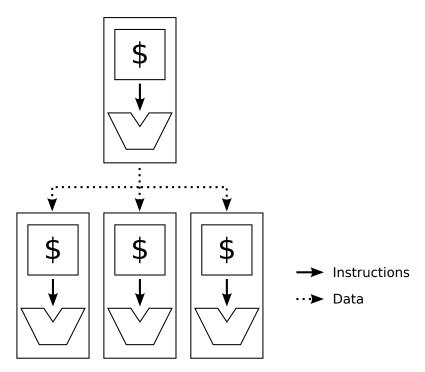

| 6.4  | DLP execution pattern with helper core                 |               |

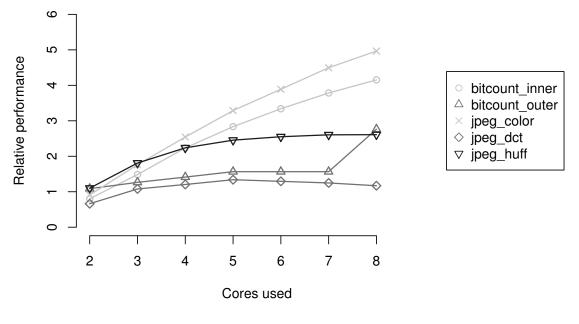

| 6.5  | Impact of DLP execution, with helper core              |               |

| 6.6  | Divergent code example                                 |               |

| 6.7  | DLP execution pattern with instruction sharing         |               |

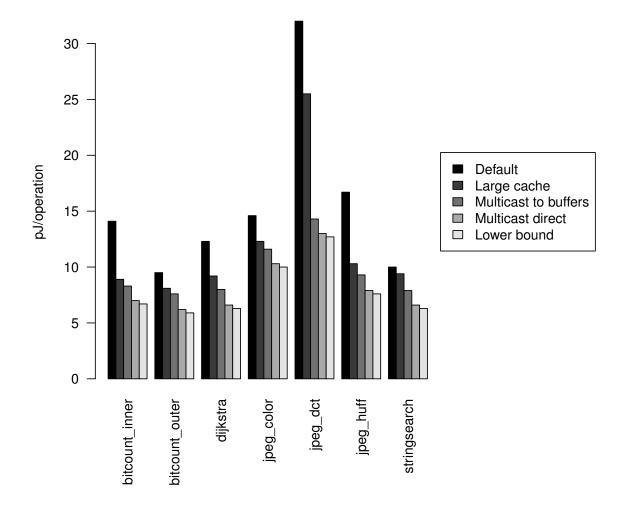

| 6.8  | DLP energy consumption with instruction sharing        |               |

| 6.9  | Worker farm execution pattern                          |               |

| 6.10 |                                                        |               |

| 6.11 |                                                        |               |

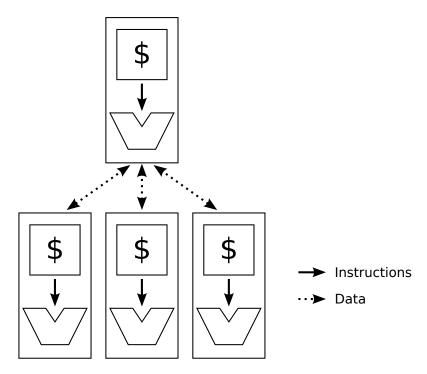

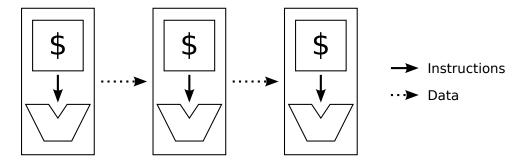

|      | Task-level pipeline execution pattern                  |               |

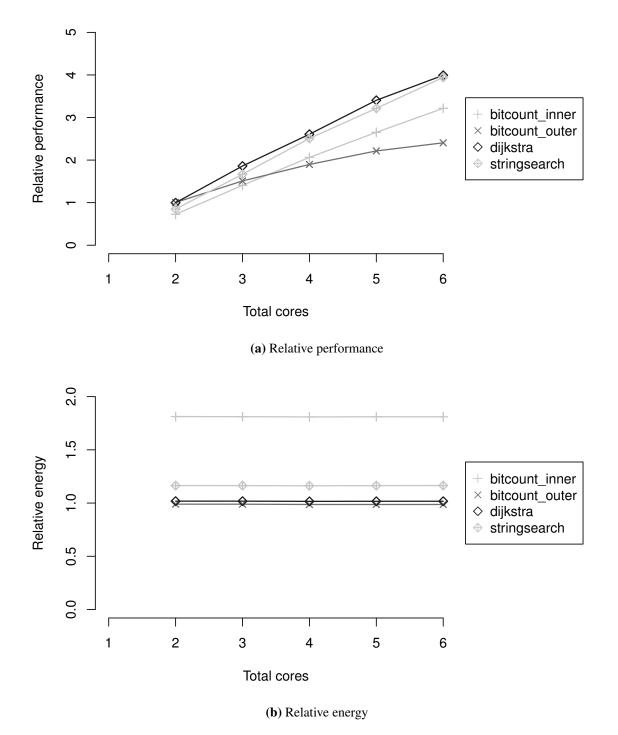

|      | Task-level pipeline behaviour   11                     |               |

| 0.15 |                                                        | $\mathcal{I}$ |

| 6.14 | Dataflow execution pattern                           |

|------|------------------------------------------------------|

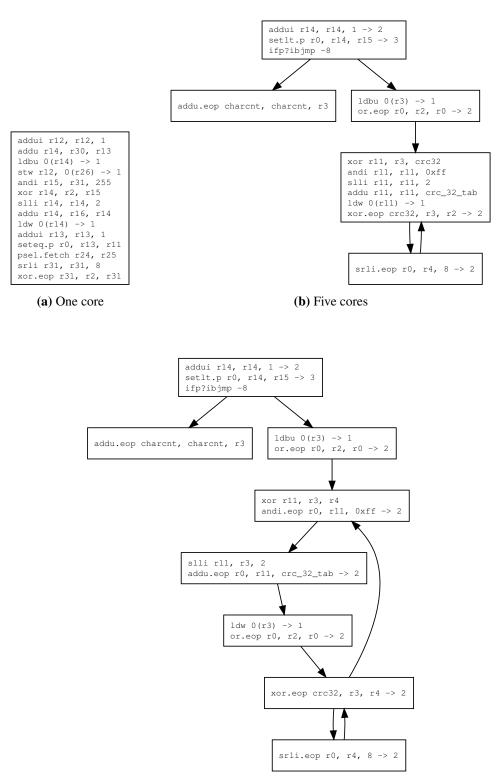

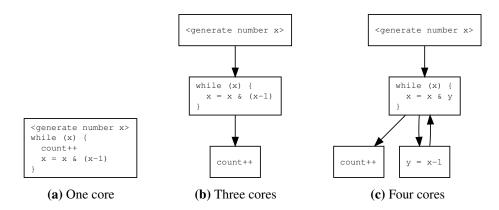

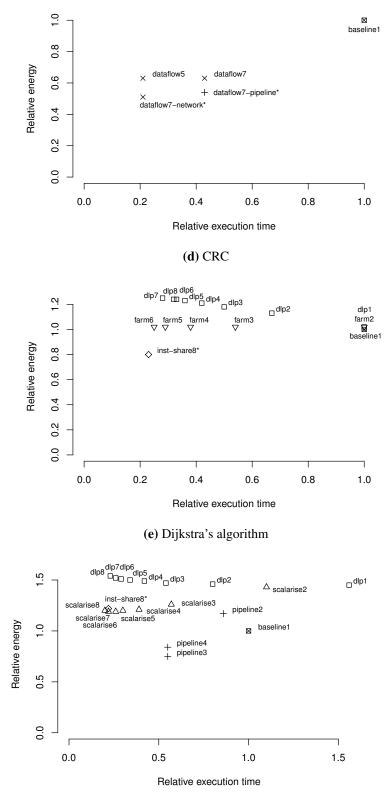

| 6.15 | CRC dataflow mappings                                |

| 6.16 | CRC dataflow behaviour                               |

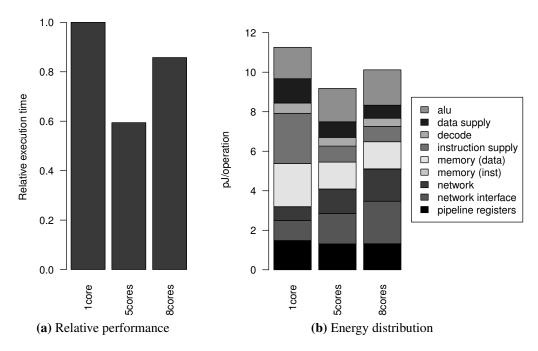

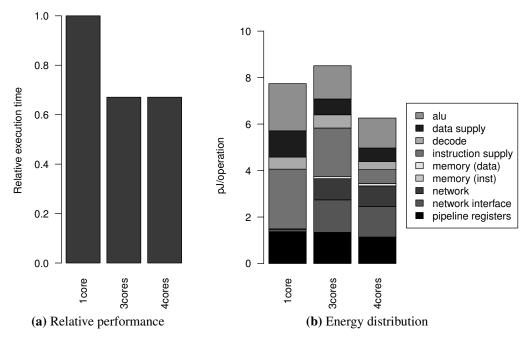

| 6.17 | Bit count dataflow mappings                          |

| 6.18 | Bit count dataflow behaviour                         |

| 6.19 | A bottleneck packet in the crc benchmark             |

| 6.20 | A bottleneck packet in the <i>bitcount</i> benchmark |

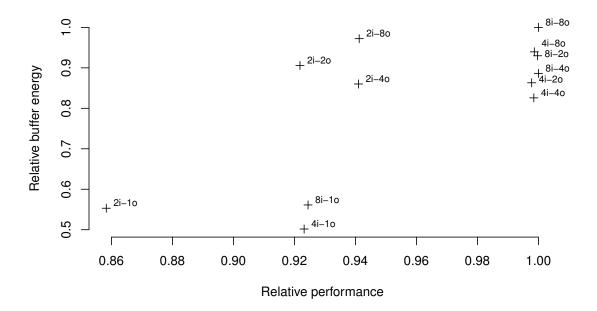

| 6.21 | Network buffer design space exploration              |

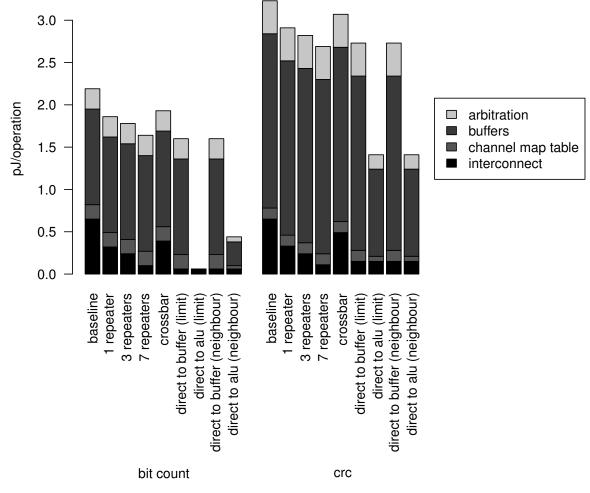

| 6.22 | Core-to-core interconnect comparison                 |

| 6.23 | Summary of execution patterns                        |

## LIST OF TABLES

| 2.1        | FPGA lookup table    23                                          |

|------------|------------------------------------------------------------------|

| 3.1<br>3.2 | Core input channel mapping    42      Predicate encodings.    50 |

| 5.2        |                                                                  |

| 4.1        | Comparison of benchmark suites                                   |

| 4.2        | Benchmark execution characteristics                              |

| 4.3        | Supported ALU operations                                         |

| 4.4        | ALU model                                                        |

| 4.5        | Arbiter model                                                    |

| 4.6        | Clock model                                                      |

| 4.7        | Crossbar model                                                   |

| 4.8        | FIFO models                                                      |

| 4.9        | Decoder model                                                    |

| 4.10       | Cache tag models                                                 |

|            | Instruction packet cache models                                  |

| 4.12       | Interconnect model                                               |

|            | L1 cache bank model                                              |

| 4.14       | Multicast network model                                          |

| 4.15       | Multiplier model                                                 |

|            | Pipeline register model                                          |

|            | Register file model                                              |

|            | Router model                                                     |

|            | Scratchpad model                                                 |

| 5.1        | Instruction packet cache implementations                         |

| 5.2        | Data structures in MiBench programs                              |

| 5.3        | Loki structure sizes                                             |

| 5.4        | Energy consumption of common operations                          |

| 6.1        | New fetch instructions                                           |

| 6.2        | Network energy comparison                                        |

| 6.3        | Dataflow architecture comparison                                 |

| 6.4        | Summary of dataflow optimisations                                |

| A.1        | Register uses                                                    |

| A.2        | Predicate encodings                                              |

| A.3        | Core input channel mapping                                       |

| A.4        | Core output channel mapping                                      |

| A.5 | nstruction set summary | 56 |

|-----|------------------------|----|

| A.6 | ALU functions          | 58 |

## CHAPTER 1

#### INTRODUCTION

This dissertation describes Loki, a homogeneous, many-core architecture targeted at embedded systems. One of Loki's main features is flexible and efficient communication between cores, allowing them to be grouped together in software to form an optimised *virtual architecture*. This software specialisation using tightly-coupled cores allows both improved performance and reduced energy consumption, whilst also addressing many other challenges faced by today's computer architects.

## **1.1 Motivation**

Multi-core chips dominate the consumer market today. Everything from smartphones, through tablets and desktops, all the way up to servers make use of multi-core processors, and the number of cores continues to rise as architects struggle to make effective use of the extra transistors they gain each process generation. A group from the University of California, Berkeley describe the situation well [12]:

The shift toward increasing parallelism is not a triumphant stride forward based on breakthroughs in novel software and architectures for parallelism; instead, this plunge into parallelism is actually a retreat from even greater challenges that thwart efficient silicon implementation of traditional uniprocessor architectures.

The problem with the trend towards multiple cores is that even after decades of research into parallelism, many applications do not make effective use of parallel architectures [21], and it seems unlikely that the number of applications executing simultaneously will scale with the number of processor cores. Work has been done on cache coherence and message passing to make using multiple cores easier, but more needs to be done if the full potential of future processors is to be realised.

One of the main challenges is the power wall: the inability to increase power consumption of processors due to limitations of the power supply (such as batteries in mobile devices) or the ability to dissipate heat cheaply. Much of the exponential performance improvements of microprocessors that we have enjoyed to date came at a cost of increased power consumption; this was a reasonable tradeoff at the time, but cannot continue today. Several factors conspire to make the power wall even more intimidating:

• As we continue to shrink features on integrated circuits, the energy consumed by each transistor goes down, but the delay and energy consumed per unit length of wire go up.

The delay rises due to increased resistance of the narrower wires, and so more powerhungry repeaters are required to maintain clock rates [63]. This suggests that large uniprocessors are no longer sensible and a move to decentralised resources is necessary in order to reduce communication distances [6].

- The clock frequency of a microprocessor is intimately linked with power consumption. Each change of state of a transistor or wire costs roughly the same amount of energy, but a higher frequency means that the state can change more often, increasing power consumption. Many techniques employed to increase clock frequencies also bring with them additional energy costs: deeper pipelining, for example, requires additional pipeline registers and more-aggressive circuits. Since this power increase is no longer an option, clock frequencies of desktop and server chips have stalled, along with the associated increase in performance. Other ways of improving performance, such as exploiting instruction-level parallelism, are also near their limits: ever more complex branch prediction and increased speculation are required to find further independent instructions, both of which require energy.

- Dennard scaling—the ability to reduce the supply voltage as transistors become smaller has essentially stopped. Power consumed when a transistor switches is proportional to the square of the voltage, so the regular decline in voltage each generation held the power wall at bay. Any attempts to reduce the threshold voltage of transistors to allow a lower supply voltage result in increased leakage current. Leakage power has quickly gone from a negligible overhead to a source of energy consumption comparable with the total energy used by active parts of the chip.

- Smaller transistors are less reliable due to fluctuations in the density of dopant atoms in the underlying silicon [22]. The obvious solution to unreliable systems is redundancy, but this involves performing additional computation, which increases energy requirements.

A consequence of the power wall in combination with the ever-increasing number of transistors available due to Moore's Law is that we may no longer be able to use all of the available transistors at the same time. This problem is known as the *utilisation wall* or *dark silicon*, and implies that some form of specialisation will be required to reduce the fraction of the chip in use at any one time [37]. A move towards specialised hardware is also desirable because of the relatively high overheads of general-purpose chips [51].

Indeed, modern chips often bundle a number of different specialised processors, cache, and other logic together, usually with a general purpose processor to fall back on when no accelerator is available. The result is a *system-on-chip* (SoC) capable of general purpose computation, but which can achieve high performance and energy efficiency for many common operations such as graphics and signal processing. This approach has seen success in the mobile market as the reduction in the number of chips reduces circuitboard area and packaging costs, and is also gaining popularity in the desktop landscape.

The move to heterogeneous computing will likely provide only a short reprieve from the challenges faced by computer architects, however, and I believe that the balance will start to swing back towards homogeneity in the near future.

• Design and validation costs are increasing rapidly as we move to smaller feature sizes. Including many different specialised units will only increase these costs, and managing communication between them complicates the design further.

- Providing many different processing units means that many different forms of fault tolerance need to be implemented when we cannot rely on all transistors working correctly.

- Heterogeneous systems are more difficult to program, and as software and algorithms become increasingly complex, this becomes less acceptable.

Computer architects are trapped by all of the constraints and walls: they can't dynamically extract more ILP, they can't use additional power to improve performance, they can't scale the voltage down to reduce power consumption, and they can't add specialised hardware because it will soon become too difficult to design and use. The only escape route seems to be to make a step-change in the design of microprocessors – one which takes into account *all* of the current challenges, rather than making incremental changes to decades-old designs.

Computer architecture is often described as a science of tradeoffs: there are many different metrics for which a design can be optimised, most of which have conflicting requirements. Smartphone consumers demand the most powerful hardware capable of advanced 3D graphics, and a large, bright, high resolution screen, whilst simultaneously complaining if battery life drops. The problem is that these tradeoffs are not static: processors designed today face completely different constraints to those designed only a decade ago. Momentum in industry dictates that processor designs are evolutionary rather than revolutionary in order to maintain backwards-compatibility, but this direction appears to be leading us to a dead-end.

In this dissertation, I attempt to take a step back and look ahead to determine what a processor should look like in the near future, in a world where high performance is needed with low power consumption. Specialisation will be required to achieve efficiency, but sacrificing programmability is unacceptable. Furthermore, we will not be able to guarantee that all of the chip will behave as expected, and design and validation costs are expected to continue rising exponentially.

To this end, I introduce Loki, a many-core homogeneous architecture, where cores are very simple and designed to be dynamically grouped together to execute a program. Flexible and efficient communication between cores is key, and allows for specialisation in software. This design attempts to address the issues imposed by Amdahl's law by allowing multiple cores to be used to accelerate both parallel and sequential regions of code. I demonstrate how tight coupling between cores can be used both to improve performance and to reduce energy consumption.

### **1.2** Contributions

My thesis is that efficient communication between processor cores provides opportunities for flexible parallelism, which can be profitable in terms of both energy and performance. In order to demonstrate this, I make the following contributions:

- I *introduce the Loki architecture*: a simple, homogeneous, many-core fabric, where communication between cores is fast and energy-efficient (Chapter 3).

- I provide *detailed energy, area and performance models* of the main components of the design, and show where the energy is consumed during execution (Chapter 4).

- I perform a simple *design space exploration* to determine a sensible implementation for a single tile of the Loki architecture (Chapter 5).

- I demonstrate that *efficient communication opens up a wide range of parallelism opportunities*, and that it becomes possible to map programs to the architecture in ways which are tailored to each program, or even each phase of an individual program (Chapter 6).

- I show that as well as improving performance, *mapping an application across multiple cores can be used to reduce energy consumption* (Chapter 6).

- I *explore software and hardware optimisations* to further increase the profitability of parallelism (Chapter 6).

My work was undertaken as part of the larger Loki project, and the design of the architecture was shaped by all members of the group and the needs of their research. I therefore must clarify which parts of this thesis are *not* my work. As far as possible, I treat others' contributions as constants; I may discuss opportunities allowed by their work, but do not explore them.

- The compilation toolchain was developed by Alex Bradbury. This had influences on the choice of instruction set, and on the communication mechanism between cores. Alex also performed an energy and performance characterisation of an ARM processor.

- The memory system from the L1 cache onwards is the work of Andreas Koltes. Again, the instruction set was influenced, and some small additions were made to the core's pipeline to optimise cache accesses.

- Robert Mullins made a significant contribution to the energy modelling framework. This included many base SystemVerilog designs, and semi-automation of the synthesis tools. He also produced the instruction set encoding.

## **1.3** Publication

A summary of this dissertation, with a particular focus on Chapters 3 and 6 is presented in the following peer reviewed publication.

**D. Bates**, A. Bradbury, A. Koltes, R. Mullins, *Exploiting tightly-coupled cores*, International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS XIII), July 2013

## CHAPTER 2

### BACKGROUND

This chapter covers the main features of the architectures which have influenced Loki's design in some way. It starts with a high-level overview of broad classes of computer architecture, and then drills down into work which is more-closely related to Loki. It is of course impossible to cover all influential work, but an attempt has been made to include everything significant.

### 2.1 History

This section gives a brief overview of the design of computer processors leading up to the present day. Reasons for design decisions are explained, and the problems facing today's computer architects are discussed. Much of the information is drawn from work by Horowitz [54] and Weste & Harris [133].

The first digital computers were necessarily very simple; they were limited by the designers' ability to manually draw and place all of the components in the design phase and maintain the finished machine. Early machines were also very large, expensive and power-hungry.

The invention of the transistor greatly improved the size and power consumption of early computers, but reliability was still an issue – the mean time to failure of the Harwell CADET was around 90 minutes [76]. Advances in transistor design and manufacturing technology provided steady improvements.

Integrated circuits in the 1970s brought about another step-change, allowing thousands of transistors to be placed on a single chip, each of which was much cheaper, much more reliable, much faster and much lower-power than its discrete counterpart. Continued refinement of the manufacturing process has continued to this day, with billions of transistors per chip now possible.

Performance of microprocessors increased exponentially at around 50% per year between the mid-1980s and early 2000s. This was due to advancements in several areas. The execution time of a program can be broken down to expose a number of factors which we are able to target to improve performance, and reduction of any one of these will improve the overall execution time:

$$\frac{time}{program} = \frac{time}{cycles} \times \frac{cycles}{instructions} \times \frac{instructions}{program}$$

The clock period of microprocessors  $(\frac{time}{cycle})$  has improved greatly through a combination of advancements in manufacturing technology and pipelining.

In an attempt to keep up with the self-fulfilling prophecy that is Moore's Law, semi-conductor manufacturers have been steadily shrinking the sizes of features that can be implemented on sil-

icon chips. Each generation, the minimum feature size shrinks by 30%, and smaller transistors hold less electric charge, so are able to switch states about  $1.4 \times$  quicker each generation. There were seven process generations in the two decades described, giving a  $10 \times$  speedup. This trend looks set to continue for a while, at least, with many companies using Moore's Law as a roadmap and investing increasing sums in trying to maintain the exponential rate of development. However, we are nearing the end of CMOS, where statistics and quantum effects will mean that the number of dopant atoms in transistors will vary widely, resulting in different behaviours and even malfunction of some transistors.

In addition to improving existing transistors, new, faster logic families were discovered, offering roughly  $2.5 \times$  improvements. Improvements to these low-level building blocks of digital circuits have wide-reaching effects across the design.

The advent of reduced instruction set computing (RISC) made pipelining much more achievable because of its simpler instructions with predictable execution times. Pipeline lengths increased, reducing the amount of logic between pipeline registers and allowing clock frequencies to rise. RISC was also helped by continuous improvements to compiler technology and memory capacity, making the lower instruction density less of an issue. Pipelines increased from 5 to 20+ stages during this period, allowing a  $4 \times$  improvement in clock rates. RISC was so successful in driving clock frequencies up that many architectures with more-complex instruction sets started to internally translate their instructions into RISC-like microcode so that they could take advantage of the same techniques. This trend was not sustainable for two main reasons:

- 1. Increasing the clock frequency increased the power consumed by the chip superlinearly, as splitting the pipeline into more stages required complex logic and additional pipeline registers, and each transistor was switching on and off more times per second [111]. The power dissipation of processors hit various limits depending on the application domain the *power wall*. Mobile devices such as laptops and mobile phones became more popular, and had very strict energy constraints imposed by their limited battery supplies. In the desktop and server market, the limits of how much heat could be cheaply dissipated from the chip were being reached. Servers have now reached a point where the cost of powering and cooling the chip over its lifetime is more than the cost of the chip itself [26].

- 2. There are not many natural points to split the pipeline up. As the number of stages increased, more of the fundamental pieces of the pipeline, such as the ALU and cache, needed to be spread across multiple stages. This increased complexity, and was not always worthwhile due to non-linear performance gains [111].

Today, with power consumption as a first-order design constraint, pipeline lengths have dropped and there has even been convergence between the mobile and desktop worlds: Intel's Core i series has 14-16 stages (the precise number has not been revealed) [38], and ARM's A15 has 15 stages [74].

The process of shrinking transistors not only improved their performance and energy consumption, but also allowed more of them to fit on a single chip. This paved the way for additional logic and memory, which allow more work to be performed each cycle (reducing  $\frac{cycles}{instruction}$ , otherwise known as CPI).

The structure of pipelines changed so that more work could be done at once. Datapath widths increased from 8 to 64 bits, allowing manipulation of larger numbers with fewer instructions. There are limits to how far this trend can continue because increasing the bus width adds an overhead to any instructions which do not need the full width, and there is currently limited need for anything beyond 64 bits. Many architectures now offer special vector instructions and

registers, allowing the same operation to be performed on multiple operands simultaneously without impacting the common case.

Pipelines also introduced multiple functional units to allow multiple independent instructions to be executed simultaneously. Again, there are limits to the number of independent instructions which can be found. While there is often a large amount of available ILP [83], it is usually hard to access. Finding enough independent instructions to supply all functional units requires speculation across multiple branches and accesses to many separate parts of the instruction (and data) store simultaneously, which is expensive to support.

Compiler technology improved greatly as higher-level languages became more popular, reducing the number of instructions used to execute a program.

In total, these changes to caches, datapaths and compilers delivered a  $5-8 \times$  improvement in SPECint/MHz, a measure of how productive a processor is each clock cycle. This improvement took place even with the much-reduced clock period.

In recent years, to try to continue improving performance of microprocessors despite all of the obstacles in the way, chip designers have turned to placing multiple cores on each chip. The performance of each core now increases only slowly, if at all, and instead the number of cores on each chip increases exponentially. Mobile devices with four or more cores are not uncommon today.

The problem with this new approach is that in order to take advantage of the multiple cores, there needs to be available thread level parallelism (TLP). It is not too difficult to find small amounts of TLP: multiple programs can run at the same time, or a single program can have separate threads for the user interface and the background processing to keep everything running smoothly, but TLP is not scaling anywhere near as quickly as the number of cores per chip, despite the decades of research that have been put into parallel computation [21].

The work in this dissertation looks ahead a few years, assuming that the number of cores keeps increasing, to a time where single chips can have hundreds or thousands of cores. I explore how these cores might be implemented and how such a large number of them can be managed and utilised effectively. Available thread level parallelism is expected to rise slightly, as devices perform an increasing amount of background processing, and programmers slowly begin to write more-parallel applications, but I concentrate on exploiting other forms of parallelism within individual applications to make use of the many cores.

### 2.2 Classes of architecture

This section describes the main broad classes of architecture which currently exist, and the tradeoffs between them. Each class is designed for a different purpose and is at a different point in the design space encompassing programmability, flexibility, cost and energy efficiency. There are also architectures which attempt to bridge the gaps between different classes to combine a number of different desirable traits.

#### 2.2.1 Multi-cores

Multi-core processors are ubiquitous today, in devices ranging from mobile phones to servers. They are an evolution of the "standard" single-core chips which came previously; they consist of multiple cores with additional logic to ensure that shared structures (such as caches and memory contollers) are always in a consistent state. Architects were forced to head in this direction because of the diminishing returns in making single cores faster and more complex.

Many multi-cores are homogeneous (Intel, AMD, Tilera), but some are heterogeneous to optimise for the various use cases. Cell [46] offers one complex core for handing controlintensive code, and eight simpler vector units optimised to speed up data processing. Modern mobile phone processors typically have two to four general purpose cores, and a large number of accelerators to improve performance and reduce energy consumption of common operations such as video decoding.

General-purpose processors are the easiest of these architectures to program. There is an established compiler infrastructure which can transform a large range of high-level languages to the required machine code. The problems are that writing code for multiple cores is often difficult due to the need to find parallelism whilst avoiding conflicts and deadlock, and that the flexibility introduces inefficiency. Only a small portion of the area of a processor is devoted to computation; the rest is there to make sure there is a steady supply of instructions and data, and that the instructions can execute quickly. It has been shown that only 6% of the energy of a representative general-purpose processor is used to perform arithmetic [33].

#### 2.2.2 Graphical processing units (GPUs)

With the increasing importance of graphical user interfaces and smooth 3D graphics in games, architectures specialised for computer graphics have become common. Typical workloads involve massive data-level parallelism, since graphical computations often involve performing the same task for each pixel on the screen or each vertex in a model.

The usual approach is to have a huge number of threads. These are organised into *thread blocks* which represent the computation to be performed, and are in turn split into *warps* (in NVIDIA's nomenclature). A warp may consist of 32 threads, all of which execute the same code simultaneously on one of the GPU's *streaming multiprocessors*. This means that only one instruction fetch unit is required for each warp, greatly reducing the resources spent supplying instructions to the functional units. The huge number of threads is used to hide memory latency: if a warp requests data which is not held locally, instructions from other warps are issued until the data arrives. This reduces the need for on-chip cache, making space for more functional units.

GPUs are more energy efficient and perform better than general-purpose processors for their domain of applications, but their specialisation means that they are useful less of the time. When the number of threads drops, performance is impacted since it is no longer possible to hide memory latency. Dealing with control flow is also awkward. Since all threads in a warp execute the same instruction at the same time, there are problems if different threads are on different paths. In practice, all required paths are executed sequentially, with some way of masking out threads which do not need to execute the current instructions.

There is a movement towards making GPUs more general purpose and easier to program so that their efficiency can be used more of the time [95], and a similar movement towards making it possible for general purpose processors to exploit increasing amounts of data-level parallelism [1]. Taking one step further, OpenCL [67] provides a framework for writing parallel code which can be used across both CPUs and GPUs. This trend also includes hardware modifications such as adding increasingly-wide SIMD units to general-purpose processors, and adding scalar execution resources to GPUs [85].

The two classes of architecture are also physically being brought closer together, with many companies providing general-purpose processors and a number of graphics cores on the same chip. In addition, AMD plans to introduce a shared ISA and dynamic run-time compilation, so

that code can transparently migrate between GPU and CPU depending on the available parallelism [110]. This trend suggests that perhaps in the future the two architectures will converge as a massively-parallel, general-purpose architecture.

#### 2.2.3 Field-programmable gate arrays (FPGAs)

FPGAs consist of a large number of lookup tables (LUTs) and a configurable interconnect which can be used to simulate arbitrary digital circuits. Each logic block is a small memory which is addressed using a number of input lines, and outputs a result.