Technical Report

Number 7

**Computer Laboratory**

# Local area computer communication networks

Andrew Hopper

April 1978

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

http://www.cl.cam.ac.uk/

# © 1978 Andrew Hopper

This technical report is based on a dissertation submitted April 1978 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Trinity Hall.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

#### PREFACE

I am indebted to my supervisor, Professor D.J. Wheeler, for initially introducing me to the subject of computer networks and for many interesting and wide-ranging discussions during my three years under his supervision.

I am also grateful to Professor M.V. Wilkes for advice and help given in numerous ways and for enabling me to visit the United States during the last year of my research which proved to be a very valuable and stimulating experience.

Dr J.W. Pitman of the Department of Pure Mathematics and Mathematical Statistics devoted much of his time to educating me in the complexities of queuing theory and Markov chains, for which I am grateful.

My thanks also go to Sheena Baptie for expertly typing the drafts and final copy of this thesis.

This research was funded by the Science Research Council.

\* \* \* \* \* \*

No part of this dissertation has been submitted for any other degree or diploma at any other institution.

The work described in this dissertation is to the best of my knowledge original, and was done by myself without collaboration. The early chapters contain a discussion of the background to the research in terms of the work done by others; but the criticism of this work is my own.

# CONTENTS

Ø

| 1. | Motiva  | tion and             | Aims                                                            |    |

|----|---------|----------------------|-----------------------------------------------------------------|----|

|    | 1.1     | Introduc             | tion                                                            | 1  |

|    | 1.2     | Technolo             | ду                                                              | 1  |

|    | 1.3     | Basic el             | ements                                                          | 3  |

|    |         | 1.3.1                | The spectrum of networking technology                           | 3  |

|    |         | 1.3.2                | Characteristics of local networks                               | 6  |

|    |         | 1.3.3                | Users requirements                                              | 9  |

|    | 1.4     | Problems             | encountered                                                     | 9  |

|    |         | 1.4.1                | Local network development                                       | 9  |

|    |         | 1.4.2                | Measures of performance                                         | 10 |

|    |         | 1.4.3                | Choice of network architecture                                  | 12 |

|    |         | 1.4.4                | Simulation and analysis                                         | 14 |

|    | 1.5     | Points of<br>dissert | f investigation and outline of<br>tation                        | 14 |

| 2. | Local 1 | Network Su           | urvey                                                           | 16 |

|    | 2.1     | Introduct            | tion                                                            | 16 |

|    | 2.2     | Ring netw            | vorks                                                           | 16 |

|    |         | 2.2.1                | Early systems                                                   | 16 |

|    |         | 2.2.2                | University of California Irvine,<br>Distributed Computer System | 18 |

|    |         | 2.2.3                | University of Cambridge, Ring Project                           | 20 |

|    |         |                      | 2.2.3.1 Ring organisation                                       | 21 |

|    |         |                      | 2.2.3.2 Error recovery                                          | 24 |

|    |         |                      | 2.2.3.3 Hardware                                                | 25 |

|    |         |                      | 2.2.3.4 Discussion                                              | 27 |

|    |         | 2.2.4                | Ring system conclusions                                         | 28 |

|    |        |            | · ·                                                            | Page    |

|----|--------|------------|----------------------------------------------------------------|---------|

|    | 2.3    | Broadcas   | st networks                                                    | 29      |

|    |        | 2.3.1      | Aloha systems                                                  | 29      |

|    |        | 2.3.2      | Carrier sense multiple access systems<br>(CSMA)                | 30      |

|    |        |            | 2.3.2.1 Xerox Corporation, Ethernet                            | .31     |

|    | 2.4    | Other lo   | ocal network proposals and developments                        | 34      |

| 3. | A peri | formance o | comparison of ring communication networks                      | 36      |

|    | 3.1    | Introduc   | ction                                                          | 36      |

|    | 3.2    | Previous   | s work                                                         | 36      |

|    |        | 3.2.1      | Previous work on ring systems                                  | 37      |

|    |        | 3.2.2      | Input buffer structures                                        | 40      |

|    | 3.3    | The infi   | nite size input buffer model                                   | 41      |

|    |        | 3.3.1      | The register insertion system basic performance function (BPF) | 41      |

|    |        | 3.3.2      | The empty slot system BPF                                      | 44      |

|    |        | 3.3.3      | The permission token system BPF                                | 45      |

|    |        | 3.3.4      | The pre-allocated bandwidth system BPF                         | 46      |

|    |        | 3.3.5      | Line utilisation equations                                     | 47      |

|    |        | 3.3.6      | Delay equations                                                | 49      |

|    | 3.4    | The sing   | le packet input buffer model                                   | ,<br>51 |

|    |        | 3.4.1      | The register insertion system delay equation                   | 53      |

|    |        | 3.4.2      | The slot system delay equation                                 | 54      |

|    |        | 3.4.3      | The permission token system delay equation                     | 56      |

|    |        | 3.4.4      | The pre-allocated bandwidth system delay equations             | 56      |

|    |        | 3.4.5      | Line utilisation equations and packets turned away             | 56      |

|    | 3.5    | Evaluati   | on of systems                                                  | 57      |

|    |        | 3.5.1      | Traffic estimates                                              | 57      |

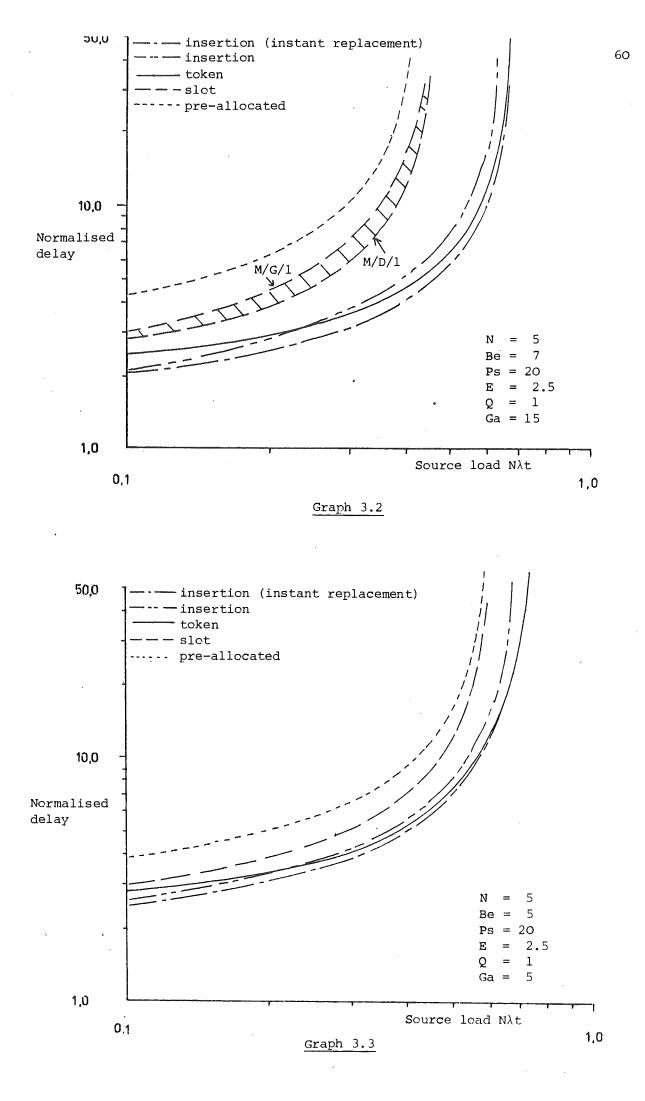

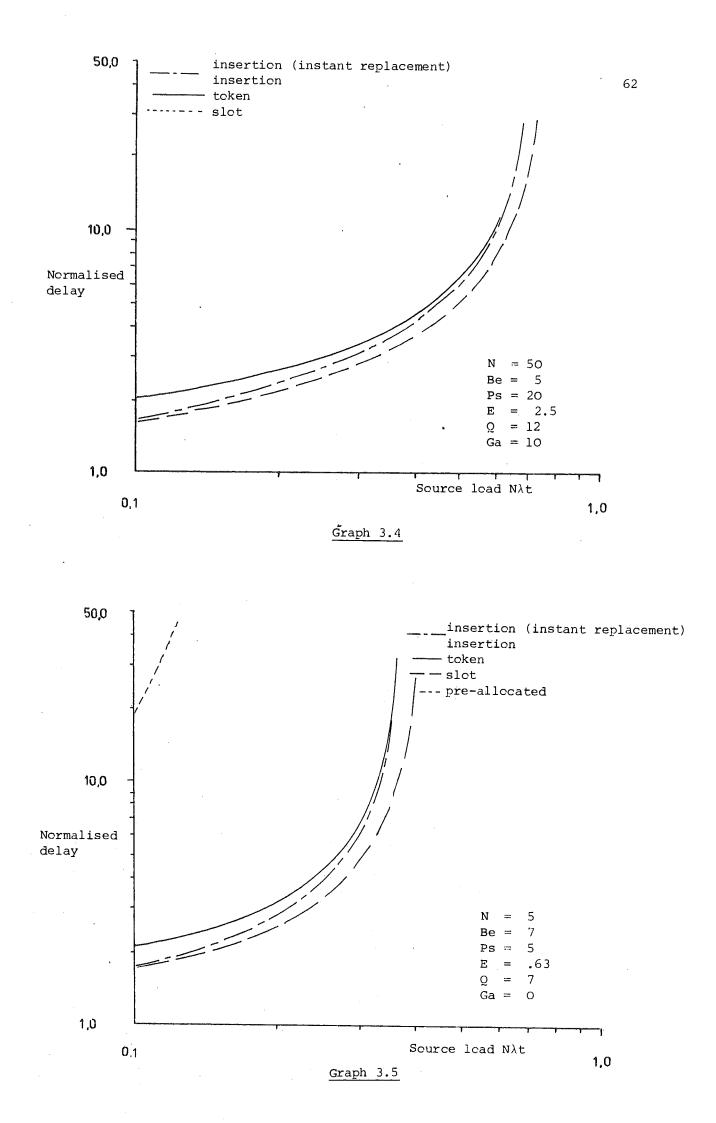

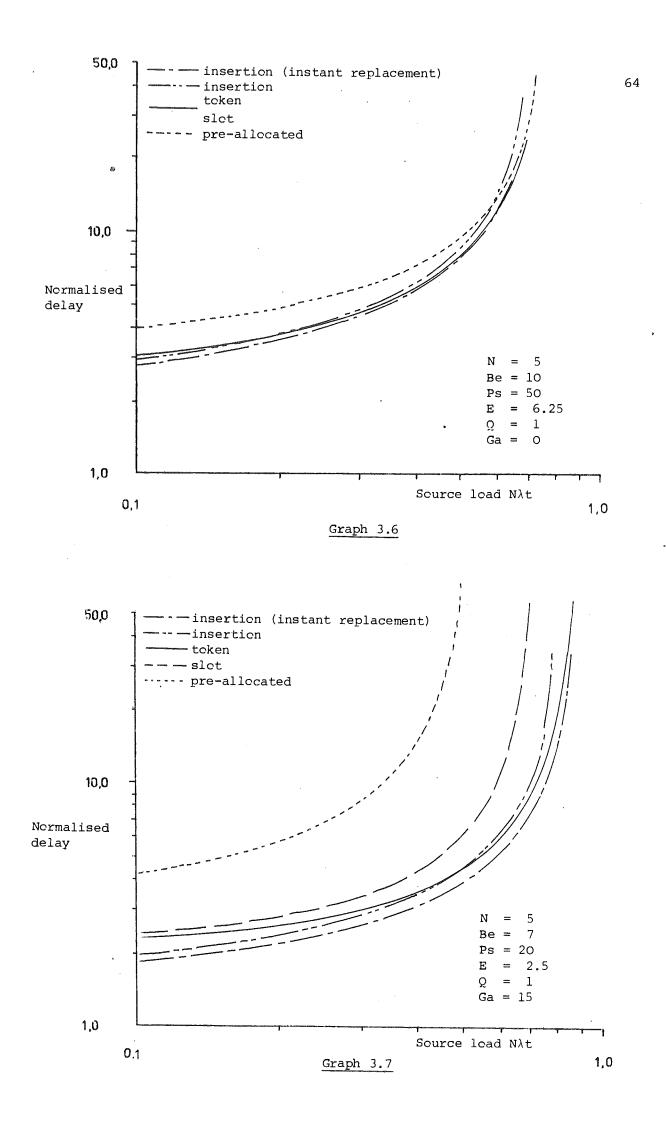

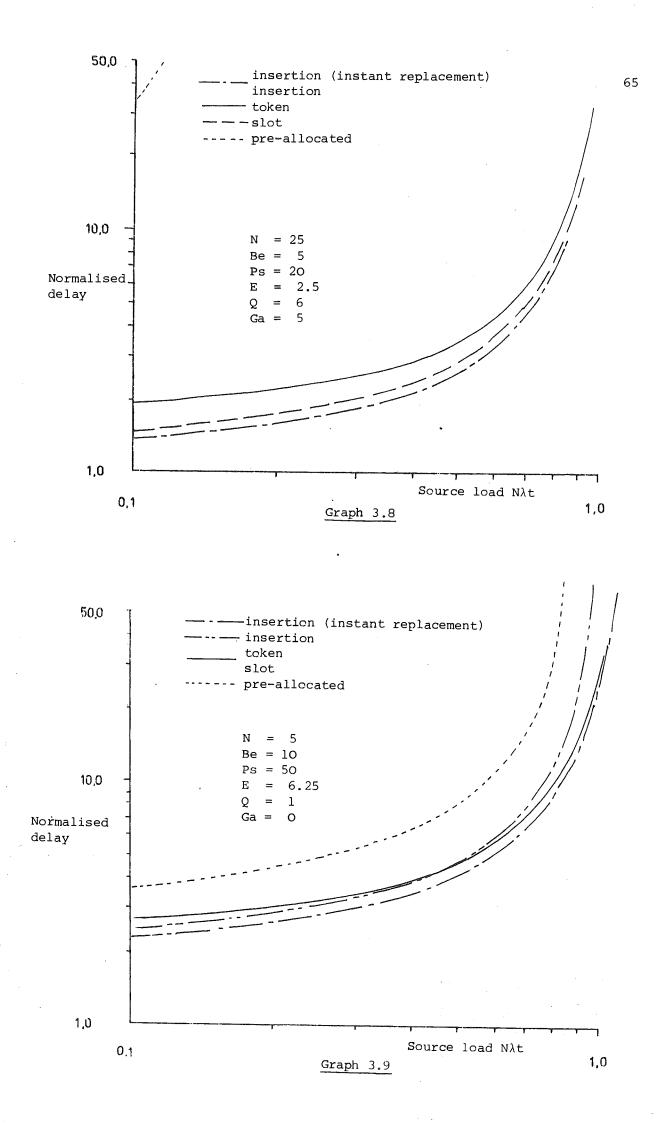

|    |        | 3.5.2      | A comparison of delay characteristics                          | 58      |

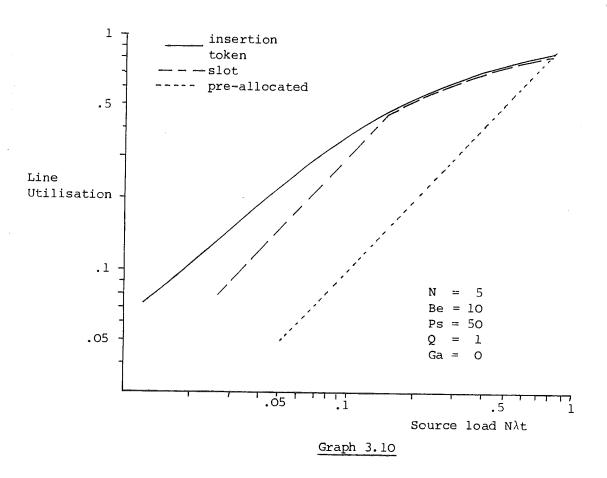

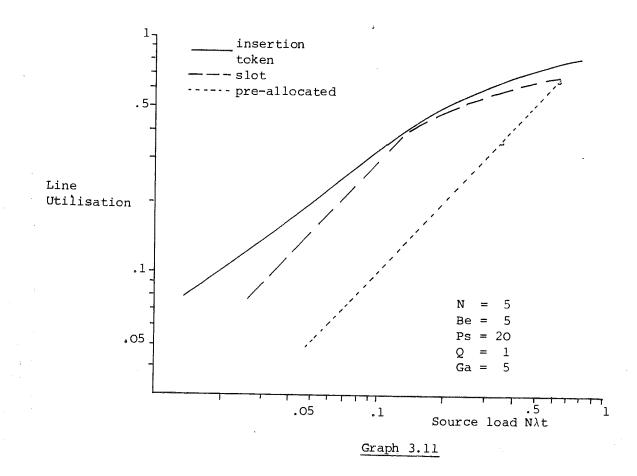

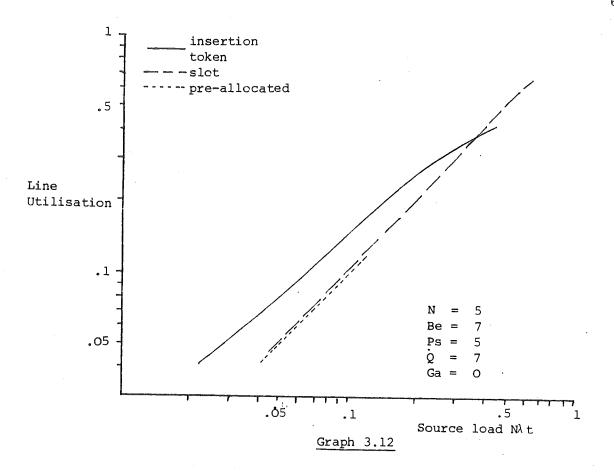

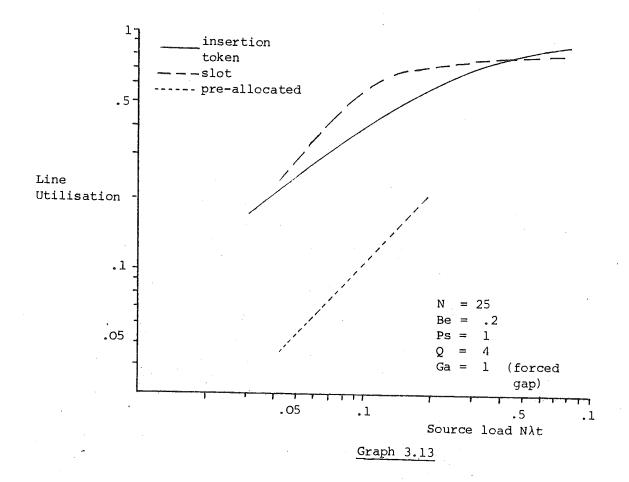

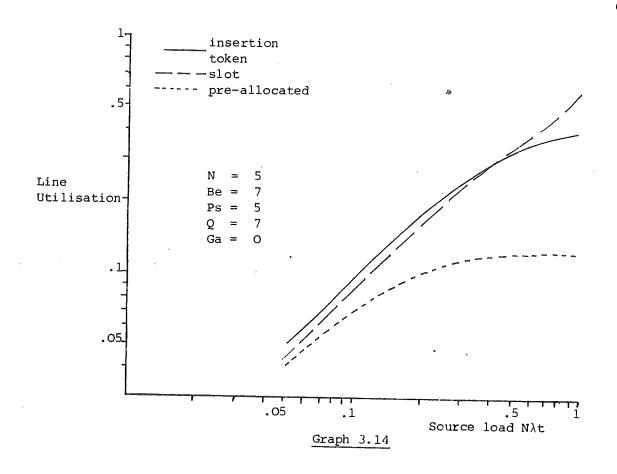

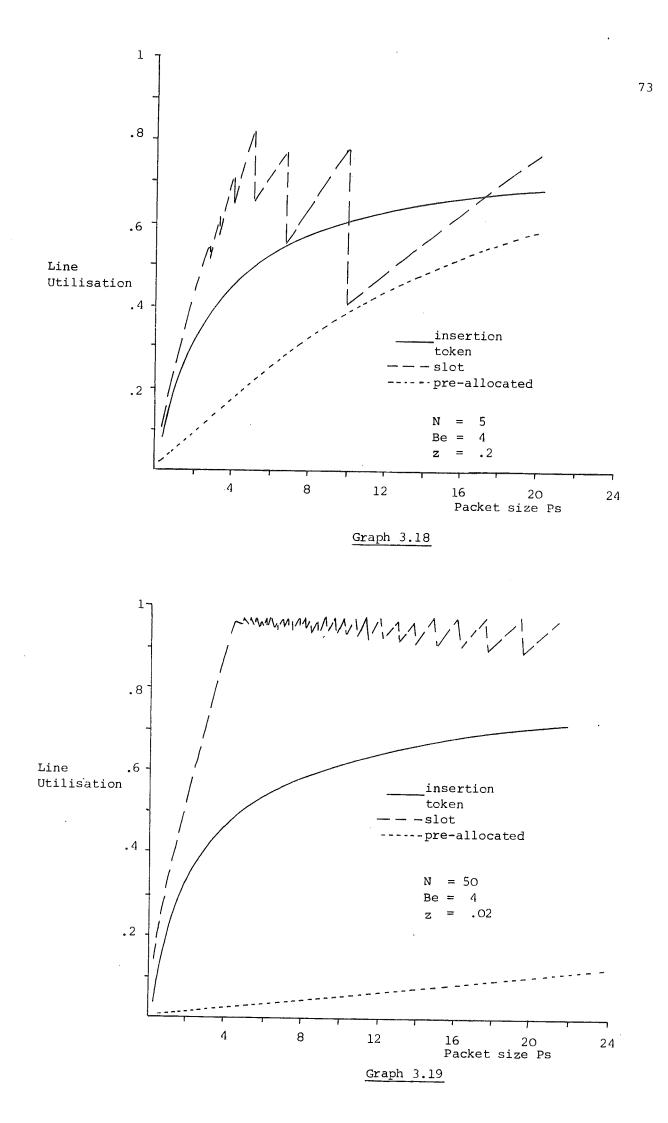

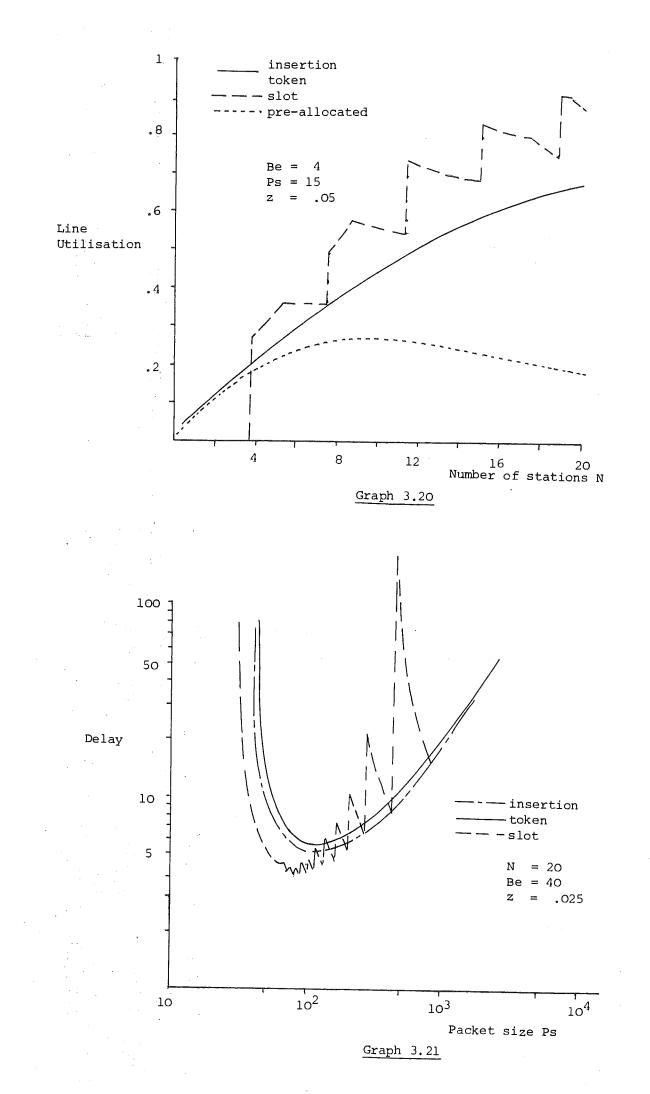

| ,  |        | 3.5.3      | A comparison of line utilisation characteristics               | 63      |

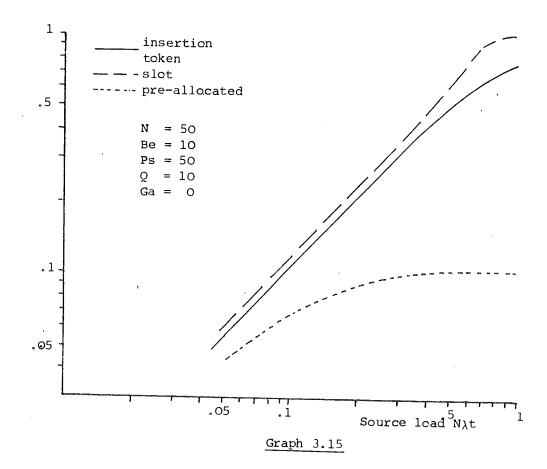

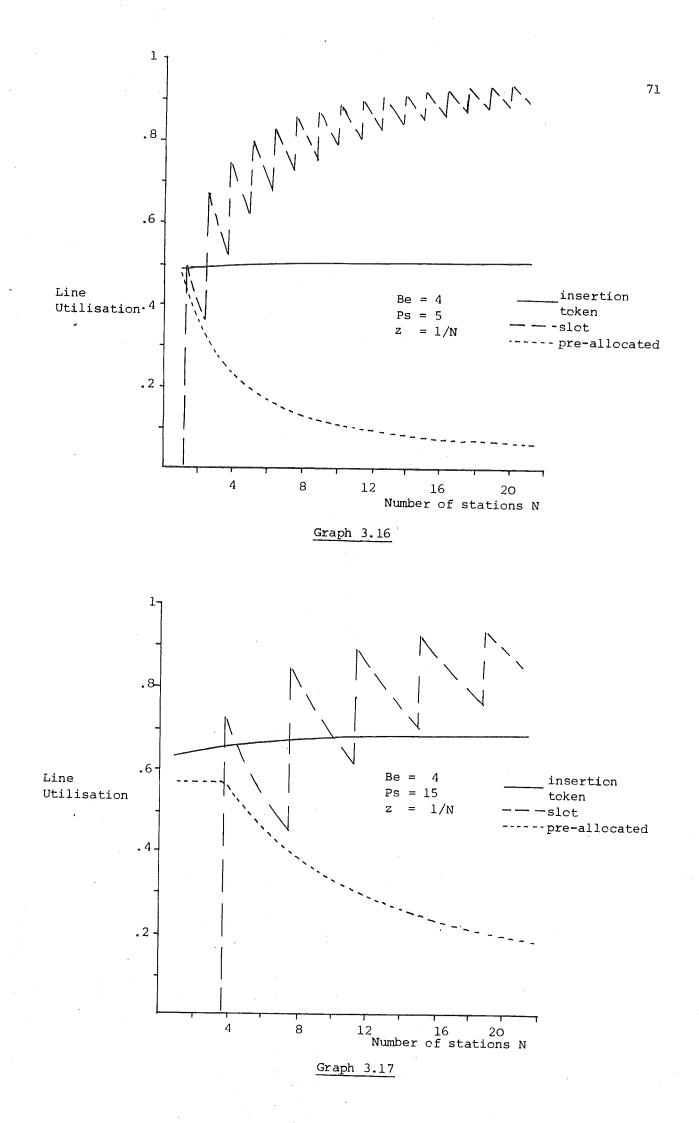

|    |        | 3.5.4      | The effect of the number of stations<br>and packet size        | 70      |

|    |       |                  |                                                                                                             | Page |

|----|-------|------------------|-------------------------------------------------------------------------------------------------------------|------|

|    | 3.6   | The do           | minant user                                                                                                 | 72   |

|    | 3.7   | Fixed            | address field overhead and errors                                                                           | 76   |

|    |       | 3.7.1            | The effect of fixed size control fields                                                                     | 76   |

|    |       | 3.7.2            | The effect of packet size on performance                                                                    | 77   |

|    |       | 3.7.3            | Data stored in rings and errors                                                                             | 78   |

|    | 3.8   | Towards          | s real systems                                                                                              | 79   |

| 4. | Stabi | lity and         | Performance in Broadcast Networks                                                                           | 82   |

|    | 4.1   | Introdu          | action                                                                                                      | 82   |

|    | 4.2   | Previou          | as work                                                                                                     | 82   |

|    | 4.3   | Algorit<br>perfo | chms for stabilising and improving the ormance of the slotted Aloha channel                                 | 86   |

|    | 4.4   | Modelli          | ng the stabilised Aloha channel                                                                             | 91   |

|    |       | 4.4.1            | The analytical model                                                                                        | 91   |

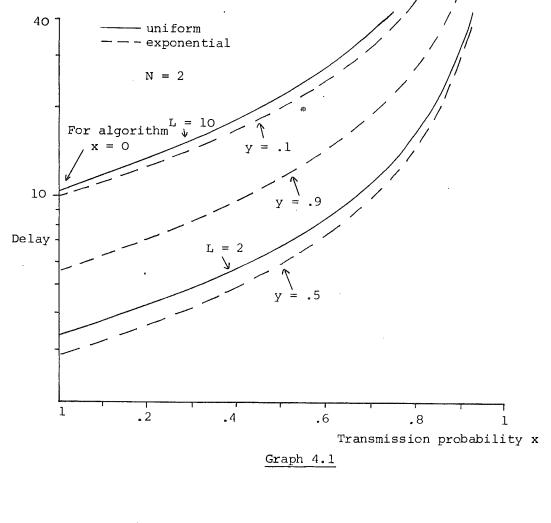

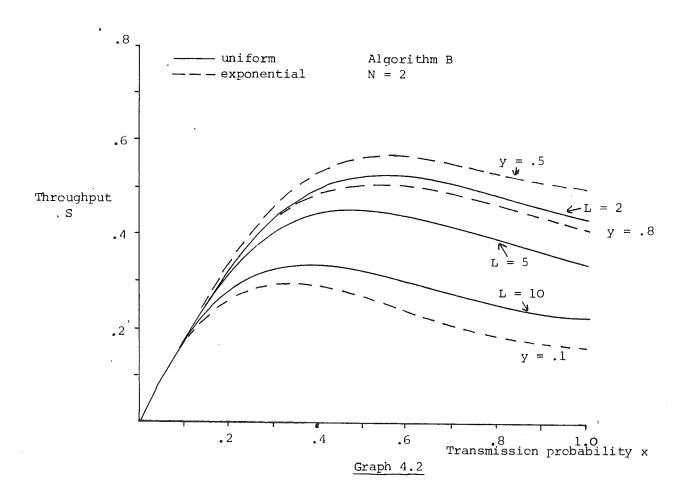

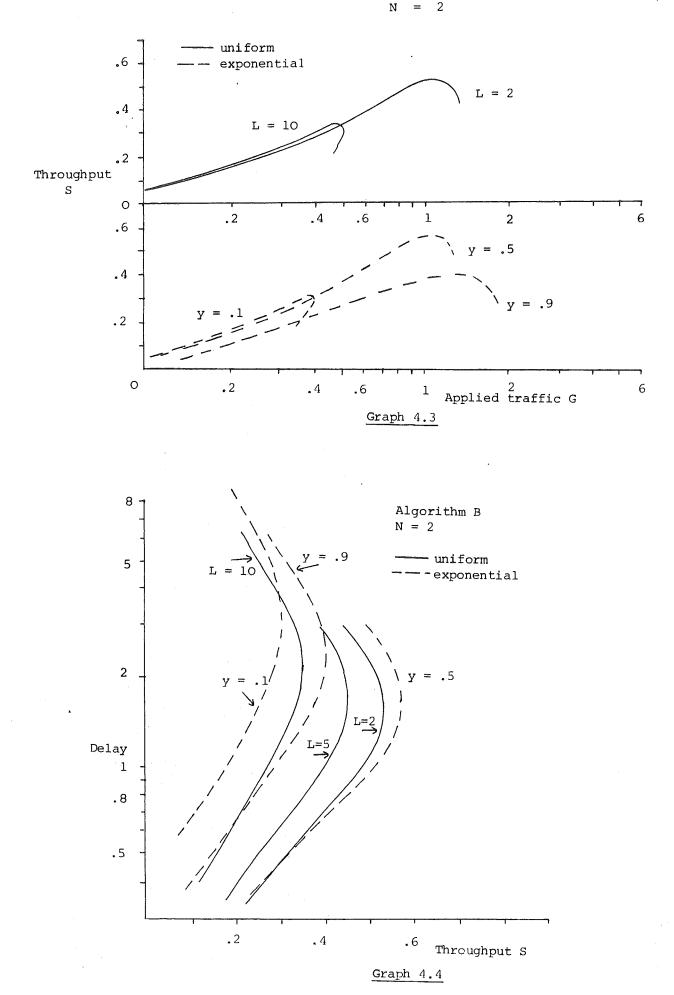

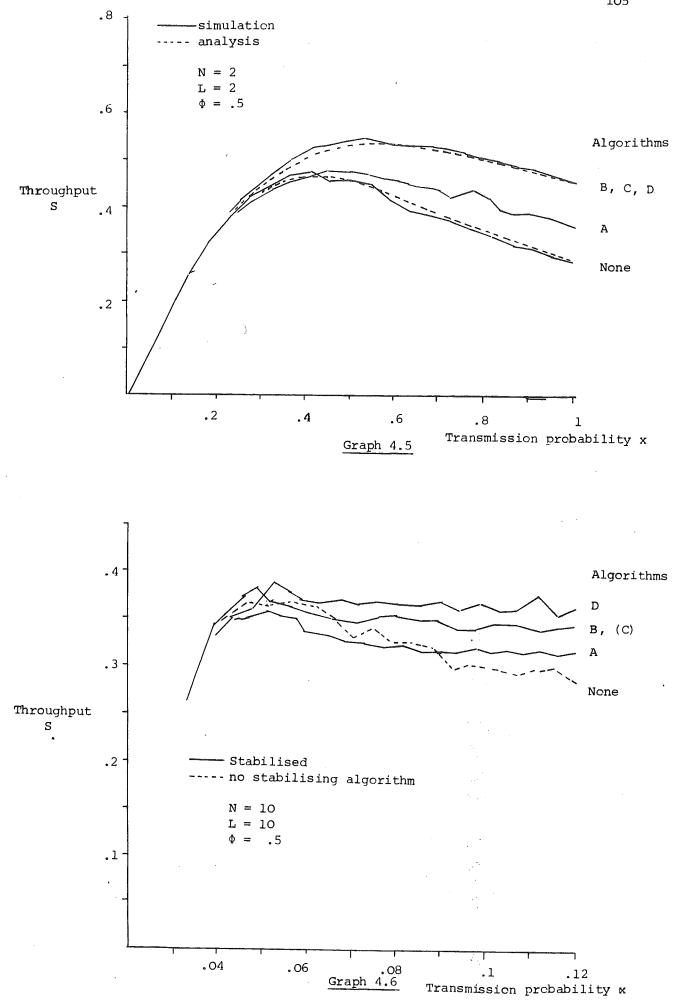

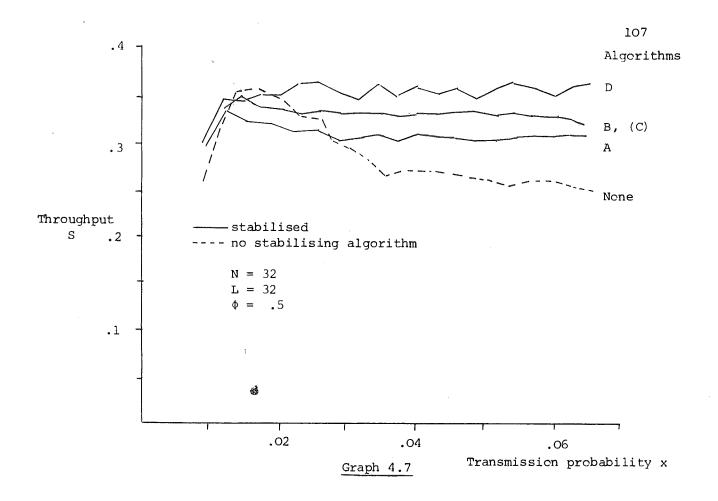

|    |       | 4.4.2            | Graphs of analytical model                                                                                  | 102  |

|    |       | 4.4.3            | Simulations of the stabilised Aloha channel                                                                 | 102  |

|    | 4.5   | Perform<br>slott | ance improvement in the uncontrolled<br>ed Aloha channel                                                    | 106  |

|    |       | 4.5.1            | Analytical approach                                                                                         | 106  |

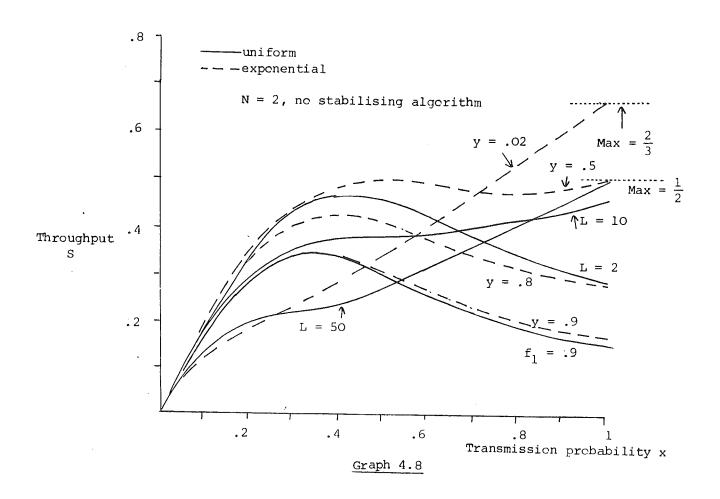

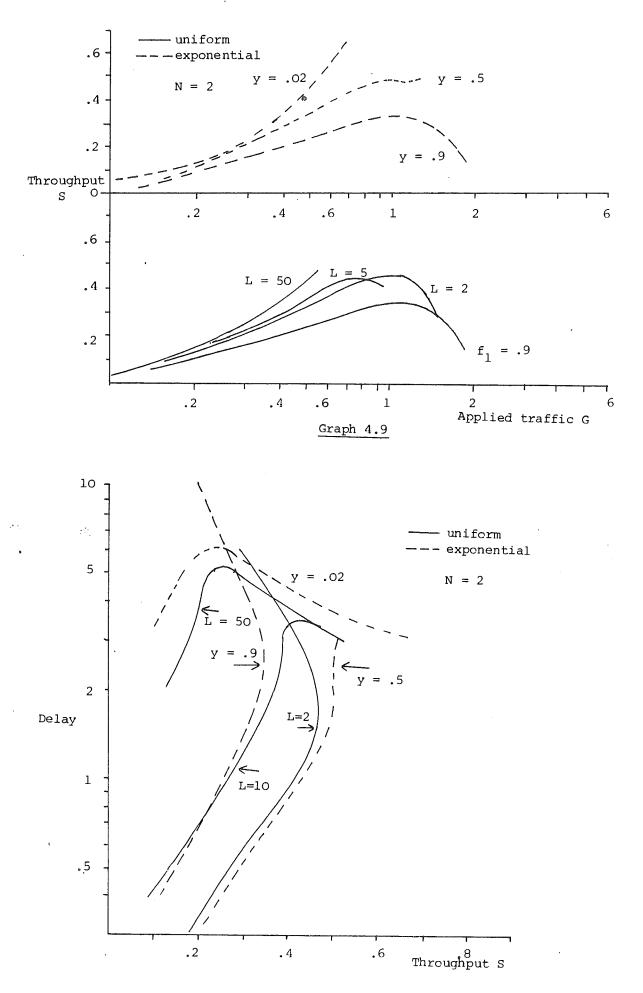

|    |       | 4.5.2            | Graphs of analytical model                                                                                  | 111  |

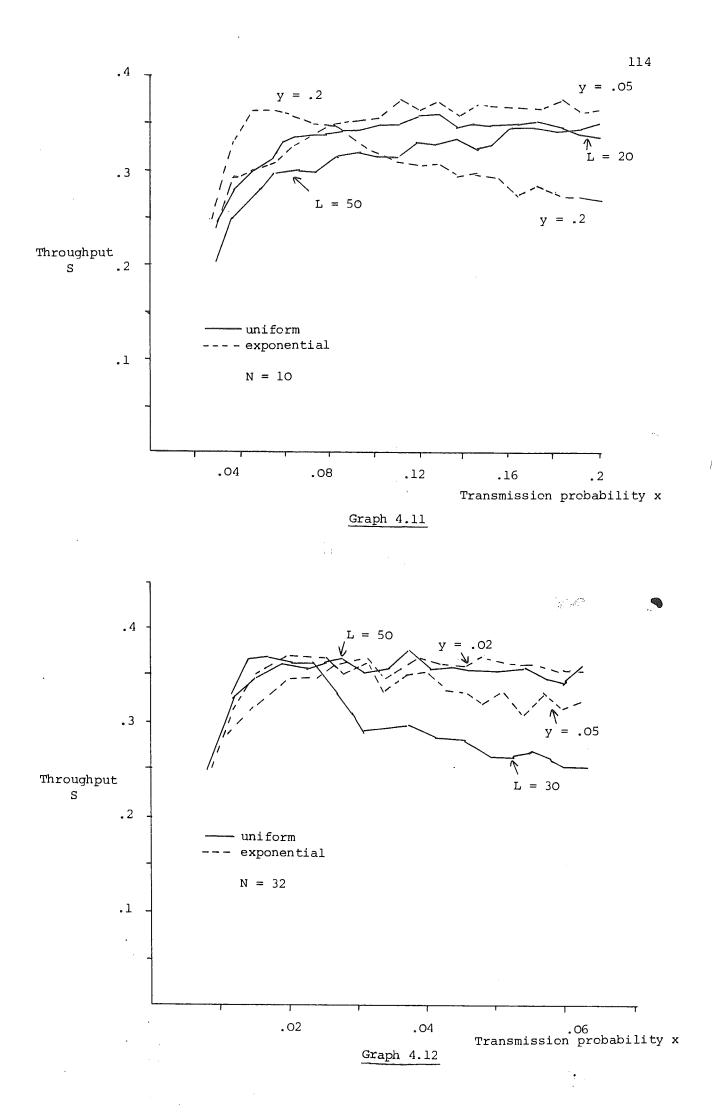

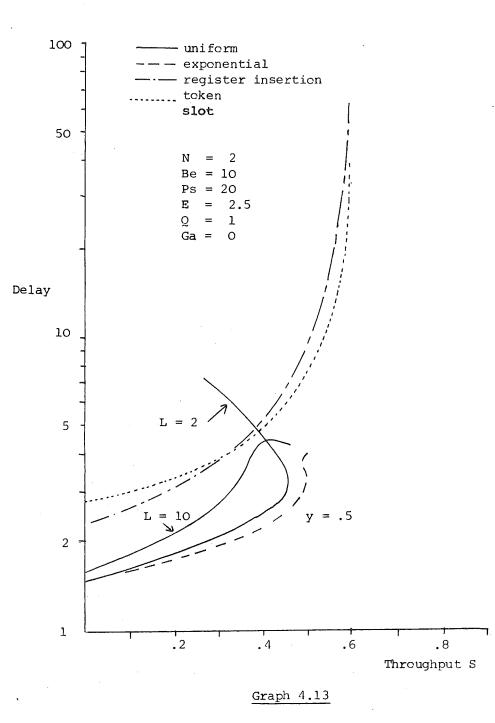

|    |       | 4.5.3            | Simulations of the exponential and<br>uniform retransmission distributions<br>for the slotted Aloha channel | 113  |

|    | 4.6   | Carrier          | sense multiple access networks (CSMA)                                                                       | 115  |

|    |       | 4.6.1            | The ring contention network                                                                                 | 115  |

|    |       | 4.6.2            | Analytical modelling of the CSMA network                                                                    | 117  |

|    | 4.7   | A compa:         | rison of broadcast and ring networks                                                                        | 121  |

| 5. | The o | design of a local network LSI chip                   | 125 |

|----|-------|------------------------------------------------------|-----|

|    | 5.1   | Introduction                                         | 125 |

|    | 5.2   | The environment of a local network chip              | 126 |

|    | 5.3   | Hardware and interface design                        | 128 |

|    | 5.4   | Modulation and clocking                              | 134 |

|    | 5.5   | Networks implemented in the station logic chip (SLC) | 136 |

|    | 5.6   | Removal of lost packets                              | 146 |

|    | 5.7   | SLC architecture                                     | 148 |

|    | 5.8   | Issues of complexity                                 | 154 |

|    | 5.9   | Applications                                         | 158 |

| 6. | Proto | ocol Issues                                          | 160 |

|    | 6.1   | Introduction                                         | 160 |

|    | 6.2   | Local network protocols                              | 160 |

|    | 6.3   | A redesign of the Cambridge Ring                     | 162 |

|    | 6.4   | Protocols for the Cambridge Ring                     | 168 |

| 7. | Summa | ary and Concluding Remarks                           | 174 |

|    | 7.1   | Summary                                              | 174 |

|    | 7.2   | Conclusions                                          | 175 |

|    | 7.3   | New local network architectures                      | 177 |

|    | Appen | dix (summary of notation)                            | 182 |

|    | Refer | ences                                                | 185 |

Page

#### CHAPTER 1

#### MOTIVATION AND AIMS

#### 1.1 Introduction

In this thesis a number of local network architectures are studied, and the feasibility of a LSI design for a universal local network chip is considered. Local means within one or several buildings, or on one site. In this chapter the basic problems encountered in local network design are defined, and an overview of the thesis is given.

# 1.2 <u>Technology</u>

The development of computer systems has been greatly influenced by underlying shifts and developments in hardware technology. These two processes have not been independent: hardware is developed as there is a need for performance improvement in new systems, and new systems are designed to take advantage of hardware developments. In recent years these shifts have been tending towards design in LSI (Large Scale Integration) with up to 16K RAM (Random Access Memory) chips and microprocessors consisting of more than 2K gates.

A description of current hardware technology is outside the scope of this thesis, but a number of techniques can be mentioned as showing promise for the future. Of the MOS techniques (PMOS, NMOS, CMOS, SOS, DMOS) and bipolar techniques (DTL, TTL, ECL, MECL,  $I^2L$ ), it seems that NMOS, TTL, and  $I^2L$  will compete in the future [FERRE77]. NMOS has moderate speed characteristics and a higher density (80 - 120 gates/mm<sup>2</sup>) than  $I^2L$  and therefore a lower cost-per-gate. TTL, especially of the

low power Schottky variety, offers high speeds (5nsec/gate delay), is well known, and with improvements should stay competitive in the future.  $I^{2}L$  provides a compromise between bipolar speeds and MOS densities ( $I^{2}L$  density 100 - 200 gates/mm<sup>2</sup>, speed 5 nsec/gate) and will probably be used in most areas with the exception of the very low-cost (PMOS) and very high-speed (ECL) applications. ECL is likely to flourish where very high performance is required (.5nsec/gate delay), for example in CPU design, and is likely to be developed in the form of uncommitted logic arrays (ULAs) so the preliminary manufacturing steps can be carried out before the final design is known.

The design of an LSI device has high initial costs. However, if these are amortised over a large production run, then the price of each unit becomes low. Thus, custom made LSI units have been developed for use in areas where the same device can be used at many points in the system. An area which only recently has been subject of study from this point of view is that of computer networking. Although developments in silicon technology over the past fifteen years have seen a threefold decrease in cost per gate, these developments have mostly benefitted CPU and memory hardware, while input/outpt and communications hardware have lagged behind. The time thus seems ripe for a move in this direction, especially now that communications technology has at last been moving forward with the advent of optical devices. These are used both as optical isolators, where the price has dropped to several dollars for units which operate a 2-3MHz, and as optical cables to replace conventional twisted pair or coaxial systems. The cost/performance improvement in communications technology by 1985 is forecast as twofold in performance and threefold in cost, giving a total improvement factor of six [HOB77].

# 1.3 Basic Elements

1.3.1 The spectrum of networking technology

Systems connecting a number of computers can be classified according to their memory/processor interconnection structure as shown in Fig. 1.1.

## Network Type

# Interconnection Structure

Global Computer Networks

Local Networks/Computer Modules

Multi-Processor Computers

Crossbar switch in the most general case.

Computers loosely coupled by links

Some memory at processing units linked by high speed transmission

# Fig. 1.1 Computer Network Spectrum

lines

Global computer networks grew as the need arose for communication between computers and remote terminals. In such loosely coupled systems the communicating devices can function as independent units and are connected by a network which can span a large area. As these systems developed, more and more computer-to-computer traffic resulted and sophisticated protocols were developed to enable connections to be set up quickly and automatically. These large systems improved the reliability and availability from the users point of view, but generally made inefficient use of the available computing power and were very costly. Examples are the Aloha net at the University of Hawaii [AB70], which was originally developed to link a number of terminals to a central computer, and the ARPA network, which is a sophisticated and geographically distributed network linking machines of many different types [KL75b].

At the other end of the spectrum lie the multiprocessor computer systems where individual units are in close proximity to each other and share common memory. Such multiprocessor systems were initially developed to enable relatively inexpensive processors to share expensive peripherals such as discs. The software did not require alteration, except that the problem of simultaneity of access to the shared resource had to be solved. A concept which extended this was spooling (simultaneous peripheral operation on line). Such systems developed into the very tight multiprocessor configurations where each processor can access a common memory or set of memory modules through a crossbar switch. This can be considered as a network, although crossbar switches quickly become very complex when interconnecting large numbers of modules and thus are only useful for small numbers of processors and memory units. On the other hand these tightly-coupled systems do satisfy some of the objectives of multiprocessing which are availability, adaptability, modularity, performance, and programmability. There has been a trend in recent years to improve reliability by decentralisation. Multiprocessor systems then fare well as they do not depend upon any particular memory module or processor and can be reconfigured at failure.

Between the two areas of remote computer networking and multiprocessing lies the ill-defined area of local networking. It seems that a growing percentage of computer applications will gravitate to this kind of system because of its inherent advantages such as low cost, reliability, availability, adaptability to specific applications, and flexibility for growth. A number of local networks have been developed,

noteably the Ethernet [METC76] and DCS systems [FARB72] which will be described in more detail in the next chapter. Local networks tend to vary between systems which are designed to provide a communications capability for I/O sharing in a University or organisation, and others which attempt to provide more reliable and sophisticated computer systems for the user by dispersing the computer tasks over a number of distributed machines.

A scheme which attempts to totally decentralise the computing functions into a multiplicity of computing units and is best suited to applications where the load is highly variable is the Computer Module system built at Carnegie-Mellon University [FU73]. In such systems data has to be freely available to all modules, and thus all input/ output is shared between processors. Such homogeneous processors and input/output controllers allow easy expansion and economic redundancy but require an efficient communications subsystem. These systems will be treated as part of the local network spectrum since the interaction between modules is not as critical as in a multiprocessor and could thus be implemented in a fast local network.

The differences between remote networks, local networks, and multiprocessors are summarised in Fig. 1.2.

|                   | Global Network                             | Local Network                                                                       | Multiprocessor                                       |

|-------------------|--------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------|

| Separation        | >10 Kilometers                             | 10K-50 metres                                                                       | <50 metres                                           |

| Data rate         | 10-50 KHz                                  | l - lo MHz                                                                          | >10 MHz                                              |

| Response time     | l sec                                      | <.lm.sec                                                                            | .5 µsec                                              |

| Port Architecture | asynchronous<br>communication              | shared address<br>and interrupt                                                     | shared<br>primary memory                             |

| Applications      | terminal share<br>load share<br>file share | Distributed computing,<br>high perf. fixed applic-<br>cation,special by<br>function | general purpose                                      |

| Ability to grow   | possible,<br>but<br>expensive              | inexpensive,but<br>algorithms do not<br>exist                                       | size and perfor-<br>mance vary with<br>cost and time |

#### Fig. 1.2 Characteristics of Computer Networks

# 1.3.2 Characteristics of Local Networks

Local networking having been placed in the spectrum of network technology, the particular characteristics of local networks will be enumerated and compared with global networks to determine which factors make the two different. As local networking represents an intermediate area, it is difficult to define a precise set of criteria. The list that follows is the set of likely, rather than definitive, features a local network possesses.

- (1) It is likely to have high bandwidth where the speed of the hardware does not represent a bottleneck. Various networks operating at speeds of up to 10 MHz have been proposed and built.

- (2) It is likely to have a very simple connection topology so that routing problems are either non-existent or very simple.

- (3) Messages in the local network have short life times, primarily as a result of the high data rates and low buffering requirements of such systems.

- (4) Local networks tend to be optimised to the application. This is true even when the network is completely homogeneous and is constructed using one type of computer which is chosen for the application.

- (5) Because the local network is cheap to interface to the outside world, the addition of extra nodes does not represent a great expense.

- (6) There is little or no buffering in the communications subnet as local network nodes are simple and do not perform sophisticated control algorithms.

- (7) The local network may be designed in such a way that there is a central controlling device. In a local network a central control node can communicate with other nodes quickly and efficiently and thus is economically feasible.

- (8) Local networks tend to be inexpensive as often they are connecting simple devices, and thus high costs are not economically justifiable.

- (9) Local networks are built around a very simple or non existent backbone network and communication can be directly at the hostto-host level.

The design goals of any network are to enable computers to share resources and to allow process to process communication. This is true whether the network is local or global. Furthermore, the network should have well defined operating characteristics, degradation properties, and should be incremental in nature. That is, it should be designed

in a modular fashion so that it can be expanded cheaply and easily. For local networks this can be achieved by designing simple, clean systems, where the communication and application functions are well partitioned and which behave deterministically under most conditions. The user requires a number of services from the network, which makes it necessary for a set of protocols to be defined. Such protocols exist whether or not the network is local; and although some optimisations can be made in the local case they are generally invariant for the two network types from the users-functionality point of view. Thus, to satisfy the user, the local systems will require most of the features of the global system (e.g. a layered protocol structure, virtual circuit connection, etc.). From the network designers point of view these protocols can be provided much more simply if the network is local. That is, routing and retransmission algorithms are simpler, as are some protocol time outs. For example, advantage can be taken of the specialised link types available and of communication at the host-to-host level. This means that a 16 bit parallel channel network can be devised with very high data rates and with no problems such as packets out of order or inadequate buffering at the network level.

One final requirement of both global and local networks is that they are capable of easily providing information about the traffic in the system. This can be achieved either by using a promiscuous node which looks at all passing traffic (as in Ethernet) or by special hardware units that trap erroneous packets. It is interesting to note that in the packet radio system as SRI as much money was spent on the monitor hardware as on the rest of the system.

Thus, most of the differences between local and global networks are due to physical size and are only governed by the environment of the network.

# 1.3.3 Users Requirements

From the users point of view the basic requirements of a network are that it should function in such a way that errors do not occur on transmission, that data arrives in the order it was transmitted, and that the user has some control over the movement of data within it. He also requires some guarantee of the security of data and an indication of the performance of the network under various loads. Thus the behaviour of the network should be specified under the following conditions.

- (1) Performance of the network when it is working correctly and within its design limits. The user requires to know the delay in obtaining a service, consisting of the time to set up that service followed by the time to transmit the data. This includes delays due to buffering acknowledgement, etc.

- (2) Performance of the network when it is not working correctly. The user requires to know what the response will be during degradation: which resources are given priority, and which are lost. He needs to know the response time during restoration and the mean time between failures when the network is working normally.

- (3) Long term performance of the network. This includes both long-term data rate as opposed to that achievable in burst mode and the long-term failure characteristics.

- 1.4 Problems Encountered

#### 1.4.1 Local network development

Numerous *ad hoc* techniques have been developed for interconnecting machines in a local network; however, for larger systems envisaged for

for the future a more rational approach to network design will have to be adopted. Some of the actions which must be taken before local networks become better understood and more widely used are listed below:

- Investigation of transmission problems in such networks.

This includes hardware design, network design, protocol design, and error control.

- (2) Development of cost effective LSI partitioning of such networks. This requires standards to be set to enable a chip or family of chips to be manufactured to perform some of the local network functions.

- (3) Development of suitable control mechanisms. It is not clear to what extent control in a local network should be distributed or what kind of control algorithms should be used for optimum network performance.

- (4) Determination of additional functions of local netoworks.

- (5) Modularisation of such networks to enable the building of larger, perhaps global, systems.

#### 1.4.2 Measures of Performance

The performance of a local network can be measured in terms of many factors. These include response time, throughput, delay, line utilisation, error rate, reliability, buffer requirements, processing requirements, behaviour at saturation, and error recovery time. Each network designer balances these parameters according to the application and it is difficult to compare different systems. However, the important parameters include cost, line utilisation, and reliability. These

are discussed below.

The cost of communication is a function of the distance between the communicating devices and the computing power required to enable the communication to take place. Local networks are less sensitive to the former of these costs than the latter. The network can be designed so that the host computer performs most of the computational functions of the network itself. This reduces cost but may require the host to perform sophisticated transmission algorithms. Alternatively, the local network can be designed along conventional lines with separate hardware at each node for network control functions. Such a network can be made completely transparent and autonomous to the user (the host being only aware of a data stream connection to another host) but is more expensive. Systems can be devised where the network not only performs transmission functions, but also some operating system functions. This enables a distributed computing system to be implemented more efficiently. These networks tend to be more sophisticated and expensive. The cost of a local network is thus influenced by the computational task it has to perform and more specifically by the point where the line between host computer functions and network functions is drawn.

Line utilisation is the proportion of time the transmission `line is carrying useful data. This should be maximised, although on past experience, high line utilisations have not been easy to achieve. For global networks this figure has been rising from a level of about 10% for ARPANET to 60-70% for TELNET, but for local networks line utilisations are still low [KL76].

Local computer networks can improve reliability and availability from the users' point of view. Reliability is the probability of

completing a task that has already been started, and availability is the proportion of time that the system is available to the user and is related to response time. Reducing the mean time to repair to zero does not make the availability 100%. This is because it takes a finite time to set up a connection; and if the system breaks down, these connections are reinitialised and availability decreases. The reliability of a system decreases with the number of components in the system. This means that distributed computer systems seen as a whole are less reliable than centralised systems. However, from a users point of view, this is not true as most of the time he uses local resources and only occasionally requests a service from another node. As such services are replicated and are not dependent on any particular configuration, he is more likely to have his request granted. Thus, for the user the distributed system is more reliable.

#### 1.4.3 Choice of Network Architecture

There are many choices available in the design of a network in terms of overall design and technology. Architectures are compared in terms of modulation (coding) schemes, the complexity of network interfaces, as well as measured performance parameters. The local network architectures include random access, broadcast, ring, loop, polling, direct-connection, circuit-switching, and shared-memory systems. Recently, the broadcast and ring schemes have been prominent, and these will be examined in more detail later. An interesting new technique is that of using optical systems. As fibre optic couplers have been developed and have become available at reasonable cost, such systems are now increasingly feasible. However, fibre optic systems are not always

suitable: for example, a broadcast system built around high-speed optical devices (200-300MHz) would have poor operating characteristics and require very long packets.

Different problems arise when the network is homogeneous and consists of identical units (e.g. Ethernet) and when it is constructed using dissimilar machines (e.g. DECNET, SNA). For non-homogeneous networks microprocessors can be used to perform some of the network-tohost interaction functions. However, as local networks tend to operate at high speeds, microprocessors can be a bottleneck and are not always suitable. When networks are homogeneous, addressing can be simplified by specifying network-wide address formats. Sets of such networks can be interconnected using devices which do not perform any protocol translation but only buffer the varying speeds of such networks. These devices can thus be simple and cheap.

Other network architecture issues which arise are what kind of error check facilities are provided and whether any special features such as a broadcast mode should be used. As local networks (with the exception of contention) can be made almost completely error free, the error check can be omitted in some cases. It is unwise to use a communication network without any error checking, but providing errors are rare, retransmission at a higher level is not inefficient. Some networks provide sophisticated error check facilities (Ethernet); and in some cases, the CRC check is used as a basic component in the packet structure (DCS). An important issue which has not been addressed by network designers is that of exploiting the broadcast facility of the bus and ring networks. Such a feature has been used to communicate between the source and one or two other nodes, but it is rarely used tc communicate with all nodes in the system simultaneously. One of the

reasons for this is that the broadcast message can become corrupted, and additional protocols have to be defined to cater for this possibility.

The design of the local network has to be seen in the light of possible LSI implementation. In order to do this, the functions of a chip have to be defined, as well as the interfaces between the network and the host. Such a chip can be complex and require simple interfaces, or it can be simple and cheap with sophisticated interfaces to the communicating devices. Finally, the local network has to be capable of allowing logistic problems of network administration and protection of data by encryption to be resolved.

#### 1.4.4. Simulation and Analysis

The performance of a local network can be measured by employing suitable simulation and modelling techniques. The analytical techniques include queuing theory analysis and Markov theory analysis. Such analytic models are generally some way removed from the real system due to simplifying assumptions and give only general results. On the other hand simulations tend to be more specific and thus give more application dependent results. Local networks will be studied using theoretical techniques in later chapters. The problems encountered and assumptions taken will be discussed in detail then.

#### 1.5 Points of Investigation and Outline of Dissertation

In this dissertation the tradeoffs in implementing a local network using a number of architectures are investigated. This is done both by considering the performance characteristics and hardware requirements of the systems. The networks chosen for comparison

include ring and broadcast schemes. The ring systems consist of the empty slot system [HOP78], the permission token system [FARB73], the register insertion system [HAF74b], and a pre-allocated bandwidth system. The broadcast schemes consist of the Aloha system [AB70] and the Ethernet system [METC76]. LSI partitioning of the network hardware is considered, as well as the feasibility of a single, variable architecture, generalpurpose, multi-network chip. Hardware support for protocol implementation is also examined.

Chapter 2 surveys local networks and gives a detailed description of the ring network at the Computer Laboratory, Cambridge. Chapter 3 compares ring systems, and Chapter 4 considers the stability and performance of broadcast systems. Chapter 5 presents a design and considers the feasibility of manufacture of a general purpose local network chip. In Chapter 6 the Cambridge ring is redesigned to provide hardware support for protocol implementation. Finally Chapter 7 presents some novel local network architectures incorporating simple packet routing mechanisms.

#### CHAPTER 2

#### LOCAL NETWORK SURVEY

# 2.1 Introduction

In this chapter a survey of local networks is presented. Initially, early systems are considered, followed by descriptions of a number of local networks in operation today. These include the University of California Irvine DCS, the Xerox Corporation Ethernet, as well as the ring system at the Computer Laboratory, Cambridge.

# 2.2 Ring networks

# 2.2.1 Early systems

An early example of a ring scheme is the IBM 2790 data communications system [STE70] where the data is transmitted to, or received from, a single loop supervisor. The 2790 system is based on fixed assignment of time-slots to channels. Each slot is assigned in turn to a different channel, the total data rate being 514.67 Kbits/sec. The primary use of the 2790 system is limited to data collection.

Another example of an early ring system is the permission token scheme proposed by Farmer and Newhall [FARM69]. Each terminal is allowed to transmit an arbitrary length message when in possession of a token. The token is placed at the end of the message to pass to the next node downstream. Such a scheme is particularly suited for sources of a bursty nature; however, only one source can transmit at a time. The token is implemented with the aid of a polarity violation modulation technique. A digit is transmitted as a pair of pulses with opposite polarities, and a violation of this principle indicates start of message (SOM) or end of message (EOM). The single bit which follws the EOM is the token and is either taken off by the node which transmits its data or is passed on unaltered. A ring monitor (Honeywell 516) is used to detect when the token becomes corrupted or when more than one token exists.

Further work on rings was done by Pierce, who proposed that a ring be divided into a number of fixed size slots [PI72a]. Each slot is marked full by the transmitter and empty by the receiver. Such a scheme allows an arbitrary amount of parallelism but has the disadvantage that hogging may occur; and if messages are longer than the slot size elaborate disassembly, sequencing and reassembling facilities have to be provided. Pierce further proposed a hierarchy of rings with buffering devices transferring messages between neighbouring rings. A single supervisor monitors each ring to ensure it does not become blocked with undeliverable data. Pierce's system was implemented by Kropfl [KR72] and also by Cocker [C072], who connected two laboratory computers (Honeywell 516) and achieved a maximum transmission rate of 50 Kbits/sec. To obtain simplicity at the gateway between rings, an addressing scheme with routing based on the Hamming distance between nodes has been developed by Graham [GR71].

A system where the controller is much more sophisticated and performs error control functions and coordinates terminals operating at different speeds is the Bell Laboratories Spider network [FRAS74a]. This network can handle up to 64 duplex data transmissions at the same time and makes use of two packet types. Large packets are used for data, and small packets for network control signals. The ring is divided into a number of slots, each slot being able to hold one packet of each type. The Spider network determines the route for all packets in a message in

advance of transmission, which allows the number of bits in the address field to be reduced. This has the advantage that there are fewer special error and control states, but there is an overhead to changing the communication path.

A ring scheme has independently been proposed by Hafner and by Reames based on inserting a shift register into the communications path [HAF74b, RE75a]. The packet to be transmitted is placed in the shift register before being transmitted to the next station. A packet can thus be inserted between two other packets on the ring. This means that bandwidth is distributed evenly between all users, and that the delay round the ring is proportional to traffic. A number of techniques can be devised for removing a shift register from the ring, some of which allow the register to be used again before the previous packet has been removed.

#### 2.2.2 University of California, Irvine Distributed Computer , System (DCS)

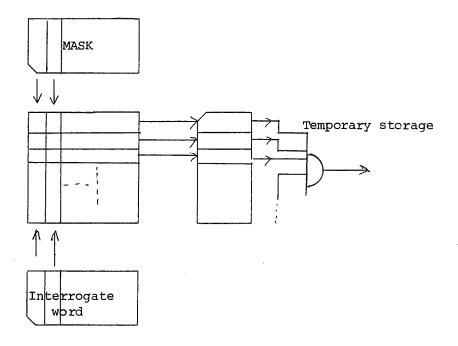

The Irvine ring is used for communication between computers in a distributed computer system. The ring interface allows process-to-process communication by use of an associative name table at each node. A new design called the Local Network Interface (LNI) has been proposed, which incorporates additional address fields for masking purposes, and which can be implemented in LSI [MO77].

The LNI connects a host to a communications medium and allows some changes in message format and transmission protocol. It is to be implemented on a single LSI chip, supported by line drivers and power supplies. The final design speed for the LNI is 1-5 MHz.

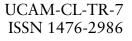

| DPNM | - | Destination Process Name Mask |

|------|---|-------------------------------|

| DPN  | - | Destination Process Name      |

| OPN  | - | Originating Process Name      |

| CRC  |   | Cyclic Redundancy Check       |

| MAEC |   | Match/Accept Error Check      |

#### Fig. 2.1 DCS Packet Structure

The structure of a DCS packet is shown in Fig. 2.1. Each LNI has a Name Table (NT) with two fields: the name field and the mask field. Each of these fields is 32 bits long, and the NT can hold a variable number of entries. As a message passes an LNI, all entries in the NT are compared in parallel with the address fields of the message. If one of the entries in the NT corresponds to the name in the message, an attempt is made to copy the data. The mask fields can be used to • override components of the name, which can then be subdivided into a number of fields. There are two control bits: the Match bit (M) and the Accept bit (A). These control bits are set by an OR operation at each LNI. The logical section of the message is protected by a CRC check, and there is a separate error check field for the MA bits (MAEC). As the MAEC field is typically much shorter than the CRC field, the delay through the LNI is minimised.

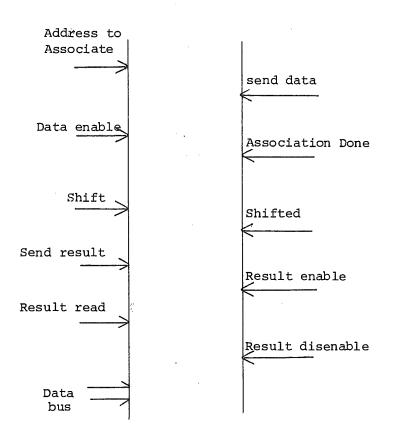

The transmission system allows only one LNI to add a message to the ring at a time. This is achieved by using a unique permission token (eight ones), which is used in the same way as in Farmers scheme [FARM69]. If no token arrives before a time-out takes place, a new token is generated. If more than one LNI times-out at the same time, several new tokens are created. These will either destroy themselves by overwriting, or two messages and two tokens will be output onto the ring. In the latter case, the LNI will notice that the CRC of the message following the token (which is the way it identifies its own message) is different to the one it originally transmitted and delete both messages. As the time-outs are set to different values, the ring recovers. The LNI is designed as a finite state machine built around a number of programmed logic arrays (PLAS). There are 18 byte input and output buffers, and the delay through each LNI is about 1 microsec. The maximum distance between LNIs is 1km, and the ring is optically couped to each LNI.

The Irvine ring provides very powerful addressing facilities, and thus allows efficient process to process communication. This is achieved at the expense of additional hardware in the LNI and of additional control fields in the packet. Such a system is not suited for applications where the network only provides a communication mechanism. Also, the scheme for token regeneration is complex; and as maximum packet length is 64 Kbits, the effects of hogging may reappear.

#### 2.2.3 University of Cambridge, Ring project

A system which the author has been concerned with is the ring project at the University of Cambridge. The data ring at Cambridge was designed to provide a high-speed, low-perror rate communications path between computers and other devices in the Computer Laboratory.

These devices are connected through the ring on an individual basis, and as yet there are no global high level protocols to provide automatic call establishment. The primary uses of the ring are for equipment sharing and file dumping [WI75, HOP78].

# 2.2.3.1 Ring Organisation

The original design was based on the register insertion principle, but in due course it was realised that a more attractive system would be one based on the empty slot principle. In its simple form the empty slot system suffers from hogging. This defect can be overcome if each packet makes a complete revolution of the ring and is not marked empty until it has passed the original source. With this scheme the interaction with the ring at each node is minimised and reliability is improved. As performance characteristics of the register insertion and empty slot systems are very similar, the latter was adopted as the basis for the Cambridge ring.

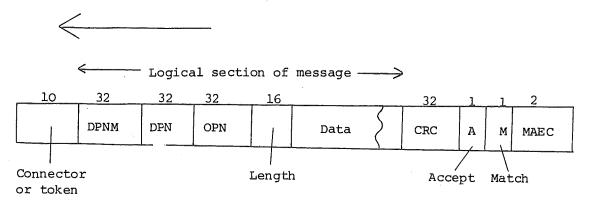

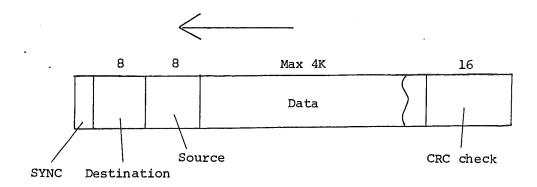

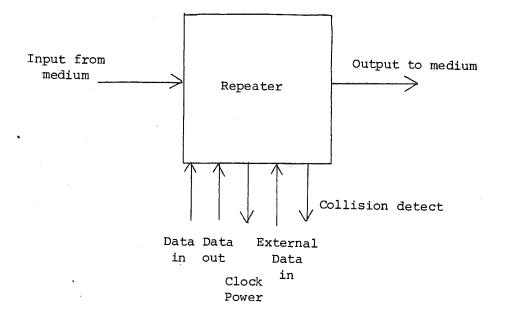

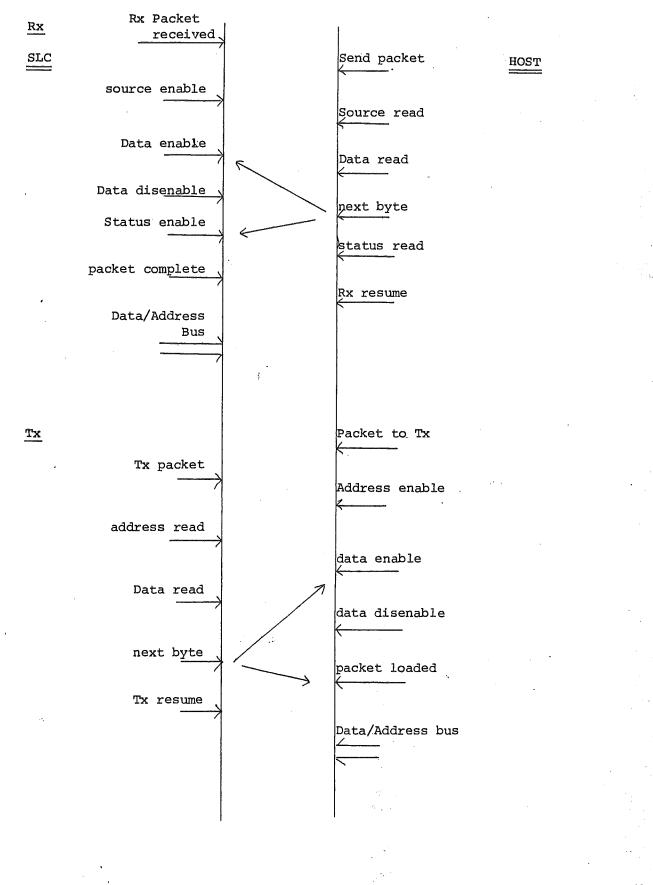

The structure of the ring is shown in Fig. 2.2. Repeaters are used to regenerate the signal at each node and can operate autonomously from the stations which perform the logic functions for transmission and reception of packets. Each station is interfaced to its host via a specially built access box. The access box tends to be sophisticated for a simple device such as a line printer and simple for an intelligent device such as a computer which can perform most of the required logic functions internally. There is a unique station called the monitor station, which is used for setting up the slot structure during turn-on, for monitoring the ring and clearing lost packets, and for accumulating error statistics.

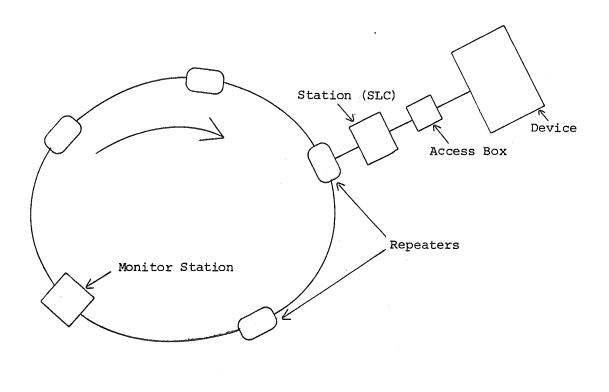

The packet structure is shown in Fig. 2.3 and is chosen to allow the maximum timing tolerance and minimum delay at the transmitter and

Fig. 2.2 Ring Structure

# Fig. 2.3 Packet Format

receiver. The leading bit is always a one, and is followed by a bit to indicate whether the slot is full or empty. Now follows a control bit used by the monitor station to mark as empty packets which are circulating indefinitely due to an error in the full/empty bit. This is followed by 4 eight-bit bytes, the first two of which are used for destination and source addresses and the last two for data. Finally, there are two control bits used for acknowledgement purposes.

When a station has a packet ready for transmission in its shift register, it waits until the beginning of the next slot. It now reads the full/empty bit and at the same time writes a one at the output. If the full/empty bit was a zero it transmits the packet. If, however, the full/empty bit was a one, the slot is already occupied and the algorithm is repeated at the following slot. This scheme minimises the delay at each node, which can be less than one bit time.

The transmitted packet makes its way to the destination, where the control bits are set on the fly to indicate accepted, busy, or rejected. It now returns to the source where the slot is marked empty. If the packet returns with the control bits unchanged, it was not recognised by any destination. Each station automatically computes the total number of slots in the ring and can thus clear the full/empty bit immediately.

It can thus be seen that on transmission the packet is delayed until an empty slot is found, but then the transmission is rapid. This is in contrast to the register insertion scheme where the delay round the ring can be large, but the initial delay before the register is inserted is small. As the destination does not explicitly signal when it is ready to receive the next packet, the ring can become clogged with packets returning marked busy if devices with varying speed characteristics are being interconnected. In order to overcome this the following algorithm

is incorporated in the hardware to delay responses other than accepted. If a source transmits the same packet twice, and both times it returns marked busy, then it is not allowed to retransmit it again until some time later. This additional delay is 2 x ring delay x traffic density for the first retransmission, and 15 x ring delay x traffic density for succeeding tries. Thus the number of busies is decreased and performance is improved. As the data field is short, line utilisation may be poor; however, multi packet messages can be received asynchronously.

Each station possesses a station select register which is initialised by the host. This register can be set to accept or reject all packets addressed to it, or to receive from one source only. When combined with a time-out mechanism, it can be used to allocate resources on the ring.

#### 2.2.3.2 Error Recovery

There are no CRC or parity checks on the transmitted packet, however, a copy of the information is retained at the source and is compared with the returning packet. This provides a powerful error detection facility but does not indicate that the packet was correctly copied at the destination.

If one of the SOP bits is corrupted or the full/empty bit becomes full, then this will be detected and corrected by the monitor station. If full becomes empty, then the packet might be ignored at the destination, but this will be detected by the source. Similarly, the transmitter will detect if the monitor station bit becomes corrupted in such a way that the slot is marked empty. An error in the address fields may cause the packet to be delivered incorrectly or be assigned to the wrong source. An error in the response bits may have a more serious effect as it will not be detected by the transmitter, which might

repeat the packet or assume it was received correctly when this was not the case. Under some circumstances such errors can propagate, but generally they are detected by the source or monitor station within one ring delay. Unnoticed errors are rare.

Each station continually determines the slot count by using the gap digits and packet leader digits. The gap digits are set to zero, and at least one such digit must be present in the system.

Additional error detection facilities are provided by the monitor station which can issue test packets, store erroneous ones, and provoke a response from any station. This response is independent of the returning data so that such a test can be carried out when the ring is broken.

#### 2.2.3.3 Hardware

The ring is built using TTL technology and operates at 10 MHz, with a maximum distance of 200 meters between repeaters. Higher rates would be readily attainable with faster logic. The signals are transmitted along twisted pairs of the type normally used for duplex operation of teletypes. Transformers are used throughout for isolation and common mode rejection. As the repeaters have to operate reliably, whether they are connected to a station or not, they are powered directly from the ring. This power is injected into the system by a number of power units.

Each station is fully duplex so it can transmit and receive concurrently and independently. The number of bits delay at a station is a fraction of a bit, and the minimum ring delay is about 4 microseconds.

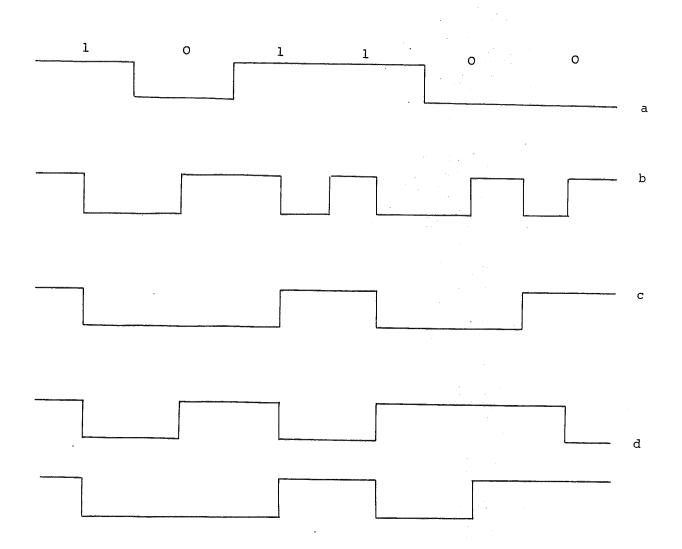

A number of modulation techniques were considered, and some of these are shown in Fig. 2.4. The four wire scheme was chosen as it is suitable for a pair of twisted wires and has no ambiguity about the

a. pulse for 1 no pulse for O

b. phase modulation

c. p.m./2 (delay modulation)

d. four wire system

start of a digit (unlike phase modulation). A change on both pairs indicates a one and a change on only one pair indicates a zero, each pair being used alternately. The advantages of the four wire system can be summarised as follows:

- (1) it is DC balanced

- (2) there is very little encoding or decoding delay

- (3) both pairs are treated identically thus minimising skew

- (4) a choice of clock techniques is available

- (5) it is easy to provide a control signal for a phase locked loop (PLL).

- (6) it is easy to detect some errors (e.g. no change on either pair)

- (7) it cannot move half a digit out of phase

- (8) it is easy to transmit power without elaborate filters.

#### 2.2.3.4 Discussion

The Cambridge ring was designed in an environment where many different types of machines exist and where the disruption to their operating systems has to be minimal. This differs significantly from systems where the designer has a free hand to develop host software according to his wishes, and especially from systems which connect a large number of identical machines. Furthermore, it was a design task to make the system as inexpensive as possible, and it was thus kept simple. Nevertheless, many options are left, and some of these are discussed below.

In a simple scheme each source transmits to only one destination at a time. This can be extended to allow the multiplexing of packets to different destinations. If this is done, an algorithm has to be developed for matching the speed of transmission and reception and to ensure no sources are continually blocked. For devices with similar speed characteristics this can easily be done by employing a round-robin scheme. Where the communicating devices operate at different data rates, a speed number could be associated with each destination. This number is updated when the delay does not match the estimate. Other algorithms have been developed which achieve this in different ways.

Under some circumstances the services of a particular node might be required by a number of stations at the same time. In the Cambridge system such requests are arbitrated on a random basis, and thus some sources experience additional delay before successfully transmitting. Where the application demands more precise performance characteristics, such requests should be queued.

# 2.2.4 Ring System Conclusions

Rings allow a number of users to demand share a single communications link. As one of the most important parameters in network design is delay, the rings are normally operated at low loads. This has the advantage that most of the irregularities inherent at high traffic levels do not occur.

Rings allow easy implementation of distributed switching and control functions and are thus well suited for use in distributed computer systems. There are also economic advantages to ring systems: they can be designed to be completely modular and incremental in nature and thus do not require a large initial investment.

The reliability of a ring system poses a problem as the failure of any element will disable the entire network. This can be overcome by incorporating a parallel standby ring, and a number of such schemes have been proposed [ZA74]. Such techniques are not suitable for rings with a small number of stations as the probability of failure of the reconfiguration units is greater than the probability of their improving

network reliability. In any case, ring failures will often be less serious than a breakdown in a centralised system in terms of fault location and repair times.

### 2.3 Broadcast Networks

Broadcast networks are characterised by the fact that a number of nodes may attempt to transmit at the same time, which results in all transmissions being corrupted. Such networks have been developed primarily to exploit the broadcast and multi-access capabilities of radio channels, although they can be implemented using a conventional cable system. The radio broadcast channel can be designed using satellite or ground radio. In the former case the round trip delay is approximately 0.27 secs, and in the latter the propagation delay is much smaller (microseconds). For a satellite channel, by the time a packet reaches the receiver, the transmission is past history, and no control action can be taken. When the propagation delay between transmitter and receiver is small, the transmission can be aborted early on if this is desirable.

# 2.3.1 Aloha Systems

The broadcast network was first proposed by Abramson for inter-• connecting terminals to a central computer at the University of Hawaii using a UHF radio channel [AB70]. One channel is used for transmitting data to the computer, and another for transmitting acknowledgements back to the terminals. Each terminal transmits and stores one packet at a time and then initiates a time-out for the returning acknowledgement. The central computer monitors incoming traffic and can detect if a collision has taken place by using a suitable error check, in which case it does not send the acknowledgement. If no acknowledgement is received at the terminal before the time-out, the packet is retransmitted. In order to avoid two terminals timing-out and colliding repeatedly the time-outs for each are set to different values. An alternative scheme is for each terminal to choose the retransmission interval from a random distribution. A terminal uses no part of the channel when it is idle, but can utilise all the bandwidth during a burst. However, the maximum theoretical channel utilisation is 18%, and it has been shown that the system is unstable at saturation traffic levis [FAY77].

An Aloha network with users transmitting at different power levels has been proposed, where if a collision takes place, the most powerful user transmits successfully [RO73]. This is achieved by employing the capture effect of receivers, a transmission being received correctly if it is sufficiently more powerful than the others. This results in a higher theoretical channel capacity.

In a pure Aloha system a transmitted packet of length T is vulnerable to collision for a time 2T. If channel time is divided into fixed length slots, then packets either collide and completely overlap or are transmitted successfully. Thus, the vulnerable period is reduced to T, and theoretical channel capacity is doubled. This technique is more complicated than the pure Aloha scheme as a global check for synchronisation of user packets has to be provided. The slotted Aloha scheme is unstable for high traffic inputs and throughput goes to zero.

### 2.3.2 Carrier Sense Multiple Access (CSMA)

. When the propagation delay between source and destination is small the CSMA system increases the theoretical channel capacity. Before transmission the channel is sensed, and if it is occupied the transmission

is deferred until some time later. If the channel is sensed idle, then the transmission proceeds and is vulnerable to interference for a time equal to the propagation delay between the two most distant points in the system. If a collision takes place, it is detected by both transmitters, and the packets are retransmitted later. Once a transmission has been established it continues without interruption [METC76].

A number of protocols, some of which considerably increase throughput, have been proposed for the user's action after sensing the channel [KL75a]. However, like Aloha systems, the CSMA system is characterised by the throughput tending to zero for large values of channel traffic.

### 2.3.2.1 Xerox Corporation Ethernet

A local network based on the CSMA principle and built using coaxial cable as the transmission medium has been built at Xerox PARC. Ethernet interconnects a large number of small homogeneous ALTO computers, each with its own disc and VDU. These machines are linked by a number of cables which form a tree structure. A gateway computer is located at the root of the tree to perform routing and buffering functions. There exists only one path between any source-destination pair, and the cables can be extended from any point providing this rule is adhered to. In Ethernet the network specific hardware is simple, most of the communication task being performed in the microprogram of the ALTOS. Packets are restartable at the source, the absence of an acknowledgement causing the transmission to be repeated. This principle is carried on throughout the levels of the protocol structure so that if a discrepancy occurs at any level no action is taken as the appropriate procedure is carried out at the source. The reason for this approach is that the CSMA system is inherently error-prone, and it is up to the processes in the source and destination to take the necessary precautions to achieve

the desired degree of reliability.

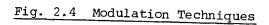

A station is connected to the Ether by means of a tap and a transceiver. The tap is designed in such a way that it can be connected without disruption to the network, and the transceiver is designed to fail without polluting the Ether. The maximum cable length is 1 KM and the system operates at 3 MHz. It is capable of interconnecting up to 256 stations, of which about 125 are in use. Phase modulation is used for transmitting data; this allows the carrier to be easily detected as there is at least one pulse on the cable for each bit-time. A typical Ethernet packet is shown in Fig. 2.5.

## Fig. 2.5 Ethernet Packet Structure

The structure and functions of the hardware and software are divided into a number of levels. The lowest level encompasses the transceiver hardware and the error check generator. Above this lies the physical-link level which is concerned with retransmission, serialisation and deserialisation of data, speed matching, sequencing, and acknowledgements. This level is efficient and has few message formats. At the next level there is the logical-link software for multiplexing several user data streams into a single data stream. It is at this level that internetwork protocols such as TCP are implemented. At the highest dialogue level messages are sent over a logical link between users; TELNET and file-transfer protocols (FTP) are implemented, as is a mailing system. The high level protocols consume the greatest amount of computational time.

It takes 40-50 simultaneous disc transfers for the system to become significiantly loaded, and thus no special retransmission algorithms are implemented in hardware. However, the following algorithm is employed in microcode to increase Ether efficiency. Retransmission intervals are multiples of a slot, and every time a transmission attempt ends in a collision, the controller delays for an interval of random length, with a mean twice the previous interval. Under light load conditions the mean is close to one, and retransmissions are prompt. As the traffic increases a backlog of packets develops and the retransmission intervals increase, the channel efficiency remaining high.

In the Ethernet system the cost and complexity of the hardware is minimised by performing most of the transmission functions in microcode. This means that the transmission algorithms can be easily changed, but the attached computers must be sufficiently sophisticated and homogeneous to allow this. The transceiver provides a collision-detect signal, which can be up to 20 DB weaker than the transmission and has to

be attached to the Ether in such a way that no reflections are produced. A break in the Ether, or a mismatched tap, disable the system.

An attractive feature of the Ethernet system is the use of ALTO computers to locally fulfil most of the user's needs, with the exception of very big tasks and I/O. These are catered for by special server nodes which can thus be optimised for their tasks. As transmission speeds increase the Ethernet (and CSMA) systems will become less attractive, since by the time a collision is detected, a large part of the packet will have been transmitted:

### 2.4 Other local network proposals and developments

There are a number of broadcast techniques which resolve the instability problem under overload conditions [HEI76]. These fall into two categories: dynamic control procedures for Aloha type systems and channel reservation schemes. Dynamic control schemes require each user to take action to prevent channel saturation when the backlog of packets reaches a certain level. Reservation schemes are suitable for systems where each message is composed of several packets since the access request is made for complete messages.

Local network techniques have been used for linking very large machines. This generally entails the design of a sophisticated station which can communicate at data channel speeds. Examples are the Goddard Space Flight Center network which links four IBM360s, a CDC-7600, a Cray-1, and a number of smaller satellite machines and has station costs in the region of \$25,000. Network Systems Corporation market a similarly priced system based on coax cable operating at 15 MHz which has been installed for fast peripheral (disc) sharing at a number of locations [NBS77].

At the other extreme a number of microprocessor based systems are being built. These can be very cheap, as in the Queen Mary College C-net [WES77], or suitable for applications where a large number of microprocessors are interconnected for control applications [DOW77]. An example of a process control application is the Ford CSMA network which monitors the operation of machines on an assembly line.

Other local networks include the Mitrenet system [HANK77], which has a network language for interprocess communication and synchronisation and is run on a single RF coaxial cable which also supports other networks, telephone and TV channels; another is a broadcast network of MIT.

#### CHAPTER 3.

### A PERFORMANCE COMPARISON OF RING COMMUNICATION NETWORKS

### 3.1 Introduction

In this chapter a number of models for ring communication networks are developed. These will be used to provide a better insight into the way the networks behave and to compare their performance characteristics. This is done by describing the communications system in terms of a network of queues. The models describe both the functions of the logical units of the networks and the different transmission protocols, as well as measure the average delay and traffic handling capabilities of the networks. The analysis takes into account the storage capacity (or delay) at each node, scheduling restrictions, and retransmissions due to errors.

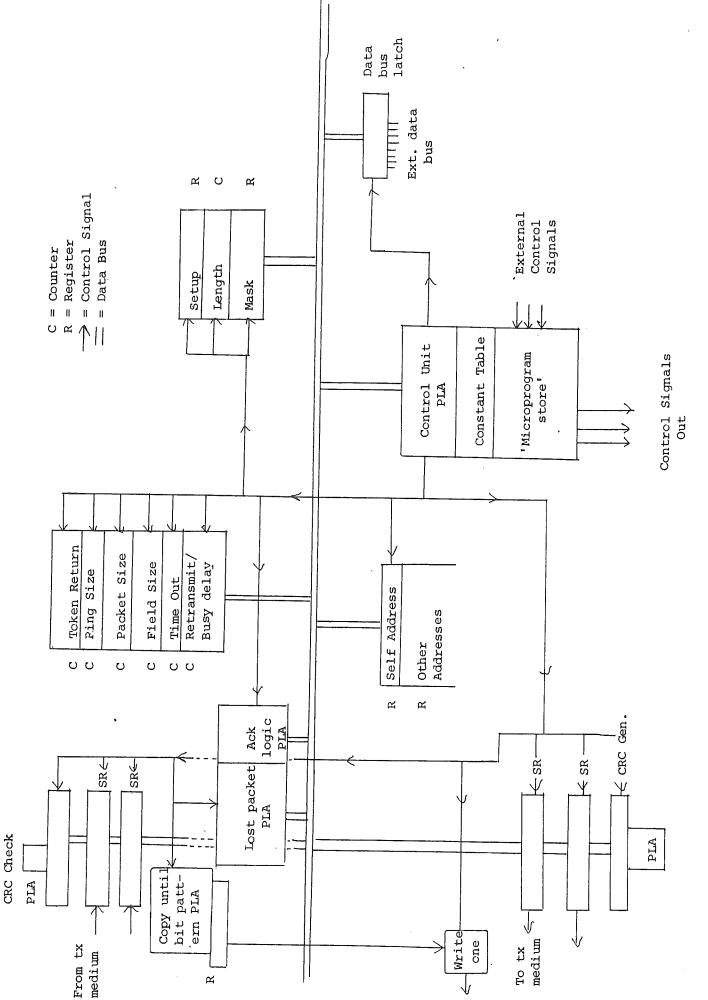

The networks compared are the register insertion system, the empty slot system and the permission token system. A further ring architecture, called the pre-allocated bandwidth system, is also evaluated, and its areas of application are outlined. These networks are implemented on the station logic chip described in Chapter 5.

### 3.2 Previous work

The main parameter of interest when studying a computer network is delay. Once this has been calculated, the throughput can be obtained either by explicit equations or by Little's theorem. The parameters which influence delay are:

- . (1) the station activity and how steady (homogeneous) it is

- (2) the amount of buffer storage on the ring

- (3) the use of protocols and structure of the ring

- (4) errors and error recovery procedures

The delay experienced by a packet can be split into two components:

- (1) the time before the packet is output onto the ring

- (2) the delay around the ring itself

Other ring performance characteristics are the line utilisation (a function of data time, busy time, and idle time), and the effects of clustering, of the monitor station, of special packets, and of a complete ring break. Some of the above properties are best studied by use of a simulation rather than an analytical model as they are too complex to handle analytically. However, a sufficiently complicated model for the ring can be developed to show the relative importance of all major parameters.

## 3.2.1 Previous work on ring systems

Previous queuing theory work on ring systems can be divided into two categories :

(1) the analysis of the general cyclic queue problem

(2) the direct analysis of ring communication systems

The problem of a cyclic queue was first studied by Koenigsberg [KO58]. In his system a fixed number of customers requested service at a number of service centres in cyclic order with no external arrivals or departures. When the service times for the servers are equal, the probability of any system state can be obtained by combinatorial methods. When each service center has a different service-time the solution is more complicated, and Koenigsberg calculated the analytical formulae for up to five service centers. The number of customers queued at a center was found, along with the delay at the center, the mean cycle time, and the probability that a stage is idle.

Finch [FIN59] extended these ideas to include cyclic queues with

feedback. He found unique solutions for two types of cyclic queue discipline. In both cases an external source feeds one node with customers. In the first system customers move to the next node on completion of service, except for one node from which they can move to any node. In the second system, as well as moving to the next node, customers can return to the queue from which they have just departed. Both Koenigsberg and Finch use the product solution to a birth-death queuing system as a starting point for their solutions. This leads to calculation of the marginal probability that there are n customers at the j'th stage, the average number of customers at the j'th stage, and the average number of customers waiting. Finch also points out that in the case of a single server, the two types of feedback are the same, and that it is then possible to treat the case of random arrivals and general service time in a manner similar to that of a M/M/1/K queue.

Cyclic queues with restricted queue lengths were studied by Gordon and Newell [GO67a]. They showed that the closed cyclic systems considered were equivalent to open systems in which the number of customers is a random variable. A two-stage system was studied, the stochastic equations being comparable to those of a finite-capacity, single server queue. Next, systems with small and large number of customers,were considered. Results show that for a system with few customers the restricted queue length at each node has little effect, and that with many customers blocking dominates, and has a similar effect to queuing.

The above results are primarily applicable to the register insertion system (and to simple store and forward networks). A parallel can be drawn between service time and the delay introduced at each node by the variable length shift register. However, this does

not emulate the real system well since the shift register is of finite length, and the analysis is difficult except in special cases.

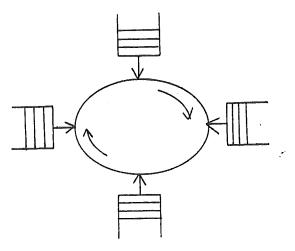

In other ring networks the delay round the ring is deterministic and is proportional to its length, the queue forming at the input (Fig. 3.1). The models developed in this chapter treat the rings in this way, the register insertion system being shown to be logically equivalent.

### Fig. 3.1 Queue Structure for Ring Network

Hayes and Sherman studied the traffic behaviour of a Pierce loop system (i.e. a system with fixed-size slots circling round a loop and with no hog prevention technique) [HAY71]. They were interested in the effect of buffering on message delay, and the model incorporates an exponential on-off input process to take into account the bursty nature of data sources. The exponential on-off source is approximated in two ways: the first, by assuming messages with exponentially distributed length arrive at Poisson rate, and the second, by assuming that the source outputs at a constant rate equal to the average number of bits/sec

output by the exponential on-off model. The first of these approximations is suitable for sources that are not very active, the second being better suited to active ones. Using this model mean line idle and busy times were obtained, leading to the calculation of throughput and delay.

Another paper by Hayes and Sherman [HAY72] is concerned with the study of data multiplexing techniques for user populations whose source characteristics are of inquiry/response type. Thus, source models for users, as well as for computer responses, are developed which approximate an inquiry/response context. The three systems compared are polling, random access, and Pierce loop. It is found that only the polling system is sensitive to synchronisation delay, which takes place every time a user station transmits to the central facility. The three schemes have similar performance characteristics, random access showing slightly lower delays than the other two.

Kaye [KAY72] studied a loop similar to the token system and gave examples with no propagation delays. He showed that for low loads, the probability of a message arriving before the previous one has been processed is low and thus developed approximations.

### 3.2.2 Input buffer structures

In this chapter two kinds of input buffer structures are modelled. In the first it is assumed that the input buffer at each node is of infinite length, and that all arriving packets are stored and transmitted in due course. When the arrival rate equals the service rate, the number of packets waiting for transmission is infinite. In the other buffer structure buffer size is limited to one packet. Any packets arriving while the buffer is full are turned away and do not effect the arrival

process. Thus the arrival rate must always exceed the service rate.

### 3.3 The infinite size input buffer

A number of functions for the performance of the networks with an infinite size buffer at the input are derived below. In all cases the fixed electronic and cable delay around the ring is given by NBe.

NBe = Nb<sub>is</sub> +

$$\sum_{i=1}^{N} b_{ii}$$

where b<sub>is</sub> is the delay in bits through station i

b is the electronic delay of the lines between station i and i+1

and N is the number of stations.

A summary of the notation used is given in the Appendix.

### 3.3.1 The register insertion system basic performance function

In this scheme each station can insert at most one packet into the ring. This packet makes its way to the destination and then back to the source where it is removed. Two cases for a subsequent transmission are considered: (a) when the next packet can be loaded and transmitted instantaneously, and (b) when this takes a finite number of bits delay E. Any bits stored in the lines when the system is idle are not utilised and form gap digits. Let us consider the delay from the time a packet arrives ready for transmission at the head of the input queue, to the time it arrives back at the source and is removed allowing another transmission to take place. This is the service delay of the ring and when divided by the ring speed, gives the service time of the ring (per packet). Service delay can be divided into three components.

- The electronic delay of the lines and the transmission and reception of own packet

- (2) The delay due to transmission only being permissable between other packets

- (3) The delay due to the transmitted packet passing through other inserted registers

Let Tx be the mean arrival rate of bits to a node from the outside world and Tr be the speed of the ring, and let

$$z = \frac{Tx}{Tr}$$

and p(z) represent the mean probability that a station has a packet available for transmission in its buffer (this packet is transmitted at the next opportunity).

The first register insertion system to be evaluated is that with instant replacement of old packets in the shift register. Type 1 delay is given by

where Ps is the packet size. If the packet to be transmitted arrives before the previous has been received back, no alignment delay is experienced. If, however, it arrives after the previous one has been processed, it is assumed that the mean value of this delay is Ps/2. The probability of encountering a packet at the moment of transmission is given by the ratio of number of packet bits on the ring to the total number of bits stored in the ring and is

$$\frac{p(z)NPs}{p(z)NPs + NBe}$$

The probability that the packet arrives after the previous has been processed is 1-p(z), thus type 2 delay is given by

$$(1 - p(z)) \frac{Ps^2 p(z)}{2(Ps p(z) + Be)}$$

3.2

Type 3 delay is governed by the number of other registers inserted into the ring multiplied by the delay in each and is given by

Thus, the basic performance function for the register insertion system with instant replacement of packets is given by combining equations 3.1, 3.2, and 3.3:

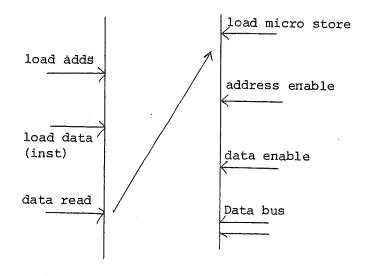

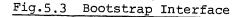

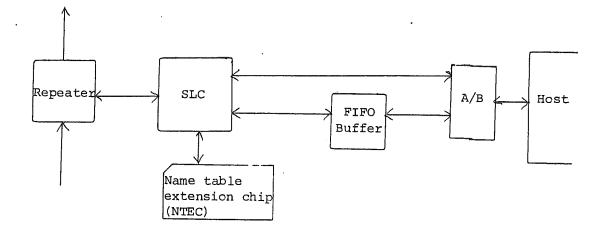

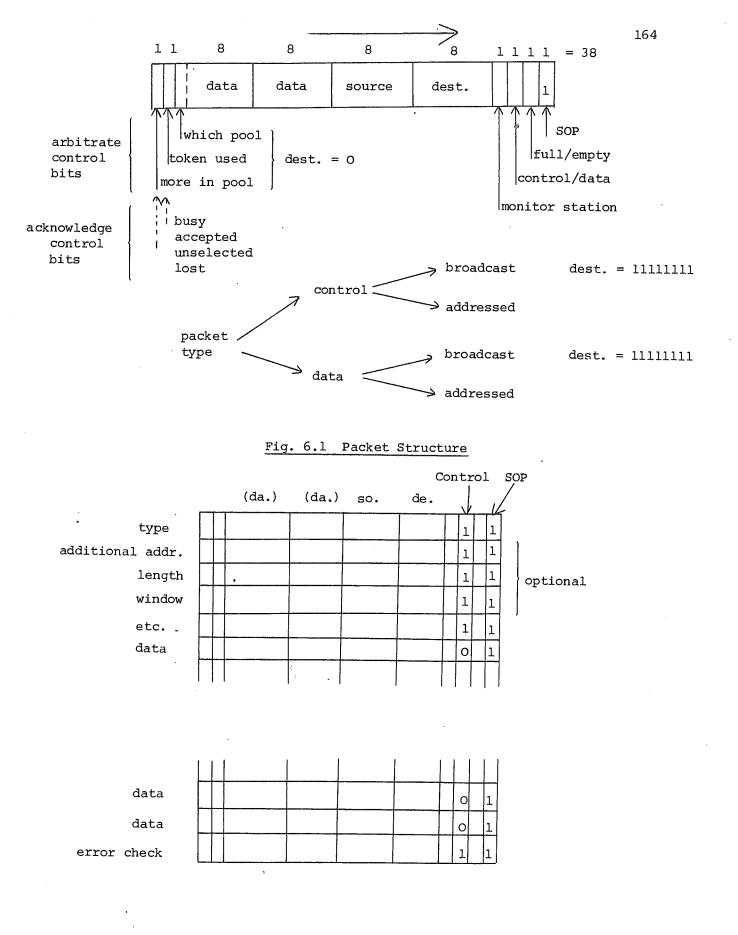

$$B_{\rm D} = NBe + Ps + \frac{(1-p(z))Ps^2 p(z)}{2(Ps p(z) + Be)} + p(z)(N-1)Ps \quad 3.4$$