Technical Report

Number 52

**Computer Laboratory**

# The design of a ring communication network

Steven Temple

January 1984

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

http://www.cl.cam.ac.uk/

# © 1984 Steven Temple

This technical report is based on a dissertation submitted January 1984 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Corpus Christi College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/TechReports/

Series editor: Markus Kuhn

ISSN 1476-2986

# THE DESIGN OF A RING COMMUNICATION NETWORK

Steven Temple

Corpus Christi College

÷

,

A dissertation submitted for the degree of Doctor of Philosophy in the University of Cambridge

January 1984

#### SUMMARY

This dissertation describes the design of a high speed local area network. Local networks have been in use now for over a decade and there is a proliferation of different systems, experimental ones which are not widely used and commercial ones installed in hundreds of locations. For a new network design to be of interest from the research point of view it must have a feature or features which set it apart from existing networks and make it an improvement over existing systems. In the case of the network described, the research was started to produce a network which was considerably faster than current designs, but which retained a high degree of generality.

As the research progressed other features were considered, such as ways to reduce the cost of the network and the ability to carry data traffic of many different types. The emphasis on high speed is still present but other aspects were considered and are discussed in the dissertation. The network has been named the Cambridge Fast Ring and the network hardware is currently being implemented as an integrated circuit at the University of Cambridge Computer Laboratory.

The aim of the dissertation is to describe the background to the design and the decisions which were made during during the design process, as well as the design itself. The dissertation starts with a survey of the uses of local networks and examines some established networks in detail. It then proceeds by examining the characteristics of a current network installation to assess what is required of the network in that and similar applications. The major design considerations for a high speed network controller are then discussed and a design is presented. Finally, the design of computer interfaces and protocols for the network is discussed.

ii

# PREFACE

I wish to thank my supervisor, Dr. Andy Hopper, for stimulating my interest in local networks and for guidance and many useful discussions during the course of my research. I should also like to thank Professor Roger Needham for his encouragement and for allowing me to spend time working in the USA.

I am indebted to the following people who have read and commented on various parts of this dissertation: Andy Harter, Jane Hewitt, Andy Hopper, Mike Muller, Robin Williamson and Neil Wiseman.

Throughout my research I have been supported by a grant from the Science and Engineering Research Council for which I am grateful.

Except where explicitly stated in the text, this dissertation is the result of my own work and is not the outcome of any work done in collaboration. Furthermore, this dissertation is not substantially the same as any that I have submitted for a degree, diploma or other qualification at any other university. No part of this dissertation has already been or is being concurrently submitted for any other degree, diploma or other qualification.

.

# CONTENTS

| 1 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                              |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|   | <ul> <li>1.1 Thesis Aims <ol> <li>1.1.1 Outline</li> <li>1.1.2 Acknowledgement</li> </ol> </li> <li>1.2 Uses of Local Area Networks <ol> <li>1.2.1 Resource Sharing</li> <li>1.2.2 Distributed Computer Systems</li> <li>1.2.3 Office Automation</li> <li>1.2.4 Other Applications</li> <li>1.2.5 Applications for a Faster Network</li> </ol> </li> </ul>                                                                                    | 1<br>2<br>2<br>3<br>4<br>5<br>6<br>7                           |

| 2 | LOCAL AREA NETWORKS                                                                                                                                                                                                                                                                                                                                                                                                                           | 9                                                              |

|   | <ul> <li>2.1 Pierce Loop</li> <li>2.2 Ethernet</li> <li>2.3 Cambridge Ring</li> <li>2.4 Macrolan</li> <li>2.5 IBM Token Ring</li> <li>2.6 Protocols and Standards</li> <li>2.7 Summary</li> </ul>                                                                                                                                                                                                                                             | 9<br>13<br>16<br>20<br>22<br>25<br>28                          |

| 3 | A CASE STUDY OF A CAMBRIDGE RING                                                                                                                                                                                                                                                                                                                                                                                                              | 29                                                             |

|   | <ul> <li>3.1 The Test Environment</li> <li>3.2 The Monitoring Device <ul> <li>3.2.1 Use of the Traffic Monitor</li> </ul> </li> <li>3.3 Observed Traffic Patterns <ul> <li>3.3.1 Utilisation</li> <li>3.3.2 Useful Traffic</li> <li>3.3.3 Block Lengths</li> </ul> </li> <li>3.4 Performance Under Heavy Load</li> <li>3.5 Comparison with Ethernet</li> <li>3.6 The Growth of the CMDS</li> <li>3.7 Changes to the Cambridge Ring</li> </ul> | 29<br>30<br>33<br>34<br>35<br>35<br>37<br>39<br>42<br>44<br>45 |

| 4 | DESIGN CONSIDERATIONS OF THE CAMBRIDGE FAST RING                                                                                                                                                                                                                                                                                                                                                                                              | 47                                                             |

|   | <ul> <li>4.1 Topology</li> <li>4.1.1 Mesh Networks</li> <li>4.1.2 Star Networks</li> <li>4.1.3 Bus Networks</li> <li>4.1.4 Ring Networks</li> <li>4.1.5 Summary</li> <li>4.2 Bandwidth</li> </ul>                                                                                                                                                                                                                                             | 47<br>47<br>48<br>48<br>49<br>50<br>50                         |

|   | 4.3 Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                | 53                                                             |

|   | 4.3.1 Broadcast Addressing<br>4.3.2 Source Selection                                                                                                                                                                                                                                                                                                                                                                                          | 55<br>5 <b>6</b>                                               |

|   | 4.4 Error Detection and Correction                                                                                                                                                                                                                                                                                                                                                                                                            | 56                                                             |

|   | 4.4.1 Maintenance                                                                                                                                                                                                                                                                                                                                                                                                                             | 58                                                             |

|   | 4.5 Reliability                                                                                                                                                                                                                                                                                                                                                                                                                               | 59                                                             |

|   | 4.6 Cost                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60                                                             |

| 5 THE CAMBRIDGE FAST RING, MARK 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| <ul> <li>5 THE CAMBRIDGE FAST RING, MARK 1</li> <li>5.1 Overview</li> <li>5.2 Addressing</li> <li>5.2.1 Address Filtering.</li> <li>5.2.2 Inter-Ring Addressing.</li> <li>5.3 Hardware Implementation</li> <li>5.3.1 Line driving system.</li> <li>5.3.2 Transmit and receive buffers.</li> <li>5.4 Transmission and reception</li> <li>5.4.1 Responses</li> <li>5.5 Error Checking and Maintenance</li> <li>5.5.2 Error Checking</li> <li>5.6 Bridge Design</li> </ul>                                   | 64<br>64<br>67<br>67<br>67<br>68<br>70<br>71<br>72<br>75<br>75<br>77<br>77<br>78<br>78                         |

| 5.7 Monitor Station Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79                                                                                                             |

| 5.8 Performance<br>5.9 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80<br>81                                                                                                       |

| 6 THE CAMBRIDGE FAST RING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83                                                                                                             |

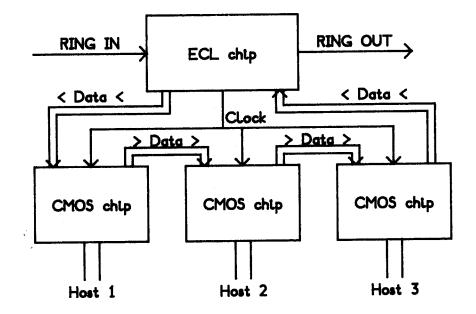

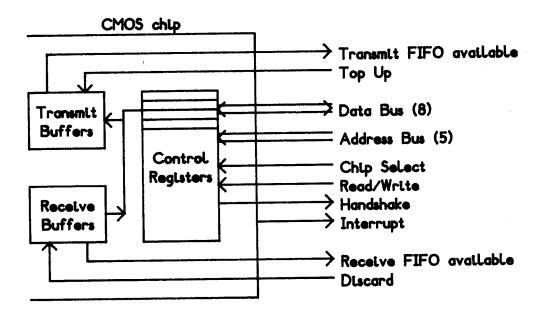

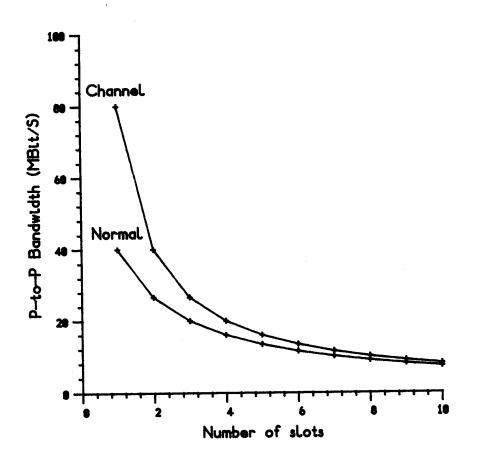

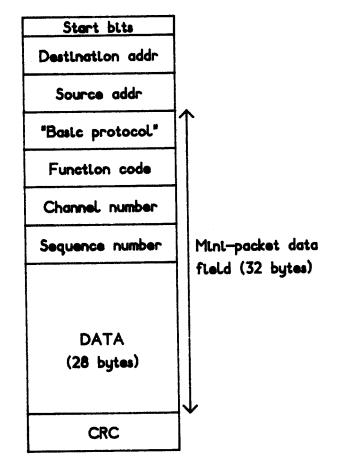

| <ul> <li>6.1 Hardware <ul> <li>6.1.1 ECL chip functions</li> <li>6.1.2 CMOS chip functions</li> </ul> </li> <li>6.2 Host Interface <ul> <li>6.3 Minipacket Structure</li> <li>6.4 Responses</li> <li>6.5 Channel Mode</li> <li>6.6 Other Changes <ul> <li>6.6.1 Error Checking and Maintenance</li> <li>6.6.2 Node Configuration.</li> <li>6.6.3 Transmission and Reception</li> <li>6.6.4 Source Selection</li> </ul> </li> <li>6.7 Performance <ul> <li>6.8 Discussion</li> </ul> </li> </ul></li></ul> | 83<br>84<br>85<br>86<br>88<br>89<br>91<br>92<br>92<br>92<br>92<br>92<br>92<br>93<br>93<br>93<br>93<br>93<br>93 |

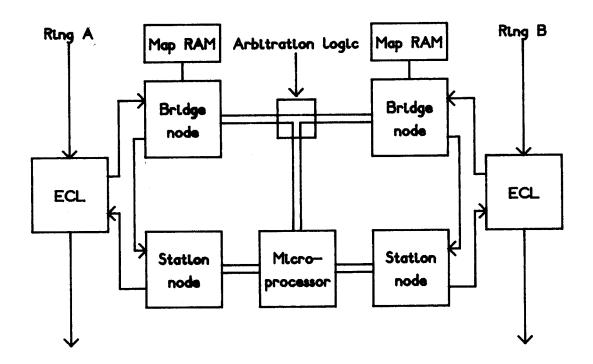

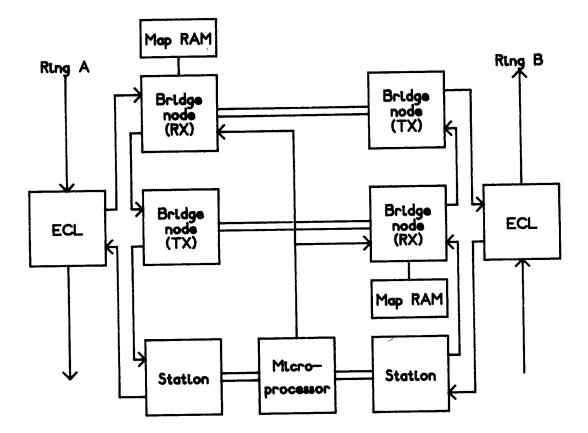

| <ul> <li>7 BRIDGES</li> <li>7.1 Modes of Use</li> <li>7.2 Ring Bridge Design</li> <li>7.2.1 Simple Bridge</li> <li>7.2.2 Full Duplex Bridge</li> <li>7.3 Bridge Maps</li> <li>7.3.1 Low Cost Bridges</li> <li>7.4 Factors Influencing Bridge Performance</li> <li>7.5 Discussion</li> </ul>                                                                                                                                                                                                               | 97<br>98<br>98<br>99<br>100<br>102<br>102<br>102                                                               |

| 8 PROTOCOLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 105                                                                                                            |

| <ul> <li>8.1 Protocols and Traffic Types</li> <li>8.2 Protocols and the CFR</li> <li>8.2.1 Basic Requirements</li> <li>8.2.2 Channel Numbers</li> <li>8.3 A Protocol for the CFR</li> <li>8.3.1 A Single Shot Protocol</li> <li>8.4 Discussion</li> </ul>                                                                                                                                                                                                                                                 | 105<br>106<br>107<br>108<br>110<br>112<br>114                                                                  |

| 9 NETWORK INTERFACES                    | 116 |

|-----------------------------------------|-----|

| 9.1 Interface Methods                   | 116 |

| 9.2 Interfaces and Protocols            | 117 |

| 9.3 Simple CFR Interfaces               | 118 |

| 9.4 High Speed CFR Interface            | 119 |

| 9.4.1 Minipacket Processor Requirements | 120 |

| 9.4.2 Protocol Processor Requirements   | 122 |

| 9.4.3 NIP Summary                       | 122 |

| 9.5 Error Detection                     | 122 |

| 9.6 Discussion                          | 123 |

| 10 CONCLUSION                           | 124 |

| 10.1 Discussion                         | 124 |

| 10.1.1 Bandwidth Partitioning           | 125 |

| 10.1.2 Bridges                          | 125 |

| 10.2 Further Work                       | 126 |

| REFERENCES                              | 128 |

|                                         |     |

.

# GLOSSARY

.

The following abbreviations are frequently used in this thesis. Where appropriate, they are explained in greater detail when they first appear in the text.

| AFC     | Address Filtering Chip                                 |

|---------|--------------------------------------------------------|

| BSP     | Byte Stream Protocol                                   |

| B/₩     | Bandwidth                                              |

| CFR     | Cambridge Fast Ring                                    |

| CFR/1   | Cambridge Fast Ring, Mark 1                            |

| CMDS    | Cambridge Model Distributed System                     |

| CMOS    | Complementary Metal Oxide Semiconductor                |

| CR      | Cambridge Ring                                         |

| CRC     | Cyclic Redundancy Checksum                             |

| CSMA/CD | Carrier Sense Multiple Access with Collision Detection |

| DMA     | Direct Memory Access                                   |

| ECL     | Emitter Coupled Logic                                  |

| FIFO    | First In, First Out memory                             |

| IEEE    | Institute of Electrical and Electronic Engineers       |

| LAN     | Local Area Network                                     |

| LSI     | Large Scale Integration                                |

| MOS     | Metal Oxide Semiconductor                              |

| MSI     | Medium Scale Integration                               |

| NCC     | Network Controller Chip                                |

| NIP     | Network Interface Processor                            |

| ррВ₩    | Point-to-Point Bandwidth                               |

| PROM    | Programmable Read Only Memory                          |

| PUP     | PARC Universal Packet                                  |

| RAM     | Random Access (read/write) Memory                      |

| ROM     | Read Only Memory                                       |

| SSP     | Single Shot Protocol                                   |

| sysBW   | System Bandwidth                                       |

| TTL     | Transistor Transistor Logic                            |

| ULA     | Uncommitted Logic Array                                |

#### Chapter 1

## INTRODUCTION

Practical research into the communication systems now known as Local Area Networks began in the late 1960's. The initial aim of the research was to provide a means of resource sharing in multi-processor environments. Local area networks evolved from larger packet switching networks such as the ARPANET [Roberts 73] and have the following characteristics:-

- Connection of digital devices over a small geographical area

typically less than a few square miles

- 2) High data rate and low bit error rate

over 1MBit/S and better than 1 in 10<sup>9</sup>, respectively

- 3) Cheap transmission media such as twisted pair or coaxial cable

- 4) Simple addressing and routing of data formed into packets

Local area networks, also known as local networks or LANs, enable large numbers of digital devices (usually computers) to be connected together. The devices are able to communicate with each other at high data rates and with little delay. The area covered might be anything from a single room to a university campus stretching over several miles.

## **1.1 THESIS AIMS**

The aim of this thesis is to describe the design of a new high speed local network, the Cambridge Fast Ring, which is being developed at the Computer Laboratory in the University of Cambridge. Having decided to undertake such a project, there are two approaches that may be adopted. One is to take an existing design and re-work it to function faster, the other is to start an entirely new design. The former method is likely to be easier and faster in implementation, whilst the second involves a great deal of research, but gives the opportunity to improve on current designs.

The design which is presented in this thesis falls between these two approaches. The new network borrows heavily from the Cambridge Ring, also developed in the Computer Laboratory, but has many new features added as a result of experience with the Cambridge Ring and other networks. The thesis attempts to describe the ideas which resulted in the new design and the ways in which the design can be exploited in the construction of computer networks.

#### 1.1.1 Outline

The remainder of this chapter describes some of the uses to which local networks are currently put and speculates on possible uses for faster networks. Chapter 2 gives an outline of several local networks developed over the last decade and is intended to give some idea of the way these designs have evolved as a result of advances in technology and experience with earlier designs. Chapter 3 describes a particular implementation of a local network and the environment in which it is used. Some measurements of traffic patterns and network load made on this network are given.

Chapter 4 presents some of the major issues which were considered in the design of the Cambridge Fast Ring and in Chapter 5 an early version of this system is described. Problems with the implementation of this version gave the opportunity for a redesign and Chapter 6 describes the Cambridge Fast Ring in its present form.

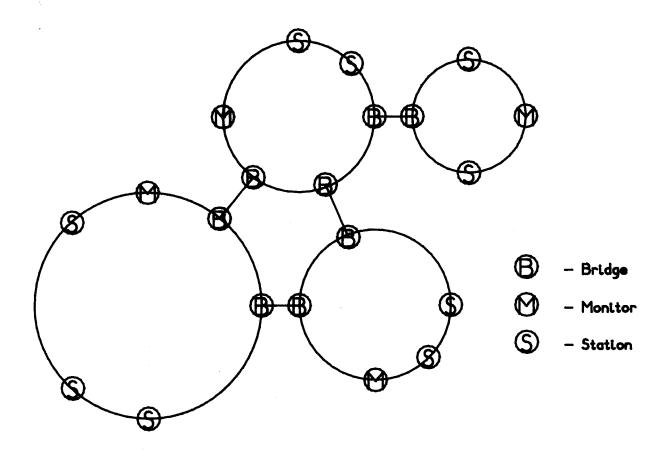

Chapter 7 discusses the use of bridges. A bridge is a means of connecting Cambridge Fast Rings together to make more complex networks. Chapters 8 and 9 consider the design of protocols and network interfaces which are necessary to make a computer network from the Cambridge Fast Ring. Finally, Chapter 10 summarises the work done and gives some ideas for further, related work.

#### 1.1.2 Acknowledgement

The designs for the Cambridge Fast Ring, presented in Chapters 5 and 6, are the result of the joint efforts of A. Hopper, R.M. Needham and the author. The author is responsible for all other discussion, for the study in Chapter 3 and for the designs described in Chapters 7, 8 and 9.

## **1.2 USES OF LOCAL AREA NETWORKS**

Many applications have been found for local area networks and they are widely used in computer systems in commercial and academic environments. In industry they are used for process control and, more recently, have been applied in office automation applications.

#### 1.2.1 Resource Sharing

The first local networks were designed with resource sharing in mind and today this is still one of their major uses. Traditional time shared computer systems consist of a processor unit, a printer, a disc store, a magnetic tape unit and a number of terminals. Many users may use the processor and peripherals on a time slicing basis. In order to use a second computer nearby, a user must get up and go to another terminal attached to that computer. This second computer will require a similar complement of peripherals and it is desirable to be able to share peripherals between computers, not least for economic reasons. Past methods of sharing one set of peripherals between many computers have been complex and costly, with little scope for expansion.

Connecting the two computers and a single set of peripherals to a local network is an effective strategy and has a number of advantages. Since each user's terminal is connected to the network, it may communicate with both processors. Also, only one printer and tape unit are required, assuming that they can cope with the load imposed on them, and the disc stores may be shared by all users. Functions such as an electronic mail mechanism common to all users of the systems are now possible. However, the security of each system is now possibly reduced and some means of authenticating network operations may be required.

The last ten years have seen a substantial fall in the cost of semiconductor products, particularly microprocessors and memories. The price of mechanical peripherals has remained much the same in absolute terms and risen considerably relative to semiconductor based products. The fall in processor prices has led to the emergence of the personal computer, a single user computer with a processing power comparable to the normal "slice" of a time shared system. There is a trend towards using these personal computers, which may incorporate a visual display unit and keyboard and yet be no larger than a conventional computer terminal.

The relative cost of peripherals is high and it is sensible to share them using a local network. The personal machines may have a small disc store but even so a large, reliable file store on the network is very useful for dependable storage and shared access to files. This file store is commonly called a **file server** and is made up of a number of disc stores, controlled and connected to the network by a dedicated computer. There may be several of these file servers on the network and more can be added should the need arise. Simpler peripherals, such as a line printer, require little

processing power in the computer which connects them to the network and a microprocessor is normally sufficient.

The cost of attaching devices to a network may well be a factor in deciding whether to employ one. If connection costs are high then the benefits must also be high to justify the purchase. The cost will be split between cabling, the network interface hardware and the software needed to enable communications. The cost of cabling will vary widely according to the installation and software costs are also difficult to assess. Current hardware costs are around one thousand pounds per connection for Ethernet or Cambridge Ring networks [Lee-R 83].

The cost of network hardware will fall when the necessary functions can be implemented by dedicated integrated circuits. Costs should then fall by a factor of ten or more for that particular part of the network. Software costs will remain the same unless the network hardware reduces the amount or complexity of software.

#### **1.2.2 Distributed Computer Systems**

The falling cost of processors and memory means that the CPU cycles of a mainframe can be obtained from a number of microcomputers at significantly lower cost. By connecting many of these computers to a network and giving one to each user, we achieve the power of the mainframe but with some additional advantages (and disadvantages). Reliability will be increased since failure of one of the processors is unlikely to affect the operation of the others. Failure of the network or some other essential part of the system is still a potential problem. However, systems in use for some years have shown the reliability of the local networks employed to be quite adequate for resource sharing and distributed computing applications [Binns 82].

The performance of a computer in this environment will be independent of the number of users of the system provided any shared resources are not being heavily loaded. Some mainframe applications, such as dedicated use for numerical calculation, may not be feasible because it is not possible to split the problem up for execution by many smaller processors.

There are a number of possible implementations of a distributed system. The Cambridge Model Distributed System (CMDS) is a working experimental system which presently supports over 20 users [Needham 82]. The CMDS approach is to connect to the network a collection of processors, not necessarily all of the same type, and

allocate these to users who request them. Users have a terminal in their office which is connected to the network and so to the processors. The processors are kept together elsewhere, which has the advantage that maintenance is easy and the noise and heat that they produce can be suppressed more effectively than if they were in the user's office.

A user may request one or more processors of given types or ability. Separate processors are required to administer the resources of the network. The processors which perform these network administration functions are small dedicated microcomputers known as **servers**. There are also file servers and printing servers for storing data and providing hard copy output.

The system is able to provide all of the facilities of a time shared system, such as electronic mail, tape archiving and the sharing of programs and data, whilst being rather more flexible in terms of expansion and accommodating user's needs. Failure of one of the processors will not affect overall operation and failure of a server can be remedied by keeping spares on the network and relocating the server function in a working spare. This may take several minutes to do but is considerably faster than repairing or replacing a faulty part of a mainframe. In practice the simplicity of the processors and servers makes them highly reliable. The CMDS has been highly successful and currently has over 30 processors, five times more than at its inception. It seems possible that such systems may replace mainframe computers in certain applications.

#### **1.2.3 Office Automation**

Many of the traditional office activities, such as typing letters and documents, filing and accounting, are presently being performed by computers. Local networks can be used to advantage in this environment in many ways. A high quality printer can be shared by many word processing systems, internal memos can be sent using electronic mail and communication of information between departments is made easy. An interface to a public wide area network allows mail to be quickly sent all over the world from a person's desk.

Most large offices have an internal telephone system controlled by a Private Automatic Branch Exchange (PABX). This connects internal telephones and external lines, routing calls as requested. The number of lines may range from less than ten to over a thousand and typically a maximum of 10% of them may be in use at once. Local networks generally have sufficient bandwidth to carry digitised telephone conversations and the functions of the PABX may be performed by a local network with a computer to coordinate operations. With voice input and output for computers probable in the next few years, this integration of function will be a natural choice. The SILK local network, manufactured by Hasler, is an office local network which integrates voice and data traffic [Jackson 81].

Digitised voice is commonly sent at a data rate of 64KBit/S. Current local networks have overall bandwidths of around 4MBit/S and so 30 two-way conversations would saturate such systems. If some other forms of traffic are required on the network, then either the network must be made to go faster or the number of conversations must be reduced. The nature of the other traffic may be such that it interferes with the voice traffic, for example by delaying it. In this case a means of segregating the two traffic types so that they do not interfere with each other is desirable. Alternatively having sufficient bandwidth on the network to cope with all demands will be satisfactory.

#### **1.2.4 Other Applications**

Local networks are used to advantage in many process control applications. An industrial site may range in size from 100m to 10km and communication is usually necessary between devices all over the site. Local networks are a cost effective way of integrating the many wiring paths which are required. The requirements of this application are rather different to previous examples, data rates tend to be lower but delay is often critical and reliability crucial. Failure to turn on a valve or to coordinate two related processes may be disastrous. The ability of local networks to combine the functions of remote control, site-wide communication and statistical and other data gathering operations, onto a single wire, makes them highly suited to this work. Some local networks can use fibre-optic links and these can be of use in electrically noisy environments.

An example of local network use in an industrial application is in controlling robots on a production line. The robots need complex sequences of commands and the actions of all the robots must be carefully coordinated. A local network is used to connect the robots to their controlling computer and this greatly reduces the wiring costs involved.

On a much smaller scale an Ethernet local network, implemented as a single integrated circuit, has been used to connect circuit boards together inside a photocopier. The low cost of the chip means that this approach is cheaper and more reliable than routing a loom of wires between the various boards.

#### 1.2.5 Applications for a Faster Network

The ability of computers to present data in graphical form is used to advantage in many applications. Many computing environments could employ a network which could carry a mixture of voice, data and real-time graphical information. Many personal computers have high resolution, bit-mapped screens and performing rapid updates to these across a network requires a large bandwidth. A very fast network could support a small number of true video transmissions or a larger number of less demanding real-time image transfers such as run-length encoded pictures. A monochrome video signal can be transmitted in digital form at a rate of 9.6MBit/S and with data compression this might reduce to less than half. Networks to support video data will need to allow data to be transmitted at these rates and ideally the overall capacity should be such that several video transmissions may occur and still leave room for other data transmissions.

A number of present applications are limited by network bandwidth, particularly bulk data transfers from fast storage devices such as disc stores. Discs are now available with transfer rates of over 10MBit/S and implementation of a virtual storage system over a local network with discs such as these could not be contemplated with currently available networks.

Faster networks will allow existing applications to grow in size and speed and will also generate new applications. Parallel processing, in which computations are split up and assigned to many processors running simultaneously, demands very rapid transfers of data and results between processors. These systems presently use circuit switching techniques for routing data between processors, a high speed local network could equally well be employed.

Many present network applications are limited in speed not by the network, but by the software which drives it. Protocols are necessary to enforce an orderly flow of data between machines on the network and these protocols are generally implemented as computer programs. The speed at which these programs run and the rate at which they can move data to and from the network are the limiting factors in many network applications. Faster networks will only be useful if the protocols and data transfers can also be speeded up. This may be achieved by simplifying the protocol where possible and by speeding up its execution. For very fast networks the latter may have to be done by implementation in hardware.

#### Chapter 2

# LOCAL AREA NETWORKS

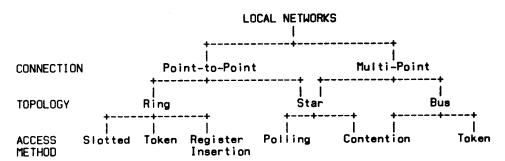

The first LAN to be constructed was probably that of Farmer and Newhall [Farmer 69] and since then over 100 LANs have been documented. When comparing LANs there are three main parameters to consider. First, the topology of the network is significant. To date most LANs have used simple topologies such as a ring or a tree. The second parameter is the protocol by which devices attached to the network gain access to it and communicate with each other. Access must be arbitrated since several devices may wish to use the transmission medium simultaneously. The final parameter is the transmission medium itself. This will have a characteristic speed and error rate and may be a fibre optic system or one of several wire systems. Some distinctive modulation and clocking scheme will be employed. The following diagram illustrates the way in which some common types of local networks are related to each other.

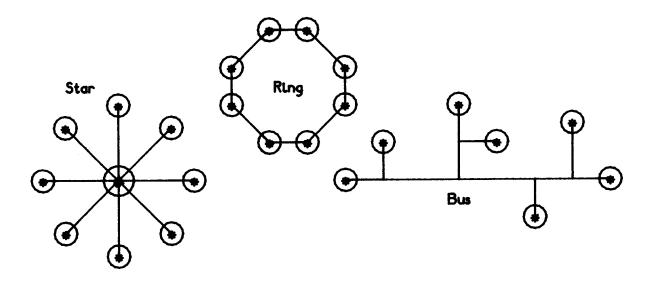

A multi-point connection scheme is one in which the signals sent by one station are seen by all others as they are transmitted. A station is the hardware which connects a device to the network and allows it to transmit and receive data. In a point-to-point system the signals are passed from station to station and only one station sees each bit at a given time. At present fibre-optic cables can only be used in point-to-point systems. Some of the topologies used for local networks are illustrated in Figure 2.0a.

## 2.1 PIERCE LOOP

Pierce postulated a loop network based on the slotted ring principle of operation [Pierce 72]. In this scheme a number of fixed length frames or **slots** (collections of bits) circulate round a loop of wire, the signals being regenerated at intervals. The

Figure 2.0a Local network topologies

slots are stored in the delay in the wire and in the nodes which are attached to the loop. The number of slots is thus determined by the length of wire in the loop and by the number of nodes. Each slot has a bit near the front to indicate whether it is full (carrying data) or empty. Devices connected to the loop are assigned addresses which are hard wired in the node and the slot contains two fields for addresses, one for the sender of the data (the source) and one for the recipient (the destination). The remainder of the slot is available to carry a message (data) between the source and destination.

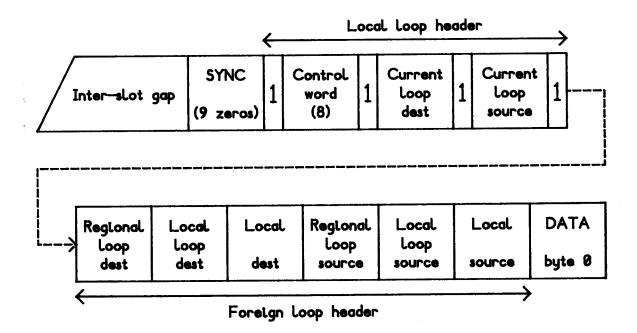

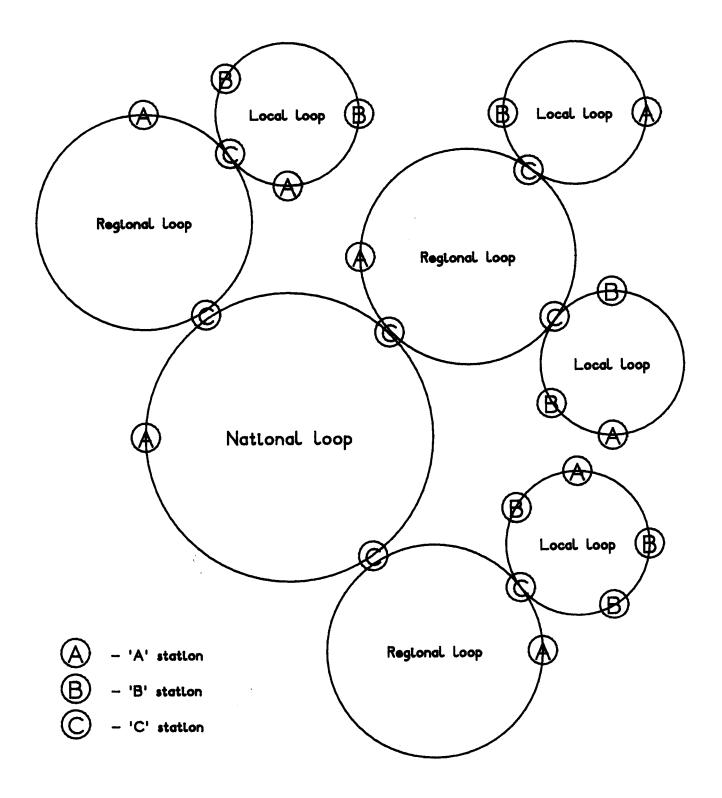

Pierce envisaged a three level hierarchy of such loops, with a single national loop serving an entire country and connected to many regional loops. Each regional loop was then connected to many local loops, each of which served a small area of a few square miles. Such a system was never realised but a single loop was constructed by Kropfl [Kropfl 72] and subsequently used by Croker [Croker 72]. Only the local loops conform to our present notion of a local network. The format of the Pierce slot is shown in Figure 2.1a.

The sync field ensures that loop interfaces align to the bit sequence of the packet correctly and the control field contains the full marker as well as some other administrative information. When used in the hierarchical arrangement further addressing information is placed in the slot after the local addresses.

Figure 2.1a Format of a slot on the Pierce loop

A Pierce loop has three types of "station" attached to it. Each loop requires a single **A-station** to initialise and maintain the slot structure. This station also removes full slots which were not claimed by their destination. Host devices, such as computers, interface to the loop via **B-stations** and finally, **C-stations** connect local to regional and regional to national loops. No C-stations were ever implemented. The arrangement of local, regional and national loops is illustrated in Figure 2.1b.

When a B-station has some data to transmit it waits for an empty slot to pass and places the data and destination address in the appropriate fields of the slot. The source address is wired into the B-station and is inserted automatically. The slot then travels around the loop being relayed and observed at each B-station. When a B-station recognises the destination address as its own and has sufficient buffer space, it copies the data and marks the slot empty. Each B-station must therefore buffer the slot at least as far as the destination address in order to be able to mark it empty. This means that in small loops most of the bits on the loop will be stored in the B-stations rather than on the wire.

Figure 2.1b Local, regional and national Pierce loops

When a full slot passes the A-station it is marked as such using another (monitor) bit in the control field. If a full slot enters the A-station with the monitor bit marked then this must be the second time it has done so and this implies that no B-station could receive the slot. This may have been because the address was invalid or the destination could not buffer the message. The A-station swaps the address fields of such slots so that the message is sent back to its source to indicate that something was wrong. The slot is also marked to show that this has occurred so that if the slot is not now received then the A-station will mark it empty when it next passes. This prevents full slots circulating indefinitely.

The Kropfl implementation of the Pierce loop used the Bell T1 modulation scheme for the data on the loop and operated with a clocking speed of 1.544MHz. A characteristic of this scheme is that each byte of data sent is accompanied by an extra bit (a one) to ensure that clock recovery can occur. The slots were 522 bits long and contained 432 bits (54 bytes) of user data. The addresses used in the loop were 8 bits long thus allowing up to 256 B-stations per loop. Pierce's addressing scheme for regional and national loops allowed 8 bits each for local and regional loop numbers thus allowing a maximum of  $2^{24}$  hosts on the network.

In the very long loops which Pierce proposed, the slotted approach had significant advantages over other network architectures in that many messages could be in flight simultaneously. Most LANs only allow one message to be in transit at once, which can result in a significant loss of bandwidth in larger configurations. Another significant point about loops in general is that they are vulnerable to cable breaks and failure of any circuitry in the loop signal path. Pierce suggested making duplicate loops with automatic switching of stations to the other loop when the primary loop failed. Slotted loops are also dependent on the correct functioning of the A-station, Pierce had no suggestions of what to do in the case of A-station malfunction.

## **2.2 ETHERNET**

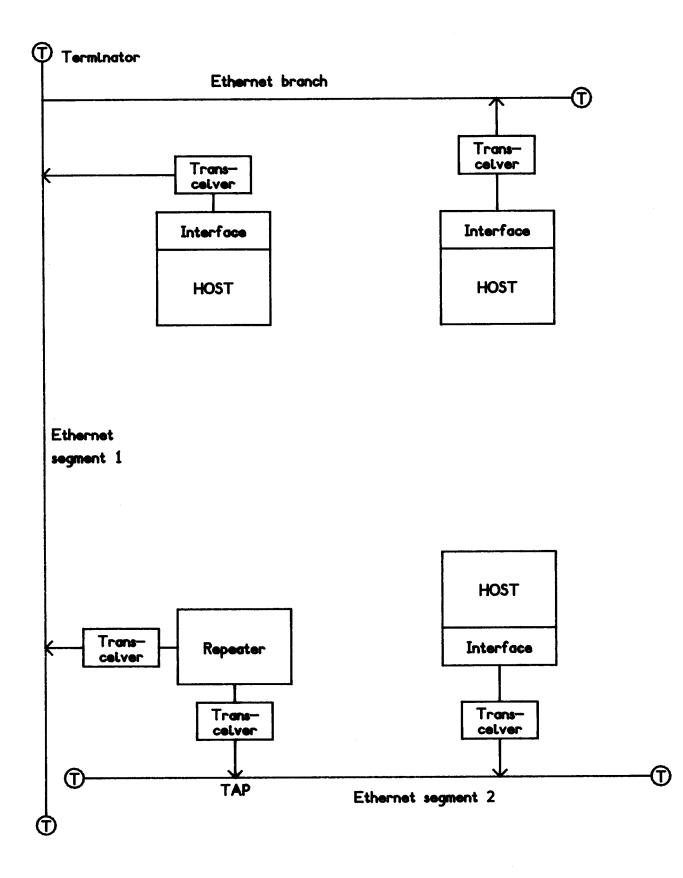

The Ethernet, developed at Xerox PARC by Boggs and Metcalfe [Metcalfe 76] is a LAN based on rather different principles to the Pierce loop. Its topology is that of a branching non-rooted tree and data is transmitted in packets of variable length. The transmission medium is a coaxial cable which, unlike a loop, is passive. This means that there are no signals present on the cable when the network is idle. There is no requirement for a network controller such as Pierce's A-station and access to the network is controlled by detecting the presence of someone else's message on the cable and delaying transmission until the network is idle. Hosts connect to the network via an Ethernet interface which incorporates a **transceiver** which "taps" the cable. Data is sent bit serially from the interface via the transceiver and so onto the cable. Packets sent in this way are broadcast all over the cable and heard by all active interfaces. Destination and source addresses (8 bits each) are present at the front of each packet and generally only one interface will recognise the destination address and receive the packet. The packet format is depicted in Figure 2.2a and an Ethernet configuration is shown in Figure 2.2b.

|        | ←    |      | Accessible by host  | •    |

|--------|------|------|---------------------|------|

| S      | Dest | Srce | Data                | CRC  |

| N<br>C | (8)  | (8)  | (0 to <b>4000</b> ) | (16) |

#### Figure 2.2a Format of an Ethernet packet

If an interface wishes to transmit, it first monitors the cable to see if anyone else is transmitting and if so waits until the transmission ceases. If no one else appears to be using the cable then the interface transmits and also listens to detect if some other interface started transmitting and thereby generated a collision on the cable. If a collision occurs both interfaces will detect it and immediately stop transmitting. Both will retransmit after an interval determined by observing the level of traffic prevailing and adding a random component. The interval is proportional to the frequency of collisions and this tends to reduce the load on the network when it is being heavily used.

This access method is called Carrier Sense Multiple Access with Collision Detection (CSMA/CD). The time during which a collision is possible is small in relation to the packet size, being the propagation delay of signals between the two furthest spaced interfaces. Thus if the first few bits of a packet are transmitted successfully then the whole packet will be.

Figure 2.2b A typical Ethernet configuration

The original Ethernet supported up to 256 interfaces on a network with a maximum span of 1km. It was clocked at 3MHz and packets could be up to 4000 bits long. This limit on the maximum length prevents one host hogging the network. The access method is such that it is not possible to guarantee access to the network in any finite time. A probability of access can be calculated, however, and in normal operation no problems arise because of this. It does mean that the use of Ethernets is restricted in certain real-time applications.

In common with many LANs the Ethernet has a broadcast facility. Using this a single packet can be transmitted which may be received by all hosts on the network. The Ethernet does this by having a special destination address for the purpose and the facility has been used to advantage in some of the higher level Ethernet protocols.

Unlike a loop, an Ethernet cannot be extended indefinitely since each transceiver must be capable of driving the entire network, rather than just the next loop link. Ethernets may be extended in terms of size by means of packet repeaters which link two Ethernet segments and amplify signals passing through them in either direction. This makes the network active however and reduces the performance somewhat. Extending the addressing range to accommodate more hosts can be accomplished in much the same manner as proposed by Pierce and this has been successfully done for the Ethernet by means of packet gateways and a suitable addressing scheme [Boggs 80].

Recently a new version of Ethernet, supported by a number of computer manufacturers, has emerged. This runs at 10MHz and has 48 bit addresses which are thought to be enough for world-wide use. This is an attempt to bring Ethernet in line with a proposed standard for local area networks.

#### **2.3 CAMBRIDGE RING**

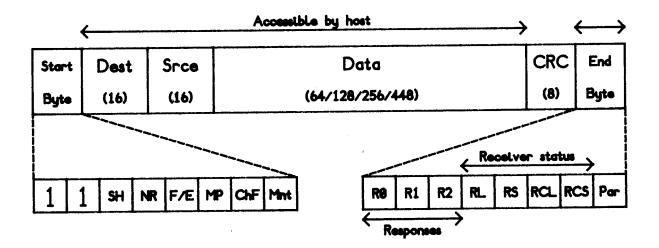

The Cambridge Ring (CR) is a slotted ring similar to the Pierce loop. It was developed by Wilkes, Wheeler and Hopper at the Computer Laboratory in Cambridge in the mid 1970's [Wilkes 79]. The slots of the CR are called **minipackets** and are somewhat smaller than either the Ethernet packets or Pierce's slots. The minipacket is 38 bits long and in addition to control bits contains two 8 bit address fields and 16 bits of data as shown in Figure 2.3a.

| Accessible by host |   |   |      |      |      | $\longrightarrow$ |   |        |

|--------------------|---|---|------|------|------|-------------------|---|--------|

| S                  | F | Μ | Dest | Srce | Data | R                 | R | Р      |

| O<br>P             | E | Р | (8)  | (8)  | (16) | 1                 | 2 | a<br>r |

Figure 2.3a Format of a Cambridge Ring minipacket

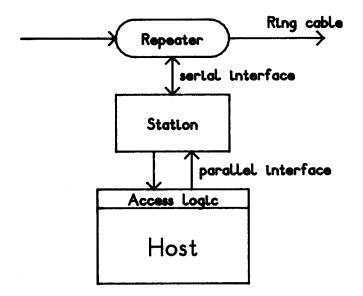

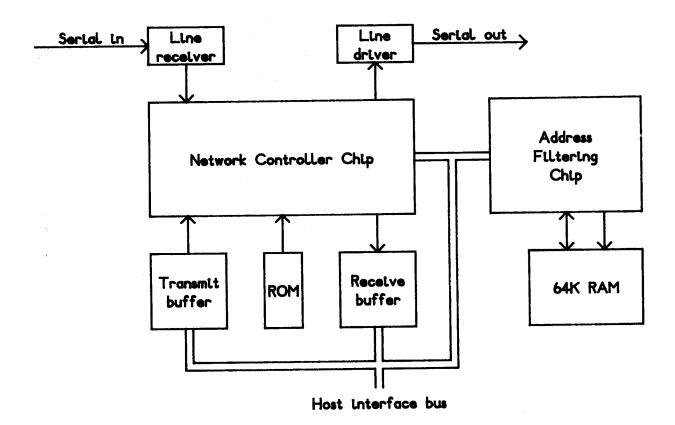

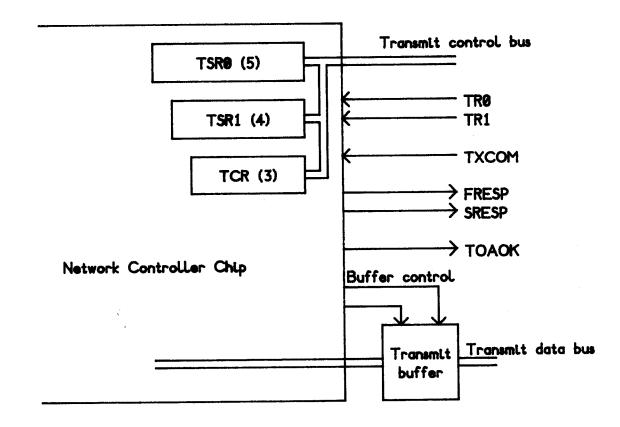

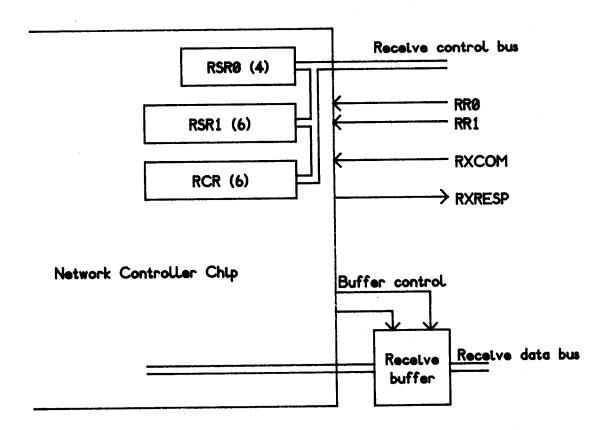

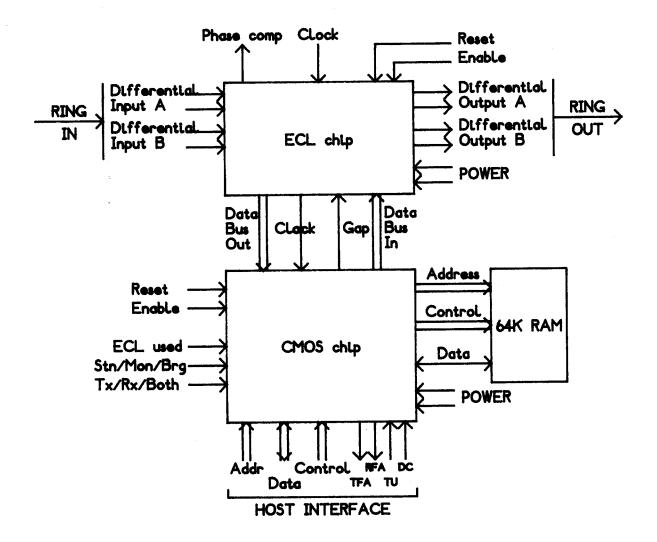

The minipackets form a head to tail train on the ring with the excess length of the ring containing a gap of zero bits. The CR has a monitor station which is comparable in function to Pierce's A-station and hosts interface to the ring via stations and repeaters. Repeaters regenerate the signals on the ring and also provide a serial interface to a station (Figure 2.3b).

#### Figure 2.3b Connection of a host to the Cambridge Ring

The transmission medium used on the CR is a dual twisted pair and a phase modulation scheme is used. This allows an overall clocking rate of 10MHz with each twisted pair carrying data at half of this speed. Fibre-optic links have also been used successfully in a Cambridge Ring. Stations contain minipacket buffers and control logic for interfacing to a host computer. Like the Pierce slot, each CR minipacket has a full/empty bit and a bit to indicate whether it has passed the monitor station while full. The minipacket also has control bits at the rear, two of which (the response bits) are marked by the destination station. When a minipacket is transmitted, it travels round the ring to its destination where it may or may not be received. Unlike the Pierce loop the slot is not marked empty at this point, but continues round the ring back to the source where it is marked empty. This has two major effects. First, hogging of the ring is prevented, since the transmitter is obliged to wait for the return of a minipacket before transmitting another. Second, the response bits at the back of the minipacket allow the destination to convey information back to the source without the cost of an explicit transmission. The price paid for this is that some bandwidth is wasted on the return path.

Another notable feature of the CR is the parity bit at the back of each minipacket. This is the parity of all previous bits in the minipacket and is tested and corrected at each active station. If it is found to be incorrect the station which detected the error transmits an error minipacket to an error logging station. Since the error minipacket will contain the address of the sending station, the source of the error can be localised to a single link. This has proved to be of value in detecting broken links and links with an abnormally high error rate. The monitor station co-operates in this continuous testing by placing random bits in empty packets which would otherwise contain zeros. The monitor station also checks for certain types of bit errors which could be fatal to the correct operation of the ring. An example of this is a corruption of the full/empty bit, if an empty minipacket is erroneously marked full it could circulate indefinitely, unable to be used by anybody.

A coding plug is used at each station to supply the station address and also the number of slots on the ring. Knowing the number of slots means that a source station can empty a returning minipacket without having to wait to see the source address field. The delay through a repeater and station can thus be kept small, being only 3 bits in present implementations.

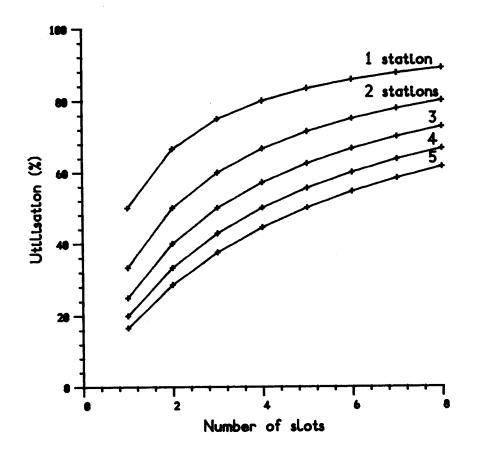

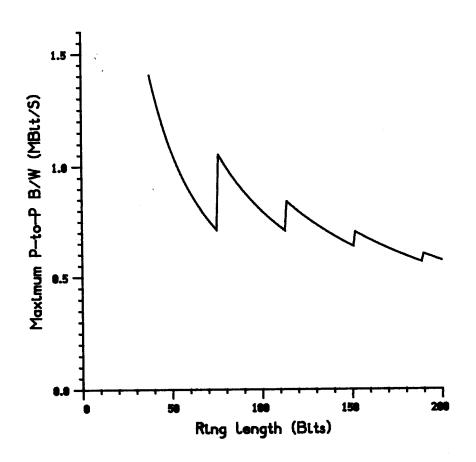

Although clocked at 10MHz, the CR slots contain much control and addressing information and just 4MBit/S is available to carry user data. Only part of this bandwidth is available on a point-to-point basis and one station sending data to another can only achieve 1.6MBit/S on a ring with a single slot. Because a station

must wait for a minipacket to pass round the ring before it can transmit again, the bandwidth at a station falls as the delay in the ring increases. This is made up of the wire delay and the delay in each repeater. Adding more stations and repeaters to a ring will therefore reduce the bandwidth available at all stations.

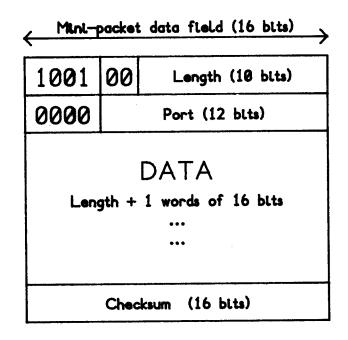

The small size of the minipacket means that some form of protocol is necessary to send messages of more than two bytes from one host to another. A protocol which is widely used on the Cambridge Ring to perform this function is the Basic Block Protocol [Walker 78]. This allows the transmission of up to 2048 data bytes along with a port number. The port number is used, for example, to address the data to a specific process or function within the destination host. The Basic Block is sent as a sequence of minipackets (Figure 2.3c), the first being a header containing the block length and the second containing the port number.

#### Figure 2.3c Structure of a Basic Block

Subsequent minipackets contain data up to the specified length and finally a minipacket containing the checksum of the data fields of all minipackets in the block is sent. The checksum provides a very strong check that all minipackets were delivered correctly, in particular that lost minipackets are detected. The very low error rate of the ring, typically 1 bit in  $10^{11}$  according to [Dallas 80], means that very few minipackets are delivered in a corrupt state.

In order to allow a host to concentrate entirely on minipackets from a given source, for example while receiving a Basic Block, each station contains a **Source Select Register** (SSR) which may be written by the host. When the SSR contains zero the station will reject all minipackets sent to it by marking the response bits **unselected**. When the register contains 255 (all ones) the station will accept minipackets from any address and when it contains a valid station address (1 through 254) it will accept minipackets from that station and reject all others. In an environment where the Basic Block Protocol is used the normal state of the SSR is such that the station will accept minipackets from anyone. When a valid header minipacket arrives the host will set the SSR to the source of the header and receive the rest of the block. If at any point the destination host decides that it does not want to receive the block, it will set its SSR to zero and the source will find its minipackets being rejected and cease transmitting.

The two response bits can be used to encode four states of the destination. One of these is unselected and another is **accepted**, meaning that the minipacket was successfully received. The third state is **busy** which means that the receive buffer of the destination was full and implies that the destination is slow in processing minipackets and that the current minipacket should be retransmitted. Thus a low level flow control system is effected by the busy response. The fourth state of the response bits is **ignored**. In this case the response bits return in the same state as that in which they were transmitted, implying that the destination is switched off or non-existent.

Because the repeaters must be powered at all times for the ring to function, they must be powered independently of the host machines. Stations normally share the host's power supply and are isolated from the repeaters by a relay which is kept closed by the host supply. Power for the repeaters is carried in the ring cables and supplied by a number of co-operating supplies. Failure of one supply is not fatal, provided the remaining supplies can power all repeaters on the ring.

#### 2.1 MACROLAN

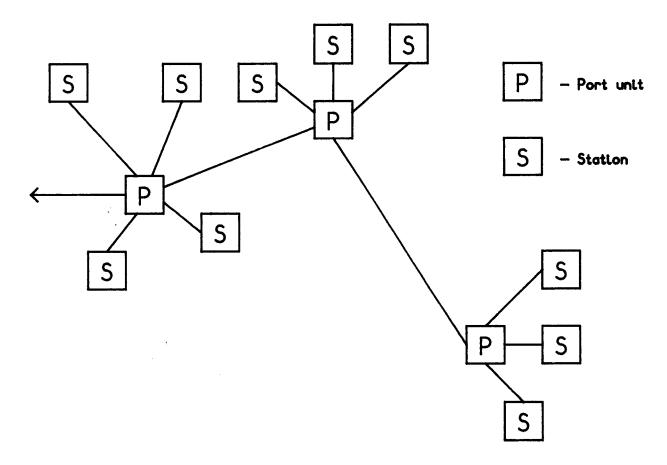

Macrolan is a recent development by ICL, its main aim being the efficient linking of peripherals and mainframe computers. It is a high speed network with a data rate of 50MBit/S [Stevens 83]. The topology is an interconnection of stars; hosts connect to stations which then connect via a bidirectional link to a star switching unit or port

unit. Port units may also connect to other port units in the same way that they connect to stations (Figure 2.4a).

Figure 2.4a Structure of the Macrolan network

Access to the network is by means of a token character (bit sequence) which is passed between stations by the port units. When a port unit is passed the token or "go ahead" character (GA) on one of its links, it sends it back down the next link in sequence. In this way the GA character will eventually reach a station and give it the opportunity to transmit.

When a station receives a GA character it will immediately send it back to the port unit if it does not wish to transmit. The GA will pass from station to station until one of them wishes to transmit. When a station wants to transmit a message and has the GA character, it sends a "start of frame" character (SOF) to the port unit followed by the message. The port unit recognises the SOF character and broadcasts it and the message on all its links. The message thus reaches all parts of the network and a further facility is provided whereby a message may specify that an acknowledgement is required. In this case the receiving station sends an acknowledge character (AK) back to its port unit, which then sends it back down the link on which the message arrived. All port units do likewise and the AK is thus routed back to the source station. When the transmission is complete the source station sends a GA character back to its port unit which continues passing it to its other links.

One of the major points of interest in Macrolan is its implementation. The networks discussed so far have generally been constructed from "off the shelf" small and medium scale integrated circuits (SSI and MSI) and used conventional metal conductor transmission techniques. Macrolan has been implemented in large scale integrated circuits (LSI) and uses fibre-optic connections for the station to port unit links.

At present 50MBit/S is the maximum rate that can be achieved by inexpensive fibre-optic systems such as the Plessey HRCL system [Sumerling 82]. This rate is well within the capabilities of the Emitter Coupled Logic (ECL) from which the port unit is constructed. The port unit is implemented as three uncommitted logic arrays (ULA) and has a complexity of around 1200 gates. It provides for six links to stations or other port units.

The station is also constructed using a ULA to perform the majority of its functions, which include framing, bit stuffing and error detection. The advantages of this method of implementation are many. Cost is reduced significantly by reducing component count and construction costs. Simpler power supplies are required, since the power consumption is low. Reliability is enhanced, primarily because the hardware is much simpler than it would otherwise be using conventional techniques. The fibre-optic cables are light and easy to lay and provide a significant improvement when links must pass through electrically noisy areas.

#### **2.5 IBM TOKEN RING**

The IBM token ring [Bux 82] is based on the token passing principle also used in Macrolan. Access to the ring is gained by taking possession of a token which circulates around the ring. Having obtained the token, the transmitter sends its message round the ring, replacing the token when it returns. The token then continues round the ring giving each station an opportunity to transmit. This method of working, where stations transmit on a strictly round robin basis, is termed asynchronous transmission. The IBM token is a collection of several bits, one of which

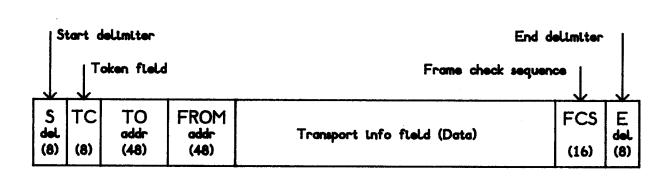

indicates whether the token is in use. The other bits are used to detect failures of the monitor node and to provide for different transmission methods. Data is transmitted in frames with the token at the start of the frame (Figure 2.5a).

Figure 2.5a Format of an IBM token ring frame

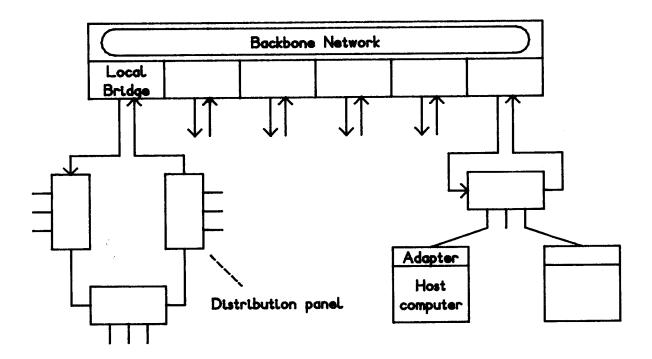

The token and message frames are transmitted on the same cables and must be clearly distinguishable. The IBM ring uses violations of the line coding scheme to indicate the arrival of the token field. The ring is clocked at 4MHz and is part of a two level network which consists of many rings connected together by a high speed backbone network (Figure 2.5b).

Early versions of the ring employed 32 bit addresses, but the latest version uses 48 bits to bring it in line with various proposed LAN standards. Of the 48 bits, 16 are used to address a single ring on the network and the remaining 32 identify a single host on that ring.

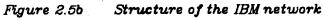

One of the major aspects of the design is its reliability. The configuration is a ring, but organised as a linked series of distribution panels with several arms radiating from each panel to ring adapters, which provide the host interface to the network (Figure 2.5c).

Figure 2.5c Connection of a host to the IBM ring

The distribution panel contains bypass relays to allow isolation of any host and when a host is isolated the relay loops the adapter's output back to its input so that self testing of the adapter link is possible. There is circuitry in each ring adapter to detect malfunction and hence operate the bypass relay.

Another aspect of reliability is ensuring the validity of the token. Normally there should only be one token on the ring but errors could remove it altogether or create several tokens. In previous token ring implementations a single dedicated monitor station checks for such errors and performs correction. The IBM ring takes a slightly different approach in that all ring adapters contain circuitry to perform the monitor function but only one is actually active at any time. The passive monitors check the operation of the active monitor and in the event of its failure arbitrate amongst themselves to choose a new active monitor.

Another prominent feature of the IBM ring is the inclusion of a second transmission method with different properties to the asynchronous one already described. This new method is termed **synchronous** and is a way of bypassing the potentially long wait for the arrival of the token.

Synchronous mode is intended for use in applications which have a strict access time requirement, such as might be found in digital telephony or other real-time applications. The monitor coordinates synchronous mode by periodically marking the token so that asynchronous transmitters will no longer attempt to use it and synchronous ones will. The marked token then leaves the monitor and the first synchronous adapter downstream of the monitor will use the token to transmit to a (synchronous) destination. The destination may place data in the frame to give to the source and on its return the source passes the token on to the next synchronous adapter. Eventually the token will return to the monitor, which will mark it as being once again available for asynchronous use.

The backbone network is a store and forward system known as the **block switch**, whose purpose is the transfer of frames between rings. Frames are buffered in queues on and off the block switch and a method of queue jumping is provided for synchronous frames. An aggregate data capacity of over 100MBit/S is claimed for the block switch. Prototypes of the ring and block switch have been constructed and work is under way to integrate the ring adapters and other network logic onto LSI circuits.

# 2.3 PROTOCOLS AND STANDARDS

Most communication networks, no matter what their size or speed, can be usefully divided into a layered structure in which each layer provides a service to the next higher layer and is in turn dependent on the layer below. This simplifies the design of the networks and enables standardisation between networks by means of well defined interfaces to the various layers. This approach has been applied by the International Standards Organisation (ISO) in producing the Reference Model of Open Systems Interconnection. This is described in [Zimmerman 80] and consists of seven layers. The lowest layer is the Physical Layer and this defines the mechanical and electrical interface to a network. The next (second) layer is the Data Link Layer and its function is to provide an error free transmission method for a stream of data. It will generally do this by dividing the data up into "frames" and having the destination acknowledge the arrival of frames.

The third layer is the Network Layer and this controls the sending of "packets" of data across the network. Messages passed down to this layer will be split into packets and routed to their destination. The fourth layer is the Transport Layer. This is responsible for transferring messages between hosts in an efficient manner and is the layer at which a network independent interface becomes possible. The topics discussed in this thesis correspond mostly to these lower layers, particularly the Physical and Data Link Layers. The higher layers (Session, Presentation and Application) are the user's interface to the network and are beyond the scope of this thesis.

Taking the Cambridge Ring as an example, the Physical Layer is the ring cable and modulation system. The Data Link Layer is formed by the minipacket transmission system and the Network Layer by the Basic Block Protocol. The Transport Layer is partially implemented by the Byte Stream Protocol [Johnson 80] and this has been enhanced to fully implement this layer as the Transport Service Byte Stream Protocol [Dallas 80].

The low bit error rates of LANs, their high bandwidth and low delay, mean that their protocols are somewhat different to those of earlier wide area networks such as ARPANET, which were generally based on slow telephone lines. The likelihood of error is much less and the cost and time of retransmitting a packet is small. Therefore the protocols can be simpler, performing error correction by retransmission rather than by redundant coding techniques.

The simple topologies of LANs means that there is generally only one route which data may take from source to destination. This means that packets will never arrive out of sequence, though they can still be lost on the way. Flow control can also be simplified in LANs. The low transmission delay means that it is frequently possible to send an acknowledgement for each packet sent. This arrangement would slow many larger networks considerably.

### LAN Standards

In the past few years several committees have attempted to define standards for local area network implementations. In the USA the IEEE is the major force while in Europe ECMA has been the most active organisation. In the UK a definition of a standard Cambridge Ring, known as CR82 [JNT 82], has been prepared by the Joint Network Team. The ECMA standard overlaps the IEEE standard in places, in particular the IBM token ring and 10MHz Ethernet are acceptable to both. Overall, the emerging standard seems to be that set down by the IEEE, although even that is incomplete at the time of writing [Nelson 83].

The IEEE Local Networks Standard Committee was formed in 1980 to work on IEEE Project 802 whose aims are to provide a set of standards for LANs, from the wire level up to protocols for interconnecting local area networks. The IEEE approach is to define a layered system of standards, using the ISO model, in which the transmission medium, the topology and the distance of interconnection are all independent.

Initially the project favoured only a single LAN implementation based on the 10MHz Ethernet. This was proposed by a combination of the DEC, Intel and Xerox Corporations and known as the DIX Ethernet. This came close to being the adopted standard until it was pointed out that Ethernets were weak in certain areas, particularly real-time applications where access to the network must be obtained within a fixed time. As a result of this the project adopted two other network types as part of the standard. One of these is a token ring very similar to that of IBM and the other is a token bus. The token bus has a topology like that of Ethernet but with access controlled by passing a token between the network interfaces. The busses can use broadband or baseband signalling and all systems employ 48 bit addresses. The addressing is such that an individual host, a small group of hosts, or all hosts may be specified by a single address. The two token systems specify a priority function to give certain transmissions precedence over others.

The present status is that Project 802 has divided into a number of sub-groups each with responsibility for one of the systems or some other specific area. One group (802.6) is looking at metropolitan area networks which have a somewhat greater size than LANs and might cover a small town.

#### 2.7 SUMMARY

While the networks described in this chapter are but a small cross section of the many LANs which have been built, they illustrate a number of general points. The Pierce Loop is interesting because it was an ambitious design which satisfied the need for a local network for resource sharing, but was expandable, using facilities explicitly included in the design, into a very large network. Later LANs, like the Cambridge Ring and Ethernet, were simpler and did not allow for network expansion. Recently, however, the need to expand and interconnect local networks to increase their geographic range has become apparent. The mechanisms to do this were not designed into the Cambridge Ring or Ethernet and the interconnection of these networks, in particular the addressing of packets, is performed by software. The IBM token ring and the local network described later in this thesis allow the connection of many small networks to make a larger one, by means of facilities provided in their hardware.

The methods of implementing local networks have also evolved over the years. Early networks were generally constructed with small and medium scale integrated circuits. The demand for networks has increased and it is no longer appropriate to use such methods to build network hardware which will be duplicated many thousands of times. The initial implementations of the Cambridge Ring and Ethernet were done in this way and later they were re-implemented using LSI techniques. More recent networks such as Macrolan have been designed for direct implementation in LSI.

Local networks can carry a wide range of traffic types and some are designed with a particular type in mind, or to cope with a variety of types. Macrolan was designed primarily for the interconnection of mainframe computers and disc stores. The IBM ring provides two types of transmission method, one of which provides a guaranteed access time and is particularly suited to real time applications. The network described in this thesis incorporates a similar mechanism whereby a transmitter can send data at a guaranteed rate, regardless of other traffic on the network.

Standards are emerging for local networks. The method of standardisation is that an existing network is examined in detail and then, with only minor changes, declared to be a standard. The standard is therefore only of use in constructing copies of that particular network. This is very useful but provides little guidance for the designer of a new network.

#### **Chapter 3**

# A CASE STUDY OF A CAMBRIDGE RING

This chapter details a study made on a particular implementation of the Cambridge Ring. The ring is used to support an experimental distributed computer system. This is reflected by the traffic patterns and performance characteristics observed. While other distributed systems might offer a similar load to the network, other types of application may present a significantly different load. A comparison with another distributed system based around an Ethernet is made later in the chapter.

# **3.1 THE TEST ENVIRONMENT**

The system outlined below is the Cambridge Model Distributed System (CMDS) [Needham 82]. The CMDS is based around a pool of single user minicomputers known as the Processor Bank. These machines are allocated to users for the duration of an online session by a server called the Session Manager. A server is a (usually small) computer which is dedicated to a single function, such as name lookup or providing the date and time. The Processor Bank machines have a Cambridge Ring as their only peripheral and thus have no file store or terminal connected. A File Server provides a filing system for the Processor Bank machines via the ring. This is a dedicated minicomputer which interfaces a number of disc drives to the ring and provides a suitable set of primitive operations with which to implement a filing system. Terminals are connected via servers known as Terminal Concentrators, which connect up to 8 terminals to the ring. Another server is connected to a line printer and provides a printing service for machines on the ring.

Additionally, several other computers which are not part of the distributed system are connected to the ring for reasons of convenience. These include an IBM mainframe, an assortment of mini and microcomputers and the CAP computer which maintains a virtual storage system over the ring, using the File Server as secondary storage [Dellar 80]. A uniform set of protocols based on the Basic Block Protocol [Walker 78] is used throughout the system.

A typical session on the system proceeds as follows. The user at his terminal asks the Terminal Concentrator to connect him to the Session Manager and then asks the Session Manager to allocate one of the Processor Bank machines to him and load it with an operating system from the File Server. The Session Manager may well delegate some of these tasks to other servers but the user is unaware of this. When this is done (a few seconds) the user's terminal is connected via the ring to the allocated machine. The user then sees a conventional terminal session and can begin his dialogue with the operating system. The Terminal Concentrator allows several connections at once to a terminal and the filing system that the user how sees is located on the File Server. Thus, when the user compiles a program, the compiler and source file are read from the File Server and the resulting object code file is written back to the File Server. The response times for such operations are comparable to those experienced on a conventional time sharing system.

It is possible to identify some probable causes of traffic on the network. The File Server is likely to contribute heavily, since it supports filing systems for all users of the system and also supports the CAP's virtual store. The terminals and printer can be expected to receive more data than they produce and there will also be administrative data passing between servers and other machines.

# **3.2 THE MONITORING DEVICE**

The measurement of traffic on the ring may be approached in several ways. If we are interested in overall traffic patterns, such as the volume of data transmitted in a given time, then we must look at every minipacket which passes a given point on the ring. The time between the arrival of consecutive minipackets is less than 4uS. The operations which would have to be performed on a minipacket would take much longer than this using a conventional computer. A dedicated piece of hardware could perform the necessary manipulations much faster, but it could be quite complex.

We might also want to observe traffic at the Basic Block level, of interest are the number of blocks sent and their lengths and types when viewed as part of a higher level protocol. A number of methods for monitoring at the block level are suggested by Ody [Ody 80]. His "promiscuous station" method uses a ring station which is capable of receiving minipackets from any chosen source without marking the response bits. This method allows monitoring of blocks between a given pair of stations and imposes no extra load on the network which might upset the measurements.

An alternative method for monitoring blocks is to incorporate a facility in the software of each machine to send a logging minipacket to a logging device on the ring. Such minipackets would be sent at the start and end of a block and could provide information about the size of the block and its transmission time. This method will, of course, add traffic to the network, though hopefully an insignificant amount. A failing of both the above methods is that they do not allow inspection of the response bits of the constituent minipackets of a block and so are unable to correctly observe minipackets which are rejected and then retransmitted. Such information is of some importance in the design of ring interfaces.

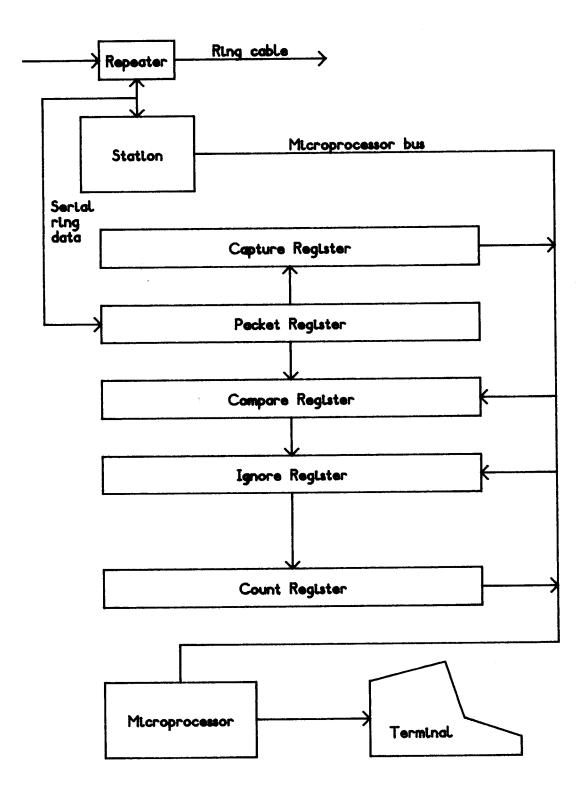

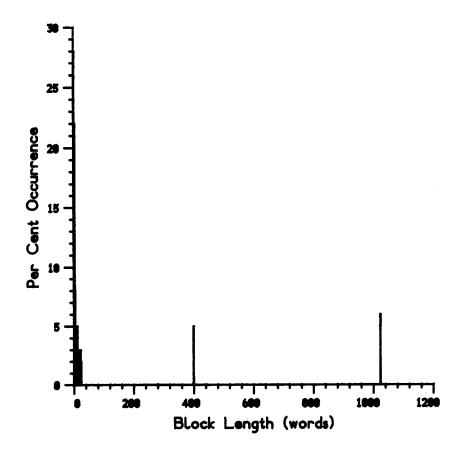

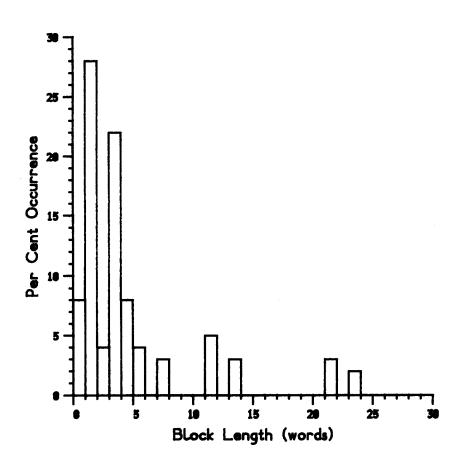

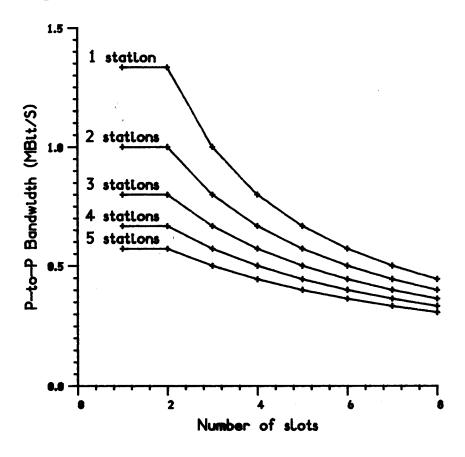

The approach taken in designing the monitoring device was to use hardware to speed up certain operations. A small computer was used to control this hardware and perform calculations on the measurements obtained from it. The device is capable of counting minipackets with chosen contents at full ring speed. It can be configured to work as a promiscuous station while also allowing inspection of the response bits. It is attached to the ring at a repeater and is readily moved around to monitor at different points on the ring.