Technical Report

Number 46

**Computer Laboratory**

# Intelligent network interfaces

Nicholas Henry Garnett

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

© Nicholas Henry Garnett

This technical report is based on a dissertation submitted May 1983 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Trinity College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# <u>Contents</u>

|    | Preface                                        | vii |

|----|------------------------------------------------|-----|

|    | Summary                                        | i×  |

| 1. | Introduct i on                                 | 1   |

|    | 1.1 Local Area Communication Networks          | 1   |

|    | 1.2 Network Interfaces                         | 2   |

|    | 1.3 Intelligent Network Interfaces             | 4   |

| /  | 1.4 Overview                                   | 6   |

|    | 1.5 Acknowledgements                           | 6   |

| 2. | Background                                     | 7   |

|    | 2.1 The Cambridge Ring                         | 7   |

|    | 2.1.1 Transmission                             | 8   |

|    | 2.1.2 Reception                                | 9   |

|    | 2.2 Protocols Used on the Cambridge Ring       | 9   |

|    | 2.2.1 Basic Block Protocol                     | 10  |

|    | 2.2.2 Single Shot Protocol                     | 12  |

|    | 2.2.3 Byte Stream Protocol                     | 12  |

|    | 2.3 The Cambridge Distributed Computing System | 15  |

|    | 2.3.1 Philosophy                               | 15  |

|    | 2.3.2 The Cambridge Distributed System         | 16  |

|    | 2.3.3 Implementation Details                   | 17  |

|    | 2.3.4 Processing Servers                       | 17  |

|    | 2.3.5 Processor Bank Management                | 17  |

|    | 2.3.6 The Nameserver                           | 19  |

|    | 2.3.7 The Cambridge Authentication System      | 19  |

|    | 2.3.8 The Fileserver                           | 19  |

|    | 2.3.9 The Filing Machine                       | 21  |

|    | 2.4 TRIPOS                                     | 21  |

| э. | The Type 2                                     | 25  |

|    | 3.1 Before the Type 2                          | 25  |

|    | 3.2 Hardware                                   | 26  |

|    | 3.3 Design                                     | 27  |

|    | 3.3.1 Requirements                             | 27  |

|    | 3.3.2 Host Commands                            | 28  |

|    | 3.3.3 Buffer Chaining                          | 30  |

|    | 3.3.4 The Ring Interface                       | 33  |

•

1

|    | 3.3.4.1 Loading                               | 33 |

|----|-----------------------------------------------|----|

|    | 3.3.4.2 Debugging                             | 33 |

|    | 3.3.4.3 Protection and Authentication         | 35 |

|    | 3.4 Implementation                            | 36 |

|    | 3.5 Performance Measurements                  | 39 |

|    | 3.6 Discussion and Conclusions                | 41 |

| 4. | The MACE                                      | 43 |

|    | 4.1 Hardware                                  | 43 |

|    | 4.2 Design                                    | 45 |

|    | 4.2.1 The Host Interface                      | 46 |

|    | 4.2.2 The Ring Interface                      | 47 |

| 1  | 4.3 Implementation                            | 47 |

|    | 4.4 Performance                               | 49 |

|    | 4.5 Conclusions                               | 49 |

| 5. | A High-Level Intelligent Interface            | 51 |

|    | 5.1 Introduction                              | 51 |

|    | 5.2 The Implementation of Protocols           | 52 |

|    | 5.2.1 Packet Protocols                        | 52 |

|    | 5.2.2 Connectionless Protocols                | 53 |

|    | 5.2.3 Virtual Circuit Protocols               | 55 |

|    | 5.2.4 Alternative Implementations             | 58 |

|    | 5.3 Systems Aspects                           | 60 |

|    | 5.4 Conclusions                               | 61 |

| 6. | The Design of a High-Level Interface          | 63 |

|    | 6.1 Host Interface                            | 63 |

|    | 6.1.1 Inter-Machine Communication             | 63 |

|    | 6.1.2 Replacing the Ring Handler              | 64 |

|    | 6.1.3 Single Shot Protocol                    | 65 |

|    | 6.1.4 Naming and Addressing                   | 66 |

|    | 6.1.5 Byte Stream Protocol                    | 69 |

|    | 6.2 The Ring Interface                        | 73 |

| 7. | The Implementation of a High Level Interface  | 75 |

|    | 7.1 Modules and Tasks                         | 75 |

|    | 7.2 The Modules                               | 79 |

|    | 7.2.1 The Operating System                    | 79 |

|    | 7.3 The Ring Drivers                          | 81 |

|    | 7.3.1 The Protocol Handlers                   | 84 |

|    | 7.3.2 The Descriptor Module                   | 85 |

|    | 7.3.3 The Host Interface                      | 85 |

|    | 7.3.4 Miscellaneous Modules                   | 86 |

|    | 7.4 BSP and the Intelligent Interface         | 87 |

|    | 7.5 Host Software                             | 90 |

|    | 7.5.1 The Ring Device Driver and Handler Task | 90 |

|        | 7.5.2 The BSP Handler Task                    | 91  |

|--------|-----------------------------------------------|-----|

|        | 7.6 Performance                               | 92  |

|        | 7.6.1 Basic Block Performance                 | 92  |

|        | 7.6.2 SSP Performance                         | 92  |

|        | 7.6.3 BSP Performance                         | 93  |

|        | 7.6.4 Effects on the Host                     | 95  |

|        | 7.6.5 Inter-Machine Communication             | 97  |

|        | 7.7 Discussion and Conclusions                | 98  |

| , 8. H | Further Aspects of a High-Level Interface     | 101 |

|        | 8.1 Cambridge Specific Features               | 101 |

|        | 8.1.1 Resource Management                     | 101 |

|        | 8.1.2 Authentication                          | 103 |

|        | 8.1.3 Transport Service Compatability         | 104 |

|        | 8.2 The Hardware of a High Level Interface    | 105 |

|        | 8.3 Security and Encryption                   | 108 |

|        | 8.4 Customised NIPs                           | 111 |

|        | 8.5 The Use of Stable Storage in a NIP        | 112 |

| 9. 1   | Protocols and Closed Networks                 | 115 |

|        | 9.1 Protocols and the Intelligent Interface   | 115 |

|        | 9.1.1 Remote Procedure Call                   | 115 |

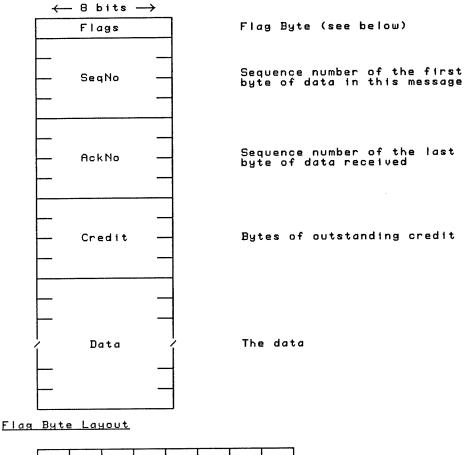

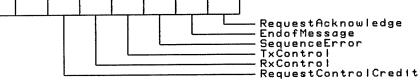

|        | 9.1.2 A Stream Protocol                       | 118 |

|        | 9.2 Closing the Network                       | 122 |

|        | 9.2.1 Protocols in the Closed Network         | 123 |

|        | 9.2.2 Network Capabilities                    | 124 |

|        | 9.2.2.1 Protocol Capabilities                 | 125 |

|        | 9.2.2.2 User Capabilities                     | 126 |

|        | 9.2.3 The Transmission of Capabilities        | 127 |

|        | 9.2.4 The Nameserver and Initial Capabilities | 128 |

|        | 9.2.5 Invalid Capabilities                    | 129 |

|        | 9.2.6 Authentication and Security             | 129 |

|        | 9.2.7 Systems Aspects                         | 130 |

| 10.    | Summary and Conclusions                       | 131 |

|        | References                                    |     |

. .....

1

# <u>Preface</u>

I wish to thank my supervisor, Professor R. M. Needham, for his help and encouragement. I would also like to acknowledge the members of the Systems Research Group for providing a pleasant environment in which to work.

During my research I was supported by a grant from the Science and Engineering Research Council; for which I am grateful.

Except where otherwise stated in the text, this dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration.

I hereby declare that this dissertation is not substantially the same as any I have submitted for a degree or diploma, or any other qualification at any other university. I further state that no part of this dissertation has already been, or is being currently submitted for any such degree, diploma or other qualification.

### Summary

Local Area Networks are now an accepted part of computing research. The technology of the network itself and the hardware to interface it to a computer is standard and in the cases of networks like ETHERNET and the Cambridge Ring is commercially available. The next level up from the hardware is the software interface between the Host computer and the network. This dissertation is concerned with one specific type of interface where the Host is not itself directly connected to the Network, but must access it via a second Network Interface Processor (NIP).

The dissertation begins by describing the design and implementation of two low level interfaces for the Cambridge Ring. The first of these, the Type 2, is machine independant and although based on a simple processor offers some sophisticated facilities to its Host. The second, SPECTRUM, is not so sophisticated, but is customized to interface to just one operating system. The difference between these two approaches is discussed.

We go on to introduce the High Level Interface, which removes all protocol and network related processing from the Host machine. This can benefit both the protocol implementation, by reducing system overheads, and the Host Operating System, by freeing CPU time for other tasks. This is particularly true in the case of time-shared machines which rely on the network for terminal connections. The design and implementation of such an interface are described.

The dissertation concludes by considering the possible roles of the NIP in the areas of security, protection, and reliability. Some thoughts are also given on the design of protocols which exploit the features of a NIP. Chapter 1

# Introduction

There has been, over the past few years, an increasing interest in computer networking. Indeed it has become not only an accepted part of computing systems research but now forms the major part of it. Computer networks may be divided into three classes: Wide Area Networks, Local Area Networks, and Multiprocessor systems. Wide Area Networks are the oldest of the three, finding examples in ARPANET [Heart70] and TYMNET [Tymes71]. Multiprocessors also have a long history, notable examples are: the CDC 6600 [Thornton70], HYDRA [Wulf74] and Cm\* [Fuller78, Jones79, Ousterhout79]. Local Area Networks are a relatively recent development and combine features of both these as well as having features uniquely their own.

# 1.1 Local Area Communication Networks

A Local Area Network (LAN) is one that connect computers, and other devices, within a radius of less than 5Km. This means that all the machines must be in the same building, or in closely adjacent ones. The closeness of this connection gives the LAN several important features. The first is that it is fast, with a point-to-point bandwidth measured in Megabits per second. The second is that its error rate is low, a figure of one bit error in  $10^{11}$  is typical. Local area networks may be divided into three groups based on their topology.

The first group is that of CSMA (Carrier Sense Multi-Access) bus networks. These consist of an un-rooted tree of cables forming a passive shared communication medium or ether. Stations are connected to this with taps at convenient points. Sources transmit data, encapsulated in addressed packets of several Kbits, only when they detect that the ether is idle. Since there is no central control it is possible that two sources will attempt to transmit at the same time. Collision detection, backoff and retry algorithms are implemented in the transmitting computers to handle this. Any packet transmitted on the ether propagates to all receivers; if a receiver recognises its address it copies the data into local memory. The best known example of this type of network is Ethernet [Metcalfe76].

The second group is that of Ring based networks. Here the stations are all connected sequentially to a looped medium. Since there is a distinct order to the nodes a distributed algorithm can be developed to share the medium without the collision/retry algorithms needed in a CSMA network. A packet from a transmitter passes in one direction around the ring until it is recognised by a receiver, which copies the data. The packet could be deleted here, but most ring networks exploit the topology to return an acknowledgement to the transmitter. Examples of ring systems are the Cambridge Ring [Wilkes79a], PRIMENET [Nelson78], and DCS [Farber75].

The final group of networks are those that do not fit into either of the above topologies, many of these apply wide area network technology to local areas and are either randomly configured or star shaped.

# 1.2 Network Interfaces

When interfacing a network to a Host computer there are many options open to the designer. The mechanism chosen is often dictated by the requirements of the Host computer, its operating system, or the characteristics of the underlying network.

At the most primitive level the network hardware can be connected directly to the Host and all aspects of network driving handled by the Host Operating System or client software. The suitability of this depends on the relative speeds of the network and Host processor, and the intended use of the network. At Cambridge examples of such interfaces may be found on the many ZBOs [Ody81a], a PDP11/45 [Gibbons80a], and a VAX11/750 [Collinson82]. In the first case the Z80 does little more than respond to requests sent via the Ring, so the primitive interface is adequate. In the other two cases the Ring is used infrequently enough for it not to have a detrimental effect. The disadvantage of this type of interface is that the real-time demands of the network may stop all other work during a network transaction.

One way to acquire faster processing, and therefore reduce the real time spent, is to move the network driving software into the processor's microcode. This can have the double advantage of speeding up the network transfers and reducing the load on the Host. The network is still being serviced, however, at the expense of Host programs. For example, the Alto Ethernet interface [Thacker79], uses 16% of the machine during data transfer, and can rise to 20% in the worst case. At Cambridge the CAP computer also has a micro-coded interface to the Ring. This approach assumes that the Host computer has an easily accessible micro-store, which is often only true if you have designed and built the machine yourself.

A significant improvement can be obtained if a modest amount of hardware is installed in the interface. The data transfer phase of the transaction can be handled automatically and access made via DMA. Since the Host processor is unlikely to use every memory cycle such an interface can have little or no effect on Host performance. Another important task that may be performed by hardware is the calculation of the checksum which most network protocols need. On a processor of modest performance this can take almost as long as the data transfer.

Local Area Networks share some characteristics with devices like discs: there may be a long delay before data is available, but when it is it comes at high speed and has associated real-time requirements. These attributes of discs are catered for by providing an intelligent, or semi-intelligent, controller. It makes sense, therefore, to use a similar approach to network access.

An interesting example of a semi-intelligent network interface may be found in the Local Network Interface (LNI) to the Distributed Computing System [Mockapetris77]. DCS is a ring network in which messages are addressed to processes rather than stations. This means that the LNI must contain an associative name table of all the process names in its Host. The destination address of any message seen passing on the ring is passed through this table and if it matches the data is copied. This is further complicated by the presence of a mask field in both the name table and the message; this allows messages to be broadcast to groups of processes selected by fields in the address. The LNI is a custom LSI chip that is controlled by an alterable Programmed Logic Array, it can therefore be considered a specialised micro-coded computer.

This dissertation is concerned with the class of truly intelligent network interfaces.

### 1.3 Intelligent Network Interfaces

An intelligent network interface is one that contains an easily programmed computer of some form. The concept of a Front-End network processor is not new and has been employed in Wide Area Networks for some time. Its role in these networks is usually to carry out message routing or maintain virtual circuits. The ideas have also been extended to Local Area Networks [Stack81]. These Front-End processors usually need to be substantial mini-computers, and are of comparable power to the type of machine we expect to comprise most of the Host processors on a LAN. The development of single chip microcomputers and their subsequent increase in performance now makes it possible to build a powerful processor that is both small (one PCB) and cheap (<{500}). It is therefore feasible to interface modest mini-computers, and even the larger micro-computers, to a network via their own Network Interface Processor (NIP).

The literature contains many examples of this: FordNet [Biba79], SWAN [Sommer81], CNET [West78], MITRENET [Hopkins81], WELNET [Mark81] and [Carpenter78]. These are all CSMA networks that use the NIP to implement the backoff/retry algorithm the network requires. All network access, including reception and transmission, is performed by the microprocessor with little hardware assistance, so data rates are limited to approximately 1 Mbit/second. Some of these are also limited by the Host/NIP connection, which is often no more spectacular than a serial line. A ring network similar to DCS but using a microprocessor in place of the LNI is described in [Lee78]. Most of these implement only the lowest protocol level; datagram or packet. Some do take advantage of the presence of the NIP to implement flow control and error detection using acknowledgement packets. This is on a node to node basis, not client to client, so it does not constitute a virtual circuit protocol. It was mentioned in the FordNet paper that they intended to implement higher level protocols in the NIP, but there appears to be no published evidence of this.

In most of the above cases the micro-processor node is an integral part of the network, and no other access method is supplied. In other cases the NIP has been used to make the network appear to be some other, more mundane device. An example of this is the Terminal Interface being developed at University College, London for the Cambridge Ring [Rubenstein81]. This is a Z80 based interface that supports a single character terminal protocol on the ring and presents the Host with an interface similar to a terminal multiplexor. Elsewhere on the ring another Z80 acts as a terminal concentrator and allows a terminal to be connected to any of several Host computers.

Of more interest is the Network Interface Processor that does not hide its true nature behind a pseudo-device interface but supplies explicit network access primitives to the Host. The prime requirement of such a device is that it does its job more efficiently than the Host could itself. Equally important is that the Host is not involved in as much work to use the NIP as it would be in driving the network directly. The first requirement may be met by using a fast processor or giving it special hardware support. The second requires that the NIP have direct access to the Host's memory so it can fetch both data and commands as it requires. Combining these two it is possible to develop hardware that can transfer data from network to Host and vice versa without the intervention of either processor.

The cost of a NIP is an important factor and can be assessed in relation to several criteria. The first, and most important, criterion is its cost compared with the Host machine it is to interface. If the cost of the NIP is more than that of the Host, or is a sizeable fraction of it, it is economically unfeasible to use it unless its advantages are great. Another comparison to be made is between the cost of the NIP and that of a simpler interface, for example a direct connection between the Host and the Network. Clearly the NIP is the more expensive, but again we can only make the comparison in the light of the comparative performance of the interfaces.

The duties of a NIP need not stop at the low level protocols, but may be extended to both more flexible implementations of these and the implementation of higher level protocols. Beyond this the NIP may take on some of the systems and management duties associated with the network. Pushing even further we come back to the case where the presence of a NIP is an integral part of the network access logic. But instead of being a limitation it now supplies all the high level functions a Host requires for communication, freeing it from performing them itself. In addition the NIP can provide a consistent interface and play a part in protection, authentication and security.

-5-

### 1.4 Overview

Chapter 2 describes the Cambridge environment against which much of the work described in this dissertation was done. The informed reader can ignore this chapter.

Chapter 3 describes the Type 2, a high performance NIP for the Cambridge Ring. This only implements the lowest level protocol: Basic Block Protocol, but supplies an extremely flexible interface to this.

Chapter 4 describes the MACE, a machine that has been put to similar use, but is based on a slower processor. The initial interface program for this machine, SPECTRUM, was less flexible than that for the Type 2, but is closer in specification to the Host's requirements.

Chapter 5 presents the concept of a High Level Interface that provides its Host with more powerful protocols and services. Chapters 6 and 7 describe the design and implementation of a High Level Interface on the MACE, called SuperMACE, and show that this approach results in an improved system performance.

Chapter 8 covers further aspects of a High Level Interface including some thoughts on possible hardware improvements and its role in security and authentication.

Chapter 9 examines the influence a NIP may have on the design of protocols, and goes on to describe the architecture of a system that provides a high degree of protection between machines.

Chapter 10 concludes this dissertation.

### 1.5 Acknowledgements

All the NIP programs described in this dissertation are my own work. The hardware of the Type 2 was designed and implemented by J. J. Gibbons and M. A. Johnson, the MACE was designed and implemented by M. Muller. The Host software for the LSI4 systems and for the SPECTRUM MACE program were written by B. J. Knight. That for the SuperMACE was written by the author.

# Chapter 2

### Background

This Chapter describes some of the background to the work presented in this dissertation. This material is presented here in preference to introducing it when the subject arises to dispose of it as soon as possible. Those familiar with the following items may skip them in the safe knowledge that they are not missing anything original.

### 2.1 The Cambridge Ring

The Cambridge Ring is a high performance Local Area Network (LAN) developed at the Cambridge University Computer Laboratory. The ring consists of a loop of two twisted pairs interrupted by repeaters that regenerate the signal. Data is carried in several packets that circulate in a fixed pattern. The number of packets is determined by the length of the ring and its clock rate. Since the ring is unlikely to be an exact number of packets long, the pattern consists of an integral number of packets plus a gap, which is shorter than a packet.

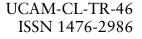

Packets are 38 bits long and consist of an 8 bit source address, an 8 bit destination address, 16 bits of data and six bits for framing, control and error detection. This is shown in figure 2.1.

### Figure 2.1 Format of a Ring Packet

Computers are connected to the ring via a station, which is in turn connected via a repeater. Each station has an unique address in the range 1 to 254, addresses 0 and 255 are interpreted specially. To the

-7-

connected computer the station supplies a full duplex interface, so transmission and reception may be viewed as completely independent devices. This is particularly useful when developing ring driving software since not only may the two halves be tested independently, but may also be tested jointly by transmitting to oneself.

Of all the stations one, the monitor station, is distinguished. This is responsible for initialising the framing structure of the ring at startup and for re-initialising it when it is lost.

# 2.1.1 Transmission

The primitive transmission operation provided by the station is to send one 16 bit data packet to a selected destination. This is achieved by waiting until an empty packet passes the repeater, claiming this by setting the full bit, and loading into it the destination address, source address (itself) and the 16 bits of data. The transmission logic then waits until the packet has been all the way around the ring. When the packet returns it is compared with the packet sent as an error detection measure, and the response bits are made available to the Host.

There are two response bits, allowing for four responses in total:

- Eucy The destination recognised its address, but was not ready to receive another packet.

- Unselected The destination does not wish to receive packets from our station.

- Accepted The destination received the packet.

- Ignored No station recognised its address: it either does not exist or is switched off.

Once a transmission has been performed the station is not allowed to refill the empty packet immediately, but must allow it to pass on. This simple mechanism prevents any one station from hogging the ring bandwidth and gives each station an equal chance of claiming packets, even when the ring is heavily used.

An elementary flow control mechanism is supplied to suppress extraneous transmissions. If the response to a transmission is <u>busy</u> the station inhibits the transmission of the next packet for a time. After the first such rejection this is a period of two ring revolutions, and on the second

-8-

and subsequent times is sixteen revolutions.

### 2.1.2 Reception

The primitive reception operation is to receive a single packet from the selected source. The source is controlled by the Source Acceptable Register (SAR). If this is set to a value in the range 1 to 254 then only packets from the station of that address will be accepted; transmissions from elsewhere will be rejected **uncelected**. If the SAR is set to zero no packets at all will be accepted, and if it is set to 255 packets from any station will be accepted, in which case the actual source may be read from another register in the station.

# 2.2 Protocols Used on the Cambridge Ring

Ring packets as they stand are unsuitable for most applications. There are three reasons for this. First, the overheads of deciding what to do with each packet individually would be prohibitively large, particularly in a program driven interface. Since the hardware supplies a means of selecting packets from one source only, this may be used to allow an entire sequence of packets to be received with greatly reduced overheads.

Second, the hardware only supplies addressing to the grain of a single station. A typical computer will have several processes in it that may be communicating with processes in other machines. When data arrives it is necessary to associate it with a particular process. The only form of identification supplied by the hardware is the source address, which may not uniquely identify it. Some form of extended addressing is required. Installing this in each packet would not only significantly reduce the amount of data that could be transferred, it would not give a large enough range of addresses to be of much help. However, if the data is blocked together an extended address of whatever size was felt necessary could be included in the block format.

Third, without incurring the same penalties described above, it would not be possible to detect lost or corrupt packets without blocking.

While a strong case in favour of a primitive block protocol has been put, it should be noted that there are applications where a single packet protocol has its advantages. One such is the transmission of digitized voice communications across the ring, where the overheads of constructing blocks intrude on the real-time requirements of the application [Les]ie81]. A few lost packets will go un-noticed, and if they are, error recovery can

-9-

be dealt with by higher level protocols. Another single packet protocol is the terminal protocol implemented at University College London [Rubinstein81] where a virtual circuit between a terminal and a Host computer is implemented by two streams of packets. The implementors rely on the low error rate of the ring to eliminate the need for any error recovery.

# 2.2.1 Basic Block Protocol

Basic Block Protocol [Walker78] provides the primitive block protocol demanded above. A basic block consists of a header packet, a route packet, some data packets and a checksum packet. Its structure is shown in figure 2.2.

| 4                | 2    | 10    | Bits                 |

|------------------|------|-------|----------------------|

| 1001             | TYPE | COUNT | Header Packet        |

| <br>FLAGS        |      | PORT  | Route Packet         |

| DATA ,           |      |       | Count+1 Data Packets |

| CHECKSUM or ZERO |      |       | Checksum Packet      |

### Figure 2.2 Format of a Basic Block

The header packet contains a 4 bit pattern as a weak form of identification, a 2 bit type field and a 10 bit count field, allowing from 1 to 1024 packets of data ( the count is really in the range 0 to 1023).

The route packet contains a 12 bit port number, which is used to direct the packet to the right process in the computer. The computer has complete freedom to allocate port numbers as it wishes. The flags field has three of its four bits allocated. The top bit indicates that the block is intended for the computer's ring interface and not for the computer itself; this allows remote debugging and loading of machines and will be covered in more detail in later chapters. The lower two bits of the flags field are used to specify one of four sub-ports, and is used for communication via a ring-ring bridge. The remaining bit is unassigned.

Following the route packet are the data packets. Owing to the way the count is encoded there must be at least one of these.

The content of the checksum packet depends on the value of the type field in the header. If the type is OO then this packet contains an endaround-carry checksum of all the previous packets in the block. If the type is O1 this packet contains zero (Note that an actual checksum cannot be zero unless all the packets in the block are zero, and the header is never zero). The checksum is present more to detect block framing errors (either because the wrong packet was identified as a header, or transmission was aborted in mid-block and a new one started), than to protect against the corruption of data during transit.

Type code 10 in the header indicates that the count field contains all the data in the block, and the following packets are not sent. Such immediate data packets have only limited applications.

The fourth code (11) has been allocated to indicate the use of a somewhat different block protocol. The count field contains a fixed bit pattern, and the header is followed by an extra packet containing the amount of data in bytes. This is followed by the route, data and checksum packets in the usual way. This variant has been specified with rings that have differently sized packets in mind, and is of only passing interest.

It is an important feature of basic block protocol that the layers of software above it should receive a block in its entirety or not at all. The basic block layer should never pass back incomplete or corrupt blocks.

One perfectly valid means of implementing basic block protocol is to receive all blocks regardless of source and then discard those that are not expected, too long for the available buffering or have bad checksums. This means that a block may be lost without trace, and may result in long delays before the transmitter realises this. A more helpful mechanism is to set the SAR to zero for a brief period of time just after the route packet of an unwanted block is received; the transmitter will see the destination go **unselected** in block and by convention will interpret this as meaning that this block is unwanted. This has the advantages that the sender can abort the transmission as soon as it sees this and time is not wasted at both ends in the transfer of a block of data that is not wanted.

Even given the above mechanism it is possible for a block to be lost, and in any case some machines do not implement it. Consequently basic block protocol does not guarantee to deliver a particular block to its destination with anything other than a high probability. Higher level protocols must therefore be capable of recovering from lost blocks. I will have more to say about the details of basic block protocol in later chapters.

### 2.2.2 Single Shot Protocol

Single Shot Protocol (SSP) [Ody79] implements a simple Request/Reply protocol similar to a remote procedure call. It is built on top of Basic Block Protocol by reserving the first three data packets for type and control information, and is shown in figure 2.3.

| 6C         | FLAGS      |

|------------|------------|

| Reply      | yPort      |

| Functio    | on Code    |

| ' User Par | rameters . |

| Service | $\rightarrow$ | CII | ent | (Rep | lyPort) |

|---------|---------------|-----|-----|------|---------|

|         |               |     |     |      |         |

# Figure 2.3 Format of SSP Exchange

The only proof the sender has that its request was received is the arrival of the reply. Failure of the reply to arrive is detected with a timeout. However the expiry of this timeout can mean one of two things: that the request was lost, or that the reply was lost. To make it safe to retry the request in both cases, SSP accessed services should be idempotent (i.e. repeatable).

# 2.2.3 Byte Stream Protocol

Byte Stream Protocol (BSP) [Johnson80] provides a pair of error free, flow controlled channels across the ring. Facilities are provided to push buffered data through a channel, reset the pair to a standard state, and to close the channels down. In some respects this is similar to a Transport Service, and can be upgraded to a full implementation of that protocol [JNT82].

BSP is built on Basic Block Protocol by reserving the first two data packets of a block for control information relating to the two channels, the remainder of the block is used for data. Data is never sent unless requested, giving flow control, and every data block is acknowledged, giving error recovery. The first data packet sent in a transmitted block contains a command and sequence number relating to the channel being received by the sender. The commands may be: NULL, in which case no action is taken, RDY (ready), in which case the next block of data is being requested, or NOTRDY, meaning that the next block of data should not be sent (but the last one is being acknowledged).

The second data packet contains a command and a sequence number relating to the channel being transmitted by the sender. The command may be NULL as before, DATA, in which case the rest of the block contains the data being sent, or NODATA, meaning the sender has no data to send at present.

The protocol is normally implemented as a finite state machine and is best described by the state transition table given in figure 2.4. This table gives the state transitions for both the receiving and transmitting ends of a channel because in all major respects they are identical.

State E is entered when an Essential element (RDY or DATA) is sent; the other end is expected to reply immediately. State N is entered when a Non-essential element (NOTRDY or NODATA) is sent; the other end is not expected to send anything in return. State I is entered when the other end sends a Non-essential element; the channel remains idle until the other end sends another essential element. For any byte stream there will be four such state machines, one for each end of the two channels.

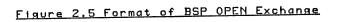

A Byte stream is initially set up by an OPEN exchange, the format of which is given in figure 2.6. The parameters passed are in two groups: the first relates to the properties of the stream to be created, the second group is defined by the user and relates to the service invoked. Only two BSP parameters are currently in use: the size of the largest block this end will send, and the size of the largest it will receive. The reply port is the port to which all subsequent BSP blocks will be directed.

The reply to an OPEN is an OPENACK. The parameters are grouped in the same way to that in the OPEN, the two BSP parameters consisting of the block sizes that will actually be used. The second word in the block (which is zero in an SSP reply) contains the port to which all subsequent BSP blocks should be routed.

| ſ |                                                      | State                        |                                                                                     |                                       |                                        |                                                                                     |

|---|------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------|

|   | Event                                                | E                            |                                                                                     | N                                     | I                                      |                                                                                     |

|   | E[rep]<br>DATA(n-1)/<br>RDY(n)                       | Retransmit<br>RDY(n)/DATA(n) |                                                                                     | Retransmit<br>NOTRDY(n)/<br>NODATA(n) | Protocol<br>Error                      |                                                                                     |

|   | E[exp]<br>DATA(n)/<br>RDY(n+1)                       | n+                           | ll buffer<br>:= 1<br>ready?<br>no:<br>Transmit<br>NOTRDY(n)/<br>NODATA(n)<br>Goto N | Protocol<br>Error                     | n -                                    | ili buffer<br>= 1<br>ready?<br>no:<br>Transmit<br>NOTRDY(n)/<br>NODATA(n)<br>Goto N |

|   | N[exp]<br>NODATA(n)/<br>NOTRDY(n+1)                  | Handsho                      | t Idle<br>ake Timer<br>to I                                                         | Protocol<br>Error                     | No                                     | Action                                                                              |

|   | Buffer<br>Ready                                      | No I                         | Action                                                                              | Transmit<br>RDY(n)∕DATA(n)<br>Goto E  | No                                     | Action                                                                              |

|   | Timeout                                              | Retransmit<br>RDY(n)/DATA(n) |                                                                                     | No Action                             | No Action                              |                                                                                     |

|   | Idie Protocol<br>Handshake<br>Timer Error<br>Expires |                              |                                                                                     | Protocol<br>Error                     | Retransmit<br>RDY(n)/DATA(n)<br>Goto E |                                                                                     |

<u>Notes:</u> n is the block sequence number (mod 16).

# Figure 2.4 BSP State Transition Table

Client → Service(ServicePort) Service → Client(ReplyPort)

| 6A        | FLAGS      |

|-----------|------------|

| Reply     | yPort      |

| Functio   | on Code    |

| Paramete  | er Count   |

| BSP Par   | ameters /  |

| / User Pa | rameters / |

| 65          | FLAGS      |  |  |

|-------------|------------|--|--|

| Connect     | ion Port   |  |  |

| Return Code |            |  |  |

| Paramete    | er Count   |  |  |

| / BSP Parc  | ameters /  |  |  |

| / User Pai  | rameters . |  |  |

### 2.3 The Cambridge Distributed Computing System

This section describes the structure of the Cambridge Distributed System, the environment in which most of this work was done. I begin with a simple overview of the system and follow with more detailed descriptions of those parts that are considered important, or have special relevance to the work presented here. A full account may be found in [Needham82].

### 2.3.1 Philosophy

The Cambridge Distributed System is based on the philosophy that it is better to give the user his own personal computer than access to a shared system. This approach becomes increasingly more realistic as the price of computer hardware falls. The advantages of this are that the machine is always to hand, under the user's control and its response is guaranteed to be constant. An isolated personal machine, however, is at a significant disadvantage. The cost of making it into a usable computing system with the addition of peripherals (terminal, hard-copy, permanent storage) is likely to be more than that of the processor itself, and if this has to be repeated several times it soon becomes more feasible to purchase a shared system. Separate machines also make the cooperation of users, and the propagation of software very difficult. The solution to these problems is to connect the computers together with a network; expensive peripherals may be shared, and programs and data moved between machines with ease.

Conventionally such a system is achieved by placing a machine of modest size, with keyboard, display and disc, in every office. While this is perfectly acceptable if the user does not get ambitious about the kind of program he wishes to run, such a machine is clearly not able to support such applications as relational databases, graphics and numerical computations. It is unreasonable to expect a user to leave his office to go in search of a suitable machine each time his computing needs outgrow his personal machine; it is also difficult to justify giving him a larger machine permanently, because he is unlikely to use it to its full capacity. Permanent allocation of a machine to a user also hinders the development and running of distributed algorithms.

One possible solution is to supply on the network a large shared computer to which the user may connect his personal machine as a remote terminal. The user now has access to enough computing power to run his more ambitious programs, but only has access when he needs it. This approach, however, is not really in the spirit of distributed computing, since most application effort would concentrate on the shared machine. At Cambridge an alternative approach has been adopted.

## 2.3.2 The Cambridge Distributed System

The Cambridge approach is to give each user a personal computer of modest performance, possibly integrated with his terminal, and without local discs. This machine is capable of only minor duties, one of which is to connect as a remote terminal to some other machine on the network. Most of the computing power of the network resides in the **Processor Bank**: a collection of machines free for any user to claim.

When a user wishes to use a **Processing Server** (as the machines in the processor bank are known) he approaches the resource management system. This attempts to find a suitable machine, load it, and allocate it to the user. Once allocated the machine belongs exclusively to the user for as long as he desires; his personal computer acts simply as a (possibly very intelligent) remote terminal.

Since processing servers may be allocated to any user they may not have any local file storage. Instead all user files are stored on the Fileserver, which is accessible from any machine. Consequently a user may access his files regardless of the physical machine he is using.

Once allocated, a user has total control over the processor bank machine he has been given. This includes being able to stop it, start it, load any code into it, and debug it at the hardware level. The degree of sharing of resources here is at a somewhat coarser grain than that supplied by a time-shared system: dealing in whole processors rather than machine cycles. This pre-supposes that there are enough processors in the bank to satisfy demand; in practice this means that there should be slightly more machines than necessary. With the trend towards ever cheaper machines this is not a great price to pay for the advantages.

The composition of the processor bank need not be homogeneous, but may be tailored to suit the requirements of the user community. For example, it might contain a large number of medium sized machines to meet most users needs, plus several more powerful machines for those with greater demands. It may even contain machines with special architectures or hardware features ( LISP and P-code machines, floating point hardware etc.). The handling of distributed applications is a simple extension of the basic system to allow a user to request more than one machine, and to allow the machines themselves to request further processors. In addition to the processor bank the Cambridge Distributed System contains many machines dedicated to providing most of the services conventionally supplied by an operating system. These range from substantial machines controlling substantial peripherals (Fileserver, Laser printer), to small machines controlling simple peripherals (Terminal concentrator, Line printer, Time-of-day clock), to machines that perform the basic management functions of the distributed operating system.

The system does not prevent conventional mainframes and mini-computers from accessing its services, and using the network for their own purposes. The mainframe may use the system to whatever extent it wishes, from simple use of printers and file transfer, to access via remote terminals and keeping its filing system on the Fileserver. An example of converting an operating system to do the latter may be found in [Dellar80].

### 2.3.3 Implementation Details

The preceding section has given a somewhat idealised view of what the system looks like. In practice users do not have personal machines, but merely a conventional cursor addressed VDU connected to the ring via a terminal concentrator. All user work is done in processor bank machines or in time-shared machines connected to the ring.

#### 2.3.4 Processing Servers

At present the processor bank contains two different machine types: Computer Automation LSI4's, and Motorola 60000's. Processing servers differ from most other types of computer in that they have no peripherals other than the Ring. Given this fact it is important that the Ring connection be of high performance. In both cases the connection is made via a second interface processor, which in addition to performing ring access functions for the Host computer is also able to exercise the kind of control over it one expects from the front panel of the machine: loading systems, stopping and starting execution, and debugging. Since these interfaces are the subject of this dissertation I will say no more about them here.

### 2.3.5 Processor Bank Management

The allocation and loading of processing servers is managed by three machines; the **Resource Manager**, the **Session Manager** and the **Ancilla**.

The Resource Manager is responsible for knowing which machines are allocated, to whom, and for how long. It is also responsible for allocating the machines and getting them loaded with the program or operating system required by the user. Requests to the Resource Manager specify the type of system to be loaded, the length of time it is wanted for, and the attributes the machine should have (i.e. large memory, floppy discs, The Resource Manager searches its list of free intimate terminal). machines for one that has the requested attributes (including any the specified system may demand) and if one is found loads it with the given system. Two times are specified in the request, one gives the maximum time for which the machine will be allocated, and an initial refresh time. Once the machine is loaded it must contact the Resource Manager before the expiry of the refresh time. The purpose of this is so that the machine may discover where it was started from and why it was started. In this message the machine must specify a new refresh time, and must repeat the exchange again before this time expires. The effect of this is to maintain a dead-man's handle between the Resource Manager and the machine and allows crashed machines to recovered. If the refresh time ever expires the Resource Manager may reclaim the machine for re-allocation.

The interface to the Resource Manager is at a low level so requests may be made by other computers for processing servers. For the user at the terminal the Session Manager provides a higher level interface. Initially the user connects his terminal to the Session Manager, which translates his typed commands into low level requests to the Resource Manager. Once the Resource Manager has allocated and loaded a machine the Session Manager drops out of the conversation and the user can communicate directly with the processing server.

The Resource Manager effects the loading of a machine by giving its name plus the name of a file containing the system to be loaded to the Ancilla. This service is responsible for knowing how to load that particular type of machine with a binary load image taken from its own filing system on the Fileserver. The exact activity of the Ancilla may range from simply passing the name of the file on to the machine's ring interface, to relaying the entire image from the Fileserver to the machine itself for less intelligent interfaces. In theory there is a separate Ancilla for each different type of machine but in practice they are sufficiently similar that they may be coalesced into a single machine (although their external interfaces remain logically distinct). The Ancilla also has a role to play in remote debugging.

## 2.3.6 The Nameserver

To use any of the various services it is necessary to address messages to them. If the system were static these addresses could be fixed and built into programs. This is, however, somewhat inflexible; we want to be able to move services between machines and move machines around the network. To allow this, all services are located by an SSP containing a textual name to the Nameserver, which replies with the address of the service. The Nameserver is distinguished in that its station address is well known and fixed for all time. Relocating a machine or service is therefore a simple matter of changing its entry in the Nameserver.

# 2.3.7 The Cambridge Authentication System

This is accomplished by at Cambridge with UID-sets. A UID-set consists of four items: a PUID which names an object or user, a TUID which represents an instance of that object, a TPUID which represents the association between the PUID and TUID, and an Authentity (<u>Authority</u> Id<u>entity</u>) which names the authority under which this association was made. These all take the form of 64-bit random numbers to protect against forgery, and any of them, particularly the TPUID, may be absent. This association is stored in the Active Object Table (AOT) and is periodically refreshed in the same manner as the Resource Manager's dead-man's handle. The AOT also supplies functions to validate, identify, create, and enhance UID-sets. The reader is referred to [Girling82] for more details.

# 2.3.8 The Fileserver

The Cambridge Fileserver [Dion81] is implemented on a Computer Automation LSI4/30 computer with 80 Mbyte CDC disc drives. It provides a slightly abstract view of a filing system with two types of object: files and indices. All Fileserver objects are named by a 64-bit <u>Permanent</u> <u>Unique Identifier</u> (PUID) which is composed of 32 bits of object identification and 32 bits of random data to provide a degree of unforgeability.

A file is a vector of 16 bit words and may be any size from zero to about 13.5 Mwords. Space is only allocated on disc for those parts of the file that have actually been written. Consecutive sequences of words may be read or written at any point in the file.

An Index holds references to objects and is simply a list of PUIDs. The only restriction on what references an index may hold is that they must not be for objects on a different disc pack, so that packs may be mounted and dismounted independently. The structure of references on a single pack, therefore, is a full directed graph or naming network, which may contain loops and multiple references. Each pack has a distinuished <u>root</u> <u>index</u> from which the entire network on that pack descends. The Fileserver guarantees to preserve any object as long as it is reachable from the root index, otherwise its PUID is invalidated and the disc space reclaimed. This is normally achieved by maintaining a count of the number of references that exist in the network to each object; deleting it when this count reaches zero. It is possible, however, for a cyclic structure of indices to become detached from the root system, and for reference counts to become higher than they should (care is taken to ensure they are never lower than necessary). These are taken care of by an asynchronous garbage collector, which is run on behalf of the Fileserver itself in a processor bank machine [Garnett80].

Two types of file are supported by the Fileserver: <u>normal</u> and <u>special</u>. Normal files are intended to be used for the majority of data storage; if a crash occurs while data is being written the Fileserver does not guarantee that the data will be left in a satisfactory state. Special files are intended for storing data that must always be in a self consistent state (for example, filing system directories). Any alteration to a special file will either happen completely, or not at all. Operations on special files are consequently more expensive than on normal files. Indices are treated like special files.

A client of the Fileserver may perform single operations on a file by quoting its PUID in the request, or it may execute a sequence of operations by <u>opening</u> it. In response to an OPEN the Fileserver returns a <u>Temporary Unique Identifier</u> (TUID) for the object which should be quoted in subsequent operations in place of the PUID. The TUID represents an interlock on the file, any attempts to access this file with the PUID will be rejected until the file is closed (and the TUID cancelled) or it times out. Opening a file (or index) has two advantages. The client gains an interlock on the object: if it is open for reading then read requests but no write requests will be granted to other clients, and if it is open for writing no other requests will be allowed on this object at all. If the object is special (or an index) all operations before the final CLOSE constitute an atomic transaction, and will either occur in their entirety or not at all.

Most Fileserver operations are single SSP exchanges with the exception of the READ and WRITE operations. The READ request specifies the object and the amount of data to be read, plus a port to which the data should be directed. The Fileserver transmits the requested data as fast as possible to the specified port, followed by the standard SSP reply. The WRITE request similarly specifies the object and amount of data to be written to which the Fileserver replies immediately, nominating a port to which the client should send the data as fast as possible. Once the Fileserver has received all the data it sends a second SSP reply to the client reporting on the transaction's success. To make the reading and writing of small quantities of data easier the Fileserver also supplies SSPREAD and SSPWRITE functions, which can transfer up to 256 words of data in one SSP exchange.

There are currently two Fileservers in operation running five disc drives. The filing systems in use include one for the processor bank machines and one for the CAP computer. There are also several smaller private filing systems belonging to servers, notably the Mail and Ancilla filing systems. To allow disc packs to be moved between Fileservers there is a service (Packserver) which, when given a file PUID, will return the name of the Fileserver on which that file is currently resident.

# 2.3.9 The Filing Machine

Processor bank machines do not in fact use the Fileservers directly, but make all their files accesses through the Filing Machine [Richardson83]. This handles all the housekeeping associated with the filing system so the client machines need only contain a stub which hands all commands on to FM. The Filing Machine is equipped with 1 Mbyte of main memory and can implement an intelligent caching algorithm. The result of this is that the most frequently used files (system commands etc.) remain permanently in the FM's cache, and need never be fetched from disc. This more than makes up for the extra level of indirection the filing machine introduces. The Filing Machine can also implement access controls and accounting.

# 2.4 TRIPOS

The system usually loaded into processing servers is a variant of the TRIPOS operating system [Richards79a, Knight82]. TRIPOS was originally designed as a portable single user operating system for mini-computers with their own discs and peripherals. It has been successfully enhanced to run in the processor bank in such a way that most of the original software may be run without change.

In the interests of portability the hardware features exploited by TRIPOS are minimal; there is, therefore, no concept of memory management or protection, privileged processor states or priority interrupt levels. The outcome of this is that the TRIPOS operating system is totally unprotected from the user and everything lies in a single global address space. The advantage of this is that objects may be passed by reference to any point in the system, rather than being copied, and TRIPOS gains greatly in simplicity because of this. The main disadvantage is that an aberrant program can cause serious disruption; but since the system is single user, and restarting it should be cheap, this is deemed not to be a problem.

TRIPOS is a multi-tasking operating system, inter-task communications being achieved by message (or packet) passing. Since all addresses are global this is accomplished by switching pointers rather than copying and consequently the system is extremely efficient. Each task has a single packet or <u>work queue</u>, packets sent to the task are appended to the end of the queue. To receive packets a kernel primitive is called which either returns the first packet in the queue or suspends the task until one is available.

The TRIPOS kernel itself only provides support for tasks, devices, message passing and store management. Other services such as a filing system, terminal handling etc. are provided by handler tasks. The kernel and device drivers are written in assembly code while the rest of the system is written in BCPL [Richards79b]. The structure of the tasks and the implementation of the kernel functions as BCPL callable procedures makes TRIPOS an extremely BCPL oriented system, and although other languages have been implemented (Fortran, Pascal, Algol68c, Algol68RS) these see only limited use.

Device drivers are accessed by packet passing in the same way as tasks, but while tasks are addressed by small positive integers, devices are addressed by small negative integers. In general a device is started by the reception of a packet and when it finishes the packet is returned. The shortcomings of this simplistic view of devices will be elaborated in later chapters.

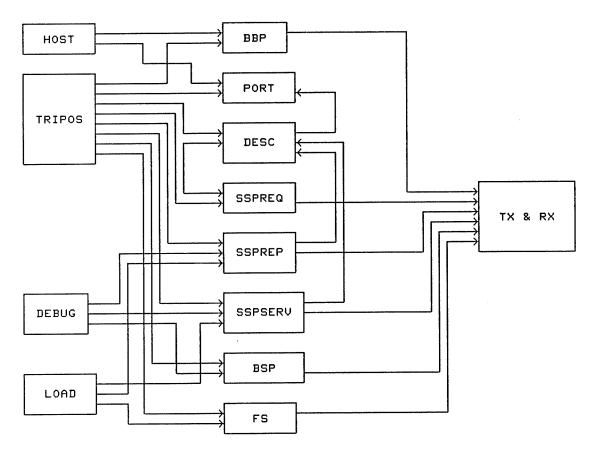

The system normally loaded into a processing server consists of seven tasks and one device driver. The device is, of course, the Ring (or, more accurately, the Ring Interface Processor). The seven tasks are:

- <u>The Ring Handler</u>: this is the only task that communicates with the Ring driver and presents a machine independent interface to it along with several ancilliary functions such as port allocation.

- <u>The BSP Handler</u>: this implements Byte Stream Protocol using the functions supplied by the Ring Handler. Normally there is only one byte stream open, which is being used by...

- <u>The Virtual Terminal Handler</u>: this is responsible for translating the virtual terminal protocol being used over the byte stream to the terminal concentrator into a normal TRIPOS stream. This task is also responsible for maintaining the dead-man's handle to the Resource Manager.

- <u>The File Handler</u>: this translates standard TRIPOS file access commands into messages to the Filing Machine.

The Command-Line Interpreter: this runs programs on the users behalf.

- The Interactive Debugger: this is always resident and the user may switch the input of his console to it at any time to monitor the machine's activity. It is BCPL oriented in that it knows the structure of a BCPL stack and program, although it may also be used at machine level.

- <u>The Ring Services Task</u>: this is responsible for starting up services in response to requests received from the Ring. These services include file transfer and user enquirys. This task is not essential and can be deleted without harm.

A major drawback of this system is that to be able to debug a program four tasks, the Kernel and the Ring device driver all need to be in working order. This can cause significant difficulty when attempting to debug a renegade program that could corrupt vital parts of store. Means to avoid this will be described in later chapters. Chapter 3

# <u>The Type 2</u>

The Type 2 is a high performance machine independent ring interface for connecting 16 bit mini-computers to the Cambridge Ring. By high performance we mean that not only is it capable of transferring data to or from the Host's memory at high speed, but is able to implement at least Basic Block Protocol on the Host's behalf.

In the context of the Cambridge Distributed System it is also required to exert control over the Host to load, stop, start and debug it. At present there are nine LSI4s connected to the Ring via a Type 2 including the Cambridge Fileserver.

# 3.1 Before the Type 2

The first Ring interface for the LSI4 was based on the Computer Automation picoprocessor, or intelligent cable. This was a simple programmable peripheral controller with DMA access to the LSI4's memory. Its program space was extremely limited, so it was configured just to DMA blocks of data to and from the Ring. Functions were also included to allow the Host to read and write the destination, select, source and status registers in the station. Basic Block Protocol was implemented in a handler task in the Host, which also had to calculate the checksum itself.

When the first Type 2s were made available the first program to be written for them was essentially an emulator of the picoprocessor. This allowed the hardware to be connected to all the machines with a minimum alteration in the Host software. Even with this simple program the Type 2 exhibited a performance improvement over the picoprocessor. This program was christened 'Noddy', due to its extreme simplicity.

### 3.2 Hardware

This section gives a brief description of the hardware configuration of the Type 2. A full description of the design process and implementation of the Type 2 can be found in [Gibbons80a].

The Type 2 is built around a Signetics 8x300 bipolar microprocessor that can execute any instruction in just 250ns. This speed derives partly from its bipolar technology, partly from its simple instruction set, and partly from the separation of its program and data address spaces, with a separate address bus for each.

The program bus has 12 address bits and 16 data bits and is read only. Each instruction is a single 16 bit word with a three bit op-code, giving just eight possible instructions. These include four standard instructions: MOVE, ADD, AND and XOR which can all work on combinations of registers and data bytes. There are three instructions that affect the course of execution of the program, the simplest of which is an unconditional jump (JMP). The only conditional branch available is to test a register or data byte and branch if it is non zero (NZT). The branch address is specified by a value that replaces the bottom five or eight bits of the program counter; such jumps are therefore limited to pages of 32 or 256 bytes. The number of bits replaced depends on the item tested, eight if it is a register, five if a data byte. The third branch instruction (XEC) specifies an instruction to be executed after it. If the specified instruction is a jump then the jump is taken, otherwise execution after this instruction is resumed after the XEC. The last instruction, XMIT, allows constant data to be inserted into registers or data bytes. Additionally any instruction that accesses a data byte can also specify a shift and mask to be applied to it before being made available. This gives the 8x300 powerful bit manipulation abilities.

The data bus is just eight bits wide and is multiplexed between address and data, thus there can only be 256 bytes of data in the address space. This is alleviated somewhat by duplicating it into two banks (known as Left and Right) which may be accessed independently. The multiplexing of the data bus is performed in part by software. Thus an access to a single byte requires one instruction to set the address in the appropriate address register, plus one to access the byte. Once a address is set, however, the same byte may be accessed repeatedly in just one instruction. Separate addresses may be set up independently for both the left and right banks. In the Type 2 the Left bank contains 256 bytes of fast RAM and the Right contains the mapped control registers of the Ring and DMA channels. These features make the machine somewhat bizarre to program, and one tends to approach it in the same spirit one approaches microcode.

The Type 2 is connected to the ring by mapping the control registers of the station into bytes in the Right bank. The Type 2 can, therefore, perform operations on the ring simply by reading and writing select locations in its own address space.

The connection to the Host is made via two bi-directional DMA channels and two I/O ports. The DMA channels contain auto-incrementing address registers to assist in vector transfers. The I/O ports present a reasonably machine independent means of establishing communication between the Host and the Type 2.

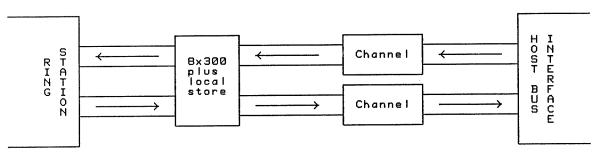

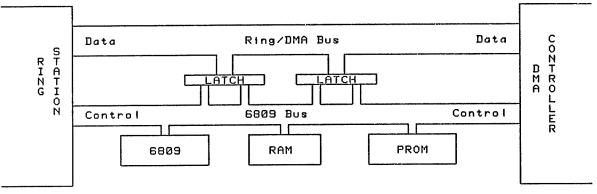

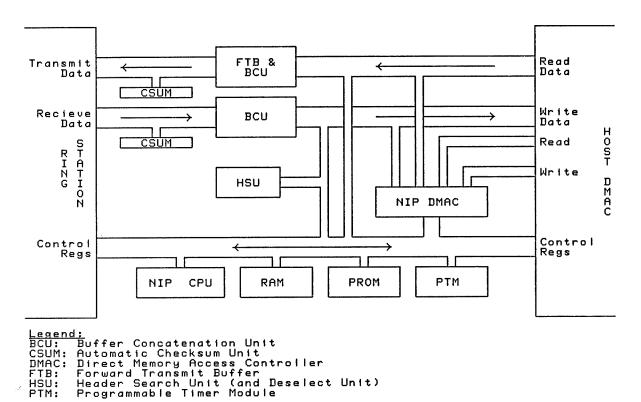

Physically the Type 2 consists of three circuit boards: one containing the 8x300 plus memory and Ring interface logic, and two identical boards each containing one DMA channel and I/O port. The interface presented by the channel boards is designed to be machine independent so a fourth board is required to slot into the backplane of the Host computer to translate this into signals suitable for the Host's bus. The organisation is shown in figure 3.1.

Figure 3.1 Type 2 Hardware Configuration

# <u>3,3 Design</u>

This section sets out the required properties of the Type 2 program and the design decisions made to meet them.

# 3.3.1 Requirements

The primary requirement is of course that the Type 2 should implement Basic Block Protocol on the Host's behalf. This means that it must preface the user's data with the header and port packets, and add the checksum packet at the end, calculating the checksum itself. Similarly the header and port should be stripped on reception, and the checksum validated. The Type 2's limitations mean that it cannot buffer the user's data, which must therefore be transferred directly from the Host's memory to the Ring (or vice versa). This means that the checksums must be calculated on-the-fly. This fact has been a major influence on the design of this, and later, intelligent interfaces.

That the protocol should only be BBP rather than any higher protocols is dictated by the Type 2's insufficiency of program and data space to implement anything more complex. Additionally it was decided that the Host would gain nothing from direct access to Ring packets.

In the context of the Cambridge Distributed System the Type 2 not only has duties to perform on behalf of the Host, it also has to implement various control functions initiated from the Ring. These functions include loading the initial system into the Host, setting it going and debugging it when it fails. The Type 2 must always be able to perform these functions, so it must protect its integrity against any possible misbehaviour by the Host or by any other machine on the Ring.

### 3.3.2 Host Commands

The principal commands given by the Host to the Type 2 are concerned with driving Basic Block Protocol. A typical command might be:

"Transmit <u>p</u> words of buffer <u>b</u> as a basic block to port <u>p</u> on station <u>s</u>."

Such a command must occupy several 16 bit words and a method must be supplied to transfer them all to the Type 2. Three such methods can readily be devised. First, they can be passed one after another through an I/O port. To prevent the Host and Type 2 getting out of step some form of protocol would be necessary to synchronise the exchange; results would have to be returned the same way. This is not in keeping with the our desire to the minimise the Host's work when using the Ring since the exchange protocol could become quite complicated. The second method parcels the entire command up into a <u>codeword</u>, or command vector. The address of this is passed to the Type 2 via the I/O port which can then read the codeword via a DMA channel. When the command is finished the results can be DMA'ed back into the codeword and its address returned via the I/O port. The third method is a variation of the second, a fixed command vector is used and the Host need only signal the Type 2 when a command is ready, since the address is already known. Results are returned via a second vector. A minor amount of protocol is necessary to prevent, for example, the Host overwriting the vector with a new command before the Type 2 has read the previous one. This can be made independent of the choice of location of the command vector by supplying the address to the Type 2 during initial loading.

The second method was implemented since the current hardware lent itself most naturally to it. To implement basic block protocol three commands are necessary. The general form of the transmit command has been given. A reception command looks like this:

"If a Basic Block arrives on port p from station  $\underline{s}$  and contains not more than  $\underline{p}$  words of data, put it in buffer  $\underline{b}$ ."

The station number <u>s</u> may specify either a specific station, or may be a value denoting that any station will do. The form of this command raises two important points about the design of the reception system in the Type 2. The first is that it must be capable of holding several reception commands at once for different port/station combinations. The second is that requests need not necessarily be returned in the order they were submitted, it depends on the order in which Blocks arrive from the Ring. This is no problem with the adopted communication method, the address of the codeword uniquely identifies it; if either of the other two methods had been used, however, it would be necessary to pass an identifier to the Type 2 with the command to be returned with the reply.

The third command cancels reception requests. The Type 2 has no concept of the passage of real time, so reception requests will remain with the Type 2 until either satisfied, or cancelled. It is the Host's responsibility to maintain reception timeouts, and when a timeout expires the relevant request must be cancelled. The Cancel command simply specifies the address of the codeword to be cancelled. Cancelling the request is simple if it is dormant; if, however, it is in the process of being satisfied there are two possible courses of action: to fail the cancellation and allow the reception to complete in the normal way, or to abort the reception of the block and satisfy the cancellation. Since the Host is cancelling the request it can be assumed that it is no longer interested in seeing it satisfied, so the second course of action is the correct one. It is still possible for a cancel command to be issued while the satisfied request is in the pipeline back to the Host and the cancel command will fail since the specified request can no longer be found. The Host must, therefore, be ready to handle the case of cancelled reception requests being returned.

# 3,3,3 Buffer Chaining

The commands described above are suitable for transmitting or receiving one basic block from (or into) just one buffer. There are cases where it would be useful to give the Type 2 a buffer larger than the maximum Basic Block size and have it either transmitted as a sequence of blocks, or not returned until it has been filled by several separate blocks. The requirement for this comes in part from the observation that Fileserver Reads and Writes require exactly these primitives. For transmission no change is required to the command format. The Type 2 can trivially detect when the supplied buffer size is greater than a Basic Block and split the transmission up into several maximum sized blocks plus one to carry the remainder.

For reception the case is somewhat more complicated. It is only useful to wait until an entire buffer has been filled if the amount of data to be received is known; for example, a Fileserver read. At other times the amount of data, and the size of blocks, will not be known and the Host will want notification on a per-block basis. The Host will here want to submit a buffer of at least the maximum size of block it expects, to be returned as soon as a block is received into it. The difference between these two lies in the action taken after a block is received: in one the codeword is returned immediately, in the other the codeword is returned only if the buffer is full, otherwise it is made ready for the reception of a further block. The Host can specify these two different actions with a little as one bit in the request codeword.

Given that splitting a single buffer into several basic block is a useful thing to do, what about splitting a basic block across several buffers? When transmitting or receiving higher level protocols (SSP, BSP) the block will be divided into two or more sections by the protocol. For example: an SSP request has three words of protocol specific header followed by user Using the simple basic block functions any SSP protocol data. implementation would either demand that the user leave three words free at the front of each buffer he submits, or would have to copy it into a buffer of its own to add the protocol data. If the Type 2 undertook to join buffers together, however, the SSP package could simply prepend the user's buffer with a three word buffer of its own. The user can lay out his buffer without worrying about leaving space for the protocol package, and when it is finally transmitted it is included in the block by indirection rather than by copying. A more suitable example it that of a long read from the Fileserver; here the data which is coming from the Fileserver is to be installed in several file handler cache blocks. The data is unlikely to arrive in blocks of the correct size, and the Host will have to engage in some elaborate shuffling to get it to fit correctly. If the Type 2 were to automatically insert the blocks into the buffers in the correct order the Host would be saved much trouble. It can therefore be declared that a general buffer/block splitting facility would be a useful attribute of the Type 2.