Number 375

# Restructuring virtual memory to support distributed computing environments

Feng Huang

July 1995

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

#### © 1995 Feng Huang

This technical report is based on a dissertation submitted July 1995 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Clare Hall.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986 DOI https://doi.org/10.48456/tr-375

#### Acknowledgements

I am most grateful to Jean Bacon, my supervisor, for her patience, constant encouragement, useful discussions and valuable support during the course of this research. Thank you, Jean.

I would like to thank members of the Computer Laboratory, specially Glenford Mapp, Sai-Lai Lo, Zhixue Wu, and Innes Ferguson for their valuable discussions and encouragement. Thanks to the past and present members of the System Research Group who develop and maintain the Wanda system which was used for the experimental work in this research. Also, thanks to Ken Moody and other members of the Opera project for providing me the opportunities to present this work and to get useful comments and practical assistance in the project meetings.

Many thanks to the following people who have read and suggested improvements to this dissertation: Jean Bacon, Glenford Mapp, Innes Ferguson, Mohamad Afshar and Shaw Chuang.

Special thanks to Roger Needham, the head of the Computer Laboratory, for his advice and help and making departmental support facilities available during this research. I also want to thank Martyn Johnson, Graham Titmus, Piete Brookes and Chris Hadley for providing much needed system support, and Lewis Tiffany and Paola Bishop for great assistance in the library.

I am very deeply indebted to my parents, school teachers and friends for their strong support. Without their support, I would not have been able to finish my school education, not to mention pursuing my PhD study at Cambridge. I also thank my parents for their incredible understanding and encouragement which kept me going for these years. Thanks also to my wife Chen Yue for her lovely letters and her emotional support during the last stage of this research.

This work is supported by a Sir Run Run Shaw Scholarship and a Caius Bursary from the Cambridge Overseas Trust, an Overseas Research Students Award from the Committee of Vice-Chancellors and Principals of the Universities of the United Kingdom, and a Research Studentship from the Cambridge Philosophical Society. All these financial supports are highly appreciated. I also thank the Computer Laboratory and Clare Hall for the financial support which enabled me to attend the Advanced Course on Distributed Systems in Lisbon and for two-month living expenses which enabled me to complete this research.

| 4 | Des        | ign of the Coherence Mechanism                | 31        |

|---|------------|-----------------------------------------------|-----------|

|   | 4.1        | Introduction                                  | 31        |

|   | 4.2        | Design Considerations                         | <b>32</b> |

|   |            | 4.2.1 Granularity                             | <b>32</b> |

|   |            | 4.2.2 Remote Interprocess Communication       | 33        |

|   |            | 4.2.3 Writing Modifications to Backing Store  | 35        |

|   | 4.3        | Public Interface and Related Issues           | 36        |

|   |            | 4.3.1 Public Interface                        | 36        |

|   |            | 4.3.2 Page-Based Lock                         | 36        |

|   |            | 4.3.3 Deadlock Prevention                     | 37        |

|   | 4.4        | Coherence Protocols                           | 39        |

|   |            | 4.4.1 Write-Invalidate Protocols              | 39        |

|   |            | 4.4.2 Write-Update Protocol                   | 41        |

|   |            | 4.4.3 Integrated Coherency Control            | 41        |

|   | 4.5        | Coherence Manager and Coherence Server        |           |

|   | 4.6        | Illustration of Coherency Control             |           |

|   |            | 4.6.1 Mapping An Object and First Access      |           |

|   |            | 4.6.2 Object Coherency                        |           |

|   |            | 4.6.3 Unmapping An Object                     |           |

|   | 4.7        |                                               |           |

| _ | T          | 1                                             | 48        |

| 5 | 1mg<br>5.1 | olementation System Environment               |           |

|   |            |                                               |           |

|   | 5.2        | Object Management                             |           |

|   | 5.3        | Persistent Object Manager                     |           |

|   | 5.4        | Coherence Manager                             |           |

|   |            | 5.4.1 Server Identifier                       |           |

|   |            | 5.4.2 Object Management                       |           |

|   |            | 5.4.3 Communication Management                |           |

|   |            | 5.4.4 Other Modules                           |           |

|   | 5.5        | Coherence Server                              |           |

|   | 5.6        | Storage Server Emulator                       |           |

|   | 5.7        | Summary                                       | 54        |

| 6 | Per        | formance                                      | 55        |

|   | 6.1        | Introduction                                  | 55        |

|   | 6.2        | Performance of the RPC System                 | 56        |

|   |            | 6.2.1 Simple RPC vs MultiRPC                  |           |

|   |            | 6.2.2 MultiRPC Speed-Up                       |           |

|   |            | 6.2.3 Summary                                 |           |

|   | 63         | Memory-Manning vs Non Memory-Manning on Wanda |           |

|                 | 6.4  | Performance of the Prototype COMMOS           | 61        |  |  |

|-----------------|------|-----------------------------------------------|-----------|--|--|

|                 |      | 6.4.1 No Coherency                            | 61        |  |  |

|                 |      | 6.4.2 Centralised-Control Protocol            | 61        |  |  |

|                 |      | 6.4.3 Distributed-Control Protocol            | 62        |  |  |

|                 | 6.5  | Summary                                       | 63        |  |  |

| 7               | Sup  | porting Distributed Persistent Programming    | 65        |  |  |

|                 | 7.1  | Introduction                                  | 65        |  |  |

|                 | 7.2  | Defining C++ Class Operators                  | 67        |  |  |

|                 | 7.3  | Overloading C++ Operator                      | <b>70</b> |  |  |

|                 | 7.4  | Supporting Fine Grained Objects               | <b>72</b> |  |  |

|                 | 7.5  | Other Issues                                  | 74        |  |  |

|                 |      | 7.5.1 Working with Pointers                   | <b>75</b> |  |  |

|                 | 7.6  | Summary                                       | 76        |  |  |

| 8               | Rela | ated Work                                     | 77        |  |  |

|                 | 8.1  | Apollo Domain                                 | <b>77</b> |  |  |

|                 | 8.2  | Mach                                          | 78        |  |  |

|                 | 8.3  | Chorus                                        | 80        |  |  |

|                 | 8.4  | The V System                                  | 81        |  |  |

|                 | 8.5  | Clouds                                        | 81        |  |  |

|                 | 8.6  | Choices                                       | 82        |  |  |

|                 | 8.7  | Spring                                        | 83        |  |  |

|                 | 8.8  | Comandos                                      | 84        |  |  |

|                 |      | 8.8.1 Amadeus                                 | 85        |  |  |

|                 |      | 8.8.2 COOL                                    | 85        |  |  |

|                 |      | 8.8.3 Guide-2                                 | 86        |  |  |

|                 | 8.9  | Casper                                        | 86        |  |  |

|                 | 8.10 | Opal                                          | 87        |  |  |

| ٠.              | 8.11 | Pegasus                                       | 88        |  |  |

|                 | 8.12 | Comparison                                    | 88        |  |  |

| 9               | Con  | clusions .                                    | 90        |  |  |

|                 | 9.1  | Conclusions                                   | 90        |  |  |

|                 | 9.2  | Further Work                                  | 92        |  |  |

|                 |      | 9.2.1 More Flexible Coherence Schemes         | 92        |  |  |

|                 |      | 9.2.2 Support for Heterogeneous Architectures | 93        |  |  |

|                 |      | 9.2.3 Exploitation of COMMOS Functionality    | 93        |  |  |

|                 | 9.3  | Final Word                                    | 94        |  |  |

| Bibliography 95 |      |                                               |           |  |  |

| A | Public Interface                               | 105   |

|---|------------------------------------------------|-------|

| В | VMM and POM Interaction                        | 108   |

| C | Coherence Protocols                            | 111   |

|   | C.1 Write-Invalidate Protocols                 | . 111 |

|   | C.1.1 Centralised-Control Protocol             | . 111 |

|   | C.1.2 Distributed-Control Protocol             | . 113 |

|   | C.2 Write-Update Protocol                      | . 116 |

| D | Coherence Manager                              | 120   |

| E | Coherence Server                               | 123   |

| F | Storage Server Emulator                        | 126   |

| G | Performance Measurements                       | 128   |

|   | G.1 RPC Performance                            | . 128 |

|   | G.2 Page Fault, Invalidation and Roundtrip IPC | . 132 |

|   | G.3 Performance of the COMMOS Prototype        | . 133 |

## **List of Figures**

| 2.1 | Monolithic Kernel vs. Microkernel                           | 6          |

|-----|-------------------------------------------------------------|------------|

| 2.2 | File Access in Monolithic Kernels and Microkernels          | 9          |

| 2.3 | Buffer Management in DBMS                                   | <b>10</b>  |

| 2.4 | Double Paging Problem                                       | 11         |

| 2.5 | Shared Virtual Memory                                       | <b>1</b> 3 |

| 2.6 | Various Approaches to Caching in Client Memory              | 15         |

| 2.7 | An Example of Accessing a Persistent Object                 | 18         |

| 3.1 | The COMMOS Layers                                           | 23         |

| 3.2 | COMMOS Architecture                                         | <b>2</b> 8 |

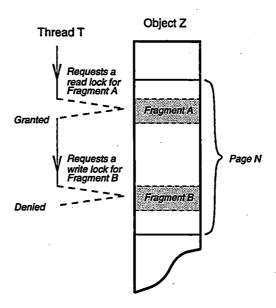

| 4.1 | Self-Deadlock When Fine-Grained Locks Are Requested         | 37         |

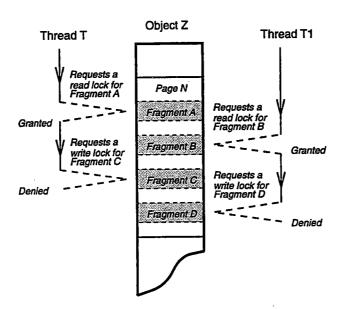

| 4.2 | Inter-Thread Deadlock When Fine-Grained Locks Are Requested | 38         |

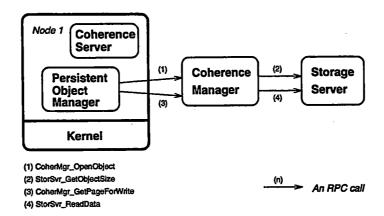

| 4.3 | Opening An Object and the First Access (All Protocols)      | 43         |

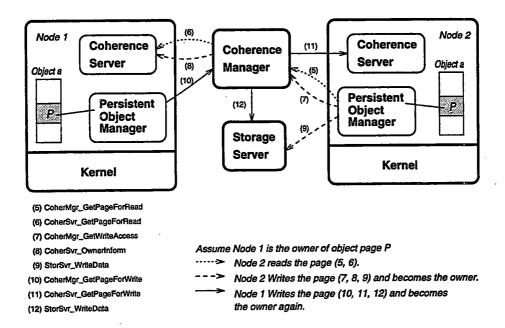

| 4.4 | Illustration of the Centralised-Control Protocol            | 44         |

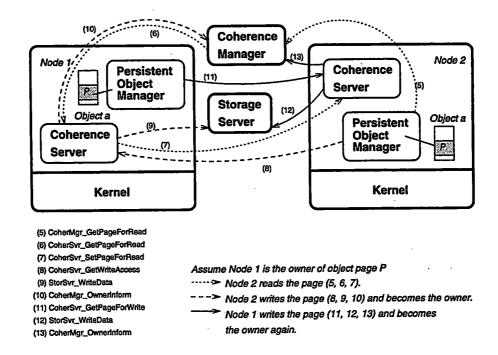

| 4.5 | Illustration of the Distributed-Control Protocol            | <b>45</b>  |

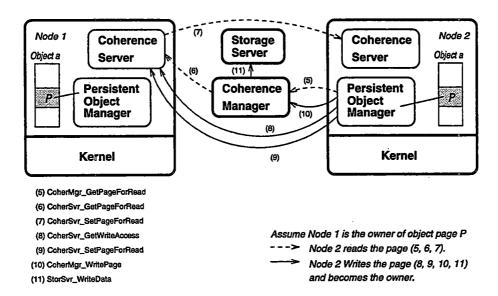

| 4.6 | Illustration of the Write-Update Protocol                   | 46         |

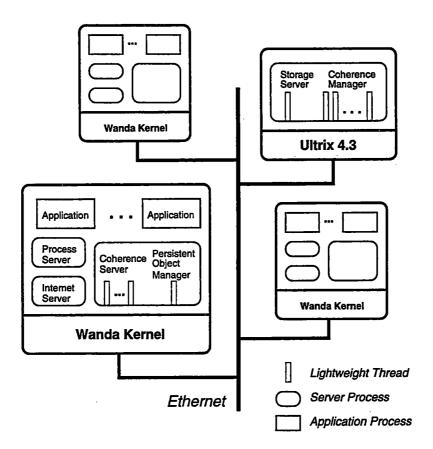

| 6.1 | Prototype Configuration                                     | 56         |

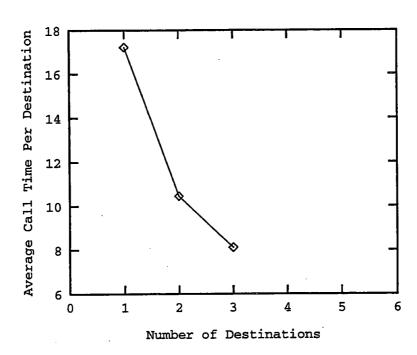

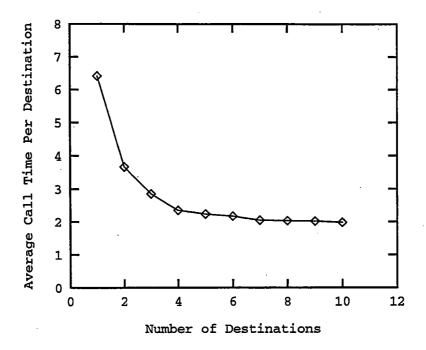

| 6.2 | Speed-up for One-to-Many Communications on Wanda            | 58         |

| 6.3 | Speed-up for One-to-Many Communications on Ultrix           | 59         |

| B.1 | VMM and POM Interaction Protocol                            | 110        |

## **List of Tables**

| 6.1  | Simple RPC vs MultiRPC for One Recipient 5                          | 7 |

|------|---------------------------------------------------------------------|---|

| 6.2  | Performance of MultiRPC on Wanda 5                                  | 7 |

| 6.3  | Performance of MultiRPC on Ultrix 58                                | 8 |

| 6.4  | Performance of A Local Roundtrip IPC 60                             | 0 |

| 6.5  | Time to Serve A Page Fault and Invalidate A Page 6                  | 0 |

| 6.6  | Fetching a Page from the Storage Server 6                           | 1 |

| 6.7  | Fetching a Page for Read in the Centralised-Control Protocol 6      | 1 |

| 6.8  | Fetching a Page for Write in the Centralised-Control Protocol 69    | 2 |

| 6.9  | Fetching a Page for Read in the Distributed-Control Protocol 68     | 3 |

| 6.10 | Fetching a Page for Write in the Distributed-Control Protocol 68    | 3 |

| A.1  | Characteristics for Mapping Objects                                 | 6 |

| G.1  | Hardware Configuration for Performance Measurements 12              | 8 |

| G.2  | Simple RPC vs MultiRPC for One Local Recipient                      | 9 |

| G.3  | Simple RPC vs MultiRPC for One Remote Recipient12                   | 9 |

| G.4  | MultiRPC to Two Remote Recipients                                   | 0 |

| G.5  | MultiRPC to Three Remote Recipients                                 | 0 |

| G.6  | Simple RPC between Wanda and Ultrix on a DECStation 13              | 1 |

| G.7  | MultiRPC from Ultrix on DECStation to Wanda                         | 1 |

| G.8  | Page Fault, Invalidation, Roundtrip IPC and System Call 13          | 2 |

| G.9  | Fetching a Page from the StorSvr                                    | 3 |

| G.10 | Fetching a Page for Read in the Centralised-Control Protocol 13     | 3 |

| G.11 | Fetching a Page for Write in the Centralised-Control Protocol 13    | 4 |

| G.12 | Fetching a Page for Read in the Distributed-Control Protocol 13     | 4 |

| G.13 | Fetching a Page for Write in the Distributed-Control Protocol $$ 13 | 5 |

## Glossary

This list defines abbreviations used in the text. Each entry ends with the number of the page on which the term is introduced.

**ACL**

Access Control List (24)

API

Application Programming Interface (12)

ATM

Asynchronous Transfer Mode (4)

**COMMOS**

Coherent Memory-Mapped Object System (1)

CoherSvr

Coherence Server (24)

CoherMgr

Coherence Manager (27)

**CSCW**

Computer-Supported Cooperative Work (93)

DSM

Distributed Shared Memory (2)

FFC

Flat File Custode (54)

LAN

Local Area Network (14)

**LWP**

Light-Weight Process (50)

MMU

Memory Management Unit (24)

**MSSA**

Multi-Service Storage Architecture (24)

POM

Persistent Object Manager (24)

**ProcSvr**

Process Server (29)

RAM

Random Access Memory (4)

RPC

Remote Procedure Call (12)

StorSvr

Storage Server (49)

**SVM**

Shared Virtual Memory (12)

**VMM**

Virtual Memory Management (23)

## Chapter 1

### Introduction

This dissertation considers traditional approaches to virtual memory and storage management and observes their limitations, particularly in the emerging distributed computing environments. A coherent memory-mapped object system (COMMOS) architecture is then proposed to overcome these limitations.

#### 1.1 Motivation

Distributed systems, which consists of workstations connected by different types of networks are emerging as the mainstream architecture of computing. The decrease in cost of physical memory and advances in hardware, such as the widening of the address space and the increase of network speed, have led to new thinking in software design. At the same time, microkernel architectures have emerged to ease the engineering of operating systems and to facilitate the development of higher levels of software.

The traditional approach to virtual memory and storage management is based on the two-level store architecture. It provides an interface defined by programming languages to access conventional memory segments and another interface defined by the file systems to access persistent data residing in secondary storage. The fact that there are two different views of volatile data and persistent data causes inconvenience to programmers and inefficiency for constructing software systems. The two-level store architecture also compromises operating system efficiency because of mandatory data copying and unnecessary user/kernel boundary crossings (or context switches in the microkernel architecture). Also limitations exist when database management systems are

built on top of this kind of memory and storage architecture.

In a wide address space architecture, distributed shared memory (DSM), an abstraction used for sharing data between processes in computers that do not share physical memory, is becoming increasingly attractive because it is easier to program than a message-passing abstraction. Distributed file systems rely on caching at clients to improve their performance. The cache coherency problem is common to these two paradigms. Current DSM systems and distributed file systems typically provide only one coherence protocol. There exists a potential mismatch between the supplied protocol and some applications and it is desirable that a more flexible approach should be employed.

Memory mapping provides a uniform view of both volatile and persistent data. It also provides better performance for accessing persistent data because information copying is no longer mandatory and the number of user/kernel boundary crossings (or context switches in microkernel architectures) is reduced. This is not a new technique but it was not very successful in the early days. The main reason is that there was no suitable hardware technology and software environment. It is now time to reexamine this technique and to explore whether it can be used, with careful design, to overcome most of the problems outlined above.

#### 1.2 Research Goal

The major goal of this research is to explore whether it is feasible to provide an integrated virtual memory framework which is general enough to support a range of higher level distributed system abstractions and distributed applications and which is flexible enough to meet different requirements for these abstractions and applications at a reasonable cost.

The approach taken combines the microkernel, memory-mapping and typed memory object principles to provide a minimum of support for distributed computing environments with the aim of making virtual memory and storage management integrated, flexible, and easy to use. It is proposed that virtual memory management cooperate with other services in an open system in order to satisfy all application requirements without sacrificing performance. Virtual memory and storage management are integrated by using the memory-mapping technique.

It is important to support both memory coherency and concurrency control in

a distributed system. However, it is recognised that no single universal coherence protocol can meet the requirements of all applications. In this work, the coherence server is separated from the external pager so that a variety of coherence protocols can be provided in a generic interface. Applications can advise the system which protocol would be used while a default protocol is supported. The low-level cache coherency control is integrated with the high-level concurrency control so that the system-wide object coherency and synchronisation are realised without severely impacting the system performance.

This dissertation shows how this goal can be achieved by a prototype implementation of COMMOS and demonstrates that the approach is feasible.

#### 1.3 Dissertation Outline

Chapter 2 reviews the technological developments of hardware and software and discusses the limitations of existing approaches to memory and storage management when they are applied to distributed computing environments. It also gives a brief introduction to memory-mapping techniques. This chapter concludes that a new approach to integrate main memory with secondary storage and local memory with remote memory is desirable.

Chapter 3 discusses requirements and outlines an architectural framework for the coherent memory-mapped object system (COMMOS), including a brief description of those aspects not directly related to coherency control. A piece of previous work and its relation with COMMOS are also given.

Chapter 4 focusses on the design of the COMMOS coherence mechanism and Chapter 5 gives the details of the prototype implementation. Chapter 6 evaluates the performance of the prototype implementation and provides the experimental evidence for some of the discussions in Chapter 2 and Chapter 4.

Chapter 7 illustrates the use of COMMOS by discussing how to build a C++ class library to support distributed persistent programming.

Chapter 8 reviews the systems and projects which are closely related to this work and compares their approaches to important issues with those of COM-MOS.

Chapter 9 concludes the dissertation by summarising the work and suggesting further research.

## Chapter 2

## Background

#### 2.1 Introduction

Computer technology has been developing very rapidly. The performance of modern microprocessors is increasing at about 35% per annum [Bacon93] while the price is constantly decreasing. Distributed systems consisting of workstations connected by different types of networks are becoming a great challenge to traditional mainframe architectures.

Several recent developments will have significant impact on future computing environments. First, the cost of random access memory (RAM) is The memory size of personal workstations quadruples every three years and hundreds of megabytes of physical memory will be commonplace [Bacon93, Needham91]. Second, wide address space machines. such as the 64-bit DEC Alpha [Sites92], HP PA-RISC [Lee89] and MIPS R4000 [Kane92] are becoming ubiquitous. These wide-address space architectures are interesting, not only because they allow applications to use almost arbitrarily large files and data structures, but also because they may fundamentally change the way operating systems are structured. Third, the speed of computer networks is increasing dramatically. Transmission rates of gigabits per second will soon be widely available. Even the components of a workstation might be connected by high speed ATM networks [Hayter93]. New thinking is necessary on how to build software, especially operating systems, to fully make use of all these new developments and to provide users with more functionality and better performance.

#### 2.1.1 Microkernels

An important trend in operating system design to meet these technological developments is to restructure the operating system as a modular set of system servers sitting on top of a lightweight microkernel [Needham91, Gien91], rather than using the traditional monolithic structure. Conventional monolithic operating systems have become large and unwieldy. They are difficult to comprehend, develop and maintain. Meanwhile, distributed systems place different functions on different machines so not all operating system functions are needed in every copy of the operating system. This has resulted in a shift towards microkernels. The new approach promises to help meet systems and platform builders' needs for a sophisticated operating system structure that can cope with growing complexity, new architectures and changing market conditions. It maintains that the kernel should provide only the most basic functionality, with the bulk of the operating system services available from user-level servers. The microkernel provides system servers with generic services independent of a particular operating system, which typically include [Bacon93, Tanenbaum92, Coulouris94, Gien91]:

- low-level process management and scheduling;

- minimum memory management;

- simple inter-process communication facilities;

- I/O device management.

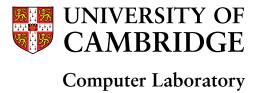

This combination of elementary services forms a base which can support all other system-specific functions. These can then be configured into appropriate system servers, managing the other physical and logical resources of a computer system, such as files, devices, much of memory management and high-level communications handling. The system servers usually run as user-level processes. Figure 2.1 shows the difference between conventional monolithic kernels and modern microkernels. In a monolithic kernel architecture, all the system services such as file service and network communication service run in the kernel and all kernels have the same configuration. By contrast, in a microkernel architecture, the high-level system services run at the user-level and different nodes may be configured in different ways.

The major advantages of a microkernel system are its openness and its ability to enforce modularity behind memory protection boundaries. There is a welldefined interface to each service and every service is equally accessible to every

Figure 2.1: Monolithic Kernel vs. Microkernel

client. In addition, it is easy to implement, install and debug new services, since adding or changing a service need not stop the system and booting a new kernel, as is the case with a monolithic kernel. The price/performance and reliability can also be enhanced because it is easier to incorporate new hardware connection technologies and new processors than in monolithic kernel architectures. A potential disadvantage is that the performance of accessing services at user-level might not be as good as accessing services in the kernel in a monolithic kernel system because of message handling, kernel boundary crossing and context switching overheads [Zahorjan91, Bricker91, Coulouris94].

Since being introduced by [Lampson79], microkernel architectures have been the subject of a great deal of operating system research, illustrated by projects such as Amoeba [Mullender90] (Vrije University and Centre for Mathematics and Computer Science, the Netherlands), Chorus [Rozier88] (Chorus Systems, France), Mach [Accetta86] (Carnegie Mellon University, USA), Spring [Hamilton93] (Sun Microsystems Laboratories Inc, USA) and the V System [Cheriton88a] (Stanford University, USA). It is likely that microker-

nel systems will gradually come to dominate the distributed systems scene, and monolithic kernels will eventually vanish or evolve into microkernels.

Memory and storage management play an important role in operating systems and have a significant effect on the system performance and usage. There are still a lot of issues in this area to be explored in order to provide users more functionality and better performance in future distributed systems. In the following sections, existing virtual memory and storage management are examined and the advantages of mapping objects into virtual memory address spaces are discussed.

# 2.2 Existing Virtual Memory and Storage Management

This section firstly examines the existing memory and storage management approaches and then considers their distributed paradigms, namely distributed shared memory (DSM) and distributed file service.

#### 2.2.1 Two-Level Store Interface

Currently, users of most operating systems use one interface defined by the programming language to access conventional memory segments and another interface defined by the file service to access objects residing in secondary storage.

#### **Virtual Memory**

Since its introduction in the Atlas computer system [Fotheringham61] in 1961, virtual memory has been employed in the design of memory management of most operating systems. User programs are allowed to use a large contiguous set of virtual addresses, called a virtual address space, which may be larger than the total amount of physical memory available on the computer. Portions of this virtual address space are loaded into physical memory as they are needed and the rest are kept on the backing store. The physical memory and the virtual memory are usually divided into segments and each segment may be further divided into fixed-size pages, which are the smallest units for transferring to and from the backing store. The physical memory is in fact

the cache of the virtual memory. Because the price of RAM is decreasing significantly, some suggest that by purchasing enough physical memory, virtual memory will not be needed in the future. However, this solution will not work for timesharing systems or for applications, such as databases, whose memory usages scale with CPU speed and scale faster than the decreasing rate of RAM price [Krueger93]. Meanwhile, because a virtual memory implementation may need to use a backing store on a separate computer from the one that contains the main memory and it is possible to share data which is simultaneously mapped into the address spaces of processes residing at different computers, virtual memory is of considerable interest as an aspect of the design of distributed operating systems.

In most of the commonly used systems, virtual memory segments are used by programming languages to store volatile information and the format of volatile information is different from that of persistent information stored in the file service.

#### File Service

Traditionally, information which needs to persist is stored on disks and other external media in units called *files*. The part of the operating system dealing with files is known as the *file system*. To access long-term objects stored in such a file system, data is first fetched to the system I/O buffers which typically reside in kernel space and is then copied to the users' address spaces as read operations are executed. On writing, data is copied from the users' address spaces to the system I/O buffers before it can be written to the secondary storage. If lots of small data items are to be accessed one by one, many unnecessary user/kernel crossings are involved. When accessing large amounts of data, on the other hand, significant extra time has to be spent on copying data between I/O buffers and the users' address spaces. Data copying and boundary interactions between kernel and user space make the system inefficient.

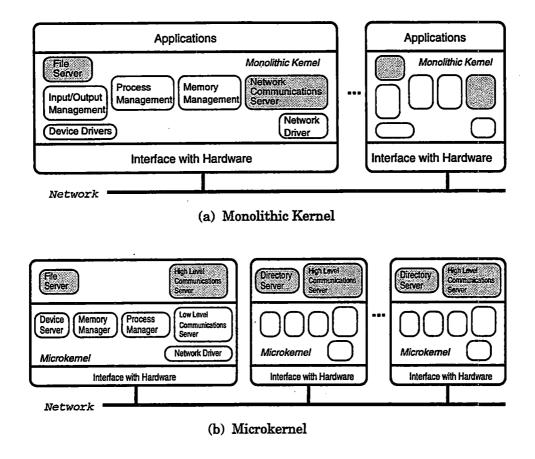

In the case that the file service runs as a user-level process in a microkernel operating system, if this traditional access model is still adopted, the overall performance becomes unacceptable. The major problem appears to be the need for costly context switching [Welch91]. Figure 2.2 shows file access using the traditional model in both monolithic kernel and microkernel operating systems. In order to perform comparably to monolithic systems, a microkernel system must either make a context switch much faster, or somehow avoid it

Figure 2.2: File Access in Monolithic Kernels and Microkernels

wherever possible. Data movement must also be carefully designed to avoid extra copying of data. [Dean92]

#### **Database Systems**

Conventional database systems usually allocate buffer pools within their own virtual address spaces and provide their own buffer management facilities [Bacon93, Korth91, Ozsu91, Traiger82, Stonebraker81].

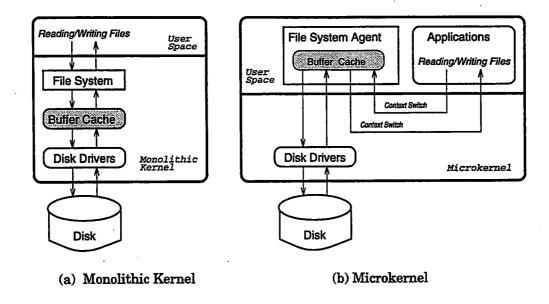

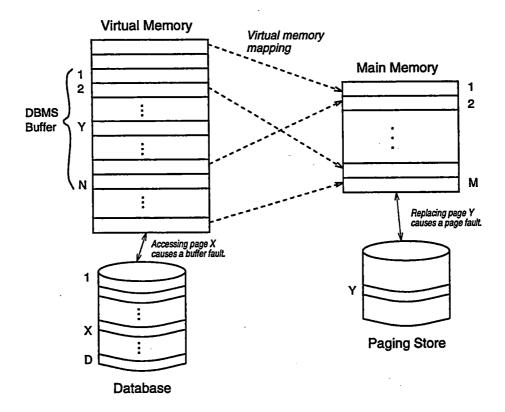

The overhead for data access in such a system is high. Figure 2.3 illustrates the data movement path in a DBMS system implemented on top of a two-level store system. Data pages are copied into a file buffer and then into a DBMS buffer before data fields are copied into an application program's variables. On writing, the path is traversed in reverse order.

Accessing the DBMS buffers may not only cause buffer faults to bring in data pages, but may also cause memory faults since the buffer page may not be mapped to a page frame and there may not be any free frames. This phenomenon is commonly called the *double paging* [Ozsu91, Chew92]. For example, if a DBMS is accessing page X which is not in its buffer pool, the buffer manager accesses the secondary storage where the database is located and then maps page X onto a virtual buffer page. This may involve replacing some page Y. However, at the virtual memory level, the frame corresponding

Figure 2.3: Buffer Management in DBMS

to Y may happen to be paged out. The virtual memory manager may have to service a real memory page fault to bring in the frame Y and then write it back to the permanent secondary storage (see figure 2.4).

There are also some other disadvantages. First, unmodified pages need to be written to the paging store at least once instead of simply being discarded. Data may be redundantly stored both in the database and the paging store. Second, double paging may lead to double paging anomaly [Goldberg74], where a significant increase in the number of page faults occurs with an increase in buffer pool size without a corresponding increase in physical memory. Besides, access control and address translation are accomplished in software. Available virtual memory hardware is not exploited.

#### **Persistent Programming**

Traditional programming languages provide facilities for the manipulation of data whose lifetime does not extend beyond the activation of the program. If data is required to survive a program activation some file I/O or database management system interface is used. Two views of data follow from this. Data can be classed as either short term and would be manipulated by the program-

Figure 2.4: Double Paging Problem

ming language facilities or long term in which it would be manipulated by the file system or the database management system. The mapping between the two types of data is usually done in part by the file system or the DBMS and in part by explicit user translation code. The explicit user translation code has to be written and included in each program. There is usually a considerable amount of code, typically 30% of the total in many programs concerned with transferring data to and from files. This includes the code concerned with the explicit movement of data between main and backing store and the code required to change the representation of the data for long term preservation and restoration. An example of the former is input and output code and of the latter is code to flatten and reconstruct a graph before and after output and input respectively. This is unsatisfactory because of the time taken in writing this mapping code and also because the quality of the application programs may be impaired by the mapping. Frequently the programmer is distracted from his or her main task by the difficulties of understanding and managing the mapping [Atkinson83, Morrison90].

Persistent programming [Atkinson83] is a relatively new concept which makes data intensive application programming much easier. The idea is that data in a system should be able to persist for as long as it is required. It eliminates the differences between the DBMS and programming language models of data. Persistent programming systems support long lived data objects of arbitrary complexity. Such data objects may not only outlive instantiations of the program that created them, but also outlive versions of the program, or even the useful life of the program in all its versions.

To date, most persistent programming systems have been constructed above conventional operating systems. Implementors of persistent programming languages have to take care of the data movements and translations by themselves. If the two interfaces to volatile and persistent data can be harmonised in the operating system the language implementors can access objects in a unified manner without worrying about the need to move objects to and from secondary storage.

#### 2.2.2 Distributed Shared Memory

In a typical distributed environment, since there is no shared physical memory, language-level user processes on different network nodes usually communicate with each other by using message passing or its higher level abstraction — remote procedure call (RPC) [Birrell84]. With a message-based application programming interface (API), programmers have to be concerned with transferring control between processes even if the interaction between these processes is limited to sharing data. A very simple situation is programmed in a complicated way. Second, the regular control flow of the system is mixed with the exchanges of control that implement the sharing of data, and the result is a system that is hard to debug. Finally, it is difficult and inefficient to pass complex data structures via message passing [Bisiani88, Herlihy82].

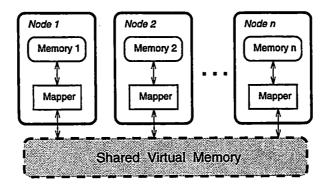

A distributed shared memory abstraction [Coulouris94, Hemmendinger92, Nitzberg91] has been proposed to cope with this problem. In this model communication recedes into the background. Programmers are spared from the concerns of message passing when writing applications that might otherwise have to use it. Applications see a single shared virtual address space as if shared memory were provided by the hardware or shared data objects. The former model is called shared virtual memory (SVM) [Li86].

Figure 2.5: Shared Virtual Memory

Shared Virtual Memory SVM extends the idea of virtual memory to a distributed system, providing a single virtual address space which is shared among all nodes in a multicomputer system, as illustrated in figure 2.5. Any node in the system can access any memory location in the address space. Application programs can use the SVM in the same way as they use a traditional virtual memory, except that processes can run on different machines in parallel [Li86]. The memory mappers in a SVM system implement the mapping between local memories and the shared virtual address space. They maintain the coherency of the address space. In a system which supports strict memory coherency, the value returned by a read instruction is always the same as the value written by the most recent write instruction allowed to complete to the same address. The shared virtual address space is typically partitioned into pages. Each memory mapper views its local memory as a big cache of the shared virtual address space for its associated node. A memory reference may cause a page fault when the page containing the memory location is not in a node's current physical memory. To serve the page fault, the memory mapper retrieves the page from either the swap space (or paging store) in secondary storage or the memory of another node.

Shared Data Object Model Shared data object systems provide sharing at the level of user data structures rather than at the system level as SVM does. Shared data objects are supported by a language that may have common high-level features such as hierarchical organisation of data. Two approaches to shared data objects are Linda [Carriero89] and Orca [Bal93]. Linda provides a flat logically shared address space within which data structures are built out of primitive objects, so that a structure may be composed of many elements that are distributed by the compiler and run time system. Orca is a high-level

language whose run-time support manages the distribution of objects, providing structured distributed shared memory. The former provides distributed data structures that may be spread across physical memory on many nodes; the latter provides distribution of data structures.

DSM permits and encourages architecture-independent programming, using a memory model similar to that used by conventional programming languages. Moreover, object migration in a SVM is potentially easier than that in a message-based system. Much research in this area has been carried and has been successful to some extent. To date, DSM is still in the stage of research rather than practical use. The major fear is that the overhead involved in maintaining memory coherency over a local area network (LAN) is much higher than in a shared memory multiprocessor system. Also scalability remains an uncertainty.

Recent advances in network technology have yielded nearly an order of magnitude improvement in both latency and throughput. This means that the performance gap between loosely-coupled and tightly-coupled multiprocessors is not as dramatic as it once was. As a result, the overhead of maintaining memory coherency in DSM will not be a severe problem in future distributed environments. Also, the overhead can be reduced by integrating the low-level coherency control with the high-level concurrency control as discussed in Chapter 4.

The major factor which affects the scalability of DSM is the number of messages needed to keep DSM coherent. This factor is in turn affected by the access patterns of the applications to the DSM and the coherence protocol used. Most of the existing SVM systems to date, which provide a flat global address space abstraction, are unstructured and use a single memory coherence mechanism. This form of coherency control causes the coherence mismatch between the access patterns and the coherence protocol (see section 3.4 for details) and hence this type of system can not scale well. The shared object model is structured and potentially more flexible. However, almost all of the existing shared data object systems are implemented as run time libraries and are sometimes combined tightly with a specific programming language. They are not as readily provided for shared memory-based programming languages as the SVM. Furthermore, users of both kinds of DSM still see two different interfaces for volatile and non-volatile objects. Systematic and architectural support for coherent persistent shared data objects is desirable.

Figure 2.6: Various Approaches to Caching in Client Memory

#### 2.2.3 Distributed File Service

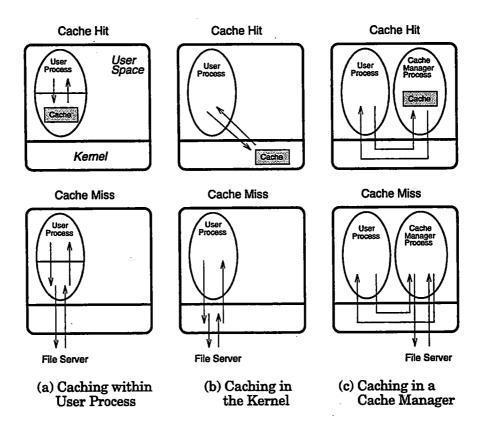

Caching of data at clients has been proven the architectural feature that contributes most to performance in a modern network or distributed file system [Coulouris94, Satyanarayanan93, Nelson88]. Caching in the clients' main memory provides best performance since it reduces the number of I/O accesses and network accesses. There are usually three approaches to implement the clients' main memory caching [Tanenbaum92] as shown in figure 2.6:

- cache files directly inside each user process' own address space.

- put the caches in the kernel.

- maintain the caches in a separate user-level cache manager process.

In the first approach, the cache is typically managed by the runtime library. When files are accessed, the library keeps the most heavily used ones around, so that when a file is reused, it may already be available. Although this scheme

has an extremely low overhead, there may exist multiple copies of the same file cache in different processes on the same client node. The disadvantage of the second scheme is that a kernel call is needed in all cases. Furthermore, it does not fit the microkernel philosophy. The third way of caching keeps the kernel free of file system code and is easier to program. As discussed before, however, it introduces more context switches. Besides, double paging may occur if the cache manager process runs on an operating system with virtual memory.

Client caching introduces inconsistency into the system. In most such systems, it is the file server which is responsible for maintaining coherence between different client caches of the same file and guaranteeing concurrency control [Nelson88, Satyanarayanan93, Coulouris94]. The file server may become a bottleneck when the system scales up.

#### 2.2.4 Conclusion

The mandatory data copying and unnecessary user/kernel boundary crossings introduced by a traditional file system cause inefficiency. This is exacerbated in a microkernel architecture where most of the user/kernel boundary crossings become context switches. The difference between the existing virtual memory and storage systems' interfaces causes inconvenience for application programmers and impairs the quality and productivity of software constructions. Although persistent programming can solve this problem it is difficult to implement persistent programming languages in a productive and efficient way without operating system support. Sharing data between processes on different network nodes is difficult if only the low-level message passing interface is provided. DSM is attempting to overcome this problem but this is still not ideal. Finally, although caching of data at clients improves the performance in distributed file systems, how to maintain the client cache more effectively is still worth exploring and the file server might become a bottleneck in a large system. These observations lead to the conclusion that some more comprehensive operating system support for distributed programming is desirable.

#### 2.3 Memory-Mapped Object Management

As discussed in the previous section, accessing files in a file system is cumbersome and inconvenient, especially when compared to accessing main memory. Starting with Multics [Organick72], some operating systems have provided a way to map files into the address space of a running process. After being mapped into the address space, data stored in files can be addressed directly by a processor and hence referenced directly by any computation. In a typical high-level language, the opened file appears as an array of bytes. The underlying system is responsible for fetching data from secondary storage as the array is accessed and for writing modified data to permanent store.

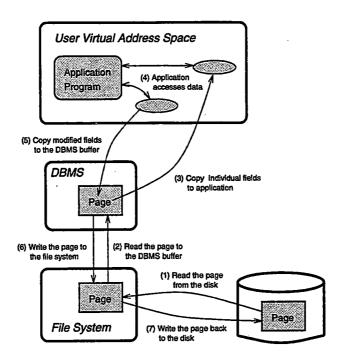

The fundamental advantage of direct addressability is that information copying is no longer mandatory. This means, for example, that core images of programs need not be prepared by loading and binding together copies of procedures before execution. Also, partial copies of data files need not be read, via requests to an I/O system, into the user address spaces for subsequent use and then returned, by means of another I/O request, to their original locations. Instead the processor executing a computation can directly address just those required data items in the original version of the file. One of the examples is shown in figure 2.7. In the two-level store approach, when a user attempts to assign values to the persistent object date\_object, memory has to be allocated for the local variable d and values are assigned to it. Then the system call write is invoked and the control is changed from the user space to the kernel (or from the user process to the file system agent process in a microkernel architecture). After that, data is copied from the local variable d to the system I/O buffer and the control is changed back to the user space. In the case of reading, a system call read is invoked and the control is changed from the user space to the kernel (or from the user process to the file system agent process) to copy the data from the system I/O buffer to the local variable d. Control is then changed back to the user space where the data is consumed. By contrast, in the memory-mapping approach, if the page is already in the main memory, the persistent object date\_object can be written or read directly without user/kernel boundary crossing and mandatory data copying. This shows that memory-mapping techniques can be used to improve the system performance since mandatory data copying is avoided and the number of user/kernel crossings or context switches is reduced.

The file store and the backing store for memory management are unified. Once the mapping is set up by the operating system, pages may be read directly from the file and updated pages may be written back to the file. The

```

struct date {

struct date {

char weekday[10];

char weekday[10];

int day;

int day;

char month[10];

char month[10];

int year;

int year;

};

void write_routine()

void write_routine()

int fd;

struct date *dp;

struct date d;

dp = mmap("date_object", RDWR);

fd = open("date_object", RDWR);

strcpy(dp->weekday, "Monday");

strcpy(d.weekday, "Monday");

dp->day = 6;

d.day = 6;

strcpy(dp->month, "June");

strcpy(d.month, "June");

dp->year = 1994;

d.year = 1994;

munmap("date_object");

write(fd, &d, sizeof(d));

close(fd);

void read_routine()

void read_routine()

int fd;

struct date *dp;

struct date d;

dp = mmap("date_object", RDONLY);

fd = open("date_object", RDONLY);

read(fd, &d, sizeof(d));

printf("%s %d %s %d\n", d.weekday,

printf("%s %d %s %d\n", dp->weekday,

d.day, d.month, d.year);

d->day, d->month, d->year);

close(fd);

munmap("date_object");

}

(b) Memory-Mapping System

(a) Two-Level Store System

```

Figure 2.7: An Example of Accessing a Persistent Object

problems of storage redundancy and the double paging in database systems are eliminated.

Direct addressability also hides the existence of the memory hierarchy and makes the system, rather than the users of the system, responsible for the movement of data between main memory and secondary storage. This kind of access to information promises a very attractive reduction in program complexity for the programmer. In a homogeneous system, data can be stored in their main memory format and hence there is no need to convert from the secondary storage format to main memory format and vice versa. This can simplify the job of implementing a persistent programming language and other

application programs. In a heterogeneous system, unfortunately, there exists the problem of different machine representations of data objects. The first problem goes beyond the byte order problem, since different processors are free to assign any given meaning to any given sequence of bits. A more difficult problem arises from software data types. Modern programming languages allow higher level types to be built on top of hardware types, for instance, in composing record structures with diverse component types. Quite often, the language definition does not specify how these types should be mapped to the hardware types, and the compiler is free to define this mapping. A well known consequence is that the different fields of a structure in the C language may be allocated at different offsets by different compilers, sometimes even among compilers for the same machine architecture. Solving the heterogeneity problem is not easy because it requires that the server has knowledge of the application's data types. This leads to undesirably close links between the application's runtime system and the compiler. Fortunately this problem can be separated into two categories: hardware data types such as integers and software data types like C structures. A general purpose server can solve the former problem and can be extended to cope with the second class of types [Forin88].

Since all data are accessed via the same interface, a single model of protection may be employed. This may be based purely on type security or may be hardware supported in order to provide multi-lingual support [Morrison90]. The user need only be concerned with one mechanism as distinct from the multi-level protection involving processes and files on conventional systems.

Finally, in a distributed environment, file mapping is in effect caching files at clients. The cache can be accessed directly within user processes without the overhead of user/kernel boundary crossings or context switches. With proper concurrency control, the system need not to maintain multiple copies of data as in the first file caching scheme shown in figure 2.6.

Despite the advantages discussed above, persistent programming language and database implementors have repeatedly rejected the idea of using the mapped file facilities offered by operating systems and have chosen to manage buffering and disk storage themselves. The main reasons are as follows [Shekita91, Tanenbaum92]:

Operating systems typically provide no control over when the data pages

of a mapped file are written to disk. The major concern here is that

the file contents may be changed as the program runs and special steps

must be taken, either by the programmer or by the system, to ensure

that sufficient information is retained for restarting after a failure. The overheads involved might be expensive. On the other hand, data may not be written back into the disk even after the program finishes. It might cause data loss if system failure occurs.

- Operating systems only know the length of a file at page granularity.

- The virtual address space provided by mapped files, usually limited to 32 bits, is too small to represent a large file or database.

- Page tables associated with mapped files can become excessively large [Stonebraker81].

With the right operating system support, however, it is possible to control when the pages of a mapped file are written to disk. in most of the database applications, shadow paging and write ahead log approaches [Traiger82, Korth91] are employed in order to be able to recover from system failure. They can still be used in memory-mapped object systems. For the second problem, the programmer can easily know how many bytes have been written to the file in most cases. Thirdly, the emerging 64-bit address space is extremely large. Even if memory is allocated at the rate of one gigabyte per second and never deallocated, the address space will last for 500 years before it is used up [Chase93]. In any case, it is clear that the address space size will continue to grow over time. Large address spaces and relatively slow disks combine with programming language developments to make this approach increasingly attractive [Bacon93]. Also, as the cost of RAM decreases, large page tables will become less of a concern. Meanwhile, inverted page tables [Bacon93] and guarded page tables [Liedtke94a] techniques can be used to reduce the page table size. Inverted page tables which can be found in the HP Precision Architecture may become more common with the increase in memory sizes. In this scheme, a single main memory page table, which is organised as a hash table, is used by the operating system to record which page of which process occupies each page frame of physical memory. Since physical main memory is likely to be smaller than virtual memory this is potentially economical in both space and searching time compared with holding a page table per process. In the guarded page tables scheme, each page table entry is supplemented by a variable length bit string called guard. A page table entry is selected by the highest part of the virtual address upon each transformation step in the same way as with the conventional multi-level page table method. If the guard in the entry is a prefix of the remaining virtual address, the translation process either continues with the remaining postfix or terminates with the postfix as the page offset. In a

sparsely occupied huge address space, this scheme reduces the size of memory occupied by page tables and the number of address transformation steps.

Though memory-mapped interfaces have been implemented on several operating systems both in the traditional monolithic systems such as Multics and Sun OS and modern microkernels like Mach [Accetta86], Chorus [Rozier88] and the V system [Cheriton88a], few of them give added functionality to the user as they do not provide the facilities for users to easily implement logical abstractions [Mapp91]. This has been explored in [Mapp91] by providing a typed interface to the virtual memory manager. His work was mainly concerned with a single machine. How to extend this approach to structure virtual memory in order to support distributed computing environments, especially how to maintain coherency between mapped copies of the same object on different nodes and how to guarantee concurrency control, are worth investigating.

#### 2.4 Summary

In this chapter, new developments both in hardware and software were presented, the limitations of the existing memory and storage management approaches were discussed and the memory mapping techniques were examined. This leads to the conclusion that a new approach to virtual memory and storage service, which integrates main memory with secondary storage and local memory with remote memory, to support the emerging distributed computing environment is worth investigating and the memory mapping technique could be used with a carefully designed framework.

## Chapter 3

## **Architecture Framework**

As discussed in the previous chapter, a new approach is desirable to integrate virtual memory with secondary storage and local memory with remote memory in distributed computing environments. This chapter proposes an architectural framework to meet such requirements.

#### 3.1 Introduction

The terms type and object are frequently used in this dissertation. Here type means different logical data abstractions managed in different ways, such as executable code, data, stack, file and persistent object types. This provides the flexibility for a number of aspects of virtual memory management and persistent object management, such as the implementation of paging algorithms and object coherence protocols.

An **object** is defined as a logical entity which is an instance of a *type* and can be mapped into a contiguous region of a process virtual address space. When an object is mapped, it can be read or written by simply reading or writing an address location within the process address space corresponding to the offset of the byte in the object. If the object is shared between multiple processes, every modification made by any of the processes is immediately visible to the others on its completion.

The use of the term "object" here does not imply any sophisticated concept used in object-oriented programming languages. It is solely an array of uninterpreted bytes, or more precisely, an array of pages, possibly associated with some backing secondary storage, which can be used to contain and enclose

Figure 3.1: The COMMOS Layers

language-level objects. Class code can be bound to it by an object-oriented programming language runtime library as illustrated in Chapter 7. The term system-level object is sometimes used in this dissertation to avoid confusion with language-level object.

Processors and network connections may fail by crashing. As pointed out by [Bacon93], failure transparency is expensive and hence is not desirable to be supported in the low-level architecture. When a failure occurs, an exception is raised and passed to the client affected. It is up to the clients to react in the face of failures.

#### 3.2 Object Management Layers

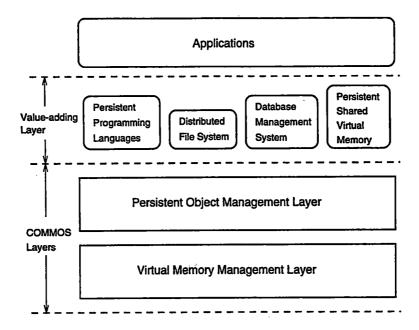

Object management in COMMOS is divided into two layers: the basic virtual memory management layer and the persistent object management layer (see figure 3.1). Above these layers, there may be other value-adding clients, such as persistent programming languages, database management systems, distributed file systems and persistent shared virtual memory.

The virtual memory management (VMM) layer manages the local memory and is further divided into machine-dependent and machine-independent parts.

The machine-dependent part is concerned with managing the memory management unit (MMU) hardware and catching all page faults. The machine-independent part is concerned with managing address maps, satisfying the page faults for zero-filled objects and interfacing the virtual memory management layer with the persistent object management layer.

The persistent object management layer manages the persistent objects and consists of three components: **persistent object managers** (POM), **coherence servers** (CoherSvr) and a **public interface**. The POM is in charge of the data movement between the main memory and the secondary storage. Each object type has only one corresponding POM on each node while a POM can manage one or more object types. The CoherSvr is concerned with the object coherency control and cooperates with the POM to maintain the object coherency in a distributed system. There is only one CoherSvr for each coherence protocol while a CoherSvr can manages one or more coherence protocols. The reason for the separation of the CoherSvr from the POM will be discussed in Section 3.4. Finally an interface is provided for its clients to manipulate objects.

#### 3.3 Object Naming and Protection

A global naming scheme is desirable in order to make the persistent objects visible in any node of the system. A global name is globally unique and location independent, and can be used to refer to an object from anywhere in the distributed system. A naming scheme with fixed-length bit pattern identifiers, such as the one used in the *multi-service storage architecture* (MSSA) [Lo94] is of preference because it is convenient to manage.

In order to protect objects from unauthorised client accesses, the persistent object manager needs to know the access rights of clients to the objects it manages. This information can be stored as an access matrix [Lampson71], in which the rows represent the clients and the columns represent the objects. The access rights that a client holds for an object can be found at the intersection of the corresponding row and column. This matrix, however, is too large and sparse to store. An alternative way to represent the access matrix is to associate each object with a list containing all the clients that may access the object with their access rights. This list is called an **access control list** (ACL). The other way of slicing up the matrix is to associate each client with a list of objects that may be accessed with an indication of which operations

are permitted. This list is called a **capability list** and the individual items on it are called **capabilities**. The ACL method is chosen in this design but capabilities approach could also be used.

#### 3.4 Concurrency and Coherency Control

Allowing objects to be mapped into process virtual address spaces on different network nodes at the same time introduces the object coherency problem. One way to ensure object coherency is to allow multiple readers to read a specific object fragment at the same time but writers must have exclusive access [Bacon93, Tanenbaum92]. This can be achieved by using locking.

If the system is concurrency transparent, clients need not be aware of the existence of other clients. When a process attempts to access a memory location, the system automatically acquires a lock for the corresponding memory unit on behalf of the process. However, if language compilers are not to be changed, at least some sort of preprocessors are needed to detect the memory accesses and to acquire locks on the clients' behalf. More importantly, the semantics of transparent locking is not well defined. By contrast, in an explicit locking scheme, clients are required to acquire locks when synchronisation is desired. By doing so, clients obtained better control over concurrent accesses of shared data. The explicit locking approach is adopted in this architecture framework.

Many protocols have been developed to tackle the system wide cache coherency problem both in distributed shared memory systems and in distributed file systems with client caching. Nevertheless, it is extremely difficult to have a single protocol which can perform well for different types of application. Two kinds of commonly used protocols, namely write-invalidate and write-update, are considered here. In the following discussion in this section, the page is assumed as the unit of coherency control. The list of nodes which have a valid cached copy of an object page for reading is called the copy set of the page. The node which has the most recent write access to an object page, and hence has the up-to-date page contents, is called the owner of the page. In writeinvalidate protocols, when a process attempts to write to an object page it has to instruct the copy set of the page to invalidate their caches before it can go ahead. Any subsequent read accesses from nodes other than the owner will cause a copy of the page to be shipped from the owner. In the write-update protocols, each modification to an object page is written through to the copy set.

In the case that the copy set is relatively stable and the page is accessed many times by each node, the write-update protocols will perform better. For example, if the size of the copy set is n, for each writing operation, n RPC calls are required in the write-update protocols while  $(2 \times n)$  RPC calls are needed in the write-invalidate protocols if the page is accessed again by all the nodes in the copy set after the updating. On the other hand, if the copy set changes dynamically, the write-invalidate protocols are expected to perform better since there is no need to ship data to those nodes which are in the copy set but which do not use the data in the near future.

The separation of the CoherSvr from the POM is proposed in this dissertation to overcome the problem of coherence mismatch. A CoherSvr can implement one or more coherence protocols while there is only one CoherSvr for each coherence protocol on each node. Working with the typed object principle, this coherence mechanism enables the clients to apply different protocols to different types of object or even to different individual objects so that they can choose the most suitable protocols for their applications. Dynamically adopting different coherence protocols to meet the change of the runtime circumstance is also possible. The design and implementation of this coherence mechanism are discussed in detail in Chapter 4 and Chapter 5.

#### 3.5 Persistent Object Management

There is a data structure to represent each object which is currently in use. These data structures form an **object table** which resides in the kernel but may be mapped into the address spaces of POMs and CoherSvrs. The interaction between a user thread and the POM is carried out via a simple interface and a set of events.

The interface for the POMs supports a number of functions, such as mapping the free page list into the POM's address space, registering with the system about managing an object type, getting the relevant characteristics of an object, and getting relevant data from the network storage server to serve page faults and then returning the results.

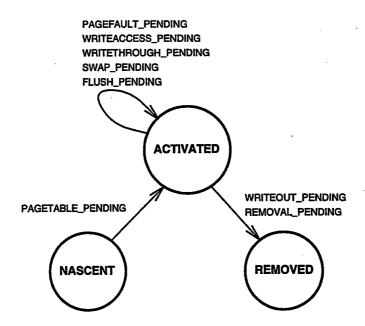

A process invokes the POM by triggering an event and then suspends itself until the POM replies. POMs handle various events which occur as objects are accessed (e.g. a page fault) or as operations are invoked by the client via the public interface. These include flushing modifications to the secondary storage, writing out changes when persistent objects are unmapped, swapping

out pages when they are selected by the paging algorithm to be removed from the main memory and reclaiming resources from a persistent object after it has fallen out of use. The details of the VMM interface and events handled by POMs are shown in Appendix B.

#### 3.6 Public Interface

This system is assumed to be used mainly by class library builders or high-level abstraction implementors. The public interface provides the facilities to map and unmap objects in an address space, to create and destroy objects, to flush modifications back to the secondary storage server and to grow or shrink objects. Multiple-reader/single-writer synchronisation is also supported. Interested readers are referred to Appendix A for the details of the public interface.

In order to support persistent programming and database applications, it is important that upon successful return of a request to write modifications to the backing store, the modifications have indeed been written. So the operations of flushing and unmapping an object should be synchronous. This means that the caller is blocked until the POM has completed the operation and indicates whether the operation is successful. The other important issue is that the clients should be allowed to choose whether to be blocked when acquiring a lock which can not be granted immediately.

#### 3.7 COMMOS Architecture

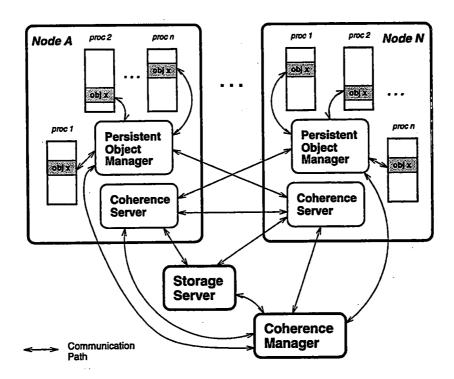

The coherent object management system consists of well-known global **coherence managers** (CoherMgr) and per node based **coherence servers** (CoherSvr). For each coherence protocol, there is one corresponding CoherMgr and multiple CoherSvrs, one per node. One set of CoherMgr and CoherSvrs may manage one or more protocols. When a persistent object is mapped onto a network node for the first time, the CoherMgr is made the default owner of all the pages of the object. The CoherMgr, CoherSvrs, POMs and the network storage server work together to manage objects and their coherency in the system. This is illustrated in figure 3.2. A number of processes on each network node have object x mapped into their address spaces, possibly at different virtual addresses, and are accessing it. When page faults or other events

Figure 3.2: COMMOS Architecture

occur for object x, the POM, which manages all the objects of the persistent object type of x, is invoked. The POM communicates with the CoherMgr or the CoherSvr on another network node and the network storage server to move different parts of the object to and from the secondary storage and maintain the guarantee of object coherency if required.

# 3.8 Previous Work: Memory-Mapped Object Management on Wanda

This section presents a memory-mapped object management system in a locally developed microkernel which forms the starting point of this work.

Wanda [Dixon91, Bacon93] is an experimental microkernel operating system developed at the University of Cambridge. It is a vehicle for research into kernels for high-performance services. Wanda supports preemptive multithreaded processes and multiprocessor thread scheduling. Memory management is based on paged segments, and page mapping and unmapping is used for efficient inter-process communication and for network I/O. Semaphores

are supported and are used both in the kernel and for user-level inter-thread communication within an address space. Wanda also employs an event mechanism by which processes are notified about various events.

An extension to the kernel virtual memory management supporting memorymapped objects [Mapp91, Huang92] has been designed and implemented on Wanda Snap2. Objects are typed and managed by external object managers, which are in charge of the data movement between the main memory and the secondary storage.

In this system, a Wanda process consists of various objects namely: a code object, a data object, a bss (uninitialised data) object, a stack object, an environ object, and other objects created or mapped by the process. Information about where and how an object is mapped is contained in a process map which is mapped read-only into the address space of the process as part of its initialisation. Each entry in the process map, known as a map\_entry, contains the name of the object, the type of the object, the starting address and the length of the object, the access rights of the user process, the index (called vir\_id) of the map\_entry in the process map and the number of threads accessing the object in the same address space. The creation of user processes is managed by a process server (ProcSvr) running in user mode.

Some ideas on which the Wanda memory-mapped object management was based have been used in the design of the COMMOS. These include the principle of typed object and the use of external object managers. Much of the source code is used in the COMMOS prototype implementation. However, the COMMOS differs from this previous work in the following key points. The operations to flush the modifications back to the secondary storage and to unmap an object were asynchronous. Although this provides better response time, it is potentially dangerous in persistent programming and database applications since data may be lost after the clients are told that they have been written back. Also, lock operations always block the caller in the previous design. This is not feasible because the high-level applications can not use these operations to construct their own sophisticated mechanisms like two-phase locking. More importantly, the previous design did not tackle the object coherency problem so it was not suitable to be used in a distributed computing environment.

## 3.9 Summary

A coherent memory-mapped object system architecture has been introduced in this chapter. The object model, which is based on the typed object principle is given and a two-layer structure for the COMMOS is chosen to meet the requirements discussed in the previous chapter. A broad outline of the architecture framework was then presented. Finally, the Wanda kernel and its memory-mapped object management were described.

The following chapters will present the design details of the coherence mechanism and a prototype implementation.

## Chapter 4

## Design of the Coherence Mechanism

#### 4.1 Introduction

In order to support the memory-mapped object management system in distributed computing environments and to retain the same object sharing semantics as that in a centralised system, mechanisms to maintain the coherence between memory-mapped copies of the same object on different network nodes are desired. As discussed in Section 3.4, no single universal object coherence protocol can satisfy the needs of all kinds of applications. Also the support of typed objects in the memory management system provides a good opportunity to apply different protocols to different types of object. The key issue here is to design a well-defined and flexible interface to a variety of object coherence protocols by which applications can advise the system to apply the most suitable protocol for a specific type of object. Besides, there may be a need to apply different protocols to individual objects as well as dynamically changing the protocol being used according to the system load and the concurrency level being experienced.

This chapter explores the design of the COMMOS coherence mechanism to support multiple coherence protocols. Various major design issues are considered first and the public interface is then given. Third, the coherence protocols are presented. After that, the coherence manager and the coherence server are described. The coherency control using the COMMOS coherence mechanism is illustrated in Section 4.6. Readers who are not particularly interested in the inside details of the coherence mechanism may skip this section.

## 4.2 Design Considerations

#### 4.2.1 Granularity

The granularity of memory, at which coherency is maintained, is an important design issue. The larger the granularity, the greater the contention will be [Coulouris94]. Memory contention occurs when two or more nodes attempt to access the same memory unit and at least one required access is a write. To reduce memory contention, a small granularity is desirable. In a typical network environment, due to the overhead of the software protocols, the transmission of large packets which may contain thousands of bytes is not much more expensive than the transmission of small ones. Therefore, large granularity is expected to improve the network throughput. In the emerging ATM network environments, network throughput improves while the packet size increases to a certain point [Dharanikota94, Kara94]. Beyond that point (8KB for IP in the environment used in [Dharanikota94]), the throughput drops because segmentation and reassembly takes more time. Meanwhile, a page represents the smallest memory unit on which protection can be enforced by the memory management hardware and the existing page fault schemes can be used. A page-based approach therefore seems natural.

#### Supporting Variable Length Granularity for Users

It is inappropriate for most distributed applications programmers to be required to be concerned about the details of page-level management. A friendlier interface supporting variable length units for synchronisation is desirable.

One way to provide variable length granularity is to allow fine-grained locking but updates are always directed to the process' own shadow copy. Modifications are merged to the master copy on release of a lock. The *copy-on-write* technique can be used to speed up page shadowing. A software approach always provides higher flexibility but is likely to be more complicated to implement and the performance will be poor due to software overhead.

An alternative approach is to translate variable length granularity in the user interface into the underlying page-based mechanism. This is relatively simple and straightforward and is adopted in this design. The major shortcoming is that memory contention is potentially high for fine-grained object sharing, and deadlock may be another problem (see Section 4.3.3 for details). Some object

33

clustering strategies to organise fine-grained objects which are unlikely to be accessed simultaneously into the same page may be desirable.

Some researchers have started exploring memory management techniques to support fine grained page size [Liedtke94b] and to accommodate mixed page sizes in virtual memory [Liedtke94b, Khalidi93b]. If these techniques become available in the future, hardware enforcement can be used for variable length granularity.

#### 4.2.2 Remote Interprocess Communication