Number 358

# Multithreaded processor design

Simon William Moore

February 1995

This report was also published as a book of the same title (Kluwer/Springer-Verlag, 1996, ISBN 0-7923-9718-5).

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 https://www.cl.cam.ac.uk/

#### © 1995 Simon William Moore

This technical report is based on a dissertation submitted October 1994 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Trinity Hall.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986 DOI https://doi.org/10.48456/tr-358

# **Abstract**

Multithreaded processors aim to improve upon both control-flow and data-flow processor models by forming some amalgam of the two. They combine sequential behaviour from the control-flow model with concurrent aspects from data-flow design.

Some multithreaded processor designs have added just a little concurrency to control-flow or limited sequential execution to data-flow. This thesis demonstrates that more significant benefits may be obtained by a more radical amalgamation of the two models. A data-driven microthread model is proposed, where a microthread is a short control-flow code sequence. To demonstrate the efficiency of this model, a suitable multithreaded processor, called Anaconda, is designed and evaluated.

Anaconda incorporates a scalable temporally predictable memory tree structure with distributed virtual address translation and memory protection. A temporally predictable cached direct-mapped matching store is provided to synchronise data to microthreads. Code is prefetched into an instruction cache before execution commences. Earliest-deadline-first or fixed-priority scheduling is supported via a novel hardware priority queue. Control-flow execution is performed by a modified Alpha 21064 styled pipeline which assists comparison with commercial processors.

# **Preface**

Except where otherwise stated in the text, this dissertation is the result of my own work and is not the outcome of work done in collaboration.

This dissertation is not substantially the same as any I have submitted for a degree or diploma or any other qualification at any other university.

No part of this dissertation has already been, or is being currently submitted for any such degree, diploma or other qualification.

This dissertation does not exceed sixty thousand words, including tables, footnotes and bibliography, but excluding appendices, photographs and diagrams.

#### **Publications**

The paper entitled "Scalable Temporally Predictable Memory Structures" was presented, by the author of this thesis, at the 2<sup>nd</sup> IEEE Workshop on Real-Time Applications, Washington D.C., July, 1994. This paper contains the early ideas which form chapter 5 of this thesis.

# **Trademarks**

Alpha and VAX are trademarks of Digital Equipment Corporation

CM2 is a trademark of Thinking Machines, Inc.

DAP is a trademark of ICL

HEP is a trademark of Denelcor Corporation

Hobbit is a trademark of AT&T

Motorola is a trademark of Motorola, Inc.

PowerPC is a trademark of IBM, Motorola and Apple Corporations

Tera is a trademark of Tera Corporation

Transputer and T800 are trademarks of INMOS Ltd.

# Acknowledgements

I would like to thank my supervisor, Derek McAuley, for his guidance and encouragement. Eoin Hyden has been a great friend and colleague, offering sound advice and copious comments on several drafts of this dissertation. Brian Graham's skills in formal methods have been invaluable and his work, in appendix A, is suitably accredited. Thanks are also due to Timothy Roscoe for his lively comments on single address space operating systems and memory management techniques. I would also like to thank Alan Jones, Peter Robinson and David Wheeler for may thought-provoking discussions during the hardware discussion group meetings.

For reading and commenting on drafts of this dissertation, I am also indebted to Richard Black, Paul Byrne, Shaw Chuang, David Evers, Robin Fairbairns, Daniel Gordon and Johanna Stiebert.

The Computer Laboratory, and particularly the Systems Research Group, has proven to be a stimulating environment in which to work. Special thanks go to: Jean Bacon, Paul Barham, Ralph Becket, Simon Crosby, James Hall, Mark Hayter, Mike Hinchey, Andy Hopper, Naeem Khan, Ian Leslie, Ken Moody, Roger Needham, Arthur Norman, Ian Pratt, Martin Richards, Cormac Sreenan, Quentin Stafford-Fraser and Neil Wiseman.

In 1993 I spent a most enjoyable summer at Digital's Western Research Laboratory under the guidance of Jeremy Dion. My thanks go to them all for honing my knowledge of processor design and simulation techniques.

Many members of my college, Trinity Hall, have also provided encouragement and support. I would particularly like to thank: William Clocksin, Stephen Hodges, Mari Jones, David Moore, Andrew Pauza and Ishtla Sing. I am also indebted to Martin Atkins, Gary Morgan and David Pumfrey, formelly from my undergraduate days at the University of York, who continue to encourage my work. My parents, Rosalie and Peter, and my sister, Helen, have also been a tower of strength.

This work was supported by a studentship from the UK Science and Engineering Research Council.

# **Contents**

| 1 | Intr | duction 1                                             |

|---|------|-------------------------------------------------------|

|   | 1.1  | Hardware motivations                                  |

|   | 1.2  | Software motivations                                  |

|   | 1.3  | Aims                                                  |

|   | 1.4  | Synopsis                                              |

| 2 | Desi | gn Motivations 3                                      |

|   | 2.1  | Introduction                                          |

|   | 2.2  | Software motivations                                  |

|   |      | 2.2.1 General primitives to support software          |

|   |      | 2.2.2 Best effort systems                             |

|   |      | 2.2.3 Hard real-time system requirements 6            |

|   |      | 2.2.4 Multi-media and quality of service requirements |

|   |      | 2.2.5 Multi-processor computers                       |

|   | 2.3  | Hardware motivations                                  |

|   |      | 2.3.1 Signal transmission limits                      |

|   |      | 2.3.2 Active component limits                         |

|   |      | 2.3.3 Circuit techniques                              |

|   | 2.4  | Summary of hardware and software requirements         |

| 3 | Cur  | rent Processor Models 15                              |

|   | 3.1  | Introduction                                          |

|   | 3.2  | Control-flow processors                               |

|   |      | 3.2.1 Memory structure and data locality              |

|   |      | 3.2.2 Instruction coding                              |

|   |      | 3.2.3 Instruction parallelism                         |

|   |      | 3.2.4 Data parallelism                                |

|   |      | 3.2.5 Concurrency and synchronisation primitives      |

|   |      | 3.2.6 Memory protection mechanisms                    |

|   |      | 3.2.7 Assessment of the control-flow model            |

|   | 3.3 | Data-flow processors                                                    |

|---|-----|-------------------------------------------------------------------------|

|   |     | 3.3.1 Static data-flow                                                  |

|   |     | 3.3.2 Coloured dynamic data-flow                                        |

|   |     | 3.3.3 Tagged token dynamic data-flow                                    |

|   |     | 3.3.4 Assessment of tagged token data-flow                              |

|   | 3.4 | Multithreaded processors                                                |

|   |     | 3.4.1 Multiple contexts                                                 |

|   |     | 3.4.2 Communication                                                     |

|   |     | 3.4.3 Synchronisation and scheduling                                    |

|   |     | 3.4.4 Memory                                                            |

|   |     | 3.4.5 Microthread size                                                  |

|   | 3.5 | Summary                                                                 |

|   |     |                                                                         |

| 4 |     | dware Scheduling 31                                                     |

|   | 4.1 | Introduction                                                            |

|   | 4.2 | Background 31                                                           |

|   |     | 4.2.1 Variations on the heap sort                                       |

|   |     | 4.2.2 The rebound sorter                                                |

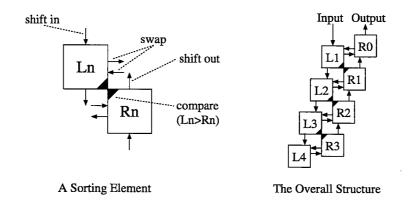

|   |     | 4.2.3 The up/down sorter                                                |

|   | 4.3 | The tagged up/down sorter                                               |

|   |     | 4.3.1 Abstracting the up/down sorter algorithm                          |

|   |     | 4.3.2 Ensuring FIFO ordering                                            |

|   | 4.4 | Clocked digital implementation of the tagged up/down sorter 40          |

|   |     | 4.4.1 Controlling the single cycle implementation                       |

|   |     | 4.4.2 Discussion of the operation of the single cycle implementation 42 |

|   | 4.5 | Conclusions                                                             |

| _ |     |                                                                         |

| 5 |     | nory structure 45                                                       |

|   |     | Introduction                                                            |

|   | 5.2 | Memory performance                                                      |

|   | 5.3 | Memory hierarchy for control-flow processors                            |

|   |     | 5.3.1 Caching                                                           |

|   |     | 5.3.2 Scoreboarding                                                     |

|   | 5.4 | Maintaining memory access frequency                                     |

|   | 5.5 | Virtual addressing for the memory tree                                  |

|   | 5.6 | Scalable memory protection                                              |

|   | 5.7 | Tree routers                                                            |

|   | 5.8 | Summary                                                                 |

| 6 | Anac | conda — a multithreaded processor                | 53  |  |  |  |  |  |  |  |  |  |  |

|---|------|--------------------------------------------------|-----|--|--|--|--|--|--|--|--|--|--|

|   | 6.1  | Introduction                                     | 53  |  |  |  |  |  |  |  |  |  |  |

|   | 6.2  | Data driven microthreads                         | 55  |  |  |  |  |  |  |  |  |  |  |

|   | 6.3  | Matching                                         | 58  |  |  |  |  |  |  |  |  |  |  |

|   | 6.4  | Scheduling                                       | 59  |  |  |  |  |  |  |  |  |  |  |

|   | 6.5  | Memory structure                                 | 59  |  |  |  |  |  |  |  |  |  |  |

|   | 6.6  | Exceptions and types                             | 60  |  |  |  |  |  |  |  |  |  |  |

|   | 6.7  | Instructions                                     | 62  |  |  |  |  |  |  |  |  |  |  |

|   |      | 6.7.1 Load, store and write through instructions | 62  |  |  |  |  |  |  |  |  |  |  |

|   |      | 6.7.2 Integer and bitwise instructions           | 64  |  |  |  |  |  |  |  |  |  |  |

|   |      | 6.7.3 Floating-point instructions                | 64  |  |  |  |  |  |  |  |  |  |  |

|   |      | 6.7.4 Branch, jump and descheduling instructions | 65  |  |  |  |  |  |  |  |  |  |  |

|   |      | 6.7.5 Type modification instruction              | 65  |  |  |  |  |  |  |  |  |  |  |

|   |      | 6.7.6 Instruction formats                        | 67  |  |  |  |  |  |  |  |  |  |  |

|   | 6.8  | Cache control and preloading context             | 67  |  |  |  |  |  |  |  |  |  |  |

|   | 6.9  | Nanokernel support                               | 69  |  |  |  |  |  |  |  |  |  |  |

|   | 6.10 | Input, output and timers                         | 70  |  |  |  |  |  |  |  |  |  |  |

|   | 6.11 | Execution unit pipeline                          | 72  |  |  |  |  |  |  |  |  |  |  |

|   | 6.12 | Summary                                          | 74  |  |  |  |  |  |  |  |  |  |  |

| 7 | Eval | uation                                           | 75  |  |  |  |  |  |  |  |  |  |  |

|   | 7.1  | Introduction                                     | 75  |  |  |  |  |  |  |  |  |  |  |

|   | 7.2  | Assembler                                        | 75  |  |  |  |  |  |  |  |  |  |  |

|   | 7.3  | Simulator                                        | 76  |  |  |  |  |  |  |  |  |  |  |

|   | 7.4  | Memory copy test                                 | 76  |  |  |  |  |  |  |  |  |  |  |

|   | 7.5  | Livermore loop 7 test                            | 82  |  |  |  |  |  |  |  |  |  |  |

|   | 7.6  | Signalling and mutual exclusion                  |     |  |  |  |  |  |  |  |  |  |  |

|   | 7.7  | Interdomain remote procedure calls               |     |  |  |  |  |  |  |  |  |  |  |

|   | 7.8  | Conclusions                                      | 93  |  |  |  |  |  |  |  |  |  |  |

| 8 | Con  | clusions                                         | 95  |  |  |  |  |  |  |  |  |  |  |

|   | 8.1  | Review                                           | 95  |  |  |  |  |  |  |  |  |  |  |

|   |      | 8.1.1 Background                                 | 95  |  |  |  |  |  |  |  |  |  |  |

|   |      | 8.1.2 Anaconda                                   | 97  |  |  |  |  |  |  |  |  |  |  |

|   | 8.2  | Future work                                      | 100 |  |  |  |  |  |  |  |  |  |  |

|   |      |                                                  | 100 |  |  |  |  |  |  |  |  |  |  |

|   |      | _                                                | 100 |  |  |  |  |  |  |  |  |  |  |

|   |      | <del>-</del>                                     | 100 |  |  |  |  |  |  |  |  |  |  |

|   |      |                                                  | 100 |  |  |  |  |  |  |  |  |  |  |

|     |             | 8.2.5     | S     | tatio | co co | de a | ana  | lys | İS  | •   |      |            |    |    |   |    |     |   |   |   |  |  |  | 101 |

|-----|-------------|-----------|-------|-------|-------|------|------|-----|-----|-----|------|------------|----|----|---|----|-----|---|---|---|--|--|--|-----|

|     |             | 8.2.6     | C     | per   | atin  | g sy | yste | m   | su  | ppo | ort  |            |    |    |   |    |     |   |   |   |  |  |  | 101 |

|     |             | 8.2.7     | C     | ach   | ing   | for  | po   | wei | rre | edu | ıcti | ion        | ٠. |    | • |    |     |   | • | • |  |  |  | 101 |

| Bil | bliogr      | raphy     |       |       |       |      |      |     |     |     |      |            |    |    |   |    |     |   |   |   |  |  |  | 103 |

| A   | Proc        | of of cor | rre   | ctne  | ess f | or   | the  | ta  | gg  | ed  | up   | / <b>d</b> | ov | vn | S | or | tei | ŗ |   |   |  |  |  | 109 |

|     | <b>A.</b> 1 | Introd    | luct  | ion   |       |      |      |     |     |     |      |            |    |    |   |    |     |   |   |   |  |  |  | 109 |

|     | A.2         | Forma     | al sj | eci   | fica  | tion | ι.   |     |     |     |      |            |    |    |   |    |     |   |   |   |  |  |  | 109 |

|     | A.3         | Proof     | ske   | tch   |       |      |      |     |     |     |      |            |    |    |   |    |     |   |   |   |  |  |  | 114 |

|     | <b>A.</b> 4 | Conclu    | usi   | on .  |       |      |      |     |     |     |      |            |    |    |   |    |     |   |   |   |  |  |  | 116 |

| В   | Ana         | conda i   | inst  | ruc   | tior  | ı fo | rm   | ats |     |     |      |            |    |    |   |    |     |   |   |   |  |  |  | 117 |

| C   | Ana         | conda r   | me    | nor   | 'y c  | opy  | pr   | og) | rai | n   |      |            |    |    |   |    |     |   |   |   |  |  |  | 121 |

# **List of Figures**

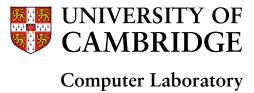

| 2.1  | Signal fanout and amplification                                       | 9  |

|------|-----------------------------------------------------------------------|----|

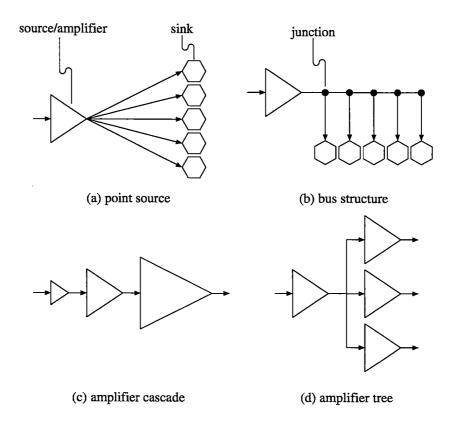

| 2.2  | Sequential vs pipelined — trading latency for frequency               | 11 |

| 2.3  | Dual rail encoding of binary numbers                                  | 12 |

| 3.1  | An example of control-flow and data-flow program structure            | 22 |

| 3.2  | Example static data-flow instruction format                           | 22 |

| 3.3  | Example tagged-token data-flow instruction and token formats          | 24 |

| 4.1  | Structure of the rebound sorter                                       | 33 |

| 4.2  | An example of a rebound sort                                          | 33 |

| 4.3  | The up/down sorting element                                           | 34 |

| 4.4  | An example of an up/down sort                                         | 35 |

| 4.5  | Abstraction of the up/down sorter                                     | 37 |

| 4.6  | Ordering problem with the up/down sorter                              | 38 |

| 4.7  | Using tagging to ensure FIFO ordering                                 | 39 |

| 4.8  | Two stage tagged up/down sorting element                              | 40 |

| 4.9  | One stage tagged up/down sorting element                              | 41 |

| 4.10 | Example timing for the one step tagged up/down sorter to perform two  |    |

|      | inserts followed by two extracts                                      | 41 |

| 5.1  | Memory tree structure                                                 | 48 |

| 5.2  | Example capability format                                             | 50 |

| 5.3  | Tree mapping of messages going up the tree from the memory modules    |    |

|      | to the processor                                                      | 51 |

| 6.1  | The overall structure of Anaconda                                     | 54 |

| 6.2  | A single logical thread constructed from a sequence of microthreads . | 55 |

| 6.3  | Example microthread structure for forks and joins                     | 56 |

| 6.4  | Data-flow styled bubble sort                                          | 57 |

| 6.5  | Activation frame format                                               | 58 |

| 6.6  | Preloading an activation frame and prefetching code                   | 59 |

| 6.7  | Anaconda capability format                                              |

|------|-------------------------------------------------------------------------|

| 6.8  | Anaconda types and their privileges 61                                  |

| 6.9  | Load and store formats                                                  |

| 6.10 | Load address group of instructions                                      |

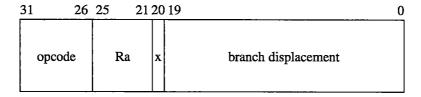

| 6.11 | Intermicrothread branch instructions                                    |

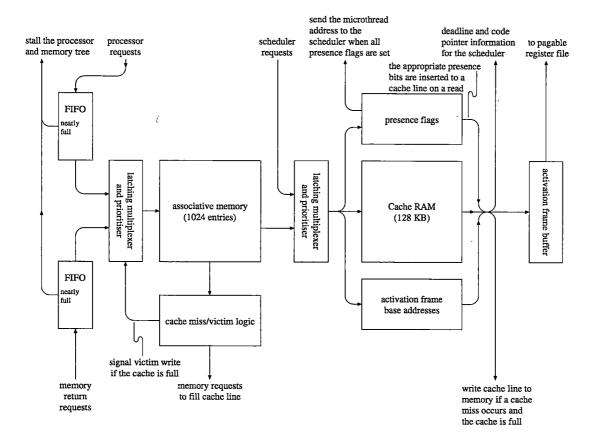

| 6.12 | Overview of the Anaconda matching store                                 |

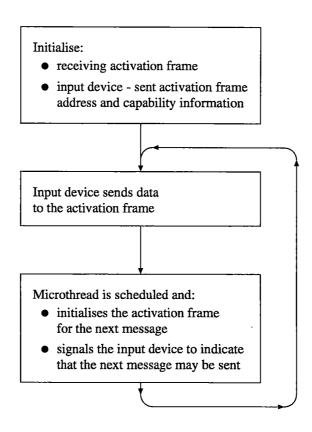

| 6.13 | Data transfer sequence to an input device                               |

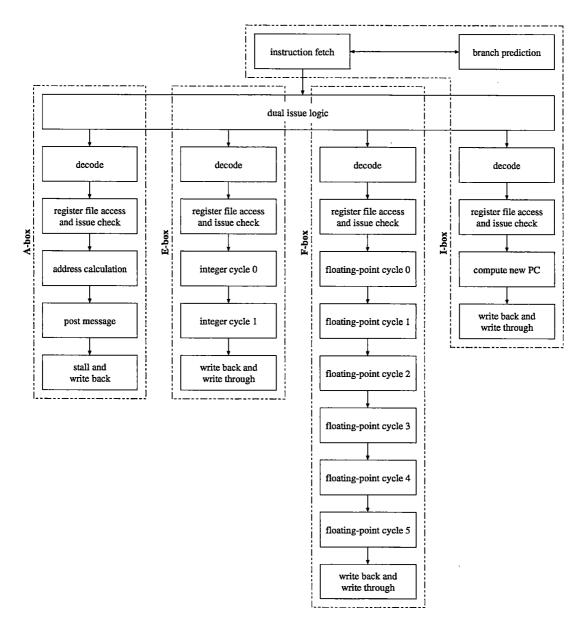

| 6.14 | Overview of Anaconda's execution unit pipeline                          |

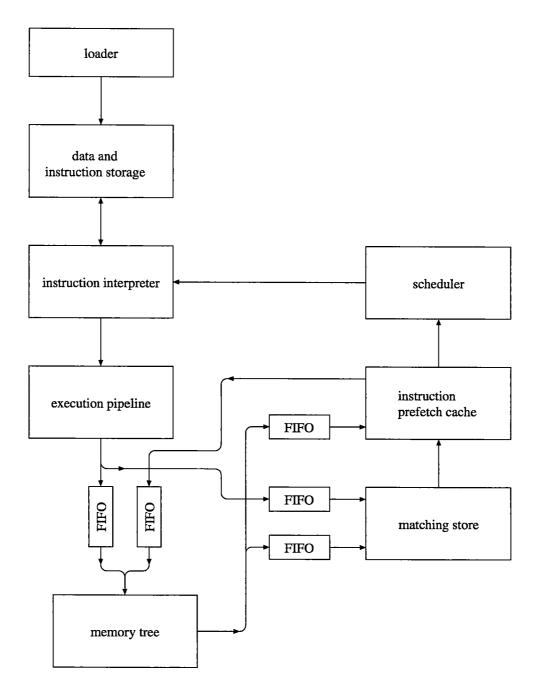

| 7.1  | Overview of the simulator                                               |

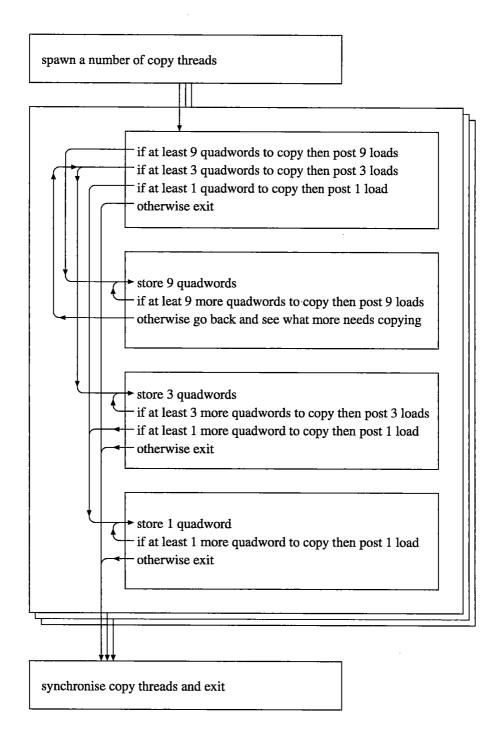

| 7.2  | Overview of the parallel memory copy routine                            |

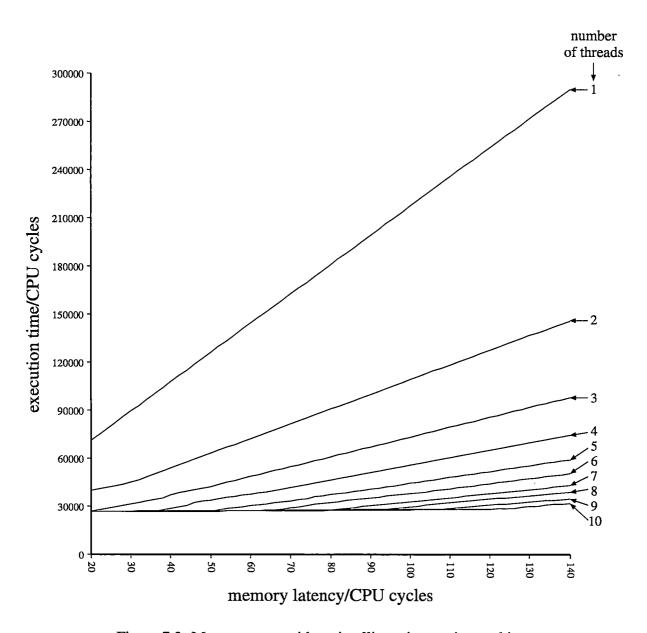

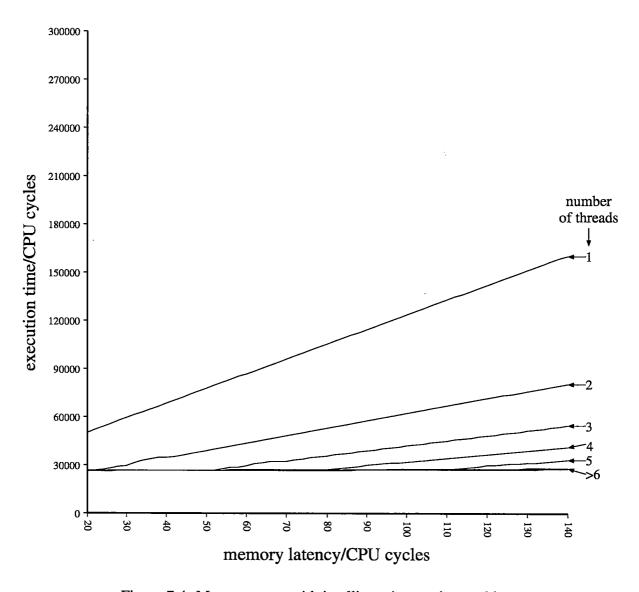

| 7.3  | Memory copy without intelligent instruction caching 80                  |

| 7.4  | Memory copy with intelligent instruction caching 81                     |

| 7.5  | Fortran code for the Livermore loop 7 kernel                            |

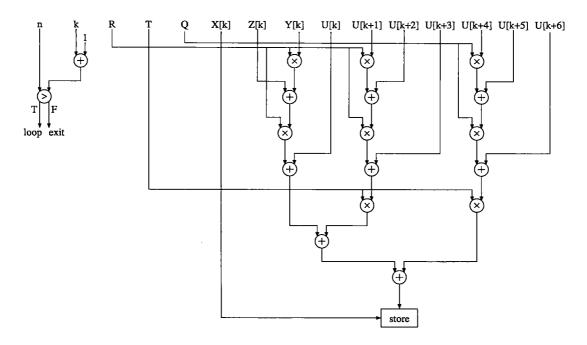

| 7.6  | Data-flow analysis of Livermore loop 7                                  |

| 7.7  | Overview of the Anaconda routine to perform Livermore loop 7 84         |

| 7.8  | Interdependencies between microthreads during several iterations 85     |

| 7.9  | Livermore loop 7 with all 9 microthreads having the same deadline 86    |

| 7.10 | Livermore loop 7 with a decreasing deadline for each iteration 87       |

| 7.11 | Livermore loop 7 with microthreads 0, 1 and 2 having a slightly earlier |

|      | deadline                                                                |

| 7.12 | Livermore loop 7 with the same parameters as figure 7.11 but with in-   |

|      | telligent instruction caching turned off                                |

| 7.13 | An implementation of Dijkstra's semaphores 91                           |

| 8.1  | Filling the control-flow/data-flow void                                 |

| B.1  | Anaconda additions to the Alpha opcode summary                          |

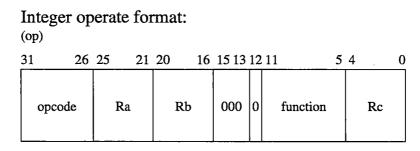

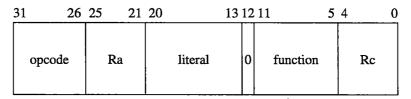

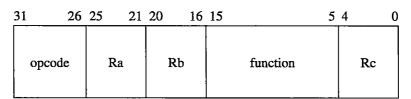

| B.2  | Anaconda instruction formats — part 1                                   |

| B.3  | Anaconda instruction formats — part 2                                   |

# Glossary

| CMOS        | Complementary Wetai Oxide                              |

|-------------|--------------------------------------------------------|

| CPU         | Central Processing Unit                                |

| <b>DMA</b>  | Direct Memory Access                                   |

| DRAM        | Dynamic Random Access Memory                           |

| <b>EDF</b>  | Earliest Deadline First                                |

| FIFO        | First In First Out                                     |

| FP          | Fixed Priority                                         |

| HOL         | Higher Order Logic                                     |

| IEEE        | Institute of Electrical and Electronic Engineers, Inc. |

| I/O         | Input/Output                                           |

| LIFO        | Last In First Out                                      |

| MIMD        | Multiple Instruction Multiple Data                     |

| OS          | Operating System                                       |

| PC          | Program Counter                                        |

| PE          | Processor Element                                      |

| QOS         | Quality Of Service                                     |

| RAM         | Random Access Memory                                   |

| RPC         | Remote Procedure Call                                  |

| SIMD        | Single Instruction Multiple Data                       |

| SISD        | Single Instruction Single Data                         |

| <b>SPEC</b> | Standard Performance Evaluation Corporation            |

| TLB         | Translation Lookaside Buffer                           |

| TTL         | Transistor Transistor Logic                            |

| VLIW        | Very Long Instruction Word                             |

| VLSI        | Very Large Scale Integration                           |

# Chapter 1

# Introduction

Multithreaded processors aim to improve upon both control-flow and data-flow processor models by forming some amalgam of the two. They exhibit sequential behaviour from the control-flow model and concurrent execution due to data-flow influences. This dissertation demonstrates the efficiency of a novel multithreaded processor designed to execute data-driven microthreads, where a microthread is a short control-flow unit of code.

### 1.1 Hardware motivations

Whilst control-flow processors dominate the current computer market, they have fundamental problems, primarily due to the lack of concurrency supported by the hardware. Too little concurrency results in processor stalls when waiting for long latency operations. A particularly thorny problem results from faster processors being used to tackle larger problems which require larger memory. Unfortunately this prohibits memory latency scaling with processor performance. Temporal and spatial locality of memory accesses may be used to cache frequently used values. However, an increasing number of ever larger caches are required to maintain a statistically low access latency. Furthermore, caches introduce a huge temporal variance which is hard to predict. This is inadequate for real-time applications.

Data-flow processors offer instruction level concurrency which allows long latency operations to be tolerated. The lack of sequential ordering, however, makes multiple assignment, to the same memory location, difficult. Thus, memory reuse and input/output operations are complex. Furthermore, instruction level concurrency implies significant synchronisation overhead which can often be greater than the time to evaluate the instruction. Also, there is insufficient time to make sensible scheduling decisions so poor use is made of the processor resource.

#### 1.2 Software motivations

A significant number of today's applications only require single threaded best effort performance. This is reflected in the synthetic benchmark applications which are often used to assess a computer's performance. However, with the increasing appearance of multimedia, and our reliance on hard real-time applications, temporal predictability is important. Unfortunately, commercial processor designers are heavily motivated by the current de facto standard benchmarks. Until industrially recognised multimedia and hard real-time benchmarks are established, processor design will not change direction. Fortunately, academia is not so short-sighted

Multithreaded languages, and suitable operating system support, are becoming increasingly common, particularly for writing large, user interactive, applications. When using commercial control-flow processors, significant software support must be provided for these applications. Also, more concurrency reduces the efficiency of the cached memory structure. On the other hand, a multithreaded processor should be able to take advantage of concurrency to tolerate various latencies, including memory access latency.

#### **1.3** Aims

This dissertation aims to investigate the data-driven microthread model to assess whether it can successfully underpin a general purpose processor designed with future hardware and software requirements in mind.

# 1.4 Synopsis

Chapter 2 reviews the hardware technology limitations and software application requirements which bound and guide successful processor designs.

Chapter 3 presents a commentary on existing processor designs.

Chapter 4 looks at hardware scheduling issues which are paramount for efficient use of a multithreaded processor resource.

Chapter 5 discusses scalable memory structures, virtual addressing support and protection mechanisms.

Chapter 6 presents a novel multithreaded processor design called Anaconda.

Chapter 7 evaluates the Anaconda design.

Chapter 8 reviews the work contained in previous chapters, draws a number of conclusions and suggests areas for future work.

# **Chapter 2**

# **Design Motivations**

### 2.1 Introduction

This chapter discusses current and possible future trends in software and hardware to determine desirable characteristics which processor designs should exhibit.

### 2.2 Software motivations

All processors are *Turing complete* (i.e. they can perform all the operations that a Turing machine can) and so can, in theory, run any application. However, in practice we must take the run-time into account. A processor must support a range of primitives, from which applications may be constructed, which allow a desirable performance to be met. Different application areas suggest different primitives and optimisations; however, there is some commonality (see section 2.2.1).

Benchmarks are synthetic applications used to assess the various performance characteristics of computers, from integer and floating-point arithmetic to memory and I/O speed. The performance of operating system support operations, like interrupt latency and context switch time, may be assessed. The efficiency of the compiler and linker also play an important role. Although benchmarks only allow an estimate to be made of the execution characteristics for a specific application, they provide essential metrics for processor designs.

The majority of processors are designed to attain good performance with respect to current industrial benchmarks. Most of these benchmarks are designed to assess uniprocessor computers where a single application requires best effort performance (section 2.2.2). However, computer control of mechanical machines, and other hard real-time applications, require temporally predictable performance (section 2.2.3). Other application areas — like multi-media — require some temporal predictability,

but not the temporal guarantees imposed by hard real-time systems; an alternative is to guarantee a certain minimum *quality of service* [35] (section 2.2.4).

As processors become cheaper, multiprocessor computers become more practical. The software implications are discussed in section 2.2.5 and new areas to benchmark are proposed.

## 2.2.1 General primitives to support software

It is commonly accepted that some or all of the following collection of functions are required for many applications. The processor may explicitly provide a primitive for a particular function, or provide some efficient combination of primitives.

- *integer arithmetic* addition, subtraction, comparison, multiplication and division; although division may not be supported by a single primitive it is now usual to provide a multiplication primitive.

- floating-point arithmetic it is now common to support floating-point arithmetic, particularly with conformance to the IEEE standard (or some workable subset thereof).

- logical operations boolean functions: AND, OR, NOT etc. and bitwise shifting.

- conditionals to allow data dependent decisions to be made upon which code is executed.

- *subroutines* to allow sharing of subprograms/software functions without code duplication.

- multiple assignment allow values to be written to a memory and for old values

to be overwritten. The ordering of reads and writes to a given location is vital if

memory is to be reused. Furthermore, it is a prerequisite for input and output

operations.

- *indirect addressing* indirect memory addressing modes are required to allow calculated addresses to be used without requiring self-modifying code.

- *virtual addressing* to assist memory allocation and garbage collection and to support *virtual memory*, by allowing paging of memory to some other storage server (e.g. a disk or a distributed memory structure), if required.

- protection to prevent undesirable interference between applications executing concurrently in case one or more of them misbehaves either due to malicious

intent or a bug. This is typically provided by a memory protection subsystem which prevents applications from accessing memory areas for which they have not been given permission. As a corollary to this, a *supervisor mode* (also called a *privileged mode* or *trusted mode*) must be provided so that the operating system can initialise protection areas, or *domains*, and assign them to applications.

- exceptions a method which invokes software to take care of errors, like division by zero, without explicitly having to add instructions to test for an error at every possible place.

- *synchronisation* of external events to appropriate handler code to be executed. One approach is to extend the exception mechanism so that an exception is taken whenever an external event occurs; known as an *interrupt*.

### 2.2.2 Best effort systems

A typical workstation is used for computational and user interactive applications which simply require a reasonably short runtime. If, for example, a calculation takes a little longer than usual or the screen is not redrawn at the same rate, then it is at worst an annoyance to the user. In other words, the user expects the computer to make the best effort it can to finish jobs as quickly as possible.

Whilst the computer's speed places an upper bound on the possible rate of execution of a single application, the operating system plays an important role in dividing processor, memory and I/O resources between applications running concurrently. These resources are typically allocated on a first come first served basis [14]. The processor resource is typically allocated on a priority basis where an application is given a base priority which may be increased if it is waiting for I/O. This is computationally simple and allows interactive applications, which spend most of their time waiting for user input, to obtain processor resources rapidly. The only hardware that is required is a timer to invoke a reschedule (known as *preemption*) so that one task does not monopolise the processor resource. From an efficiency point of view it is important that the processor supports a quick method for switching context. Memory and I/O resource allocation is typically supported by the operating system.

The SPEC<sup>1</sup> mark suite of benchmarks is, at the moment, widely used for evaluating workstations. Only total execution time is measured for each benchmark. Different benchmarks emphasise the performance characteristics of different combinations of the computer's constituent parts. For example, the compress benchmark tests file I/O (both hardware and operating system support), memory and integer arithmetic but not

<sup>&</sup>lt;sup>1</sup>SPEC marks are produced by the non-profit making company *Standard Performance Evaluation Corporation* which is supported by manufacturers of control-flow processors.

floating-point arithmetic; where as tomcatv mainly tests memory and floating-point facilities.

These benchmarks have their deficiencies. For example, the efficiency of concurrent execution of several benchmarks is rarely addressed even though this may be more representative of a typical load. Concurrent execution has profound effects upon memory performance, particularly if there are several caches in the memory hierarchy (see section 5.3.1 for a discussion on caches). Also, if a translation look-aside buffer (TLB) is used for virtual address translation and memory protection, then its efficiency is also highly dependent upon concurrent activities.

Performance of user interactive applications is also not usually benchmarked, probably because such statistics are difficult to obtain. However, to a large extent, general processor, memory and I/O benchmarks give a reasonable indication of the likely interactive performance.

#### 2.2.3 Hard real-time system requirements

Hard real-time systems require output to be produced by specified times in relation to input stimuli [63]. Furthermore, premature output may also be undesirable. For example, a car engine management system needs to cause ignition (via the spark plugs) at the correct time, neither early nor late. The real-world is inherently parallel; thus, in order that there is a clear, logical mapping between the application and its environment, software is often constructed as a set of parallel tasks or *threads* (an abbreviated form of *threads of control* which makes particular reference to the control-flow model of computing — see section 3.2).

Real-time applications must be assessed to ensure that not only their functional requirements are met, but also their temporal ones. This is assisted by the fact that most real-time applications have the whole computer system to themselves. Simple systems may have a natural periodicity which allows the scheduling of these threads to be determined off line, or *statically*. More complex systems with sporadic stimuli require run time, or *dynamic*, scheduling. Some of these systems may be scheduled using a preemptive fixed priority algorithm [12] which, as with the best effort scheduler, requires little extra hardware support. However, other applications require a more sophisticated scheduler, for example, one which schedules the task with the earliest deadline. An *earliest deadline first (EDF)* scheduler requires a priority queue to sort the deadlines of runnable tasks. This is computationally expensive, but if there are not too many tasks and scheduling does not need to occur too often, then a software implementation is satisfactory. However, this may not be the case and hardware support may be necessary (see chapter 4 for further details).

No matter how good the scheduler is, there must be sufficient processor resources for a schedule to be possible. Missing a hard real-time deadline can be catastrophic, so it is important that the worst case processor time required for each thread can be assessed. Furthermore, in a dynamically scheduled application it is vital that the processing time of threads is independent of the order in which they are scheduled. Unfortunately, as will be seen in section 3.2 on control-flow machines, this is currently far from the case and is becoming increasingly bad. One may deduce from this that most processor designers are motivated by the need to produce fast processors in the best effort sense, rather than making them temporally predictable and fast.

One reason for this may be that there are few standard real-time benchmarks; most real-time applications programmers opt for their own benchmarks to suit their specialist application. This is of little use to the processor designer. The Hartstone benchmark [67] is an exception to this but it is primarily designed for assessing Ada compilers and their associated run time support system rather than processor characteristics. Experimental results from using Hartstone indicate that a high resolution hardware real-time clock is of great importance. However, little more can be deduced.

# 2.2.4 Multi-media and quality of service requirements

Multi-media, and in particular continuous media like audio and video, require end-to-end guarantees between the source and sink. This encompasses processor, memory, disk and/or network resources. In order to reduce resource usage, compression techniques are employed, often in a layered form such that low quality, and thus low bandwidth, information is sent and processed first followed by several additional layers of information to improve the quality. This potentially allows an overloaded resource to drop the higher quality layers first if overloading occurs, thereby providing a degraded service rather than no service at all. From a processor scheduling viewpoint, applications require a minimum proportion of the processor resource which may be specified as a desired *quality of service*<sup>2</sup> [35]. If processor resources are left over then applications may receive extra resources to allow higher layers to be decoded.

As with hard real-time, predictable processor performance is essential. For multimedia systems, temporal predictability allows accurate calculation of the minimum amount of processor time required to deliver a desired minimum quality of service. I/O performance is also critical.

<sup>&</sup>lt;sup>2</sup>Quality of service may also be used to schedule network resources to deliver an end-to-end quality of service [35].

### 2.2.5 Multi-processor computers

The last three sections have concentrated on applications running on uniprocessors. Transferring these to multiprocessors poses many problems for the software engineer. These include the reworking of algorithms to allow partitioning of the processor load together with problems of efficient movement of data and associated synchronisation to ensure correct ordering of updates.

Obviously the processor design must provide efficient means to move data to and from other processors. Message passing is one approach; another is to share memory using per-processor caches for recently used data. The two methods are equivalent in that any algorithm could be rewritten to use either method [40]. Which performs best is largely application specific and so it is advantageous if both models can be supported. For shared memory some form of cache coherency mechanism is required, e.g. using a directory [42]. Message passing requires low overhead synchronisation of messages to threads.

Currently, general purpose benchmarks for parallel computers are difficult to write because there is no accepted way of coding parallel algorithms so that they run reasonably efficiently on a wide range of parallel computers. Consequently, the current practice is to hand tune code for particular parallel computers resulting in benchmarks reflecting the programmer's ingenuity as well as processor performance and compiler technology. This obviously makes comparisons problematic.

# 2.3 Hardware motivations

Computer systems employ a variety of technologies from mechanical and ferromagnetics to electronics and optics. Consequently there are a huge number of implementation technology issues, the details of which are beyond the scope of this dissertation. However, the general problems, relating to signal transmission and active devices, are pertinent to this discussion (sections 2.3.1 and 2.3.2 respectively). Basic circuit techniques are also briefly reviewed in section 2.3.3 with a slightly more detailed discussion of self-timed circuits due to their comparative novelty.

# 2.3.1 Signal transmission limits

The transmission of signals is limited by the speed of light ( $c \approx 2.99725 \times 10^8 \, \mathrm{ms^{-1}}$ ). This is a fundamental limiting factor which is becoming particularly significant as circuit switching frequency moves beyond 1 GHz, since at this speed even light only travels approximately 300 mm in one period (1 ns).

Electrical pulses in a wave guide are somewhat slower at:

$$v_p = \frac{c}{\sqrt{\mu_r \epsilon_r}}$$

where  $v_p$  is the velocity of propagation which is dependent upon the speed of light (c), the permeability  $(\mu_r)$  and the permittivity, or dielectric constant,  $(\epsilon_r)$  relative to free space. By definition,  $\mu_r$  and  $\epsilon_r$  must be > 1 but careful design can keep them near 1. However, capacitance, self and mutual inductance only make matters worse.

The power required to source a signal is dependent upon transmission line attenuation and the fanout. A signal emanating from a point source (see figure 2.1a) must provide sufficient power to each transmission line. For a bus (see figure 2.1b) power is divided at each junction so the source signal must be strong enough.

Providing a sufficiently large amplifier for a large fanout is problematic. Since amplifier gain is finite, a large amplifier requires a proportionately large signal. Consequently, for very large fanouts, a cascade of amplifiers may be required (figure 2.1c). However, large amplifiers tend to be slow. Alternatively, a tree of amplifiers may be used (figure 2.1d) but the speed of each amplifier tends to be different due to manu-

Figure 2.1: Signal fanout and amplification

facturing tolerances, resulting in temporal skew. This is obviously undesirable for synchronisation signals, or *clocks*.

To conclude, it is advantageous if transmission lines can be kept short with little fanout.

### 2.3.2 Active component limits

The switching, or active, components (for amplification and boolean function implementation etc.) which are widely used today, are often based upon complementary metal oxide (CMOS) very large scale integration (VLSI) technology [47]. For example, the Digital's Alpha series of processors are already available in CMOS with a feature size of  $0.75\mu m$  and operating at 200 MHz [62]. Whilst feature sizes remain larger than  $0.5\mu m$ , every development enabling the feature size to be reduced is rewarded by significantly improved performance. This is due to capacitance and distance being reduced whilst voltage remains at 5V to be compatible with other TTL circuits. For a fixed voltage gate delay  $\propto$  (feature size)<sup>2</sup>. However, at less than  $0.5\mu m$  the voltage has to be dropped below the usual 5V to prevent signals tunnelling through the ever diminishing insulation layers. This reduces the potential performance gain to gate delay  $\propto$  feature size because voltage  $\propto$  feature size. Therefore, it is anticipated that the density of CMOS circuits will increase but the performance will not improve as dramatically [38].

It would be foolish to attempt to predict which implementation technology will be used in the future. If room temperature superconductors become available, then quantum effect devices may be the future [31]. Alternatively, the future may be in nanomechanical machines [23]. However, whichever technology is used it is highly probable that active components will have a spatial locality which in turn enforces a spacial locality for information and computation. Furthermore, movement of information takes time and typically consumes power. Therefore, it is advantageous if efficient use can be made of local storage.

# 2.3.3 Circuit techniques

Functions to perform data manipulation range from bitwise boolean operations, integer addition or subtraction through integer multiplication and division to floating-point arithmetic. The more complex functions take a relatively long time to compute (i.e. the *latency* of the operation is long). However, to enable the *frequency* of data transfer to match the latency of simple operations, the more complex operations may be broken down into sequential stages (see figure 2.2). Latches are placed between stages to store the intermediate results. The resulting structure (a *pipeline*) allows computation

Figure 2.2: Sequential vs pipelined — trading latency for frequency

and information flow to be localised. This scales well with decreasing discrete component size and increasing components on a chip. In later sections example processor and memory pipelines will demonstrate more complex structures in which some stages branch off into two or more pipelines (see section 3.2.3 and chapter 5 respectively).

Currently the most popular technique for controlling information flow between stages of pipelines is to use one or more global clock signals to trigger the latches to transfer the information on their inputs to their outputs. The clock rate is determined by the slowest stage of the pipeline, for example the integer addition/subtraction stage where the carry has to be propagated. However, transmitting a global clock so that all the latches update simultaneously is impossible because of the transmission time and the large capacitances which the global wiring introduces. The timing difference due to delay is known as *clock skew*. In practice, using today's technology, it is still possible to keep clock skew to a tolerable level across a chip but as chip sizes and clock frequencies increase the problem is going to become worse. These problems can already be witnessed at the circuit board level where the processor is typically clocked at 2, 4 or even 8 times the board clock rate because it is impractical to broadcast the higher speed clock across the whole circuit board. When high speed circuit board clocks are used (e.g. RAM-BUS [24]) the clock follows a single path along the same route as the data to ensure equal delays. Alternatively, circuits may be clocked from different sources

but this introduces synchronisation problems and overheads. Similar techniques can be applied to signals across a chip.

Global clocks limit performance because they are set at a rate which always allows the slowest stage of the pipeline to complete its calculation correctly. Furthermore, by the time the design has taken into account manufacturing tolerances, and that silicon performance is temperature dependent, a significant margin of error (e.g. 20%) has to be allowed.

An alternative to global clocks is to use localised clocking to determine when pipeline stages have completed. This is known as *micropipelines* [65] which are a form of nonclocked, or *self-timed*, circuit. Local clocks may be derived from critical signal paths (e.g. the carry propagation of an adder) and by using delay lines which may be placed close to the associated function. This allows a stage to complete early, for example, if the carry propagation takes a fast path. Furthermore, temperature variations can be allowed for to some extent. However, current practice has shown that often a 20 to 30% margin of error has to be catered for, due to manufacturing variance [27], resulting in delays which have to be longer than one would wish, in order to avoid timing problems.

Another self-timed technique uses two bits to represent every binary digit of information together with a handshaking signal (see figure 2.3) which is known as *dual rail encoding* [18]. Functions are evaluated in a two stage process. Firstly, the function's inputs are cleared (each pair set to 00) until the outputs are all cleared. Then, data is placed on the inputs and when the outputs contain valid data (i.e. not 00 but 01 or 10) this value may be latched. Thus, the completion signal is encoded with the data. This makes dual rail encoding a very safe way of building self-timed circuits, because correct operation is independent of manufacturing tolerances and temperature effects. However, design methods have to be different from their clocked counterparts. For example, pipeline designs have to allow clear signals to propagate in the wake of data signals. An interesting example of this is a divider design which employs five pipeline stages arranged in a circle which allows enough time for clears to have been performed before the data comes full circle [71]. The primary disadvantage of this technique is that more logic is

| $A^1$ | $A^0$ | Meaning   |

|-------|-------|-----------|

| 0     | 0     | cleared   |

| 0     | 1     | logical 0 |

| 1     | 0     | logical 1 |

| 1     | 1     | illegal   |

Figure 2.3: Dual rail encoding of binary numbers

required than for a clocked implementation but with increasing chip densities and the problems with fast clocks, dual rail encoding is looking attractive.

Dual rail encoding, micropipelines and variations on the clocking theme are active research areas and it is unclear which will be the most successful. However, it is possible to draw the conclusion that whichever method is employed, some form of localised signalling or clocking domains is essential.

# 2.4 Summary of hardware and software requirements

The section on software motivations has identified the basic needs to support most applications' functional requirements (see list of desirable processor requirements on the next page). Then more specific application areas were identified and categorised according to their temporal requirements. These categories are: best effort, hard real-time and multimedia or quality of service based. An overview of benchmarks was presented because they represent the execution requirements which motivate processor designs. However, to date the majority of standard benchmarks are representative of best effort applications. Inevitably, this results in processors which are tailored to provide good best-effort performance even when this is to the detriment of supporting other categories of application. Consequently there is a vicious circle where the software designers develop languages and coding methods which yield good performance using today's processors, leaving commercial processor designers to optimise current designs.

The section on hardware motivations introduced two fundamental problems with designing computers on large and increasingly dense VLSI technology, namely signal transmission speed limitations and the fact that the popular submicron CMOS technology does not become significantly faster as density increases beyond a feature size of  $0.5\mu m$ . The problems of transmitting higher frequency global clocks were also addressed, concluding that control signals benefit from being localised. In the future some form of self-timed circuit technique may provide the required characteristics. However, it was also noted that there are many possible technologies on the horizon which will inevitably introduce different design parameters and techniques.

# **Desirable Processor Attributes**

- functional primitives

- arithmetic (both integer and floating-point) and logic primitives

- conditional and subroutine primitives

- synchronisation primitives

- memory structure and access mechanisms

- local storage of intermediate results (to avoid over use of the main memory)

- indirect addressing

- virtual addressing

- multiple assignment (and support for sequential algorithms)

- scalable interconnect (to avoid signal transmission problems)

- protection mechanisms

- memory protection

- supervisor mode (to allow protection domains to be set up)

- concurrency (processor sharing)

- including support for a sensible scheduling policy

- parallelism (multiple processors and multiple pipelines)

- efficient synchronisation of internal and external events

- temporal predictability

- a distributed real-time clock at the highest practical frequency

- localised signalling (avoid using global signalling like processor frequency clocks)

# **Chapter 3**

# **Current Processor Models**

#### 3.1 Introduction

This chapter is a commentary on current processor models with references to more indepth material. To begin with, the control-flow processor model (section 3.2) is presented because it dominates today's computer market.

Control-flow processors primarily exhibit sequential behaviour. At the other extreme, there are data-flow processors (section 3.3) which can exploit instruction level concurrency. Both of these models have their advantages and disadvantages but one tends to have strengths where the other has weaknesses. Various amalgams of these ideas, often referred to as *multithreaded* processors, exhibit improved characteristics (section 3.4).

# 3.2 Control-flow processors

The fundamental control-flow processor model was originally proposed by Eckert, Mauchly and von Neumann in 1944 and was based upon the Analytical Engine design proposed by Babbage in 1838 [69]. Programs are constructed as a linear list of *order codes*, or *instructions*, which control the processing of data. The list is traversed using a pointer — the *program counter*. Decisions are supported through changing the flow of control by conditionally modifying the program counter.

Fundamentally, this model still underpins the ubiquitous control-flow machine of today. However, many improvements in functionality have been made from the support of reusable subprograms, or *subroutines* using the Wheeler jump [68], to interrupts (reputably first introduced on the UNIVAC 1103 [60]) and beyond. There have been many performance improvements which may be grouped into:

• memory structure and data locality (e.g. the use of a register file and cache)

- instruction coding

- instruction parallelism

- data parallelism

Other issues are less performance critical on today's control-flow machines, when assessed using many industrially recognised benchmarks, which include:

- concurrency and synchronisation primitives

- protection mechanisms

The following sections briefly review each of these areas. More detail may be found in the plethora of computer architecture texts, good examples of which are [32, 54, 60].

#### 3.2.1 Memory structure and data locality

A memory is required to store programs and data. To an application the memory appears as a linear collection of bits, bytes or words which may be indexed by an *address*. However, virtual addressing may be employed to simplify memory allocation by allowing blocks, or *pages*, of virtual addresses to be mapped on to any physical page. If there are more active virtual pages than physical pages in main memory, then backing store may be used as an overflow memory, pages being *paged* between backing store and main memory on demand. Each application may have an independent set of virtual addresses. Alternatively applications may reside in a single virtual address space which is particularly useful if data and code are to be shared. 64 bit address systems are well suited to the latter approach because the large virtual address space is unlikely to be totally consumed.

Intermediate results are usually held in a very small multi-ported memory which is local to the processor (a register file). This allows several values to be read and written simultaneously and at high speed which is not possible with main memory due to its large size and distance from the processor (see section 5.2). Instead of a register file, a stack model may be presented. To allow efficient access to the most frequently used values at the top of the stack, they must be cached in some small, high speed multi-ported memory (e.g. Crisp [7], which is the forerunner to AT&T's Hobbit [5]). Both register file and stack based approaches usually use some short form of addressing to reduce instruction size; in the case of a register an index into the register file is used and for stacks a short offset from the top of the stack suffices.

To bridge the performance gap between main memory and the register file, one or more levels of caching may be used to store intermediate results. This relies on the principle of locality which is that a few addresses are accessed most of the time (temporal locality) and that many of the accesses are within a few groups of addresses (spatial locality). When caches were first introduced to microprocessors they were often shared between the instruction and data fetch sections. More recent systems have a separate cache for instructions and data (e.g. the Motorola MC88000 [49] and Digital's Alpha [20]). However, a recent fashion is to have one large wide unified cache and a short instruction buffer which is capable of reading several instructions from the cache at once (e.g. the PowerPC 601 [62]). Since data accesses typically account for 40% of instructions executed (at least for RISC processors [54]), the instruction and data accesses may be successfully interleaved with few occasions when the processor is starved of instructions. However, when the density of chips increases we are likely to see the re-emergence of separate caches because the single cache cannot be made much larger and still be sufficiently fast.

Memory for multi-processor systems is frequently based upon caching data which is currently being accessed and/or modified. Access mechanisms must be provided to ensure data integrity is maintained when multiple processors compete over writing to the same memory area. One approach is to broadcast writes to all processors so that they may update their cache. A specialisation of this, called *snooping*, broadcasts the information on a bus. However, broadcasting information from many sources becomes increasingly costly as the number of sources increases. Alternatively, a directory may be used to record which processors have a read only copy of information so that invalidation of the information may be achieved by multicasting to the appropriate processors. For example, the Stanford Dash multiprocessor [42] supports a distributed directory structure for shared memory between clusters of processors, and snooping within clusters.

# 3.2.2 Instruction coding

Typically, instructions consist of one or more operations (specified by *op-codes*<sup>1</sup>) and zero or more operands<sup>2</sup> to specify data source and destination. The type of the operands may be specified as part of the op-code, some separate field or by the data itself in the case of typed memory (see sections 6.6 and 6.7). Some operands may be implicit in the op-code so do not need to be specified. For example, *set interrupt mask bit* or *skip next instruction if the carry is set* instructions do not need to specify any operands. Operands may be in terms of an index into a register file, an index into a stack or a memory address, where the address may be a constant or be calculated using registers or a stack.

<sup>&</sup>lt;sup>1</sup>Although an op-code is unnecessary on a single instruction computer, e.g. r-move [48].

<sup>&</sup>lt;sup>2</sup>Single operand instructions being referred to as *monadic*, double operand instructions as *dyadic* and triple operand instructions as *triadic*, etc.

When main memory was expensive it was advantageous for instructions to be as compact and full functioned as possible. This lead to the design of a breed of *complex instruction set computers* (CISCs) which relied upon variable length instructions for compactness, where each instruction could perform some very complex operation. For example, VAXs had a POLY instruction for evaluating polynomials [43].

Stack based machines also require a variable length instruction because operands are indexed off the stack, the index often being short but sometimes very long.

Memory became cheaper and it was realised that high level language compilers produced code which only made frequent use of a subset of the CISC instructions. This prompted the design of reduced instruction set computers (RISC) where the most frequently used, and also the indispensable, instructions were supported and made as fast as possible. The infrequent operations were synthesised from a combination of the frequent instructions. In order to make these simple instructions execute as fast as possible, simple decoding was desirable. Therefore, RISC instructions were fixed length and came in a few basic forms. Fixed length instructions mean that multiple main memory operands were impractical because they would make the instruction length prohibitively long (assuming reasonable offsets need to be specified). This resulted in the load/store approach where the only instructions which can access memory are the dyadic load and store, triadic data manipulation instructions being register-to-register.

# 3.2.3 Instruction parallelism

Executing an instruction takes some or all of the following steps: instruction fetch, instruction decode, operand fetch, execution/calculation, memory access, register file write. Some of these steps may be performed in parallel but many have interdependencies (e.g. instruction fetch must occur before it is known which operands are required) which imposes some ordering. However, steps for different instructions may be overlapped using a pipeline. For example, whilst operands are being fetched the next instruction may be fetched. Pipelines may be a simple linear structure but more often subpipelines are used to process instructions which require more complex processing. For example, floating point and integer multiply and divide operations require a longer execution time. This leads on to parallel execution of integer and floating point operations.

Provided several instructions may be fetched and their interdependencies resolved, it is possible to simultaneously issue multiple instructions to several integer and floating point pipelines. Such an execution structure is referred to as *superscalar*. An alternative to the superscalar approach, where the grouping of instructions for parallel execution is dynamic, is to perform the grouping statically to form a *very long instruc*-

tion word (VLIW). For example, the Multiflow TRACE 14/300 VLIW computer [59] with a 512 bit instruction format which takes two cycles to execute but can issue up to 8 integer operations, 4 floating-point operations and one branch operation concurrently.

An alternative to VLIW is to specify the data movements between ALUs, register files, etc., rather than specifying which operations need to be performed. This technique is know as *transport triggered* [17, 16] because data arriving at, say, an ALU triggers some function evaluation to be performed; the result of which is placed into an output buffer or FIFO until it is moved by another transport operation. This idea is very similar to microcode [60] which is composed of instructions with a fairly verbose encoding of all the hardware control signals required on a cycle by cycle basis.

As we move from the high-level CISC, RISC and superscalar instructions through to VLIW, transport triggered and low-level microcode instructions, more potential parallelism may be elicited. However, the encodings become more verbose which often results in poor memory usage. Furthermore, the *programmer's model*<sup>3</sup> becomes more complex as we move from the high-level CISC to the low-level microcode. As the programmer's model becomes more processor implementation specific, the code becomes less portable. However, lower level instructions which are tailored to a particular processor implementation (e.g. transport triggered) can be simpler to execute and can allow more parallelism to be elicited. One solution to the problem of portability of code is to compile to some intermediate form (either completely general or processor family specific) which may then be converted into a highly optimised low-level processor specific form.

Another form of instruction parallelism is exhibited by multi-processor computers, often called multiple-instruction, multiple-data (MIMD) after Flynn's classification [25]. Whilst, for example, superscalar systems offer instruction level parallelism for a single control-flow program, MIMDs offer a coarse level of parallelism with data communication, either by shared memory or message passing. Of course superscalar and MIMD approaches may be combined.

#### 3.2.4 Data parallelism

Data parallelism is often achieved as a consequence of instruction parallelism. Flynn's classification [25] also identifies *single instruction, multiple data* (*SIMD*) computers (e.g. CLIP7A [26], DAP [53] and CM2 [33]). They tend to be used for specialist tasks, like graphics and finite element analysis, which can easily be split into many identical parallel tasks with little data dependency. Vector processing may be considered as a subset of the SIMD technique (e.g. Cray-1 [34]).

<sup>&</sup>lt;sup>3</sup>The programmer's model is one which is sufficient to enable working code to be written. A more detailed model may be required to write efficient code.

#### 3.2.5 Concurrency and synchronisation primitives

Synchronisation of data between instructions is achieved by the sequential ordering imposed by the control-flow model. This makes multiple assignment and access to I/O relatively easy. Whilst superscalar systems may perform instructions out of order they may only do so when a change of ordering will not affect the result.

Synchronisation of data coming in from an input device<sup>4</sup> is commonly achieved by sending the processor an *interrupt* signal which causes the thread of control to be suspended and forces execution to start at a particular address — usually the start of an interrupt handler routine. Concurrency is also achieved using this mechanism by using a timer to interrupt the processor at a regular period. The software interrupt handler determines where the interrupt came from and restarts a thread based upon a scheduling decision. It should be noted that *context switching* (changing threads) and scheduling decisions are typically performed in software.

#### 3.2.6 Memory protection mechanisms

A memory access protection mechanism is provided by most processors to prevent separate applications from accidently or maliciously modifying or reading another application's data. This is extended to protect I/O devices which are often memory mapped. Protection may be at several levels and at a varying granularity; for example, capabilities [70] and rings [58]. However, complex protection mechanisms do incur costs, both in terms of execution time and processor complexity.

Multi-level and fine grained protection is typically used for intra-application protection as well as inter-application protection. However, modern high level language compilers can statically check many intra-application memory accesses. Furthermore, inter-application protection is often sufficient at the page level and may efficiently be combined with the virtual to physical address translation mechanism. Thus, page based protection is the norm.

Setting up a simple page based memory protection mechanism requires a *supervisor mode* (sometimes called a *trusted mode* or *privileged mode*), where the protection is turned off. Usually only a trusted part of the operating system (or *trusted kernel*) is allowed to obtain the supervisor privilege. Entering supervisor mode usually only occurs when a hardware interrupt, or its software counterpart (a *trap* or *call\_pal*<sup>5</sup>), occurs and usually the code which is invoked is the trusted part of the operating system kernel. Thus, supervisor mode cannot be obtained subversively, which completes the memory protection system.

<sup>&</sup>lt;sup>4</sup>Arriving data may simple be placed in an input queue which needs to be read by software, or it may be transferred directly to the main memory (direct memory access or DMA).

<sup>&</sup>lt;sup>5</sup>call\_pal is the Alpha version of a software trap which will be referred to again in chapter 6.

#### 3.2.7 Assessment of the control-flow model

Control-flow processors completely dominate the computer industry and so many refinements have been made to improve performance. Electronics technology has allowed micro-processors to become more complex so that they can embody many of the desirable features developed for past mainframe computers. However, many of the architectural refinements, like the superscalar technique, have limited application. For example, the instruction level parallelism extracted by the superscalar approach is limited by data interdependencies which at best is limited by the number of registers.

The MIMD approach may be used to attain more parallelism but is limited by synchronisation and transfer overheads associated with sharing data. In particular, application level synchronisation primitives are not usually supported by the hardware. Furthermore, for many applications it is difficult to efficiently divide the program into separate cause grained tasks, or *threads of control*.

The inherently single threaded nature of control-flow machines means that the latency of cache misses tends to stall execution due to data dependencies. As memories become larger, and control-flow processors become faster, there is going to be an increasing reliance on good cache performance. Unfortunately, this means that the temporal characteristics of systems are going to become increasingly nondeterministic.

Despite the problems of the control-flow model it will no doubt continue to be refined and be used for a wide range of applications which require best effort performance and limited parallelism. The dominance of the control-flow model means than any serious move towards an alternative paradigm must provide some backward compatability.

# 3.3 Data-flow processors

Whilst control-flow programs explicitly define the order of execution which ensures that data is manipulated in the required order, data-flow programs specify the data-dependencies and allow the processor to choose one of the possible orderings. Data-dependencies may be represented as a directed graph where instructions form the nodes and the data-dependencies form the arcs (see figure 3.1). Any instruction which has received its operands may be executed, thereby allowing parallel execution. Furthermore, logically separate data-flow routines run at an instruction level of concurrency which is coordinated by a hardware scheduler.

The next sections present a brief overview of different data-flow paradigms. Then the preferred paradigm, tagged-token data-flow, is assessed.

#### control-flow data-flow destination 'a' duplicated\_ load r0,(sp+a) by source node load r1,(sp+b) multiply divide a node = an <instruction mul r0,r1,r2 matching load r1,(sp+c) add or joining div r0,r1,r0 data path = arc add r2,r0,r0 return rts

Example function: f(a,b,c) := a.b + a/c

Figure 3.1: An example of control-flow and data-flow program structure

returned value

#### 3.3.1 Static data-flow

With static data-flow [19] there is at most one *token* (datum) on an *arc* — path between one data-flow instruction and the next. The values on the arcs, or *operands*, are stored with the instruction. To ensure operands are not overwritten before they are used there are backward signal arcs which inform previous instructions when the instruction has been executed (i.e. when the operands have been used and the destinations have been written to). Figure 3.2 presents an example instruction format.

| op-code | op1 | (op2) | dest1 + dc1 | (dest2 + dc2) | sig1 | (sig2) |

|---------|-----|-------|-------------|---------------|------|--------|

where () indicates optional parameters

op-code is the instruction identifier

op1 and op2 are the spaces for operands (op2 missing for monadic operations)

dest1 and dest2 are the destinations (dest2 being optional)

dc1 and dc2 are destination clear flags (initially clear)

sig1 and sig2 are the signal destinations (handshaking arcs)

Figure 3.2: Example static data-flow instruction format

There are problems with static data-flow:

- Shared functions are difficult to implement because mutual exclusion must be enforced upon writing all of the operands to the function. This severely limits concurrency and is often inefficiently solved by replicating functions either statically or dynamically.

- The backward signal arcs double the number of tokens to be matched.

## 3.3.2 Coloured dynamic data-flow

With dynamic data-flow there may be many tokens per arc. In the coloured data-flow paradigm associated tokens are given an unique identifier, or *colour*. This allows functions to be represented because each invocation of a function is given a unique colour. Only operands with the same colour may be matched in dyadic operations. An example of coloured data-flow is the Manchester prototype [30]. The RMIT hybrid [1] also utilises coloured data-flow to encapsulate functions but supports static data-flow within functions.

The main problems are:

- Matching colours is expensive and temporally unpredictable often implemented using hashing.

- Uncontrolled fan-out can cause too many concurrent parts to be initiated resulting in matching store overflow.

# 3.3.3 Tagged token dynamic data-flow

An alternative paradigm (used for the MIT Monsoon machine [51]) is to remove operand storage from the instruction and to place it in a data page, or *activation frame*. Activation frames effectively store the context of a function. This may be implemented using a conventional flat memory store with the addition of a *presence* bit (an empty/full flag) for each word in memory. The advantage is that each instantiation of a function has its own separate activation frame which makes matching of operands easy:

- instantiating a function obtain an unused activation frame and set all of the flags to empty.

- matching a token to a monadic instruction the token's statement pointer (see figure 3.3) is used to lookup the instruction to be executed which forms an executable packet to be queued for execution.

• matching a token to a dyadic instruction — the token's statement pointer is used to look up the instruction to be executed. The instruction's r value (see figure 3.3) is then added to the token's context pointer value to form an address in the activation frame (i.e. r forms an offset into the activation frame). If there is a value in the activation frame then that value is read and matched with the token's data value which is sent, with the instruction information, to be executed and the activation frame location is set to empty. If there was not a value in the activation frame then the token's data value is stored in the activation frame to wait for its partner and the presence flag is set to full.

The matching scheme may be extended (e.g. the EM4 machine [57]) to allow intermediate results to be held in a register file, rather than being passed via a matching store, whilst instructions are executed in a control-flow manner. In the EM4 implementation the control-flow sections are limited by the number of input values into one instruction (dyadic or monadic) followed by a linear sequence of operations fetching their operands from the register file (i.e. the control-flow segments are limited to at most two input parameters).

#### Example instruction format

| op-code (r) | dest1 | (dest2) |

|-------------|-------|---------|

|-------------|-------|---------|

where

() indicates optional parametersop-code is the instruction identifierr is the activation frame offset number for dyadic operations

dest1 and dest2 are the destinations (dest2 being optional)

#### Example tagged token

|       |        | context pointer                                             |   | r s                                                       | tatement    | pointer | port | data |  |

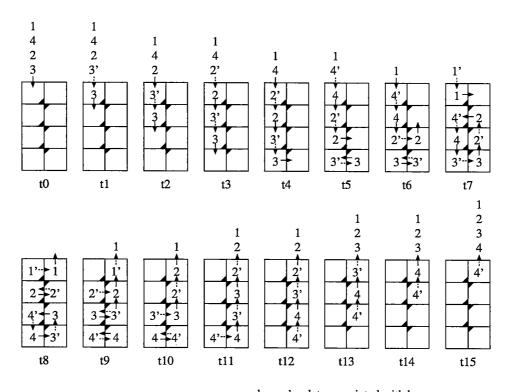

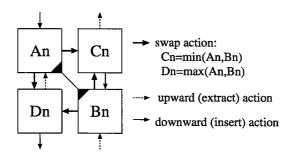

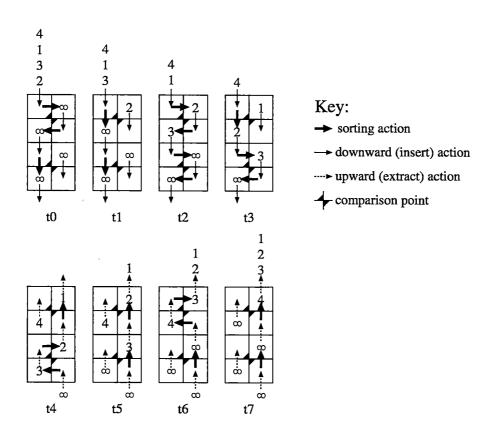

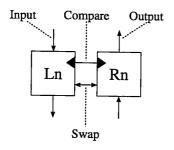

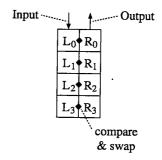

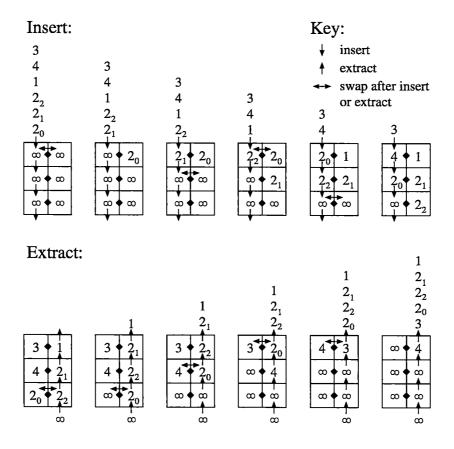

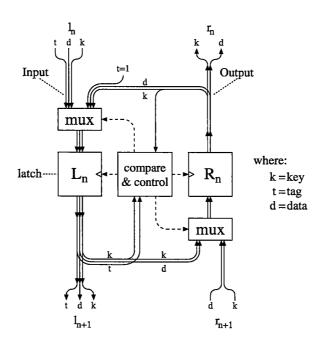

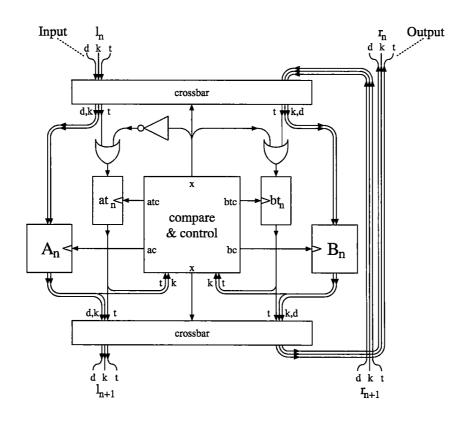

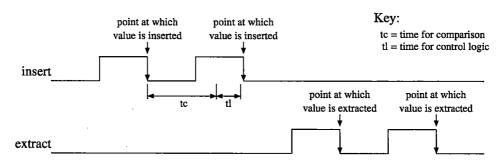

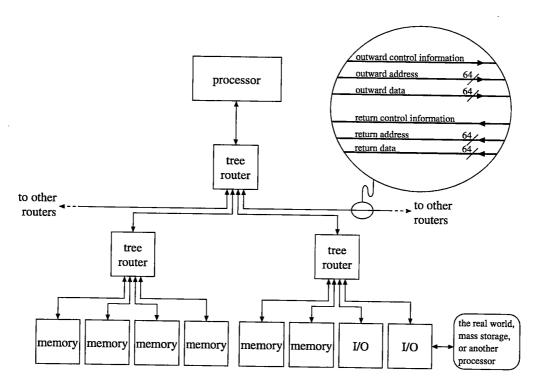

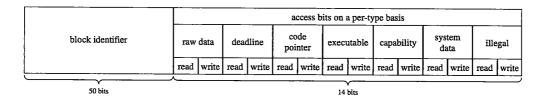

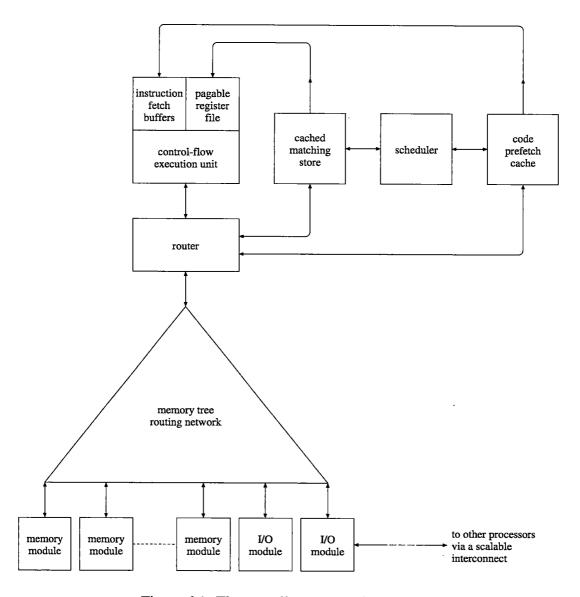

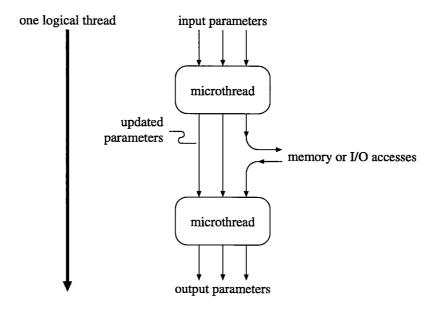

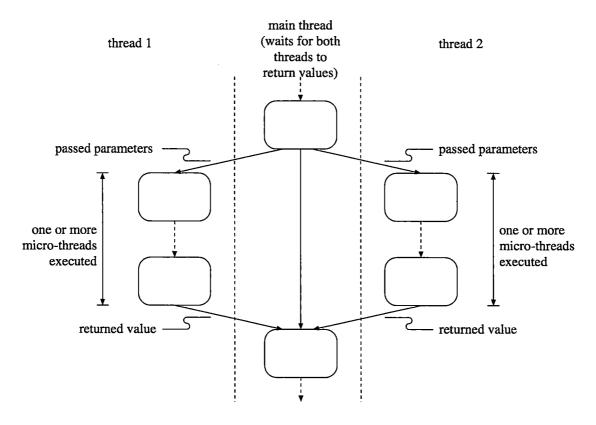

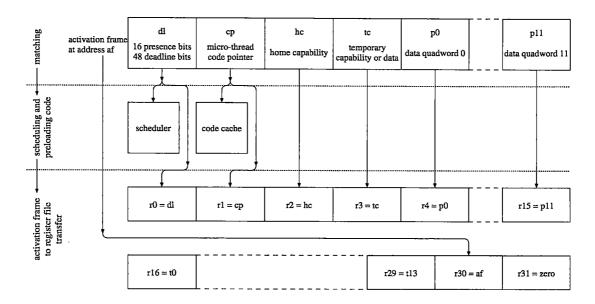

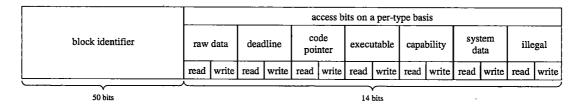

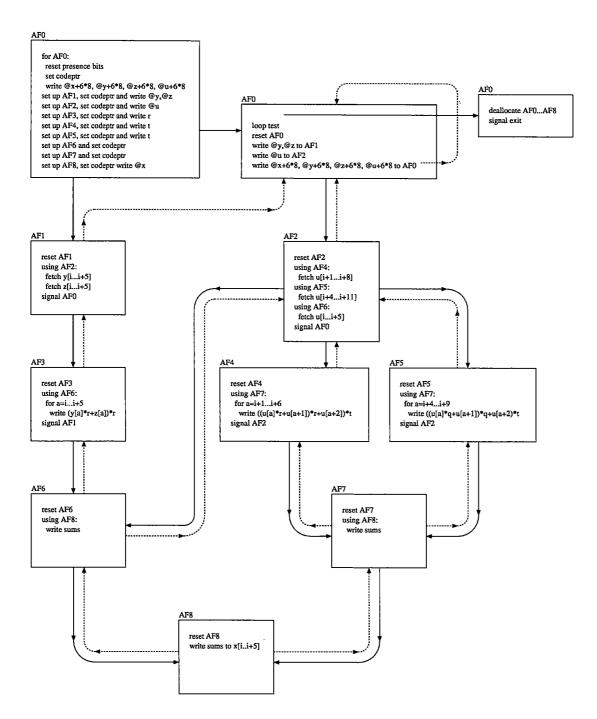

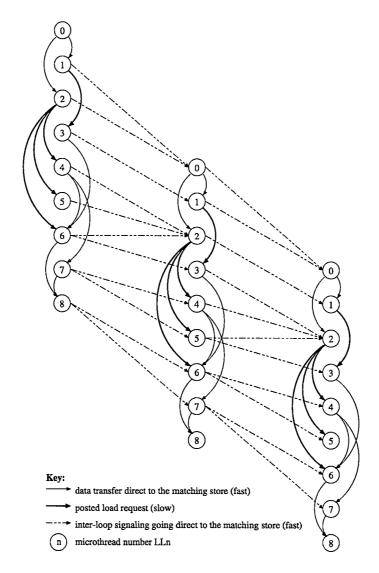

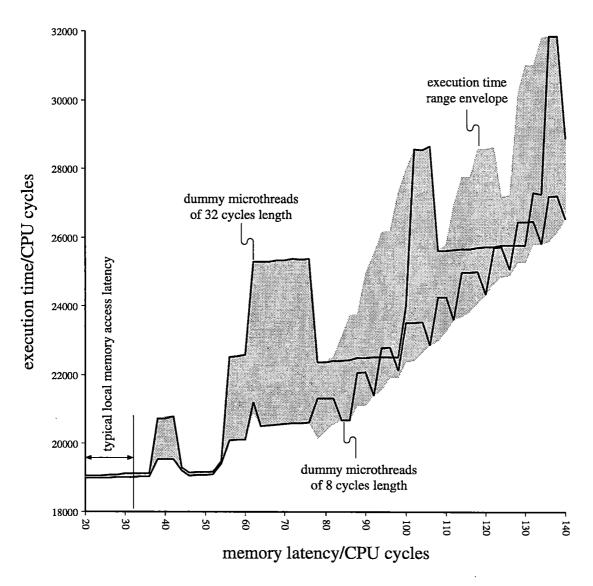

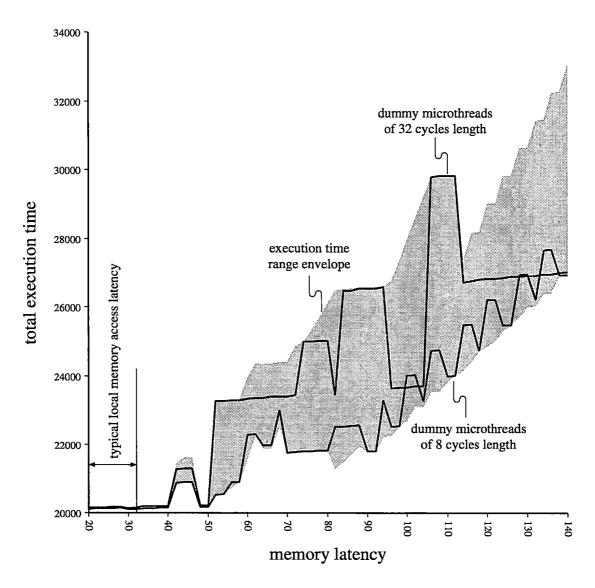

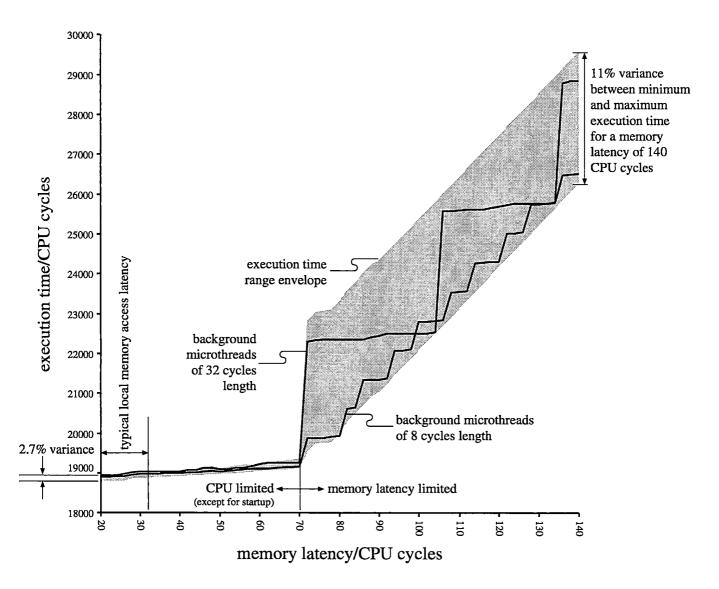

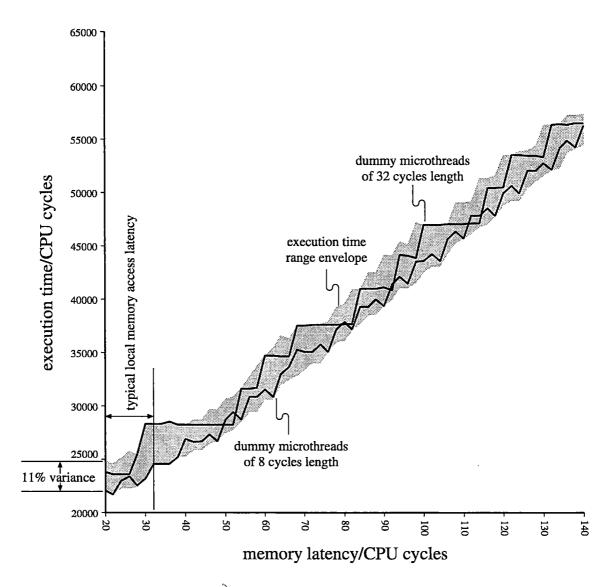

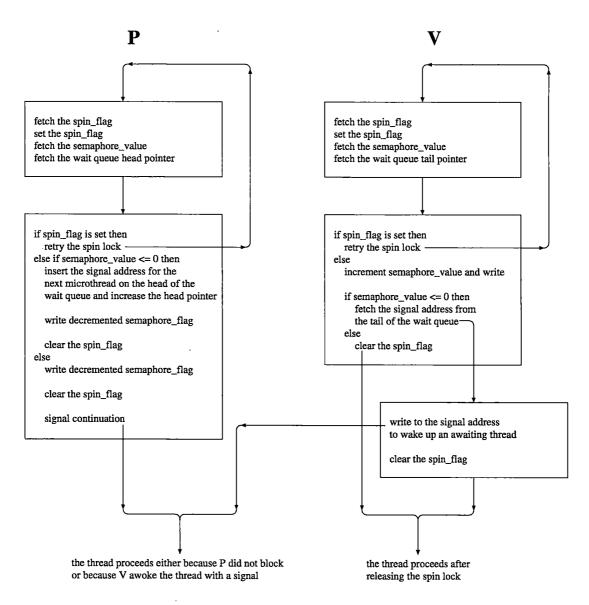

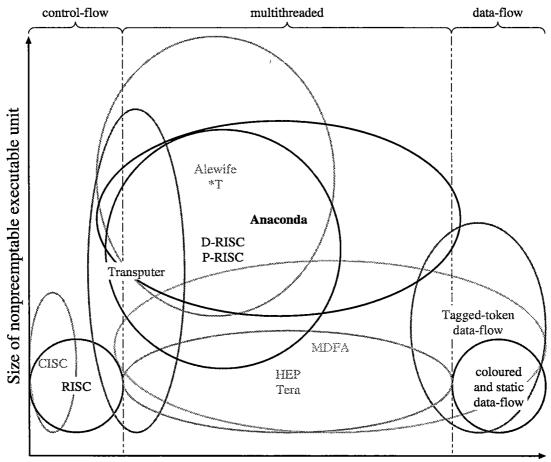

|-------|--------|-------------------------------------------------------------|---|-----------------------------------------------------------|-------------|---------|------|------|--|