Technical Report

Number 329

**Computer Laboratory**

# The formal verification of the Fairisle ATM switching element

Paul Curzon

March 1994

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

© 1994 Paul Curzon

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Contents

| 1 | $\operatorname{Intr}$ | Introduction 1 |                       |          |

|---|-----------------------|----------------|-----------------------|----------|

| 2 | $\mathbf{Gen}$        | eral D         | Definitions           | 1        |

|   | 2.1                   | Words          |                       | 1        |

|   |                       | 2.1.1          | REMBIT                | 1        |

|   |                       | 2.1.2          | BITS                  | 2        |

|   |                       | 2.1.3          | WSEGS                 | 2        |

|   |                       | 2.1.4          | BWORDLEN              | 2        |

|   |                       | 2.1.5          | PBITLEN               | 2        |

|   |                       | 2.1.6          | PWORD2LEN             | 2        |

|   |                       | 2.1.7          | MKW                   | 3        |

|   |                       | 2.1.8          | MKCW                  | 3        |

|   |                       | 2.1.9          | MKW2                  | 3        |

|   |                       | 2.1.10         | WRFOLD_DEF            | 3        |

|   |                       |                | ZEROW                 | о<br>З   |

|   | 2.2                   |                | on Vectors            |          |

|   | 2.2                   | <b>2.2.1</b>   |                       | 3<br>7   |

|   |                       | 2.2.1<br>2.2.2 |                       | 4        |

|   |                       |                | PVECN                 | 4        |

|   | 0.0                   | 2.2.3          | WPVEC                 | 4        |

|   | 2.3                   | -              | s                     | 4        |

|   |                       | 2.3.1          | SLIFT                 | 4        |

|   |                       | 2.3.2          | SWORD                 | 4        |

|   |                       | 2.3.3          | SBIT                  | 5        |

|   |                       | 2.3.4          | SWSEG                 | 5        |

|   |                       | 2.3.5          | SWSEGS                | 5        |

|   |                       | 2.3.6          | SBITS                 | <b>5</b> |

|   |                       | 2.3.7          | SREMBIT               | <b>5</b> |

|   |                       | 2.3.8          | SEXISTSABIT           | 5        |

|   |                       | 2.3.9          | SIGLEN                | 5        |

|   |                       | 2.3.10         | BSIGLEN               | 6        |

|   |                       | 2.3.11         | PSIGLEN               | 6        |

|   |                       | 2.3.12         | PSIG2LEN              | 6        |

|   | 2.4                   | Genera         | al Definitions        | 6        |

|   |                       | 2.4.1          | BETWEEN               | 6        |

|   |                       | 2.4.2          | ΤΟ                    | 6        |

|   |                       | 2.4.3          | DUP                   | 6        |

|   |                       | 2.4.4          | Results               | 7        |

|   | 2.5                   | Signal         | values over intervals | 7        |

|   |                       | 2.5.1          | DURING                | 7        |

|   |                       | 2.5.2          | STABLE                | 7        |

|   |                       | 2.5.3          | NEXT                  | 7        |

|   | 2.6                   | Frames         | 3                     | 8        |

|   |                       | 2.6.1          | FRAME                 | 8        |

|   |                       | 2.6.2          | Inactive Frames       | 8        |

|   |                       |                |                       | -        |

\_

ć

|     | 2.6.3                 | Active Frames                    | 8        |

|-----|-----------------------|----------------------------------|----------|

| 2.7 | Logica                | al Connectives                   | 9        |

|     | 2.7.1                 | Jk                               | 9        |

|     | 2.7.2                 | JkE                              | 10       |

|     | 2.7.3                 | XOR                              | 10       |

|     | 2.7.4                 | XNOR                             | 10       |

|     | 2.7.5                 | LGATE                            | 10       |

|     | 2.7.6                 | NLGATE                           | 10       |

|     | 2.7.7                 | DEL1                             | 10       |

|     | 2.7.8                 | WIRE                             | 10       |

| 2.8 | Xilinx                | Logic Gates and Latches          | 11       |

|     | 2.8.1                 | LOCAL                            | 11       |

|     | 2.8.2                 | FOR                              | 11       |

|     | 2.8.3                 | XiINV                            | 11       |

|     | 2.8.4                 | XiAND                            | 12       |

|     | 2.8.5                 | XiNAND                           | 12       |

|     | 2.8.6                 | XiOR                             | 13       |

|     | 2.8.7                 | XiNOR                            | 13       |

|     | 2.8.8                 | XiXOR2                           | 11       |

|     | 2.8.9                 | XiXNOR2                          | 14       |

|     |                       | XiIBUF                           | 14       |

|     |                       |                                  | 14<br>15 |

|     |                       |                                  | 15<br>15 |

|     |                       |                                  | 15<br>15 |

|     |                       |                                  | 15<br>15 |

|     |                       |                                  | 15<br>16 |

|     |                       |                                  |          |

|     |                       |                                  | 16       |

|     |                       |                                  | 17       |

| 2.9 |                       |                                  | 17       |

| 2.9 |                       |                                  | 17       |

|     | 2.9.1                 | •                                | 18       |

| •   | 2.9.2                 | DecoderPriorities                | 18       |

|     | $\frac{2.9.3}{2.9.4}$ |                                  | 18       |

|     | 2.9.4 $2.9.5$         |                                  | 18       |

|     |                       |                                  | 19       |

|     | 2.9.6                 |                                  | 19       |

|     | 2.9.7                 |                                  | 20       |

|     | 2.9.8                 |                                  | 20       |

|     | 2.9.9                 |                                  | 20       |

|     |                       |                                  | 20       |

|     |                       |                                  | 21       |

|     |                       |                                  | 21       |

|     |                       |                                  | 21       |

|     |                       |                                  | 22       |

|     | 2.9.15                | Accessing the fields of a header | 22       |

# iv

•

|   |     | 2.9.16 | Accessing the fields of a word of headers | 22 |

|---|-----|--------|-------------------------------------------|----|

|   |     | 2.9.17 | Fabric4x1Ack                              | 23 |

|   |     | 2.9.18 | Fabric4x1Last                             | 23 |

|   |     | 2.9.19 | Fabric4x1DataOut                          | 23 |

|   |     |        |                                           |    |

| 3 | The | Modu   | -                                         | 4  |

|   | 3.1 | IN_BUF |                                           | 24 |

|   |     | 3.1.1  | The Behavioural Specification             | 24 |

|   |     | 3.1.2  | The Structural Specification              | 24 |

|   |     | 3.1.3  | The Correctness Statement                 | 24 |

|   | 3.2 | OUT_BU | JF                                        | 24 |

|   |     | 3.2.1  | The Behavioural Specification             | 24 |

|   |     | 3.2.2  | The Structural Specification              | 25 |

|   |     | 3.2.3  | The Correctness Statement                 | 25 |

|   | 3.3 | ILATCH | H2                                        | 25 |

|   |     | 3.3.1  | The Behavioural Specification             | 25 |

|   |     | 3.3.2  | The Structural Specification              | 25 |

|   |     | 3.3.3  | The Correctness Statement                 | 6  |

|   | 3.4 | IN_LAT | СН 2                                      | 6  |

|   |     | 3.4.1  | The Behavioural Specification             | 6  |

|   |     | 3.4.2  | The Structural Specification              | 6  |

|   |     | 3.4.3  | The Correctness Statement                 | 6  |

|   | 3.5 | OLATCH | _                                         | 7  |

|   |     | 3.5.1  |                                           | 7  |

|   |     | 3.5.2  |                                           | 7  |

|   |     | 3.5.3  | The Correctness Statement                 | 7  |

|   | 3.6 | OUT_LA | атсн                                      | 8  |

|   |     | 3.6.1  | The Behavioural Specification             | 8  |

|   |     | 3.6.2  |                                           | 8  |

|   |     | 3.6.3  |                                           | 8  |

|   | 3.7 | LATCH  |                                           | 8  |

|   |     | 3.7.1  |                                           | 8  |

|   |     | 3.7.2  | The Structural Specification              |    |

|   |     | 3.7.3  | The Correctness Statement                 |    |

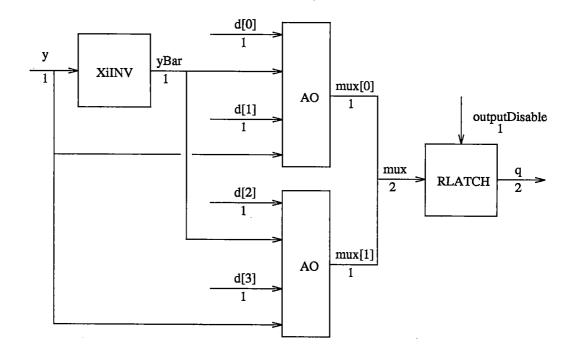

|   | 3.8 | RLATCH | <b>1</b>                                  |    |

|   |     | 3.8.1  | The Behavioural Specification             |    |

|   |     | 3.8.2  | The Structural Specification              |    |

|   |     | 3.8.3  | The Correctness Statement                 |    |

|   |     | PAUSE  |                                           |    |

|   |     | 3.9.1  | The Behavioural Specification             |    |

|   |     | 3.9.2  | The Structural Specification              |    |

|   |     | 3.9.3  | The Correctness Statement                 |    |

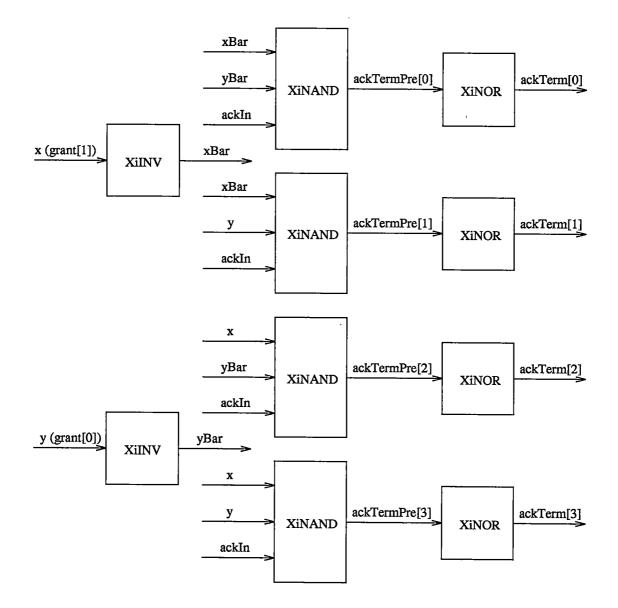

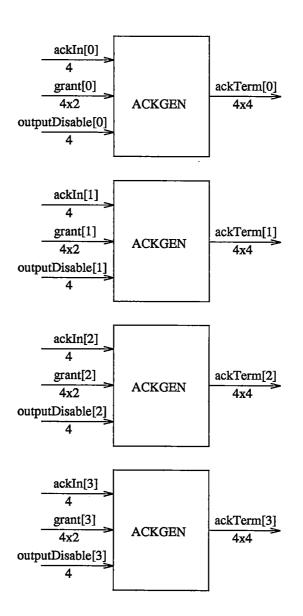

|   |     | ACKOR  |                                           |    |

|   |     | 3.10.1 | The Behavioural Specification             |    |

|   |     |        | The Structural Specification              |    |

|   |     |        |                                           | Ŧ  |

|      | 3.10.3 The Correctness Statement     | 31       |

|------|--------------------------------------|----------|

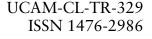

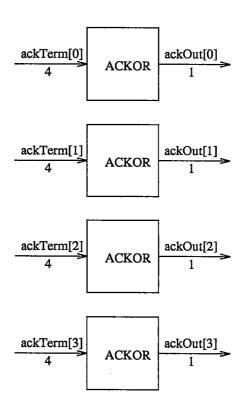

| 3.11 | ACKGEN                               | 31       |

|      | 3.11.1 The Behavioural Specification | 31       |

|      | 3.11.2 The Structural Specification  | 32       |

|      | 3.11.3 The Correctness Statement     | 32       |

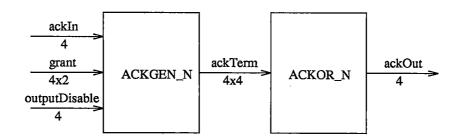

| 3.12 | ACKOR_N                              | 34       |

|      |                                      | 34       |

|      |                                      | 34       |

|      |                                      | 35       |

| 3.13 | ACKGEN_N                             | 35       |

|      |                                      | 35       |

|      |                                      | 36       |

|      |                                      | 37       |

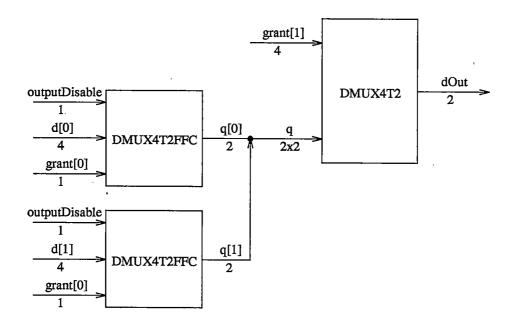

| 3.14 |                                      | 37       |

|      |                                      | 37       |

|      |                                      | 38       |

|      |                                      | 39       |

| 3.15 |                                      | 39       |

|      |                                      | 39       |

|      |                                      | 39       |

|      |                                      | 40       |

| 3.16 |                                      | 40       |

|      |                                      | 40       |

|      |                                      | 41       |

|      |                                      | 42       |

| 3.17 |                                      | 42       |

|      |                                      | 42       |

|      |                                      | 42<br>42 |

|      |                                      | 44       |

| 3.18 |                                      | 44<br>44 |

| 0,10 |                                      | 44<br>44 |

|      |                                      | 44<br>44 |

|      |                                      | 46       |

| 3.19 |                                      | 46       |

|      |                                      | 46       |

|      |                                      | 47       |

|      |                                      | 48       |

| 3.20 |                                      | 48       |

|      |                                      | 40<br>48 |

|      |                                      | 40<br>49 |

|      |                                      | 49<br>49 |

| 3.21 |                                      | 49<br>49 |

|      |                                      | 49<br>49 |

|      |                                      | 49<br>51 |

|      |                                      | 51<br>52 |

|      |                                      | 14       |

-

# vi

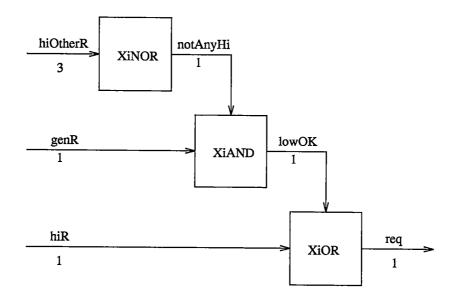

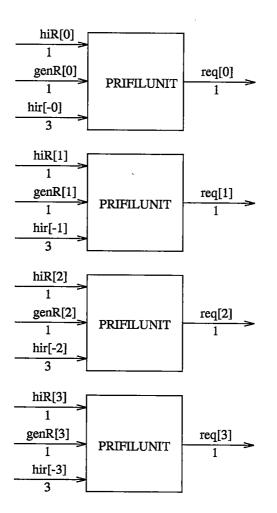

| 3 99 | PRIFILUNIT                           | 53 |

|------|--------------------------------------|----|

| 0.22 | 3.22.1 The Behavioural Specification | 53 |

|      | 3.22.2 The Structural Specification  | 53 |

|      | 3.22.3 The Correctness Statement     | 55 |

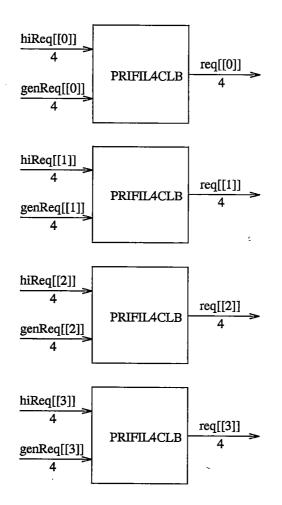

| 2 92 | PRIFIL4CLB_SPEC                      |    |

| 0.20 |                                      | 54 |

|      | 3.23.1 The Behavioural Specification | 54 |

|      | 3.23.2 The Structural Specification  | 55 |

|      | 3.23.3 The Correctness Statement     | 56 |

| 3.24 | PRIORITY                             | 56 |

|      | 3.24.1 The Behavioural Specification | 56 |

|      | 3.24.2 The Structural Specification  | 57 |

|      | 3.24.3 The Correctness Statement     | 58 |

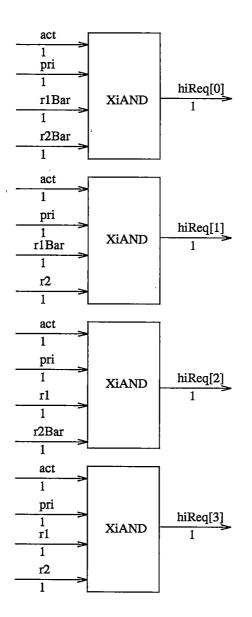

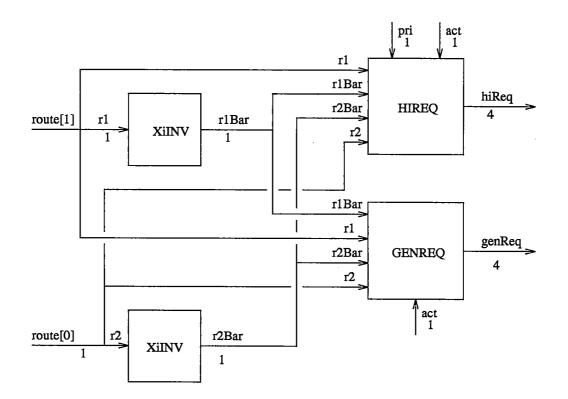

| 3.25 | HIREQ                                | 58 |

|      | 3.25.1 The Behavioural Specification | 58 |

|      | 3.25.2 The Structural Specification  | 58 |

|      | 3.25.3 The Correctness Statement     | 60 |

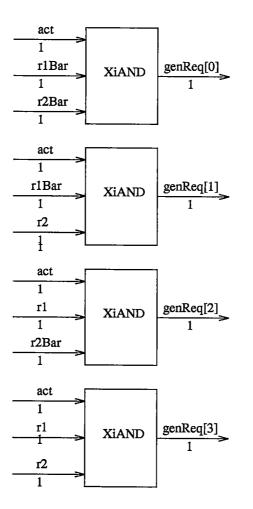

| 3.26 | GENREQ                               | 60 |

|      | 3.26.1 The Behavioural Specification | 60 |

|      | 3.26.2 The Structural Specification  | 60 |

|      | 3.26.3 The Correctness Statement     | 62 |

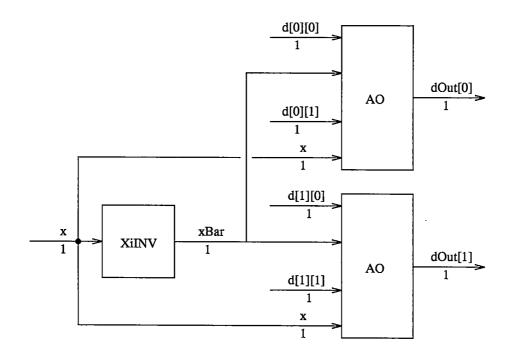

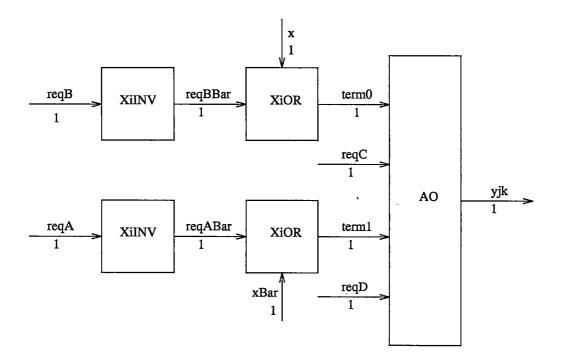

| 3.27 | DECODE                               | 62 |

|      | 3.27.1 The Behavioural Specification | 62 |

|      | 3.27.2 The Structural Specification  | 62 |

|      | 3.27.3 The Correctness Statement     | 64 |

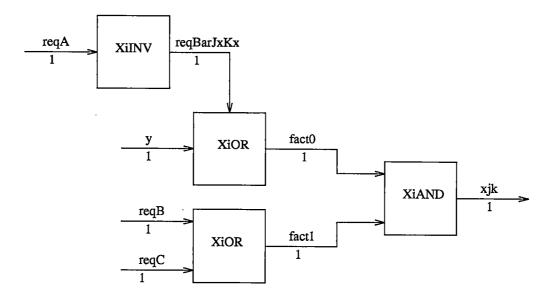

| 3.28 | DECODE_N                             | 64 |

|      | 3.28.1 The Behavioural Specification | 64 |

|      | 3.28.2 The Structural Specification  | 64 |

|      | 3.28.3 The Correctness Statement     | 66 |

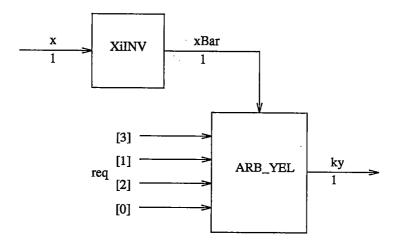

| 3.29 | ARB_YEL                              | 66 |

|      | 3.29.1 The Behavioural Specification | 66 |

|      | 3.29.2 The Structural Specification  | 66 |

|      | 3.29.3 The Correctness Statement     | 68 |

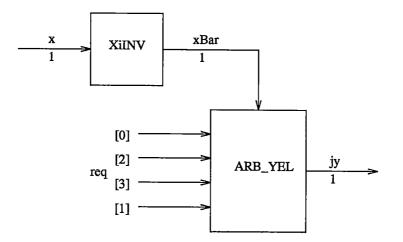

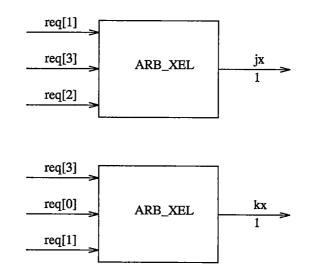

| 3.30 | ARB_XEL                              | 68 |

|      | 3.30.1 The Behavioural Specification | 68 |

|      | 3.30.2 The Structural Specification  | 68 |

|      | 3.30.3 The Correctness Statement     | 69 |

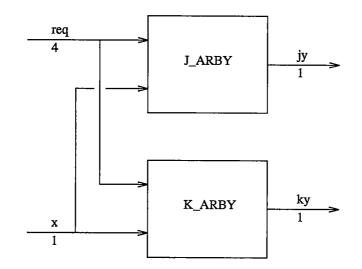

| 3.31 | K_ARBY                               | 69 |

|      | 3.31.1 The Behavioural Specification | 69 |

|      | 3.31.2 The Structural Specification  | 69 |

|      | 3.31.3 The Correctness Statement     | 70 |

| 3.32 | J_ARBY                               | 71 |

| •    | 3.32.1 The Behavioural Specification | 71 |

|      | 3.32.2 The Structural Specification  | 71 |

|      | 3.32.3 The Correctness Statement     | 72 |

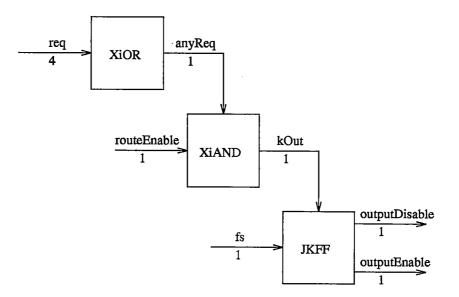

| 3.33 | ARBY                                 | 72 |

|      |                                      |    |

.

| 3.33.2 The Structural Specification         3.33.3 The Correctness Statement         3.34.1 The Behavioural Specification         3.34.2 The Structural Specification         3.34.3 The Correctness Statement         3.35.4 RBITER_FF         3.35.1 The Behavioural Specification         3.35.2 The Structural Specification         3.35.3 The Correctness Statement         3.36.1 The Behavioural Specification         3.36.2 The Structural Specification         3.36.3 The Correctness Statement         3.36.3 The Correctness Statement         3.36.3 The Correctness Statement         3.37.1 The Behavioural Specification         3.36.2 The Structural Specification         3.37.1 The Behavioural Specification         3.36.3 The Correctness Statement         3.37.2 The Structural Specification         3.37.3 The Correctness Statement         3.38.3 The Behavioural Specification         3.38.3 The Structural Specification         3.39 ARBITER         3.39.1 The Behavioural Specification         3.39.3 The Correctness Statement         3.30.1 The Behavioural Specification         3.39.3 The Correctness Statement         3.40.1 The Behavioural Specification         3.40.2 The Structural Specification         3.40.3 The Correctness Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------|

| <ul> <li>3.33.3 The Correctness Statement</li> <li>3.34.4 ARBX</li> <li>3.34.1 The Behavioural Specification</li> <li>3.34.2 The Structural Specification</li> <li>3.34.3 The Correctness Statement</li> <li>3.35.1 The Behavioural Specification</li> <li>3.35.2 The Structural Specification</li> <li>3.35.3 The Correctness Statement</li> <li>3.36.1 The Behavioural Specification</li> <li>3.36.2 The Structural Specification</li> <li>3.36.3 The Correctness Statement</li> <li>3.37.1 The Behavioural Specification</li> <li>3.37.2 The Structural Specification</li> <li>3.37.3 The Correctness Statement</li> <li>3.38.1 The Behavioural Specification</li> <li>3.38.2 The Structural Specification</li> <li>3.38.3 The Correctness Statement</li> <li>3.39.3 The Correctness Statement</li> <li>3.40 PRIORITY DECODE</li> <li>3.40.1 The Behavioural Specification</li> <li>3.40.2 The Structural Specification</li> <li>3.40.3 The Correctness Statement</li> <li>3.41.1 The Behavioural Specification</li> <li>3.41.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.41.3 The Correctness Statement</li> <li>3.41.4 The Behavioural Specification</li> <li>3.41.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.41 The Behavioural Specification</li> <li>3.42.1 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.1 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.41 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.41 The Behavioural Specification</li> <li>3.42.3 The Correc</li></ul> |        | 3.1 The Behavioural Specification    |

| <ul> <li>3.34 ARBX</li> <li>3.34.1 The Behavioural Specification</li> <li>3.34.2 The Structural Specification</li> <li>3.34.3 The Correctness Statement</li> <li>3.35.1 The Behavioural Specification</li> <li>3.35.2 The Structural Specification</li> <li>3.35.3 The Correctness Statement</li> <li>3.36.1 The Behavioural Specification</li> <li>3.36.2 The Structural Specification</li> <li>3.36.3 The Correctness Statement</li> <li>3.36.3 The Correctness Statement</li> <li>3.36.3 The Correctness Statement</li> <li>3.37.1 The Behavioural Specification</li> <li>3.37.2 The Structural Specification</li> <li>3.37.3 The Correctness Statement</li> <li>3.37.3 The Correctness Statement</li> <li>3.37.3 The Correctness Statement</li> <li>3.38.1 The Behavioural Specification</li> <li>3.37.3 The Correctness Statement</li> <li>3.38.2 The Structural Specification</li> <li>3.38.3 The Correctness Statement</li> <li>3.39 ARBITERS</li> <li>3.39.1 The Behavioural Specification</li> <li>3.39.3 The Correctness Statement</li> <li>3.40.1 The Behavioural Specification</li> <li>3.40.2 The Structural Specification</li> <li>3.40.3 The Correctness Statement</li> <li>3.41.1 The Behavioural Specification</li> <li>3.41.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.1 The Behavioural Specification</li> <li>3.42.2 The Structural Specification</li> <li>3.42.1 The Behavioural Specification</li> <li>3.42.1 The Behavioural Specification</li> <li>3.42.2 The Structural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.1 The Behavioural Specification</li> <li>3.43.1 The Behavioural Specification</li> <li>3.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> </ul>                                                                                                                                                        |        | 3.2 The Structural Specification     |

| <ul> <li>3.34.1 The Behavioural Specification</li> <li>3.34.2 The Structural Specification</li> <li>3.34.3 The Correctness Statement</li> <li>3.35.1 The Behavioural Specification</li> <li>3.35.2 The Structural Specification</li> <li>3.35.3 The Correctness Statement</li> <li>3.36.1 The Behavioural Specification</li> <li>3.36.2 The Structural Specification</li> <li>3.36.3 The Correctness Statement</li> <li>3.36.3 The Correctness Statement</li> <li>3.36.3 The Correctness Statement</li> <li>3.37.1 The Behavioural Specification</li> <li>3.37.2 The Structural Specification</li> <li>3.37.3 The Correctness Statement</li> <li>3.38.1 The Behavioural Specification</li> <li>3.38.2 The Structural Specification</li> <li>3.38.3 The Correctness Statement</li> <li>3.39.1 The Behavioural Specification</li> <li>3.39.2 The Structural Specification</li> <li>3.39.2 The Structural Specification</li> <li>3.39.3 The Correctness Statement</li> <li>3.39.3 The Correctness Statement</li> <li>3.40 PRIORITY_DECODE</li> <li>3.40.1 The Behavioural Specification</li> <li>3.40.2 The Structural Specification</li> <li>3.40.3 The Correctness Statement</li> <li>3.41.1 The Behavioural Specification</li> <li>3.41.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.3 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.4 The Behavioural Specification</li> <li>3.41.1 The Behavioural Specification</li> <li>3.41.2 The Structural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.41.1 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.41.1 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.3 The Correctness Statement</li> </ul>                                        |        | 3.3 The Correctness Statement        |

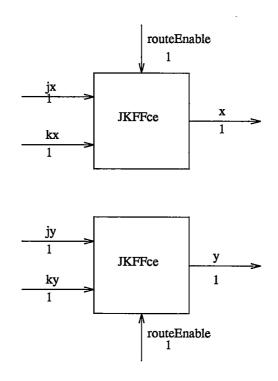

| <ul> <li>3.34.2 The Structural Specification</li> <li>3.34.3 The Correctness Statement</li> <li>3.35.4 RBITER.FF</li> <li>3.35.1 The Behavioural Specification</li> <li>3.35.2 The Structural Specification</li> <li>3.35.3 The Correctness Statement</li> <li>3.36.0 The Behavioural Specification</li> <li>3.36.2 The Structural Specification</li> <li>3.36.3 The Correctness Statement</li> <li>3.36.3 The Correctness Statement</li> <li>3.36.3 The Correctness Statement</li> <li>3.37.1 The Behavioural Specification</li> <li>3.37.2 The Structural Specification</li> <li>3.37.3 The Correctness Statement</li> <li>3.38.1 The Behavioural Specification</li> <li>3.38.2 The Structural Specification</li> <li>3.38.3 The Correctness Statement</li> <li>3.39.4 RBITER</li> <li>3.39.1 The Behavioural Specification</li> <li>3.39.2 The Structural Specification</li> <li>3.39.3 The Correctness Statement</li> <li>3.39.3 The Correctness Statement</li> <li>3.40.1 The Behavioural Specification</li> <li>3.40.2 The Structural Specification</li> <li>3.41.1 The Behavioural Specification</li> <li>3.41.2 The Structural Specification</li> <li>3.41.1 The Behavioural Specification</li> <li>3.41.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.4 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.4 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.4 The Behavioural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.4 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.4 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.4 The Switching Fabric—FABRIC4x4</li> <li>3.43.1 The Behavioural Specification</li> </ul>                                                              | 3.34   | X                                    |

| <ul> <li>3.34.3 The Correctness Statement</li> <li>3.35 ARBITER.FF</li> <li>3.35.1 The Behavioural Specification</li> <li>3.35.2 The Structural Specification</li> <li>3.35.3 The Correctness Statement</li> <li>3.36.1 The Behavioural Specification</li> <li>3.36.2 The Structural Specification</li> <li>3.36.3 The Correctness Statement</li> <li>3.36.3 The Correctness Statement</li> <li>3.36.3 The Correctness Statement</li> <li>3.37.1 The Behavioural Specification</li> <li>3.37.2 The Structural Specification</li> <li>3.37.3 The Correctness Statement</li> <li>3.38.1 The Behavioural Specification</li> <li>3.38.2 The Structural Specification</li> <li>3.38.3 The Correctness Statement</li> <li>3.38.3 The Correctness Statement</li> <li>3.38.3 The Correctness Statement</li> <li>3.39 ARBITER</li> <li>3.39.1 The Behavioural Specification</li> <li>3.39.2 The Structural Specification</li> <li>3.39.3 The Correctness Statement</li> <li>3.39.3 The Correctness Statement</li> <li>3.40.40 PRIORITY DECODE</li> <li>3.40.1 The Behavioural Specification</li> <li>3.40.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.41.1 The Behavioural Specification</li> <li>3.42.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.3 The Structural Specification</li> <li>3.42.3 The Structural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.3 The Correctness Statement</li> <li>3.42.3 The Structural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.43.1 The Behavioural Specification</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.3 The Correctness Statement</li> </ul>                                                      |        | .1 The Behavioural Specification     |

| <ul> <li>3.34.3 The Correctness Statement</li> <li>3.35 ARBITER.FF</li> <li>3.35.1 The Behavioural Specification</li> <li>3.35.2 The Structural Specification</li> <li>3.35.3 The Correctness Statement</li> <li>3.36.1 The Behavioural Specification</li> <li>3.36.2 The Structural Specification</li> <li>3.36.3 The Correctness Statement</li> <li>3.36.3 The Correctness Statement</li> <li>3.36.3 The Correctness Statement</li> <li>3.37.1 The Behavioural Specification</li> <li>3.37.2 The Structural Specification</li> <li>3.37.3 The Correctness Statement</li> <li>3.38.1 The Behavioural Specification</li> <li>3.38.2 The Structural Specification</li> <li>3.38.3 The Correctness Statement</li> <li>3.38.3 The Correctness Statement</li> <li>3.38.3 The Correctness Statement</li> <li>3.39 ARBITER</li> <li>3.39.1 The Behavioural Specification</li> <li>3.39.2 The Structural Specification</li> <li>3.39.3 The Correctness Statement</li> <li>3.39.3 The Correctness Statement</li> <li>3.40.1 The Behavioural Specification</li> <li>3.40.2 The Structural Specification</li> <li>3.40.3 The Correctness Statement</li> <li>3.41.1 The Behavioural Specification</li> <li>3.42.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.1 The Behavioural Specification</li> <li>3.42.2 The Structural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.1 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.1 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | .2 The Structural Specification      |

| 3.35.1       The Behavioural Specification         3.35.2       The Structural Specification         3.35.3       The Correctness Statement         3.36       OUTDIS         3.36.1       The Behavioural Specification         3.36.2       The Structural Specification         3.36.3       The Correctness Statement         3.37.1       The Behavioural Specification         3.37.2       The Structural Specification         3.37.3       The Correctness Statement         3.37.3       The Correctness Statement         3.37.3       The Correctness Statement         3.38.4       RBITER         3.38.1       The Behavioural Specification         3.38.2       The Structural Specification         3.38.3       The Correctness Statement         3.39       ARBITERS         3.39.1       The Behavioural Specification         3.39.2       The Structural Specification         3.39.3       The Correctness Statement         3.40       PRIORITY_DECODE         3.40.1       The Behavioural Specification         3.40.2       The Structural Specification         3.40.3       The Correctness Statement         3.41.1       The Behavioural Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | .3 The Correctness Statement         |

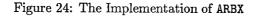

| <ul> <li>3.35.2 The Structural Specification</li> <li>3.35.3 The Correctness Statement</li> <li>3.36 OUTDIS</li> <li>3.36.1 The Behavioural Specification</li> <li>3.36.2 The Structural Specification</li> <li>3.36.3 The Correctness Statement</li> <li>3.37 ARBITER XY</li> <li>3.37.1 The Behavioural Specification</li> <li>3.37.2 The Structural Specification</li> <li>3.37.3 The Correctness Statement</li> <li>3.38.1 The Behavioural Specification</li> <li>3.38.2 The Structural Specification</li> <li>3.38.3 The Correctness Statement</li> <li>3.38.3 The Correctness Statement</li> <li>3.39 ARBITER</li> <li>3.39.1 The Behavioural Specification</li> <li>3.39.2 The Structural Specification</li> <li>3.39.3 The Correctness Statement</li> <li>3.39.3 The Correctness Statement</li> <li>3.40 PRIORITY DECODE</li> <li>3.40.1 The Behavioural Specification</li> <li>3.40.2 The Structural Specification</li> <li>3.40.3 The Correctness Statement</li> <li>3.41.1 The Behavioural Specification</li> <li>3.41.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.1 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.3 The Correctness Statement</li> <li>3.44.3 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.43.1 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.1 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> <li>3.43.2 The Structural Specification</li> </ul>                                                                                                                                                  | 3.35   | ITER_FF                              |

| <ul> <li>3.35.3 The Correctness Statement</li> <li>3.36 OUTDIS</li> <li>3.36.1 The Behavioural Specification</li> <li>3.36.2 The Structural Specification</li> <li>3.36.3 The Correctness Statement</li> <li>3.37 ARBITER XY</li> <li>3.37.1 The Behavioural Specification</li> <li>3.37.2 The Structural Specification</li> <li>3.37.3 The Correctness Statement</li> <li>3.38 ARBITER</li> <li>3.38.1 The Behavioural Specification</li> <li>3.38.2 The Structural Specification</li> <li>3.38.3 The Correctness Statement</li> <li>3.39.1 The Behavioural Specification</li> <li>3.39.2 The Structural Specification</li> <li>3.39.3 The Correctness Statement</li> <li>3.39.3 The Correctness Statement</li> <li>3.40 PRIORITY DECODE</li> <li>3.40.1 The Behavioural Specification</li> <li>3.40.2 The Structural Specification</li> <li>3.40.3 The Correctness Statement</li> <li>3.41.1 The Behavioural Specification</li> <li>3.41.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.1 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.41.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.42.3 The Correctness Statement</li> <li>3.43.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.43.1 The Behavioural Specification</li> </ul>                                            |        | 5.1 The Behavioural Specification    |

| <ul> <li>3.35.3 The Correctness Statement</li> <li>3.36 OUTDIS</li> <li>3.36.1 The Behavioural Specification</li> <li>3.36.2 The Structural Specification</li> <li>3.36.3 The Correctness Statement</li> <li>3.37 ARBITER XY</li> <li>3.37.1 The Behavioural Specification</li> <li>3.37.2 The Structural Specification</li> <li>3.37.3 The Correctness Statement</li> <li>3.38 ARBITER</li> <li>3.38.1 The Behavioural Specification</li> <li>3.38.2 The Structural Specification</li> <li>3.38.3 The Correctness Statement</li> <li>3.39.1 The Behavioural Specification</li> <li>3.39.2 The Structural Specification</li> <li>3.39.3 The Correctness Statement</li> <li>3.39.3 The Correctness Statement</li> <li>3.40 PRIORITY DECODE</li> <li>3.40.1 The Behavioural Specification</li> <li>3.40.2 The Structural Specification</li> <li>3.40.3 The Correctness Statement</li> <li>3.41.1 The Behavioural Specification</li> <li>3.41.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.1 The Behavioural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.41.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.43.42.3 The Correctness Statement</li> <li>3.43.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> <li>3.43.3 The Correctness Statement</li> <li>3.43.43.1 The Behavioural Specification</li> </ul>                                            |        | 5.2 The Structural Specification     |

| 3.36       OUTDIS         3.36.1       The Behavioural Specification         3.36.2       The Structural Specification         3.36.3       The Correctness Statement         3.37       ARBITER_XY         3.37.1       The Behavioural Specification         3.37.2       The Structural Specification         3.37.3       The Correctness Statement         3.37.3       The Correctness Statement         3.38.4       The Behavioural Specification         3.38.5       The Structural Specification         3.38.1       The Behavioural Specification         3.38.2       The Structural Specification         3.38.3       The Correctness Statement         3.39       ARBITERS         3.39.1       The Behavioural Specification         3.39.2       The Structural Specification         3.39.3       The Correctness Statement         3.40       PRIORITY DECODE         3.40.1       The Behavioural Specification         3.40.2       The Structural Specification         3.40.3       The Correctness Statement         3.41.1       The Behavioural Specification         3.41.2       The Structural Specification         3.42.1       The Behavioural Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | 3.3 The Correctness Statement        |

| 3.36.2 The Structural Specification         3.36.3 The Correctness Statement         3.37 ARBITER_XY         3.37.1 The Behavioural Specification         3.37.2 The Structural Specification         3.37.3 The Correctness Statement         3.38.1 The Behavioural Specification         3.38.2 The Structural Specification         3.38.3 The Correctness Statement         3.38.3 The Correctness Statement         3.39.4 RBITER         3.39.3 The Correctness Statement         3.39.3 The Correctness Statement         3.39.3 The Correctness Statement         3.39.3 The Correctness Statement         3.40.1 The Behavioural Specification         3.40.2 The Structural Specification         3.40.3 The Correctness Statement         3.40.1 The Behavioural Specification         3.40.2 The Structural Specification         3.40.3 The Correctness Statement         3.41.4 RBITRATION         3.41.1 The Behavioural Specification         3.41.2 The Structural Specification         3.42.1 The Behavioural Specification         3.42.2 The Structural Specification         3.42.3 The Correctness Statement         3.43 The Switching Fabric—FABRIC4x4         3.43.1 The Behavioural Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |                                      |

| 3.36.2 The Structural Specification         3.36.3 The Correctness Statement         3.37 ARBITER_XY         3.37.1 The Behavioural Specification         3.37.2 The Structural Specification         3.37.3 The Correctness Statement         3.38.1 The Behavioural Specification         3.38.2 The Structural Specification         3.38.3 The Correctness Statement         3.38.3 The Correctness Statement         3.39.4 RBITER         3.39.3 The Correctness Statement         3.39.3 The Correctness Statement         3.39.3 The Correctness Statement         3.39.3 The Correctness Statement         3.40.1 The Behavioural Specification         3.40.2 The Structural Specification         3.40.3 The Correctness Statement         3.40.1 The Behavioural Specification         3.40.2 The Structural Specification         3.40.3 The Correctness Statement         3.41.4 RBITRATION         3.41.1 The Behavioural Specification         3.41.2 The Structural Specification         3.42.1 The Behavioural Specification         3.42.2 The Structural Specification         3.42.3 The Correctness Statement         3.43 The Switching Fabric—FABRIC4x4         3.43.1 The Behavioural Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | 3.1 The Behavioural Specification    |

| 3.36.3 The Correctness Statement         3.37 ARBITER_XY         3.37.1 The Behavioural Specification         3.37.2 The Structural Specification         3.37.3 The Correctness Statement         3.38         ARBITER         3.38.1 The Behavioural Specification         3.38.2 The Structural Specification         3.38.3 The Correctness Statement         3.38.3 The Correctness Statement         3.39.4 RBITERS         3.39.1 The Behavioural Specification         3.39.2 The Structural Specification         3.39.3 The Correctness Statement         3.39.3 The Correctness Statement         3.40.1 The Behavioural Specification         3.40.2 The Structural Specification         3.40.3 The Correctness Statement         3.40.1 The Behavioural Specification         3.40.2 The Structural Specification         3.41.3 The Correctness Statement         3.41.4 RBITRATION         3.41.1 The Behavioural Specification         3.41.2 The Structural Specification         3.42.1 The Behavioural Specification         3.42.2 The Structural Specification         3.42.3 The Correctness Statement         3.42.1 The Behavioural Specification         3.42.2 The Structural Specification         3.42.3 The Correctness Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | .2 The Structural Specification      |

| 3.37       ARBITER_XY         3.37.1       The Behavioural Specification         3.37.2       The Structural Specification         3.37.3       The Correctness Statement         3.38.1       The Behavioural Specification         3.38.2       The Structural Specification         3.38.3       The Correctness Statement         3.38.4       The Behavioural Specification         3.38.5       The Correctness Statement         3.39       ARBITERS         3.39.1       The Behavioural Specification         3.39.2       The Structural Specification         3.39.3       The Correctness Statement         3.40       PRIORITY_DECODE         3.40.1       The Behavioural Specification         3.40.2       The Structural Specification         3.40.3       The Correctness Statement         3.40.4       The Structural Specification         3.41.4       The Structural Specification         3.41.3       The Correctness Statement         3.42.1       The Behavioural Specification         3.42.2       The Structural Specification         3.42.3       The Correctness Statement         3.42.1       The Behavioural Specification         3.42.2       The Structural Specifica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | 3.3 The Correctness Statement        |

| 3.37.2 The Structural Specification .         3.37.3 The Correctness Statement .         3.38 ARBITER .         3.38.1 The Behavioural Specification .         3.38.2 The Structural Specification .         3.38.3 The Correctness Statement .         3.39 ARBITERS .         3.39.1 The Behavioural Specification .         3.39.2 The Structural Specification .         3.39.3 The Correctness Statement .         3.39.3 The Correctness Statement .         3.40 PRIORITY_DECODE .         3.40.1 The Behavioural Specification .         3.40.2 The Structural Specification .         3.40.3 The Correctness Statement .         3.41.4 RBITRATION .         3.41.1 The Behavioural Specification .         3.41.2 The Structural Specification .         3.41.3 The Correctness Statement .         3.42.4 FAB484 .         3.42.1 The Behavioural Specification .         3.42.2 The Structural Specification .         3.42.3 The Correctness Statement .         3.43.4 The Behavioural Specification .         3.42.3 The Correctness Statement .         3.42.4 FAB484 .         3.42.3 The Correctness Statement .         3.43.1 The Behavioural Specification .         3.43.2 The Switching Fabric—FABRIC4x4 .         3.43.1 The Behavioural Specification .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |                                      |

| 3.37.3 The Correctness Statement .         3.38 ARBITER .         3.38.1 The Behavioural Specification .         3.38.2 The Structural Specification .         3.38.3 The Correctness Statement .         3.39 ARBITERS .         3.39.1 The Behavioural Specification .         3.39.2 The Structural Specification .         3.39.3 The Correctness Statement .         3.39.3 The Correctness Statement .         3.40 PRIORITY_DECODE .         3.40.1 The Behavioural Specification .         3.40.2 The Structural Specification .         3.40.3 The Correctness Statement .         3.41.4 The Behavioural Specification .         3.41.1 The Behavioural Specification .         3.41.2 The Structural Specification .         3.41.3 The Correctness Statement .         3.42.1 The Behavioural Specification .         3.42.2 The Structural Specification .         3.42.3 The Correctness Statement .         3.42.3 The Correctness Statement .         3.42.3 The Correctness Statement .         3.43.1 The Behavioural Specification .         3.43.2 The Switching Fabric—FABRIC4x4 .         3.43.1 The Behavioural Specification .         3.43.2 The Structural Specification .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | 79 7.1 The Behavioural Specification |

| 3.37.3 The Correctness Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 7.2 The Structural Specification     |

| 3.38 ARBITER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 7.3 The Correctness Statement        |

| 3.38.1 The Behavioural Specification         3.38.2 The Structural Specification         3.38.3 The Correctness Statement         3.39 ARBITERS         3.39.1 The Behavioural Specification         3.39.2 The Structural Specification         3.39.3 The Correctness Statement         3.39.3 The Correctness Statement         3.40 PRIORITY_DECODE         3.40.1 The Behavioural Specification         3.40.2 The Structural Specification         3.40.3 The Correctness Statement         3.40.3 The Correctness Statement         3.41.1 The Behavioural Specification         3.41.2 The Structural Specification         3.41.3 The Correctness Statement         3.42.1 The Behavioural Specification         3.42.2 The Structural Specification         3.42.3 The Correctness Statement         3.42.4 The Behavioural Specification         3.42.5 The Structural Specification         3.42.6 The Structural Specification         3.42.7 The Structural Specification         3.42.8 The Correctness Statement         3.43 The Switching Fabric—FABRIC4x4         3.43.1 The Behavioural Specification         3.43.2 The Structural Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                                      |

| 3.38.2 The Structural Specification         3.38.3 The Correctness Statement         3.39 ARBITERS         3.39.1 The Behavioural Specification         3.39.2 The Structural Specification         3.39.3 The Correctness Statement         3.39.3 The Correctness Statement         3.40         PRIORITY_DECODE         3.40.1 The Behavioural Specification         3.40.2 The Structural Specification         3.40.3 The Correctness Statement         3.40.3 The Correctness Statement         3.41.1 The Behavioural Specification         3.41.2 The Structural Specification         3.41.3 The Correctness Statement         3.42.4 FAB4B4         3.42.5 The Structural Specification         3.42.6 The Structural Specification         3.42.7 The Structural Specification         3.42.8 The Correctness Statement         3.42.9 The Structural Specification         3.42.1 The Behavioural Specification         3.42.3 The Correctness Statement         3.43 The Switching Fabric—FABRIC4x4         3.43.1 The Behavioural Specification         3.43.2 The Structural Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | 3.1 The Behavioural Specification    |

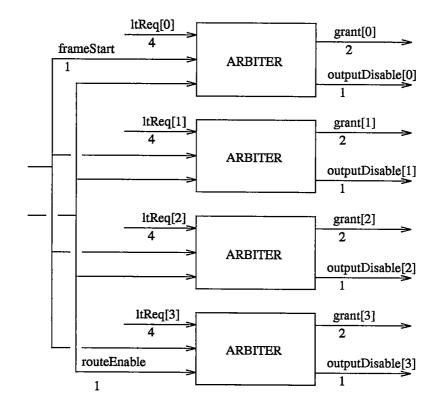

| <ul> <li>3.39 ARBITERS</li> <li>3.39.1 The Behavioural Specification</li> <li>3.39.2 The Structural Specification</li> <li>3.39.3 The Correctness Statement</li> <li>3.40 PRIORITY_DECODE</li> <li>3.40.1 The Behavioural Specification</li> <li>3.40.2 The Structural Specification</li> <li>3.40.3 The Correctness Statement</li> <li>3.41.3 The Correctness Statement</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.1 The Behavioural Specification</li> <li>3.42.2 The Structural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43 The Switching Fabric—FABRIC4x4</li> <li>3.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                      |

| <ul> <li>3.39 ARBITERS</li> <li>3.39.1 The Behavioural Specification</li> <li>3.39.2 The Structural Specification</li> <li>3.39.3 The Correctness Statement</li> <li>3.40 PRIORITY_DECODE</li> <li>3.40.1 The Behavioural Specification</li> <li>3.40.2 The Structural Specification</li> <li>3.40.3 The Correctness Statement</li> <li>3.41.3 The Correctness Statement</li> <li>3.41.3 The Correctness Statement</li> <li>3.42.1 The Behavioural Specification</li> <li>3.42.2 The Structural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.43 The Switching Fabric—FABRIC4x4</li> <li>3.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |                                      |

| <ul> <li>3.39.2 The Structural Specification</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |                                      |

| <ul> <li>3.39.2 The Structural Specification</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        | 0.1 The Behavioural Specification    |

| <ul> <li>3.40 PRIORITY_DECODE</li> <li>3.40.1 The Behavioural Specification</li> <li>3.40.2 The Structural Specification</li> <li>3.40.3 The Correctness Statement</li> <li>3.41 ARBITRATION</li> <li>3.41.1 The Behavioural Specification</li> <li>3.41.2 The Structural Specification</li> <li>3.41.3 The Correctness Statement</li> <li>3.42 FAB4B4</li> <li>3.42.1 The Behavioural Specification</li> <li>3.42.2 The Structural Specification</li> <li>3.42.3 The Correctness Statement</li> <li>3.42.3 The Correctness Statement</li> <li>3.43 The Switching Fabric—FABRIC4x4</li> <li>3.43.1 The Behavioural Specification</li> <li>3.43.2 The Structural Specification</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |                                      |

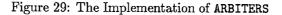

| 3.40.1 The Behavioural Specification .       .         3.40.2 The Structural Specification .       .         3.40.3 The Correctness Statement .       .         3.41 ARBITRATION .       .         3.41.1 The Behavioural Specification .       .         3.41.2 The Structural Specification .       .         3.41.3 The Correctness Statement .       .         3.42 FAB4B4 .       .         3.42.1 The Behavioural Specification .       .         3.42.2 The Structural Specification .       .         3.42.3 The Correctness Statement .       .         3.42.3 The Correctness Statement .       .         3.42.3 The Structural Specification .       .         3.43 The Switching Fabric—FABRIC4x4 .       .         3.43.1 The Behavioural Specification .       .         3.43.2 The Structural Specification .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | .3 The Correctness Statement         |