Technical Report

Number 322

**Computer Laboratory**

# Supporting distributed realtime computing

Guangxing Li

December 1993

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

#### © 1993 Guangxing Li

This technical report is based on a dissertation submitted August 1993 by the author for the degree of Doctor of Philosophy to the University of Cambridge, King's College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Contents

|   | $\mathbf{List}$       | of Tables in                                                                                                                                                                   | ĸ  |

|---|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | $\operatorname{List}$ | of Figures                                                                                                                                                                     | x  |

|   | Glo                   | sary of Terms xii                                                                                                                                                              | ii |

| 1 | Intr                  | duction                                                                                                                                                                        | 1  |

|   | 1.1                   | Problem                                                                                                                                                                        | 1  |

|   | 1.2                   | Scope                                                                                                                                                                          | 3  |

|   | 1.3                   | The Proposed System                                                                                                                                                            | 3  |

|   | 1.4                   | Outline of the Dissertation                                                                                                                                                    | 4  |

| 2 | Bac                   | ground and Issues                                                                                                                                                              | 5  |

|   | 2.1                   | Microkernel Architecture                                                                                                                                                       | 5  |

|   |                       | 2.1.1 Microkernel and Realtime Systems                                                                                                                                         | 5  |

|   | 2.2                   | Current Microkernels                                                                                                                                                           | 6  |

|   |                       | 2.2.1 Chorus                                                                                                                                                                   | 6  |

|   |                       | 2.2.2 Mach                                                                                                                                                                     | 7  |

|   |                       | 2.2.3 QNX                                                                                                                                                                      | 8  |

|   | 2.3                   | Distributed System Environment                                                                                                                                                 | 8  |

|   |                       | 2.3.1 Realtime Distributed System Environment                                                                                                                                  | 9  |

|   | 2.4                   | Example Distributed System Environments $\ldots \ldots \ldots$ | 0  |

|   |                       | 2.4.1 COOL $\ldots$ $\ldots$ $\ldots$ $1$                                                                                                                                      | 0  |

|   |                       | 2.4.2 MachObjects                                                                                                                                                              | 1  |

|   |                       | 2.4.3 DCE                                                                                                                                                                      | 1  |

|   |                       | 2.4.4 Open Distributed Processing                                                                                                                                              | 2  |

|   | 2.5  | Realtime Scheduling                                                      | 12         |

|---|------|--------------------------------------------------------------------------|------------|

|   |      | 2.5.1 Scheduling Task Synchronization                                    | 14         |

|   | 2.6  | Realtime Communication                                                   | 15         |

|   | 2.7  | Summary of Background                                                    | 16         |

|   | 2.8  | Addressed Issues                                                         | 16         |

|   |      | 2.8.1 Realtime Programming Model                                         | 17         |

|   |      | 2.8.2 Timed Remote Procedure Calls                                       | 17         |

|   |      | 2.8.3 Description of Temporal Behaviours                                 | 18         |

|   |      | 2.8.4 Empirical Validation                                               | 18         |

|   | 2.9  | Summary                                                                  | 18         |

| 3 | The  | RIDE Realtime Programming Model                                          | 19         |

|   | 3.1  | Distributed Object Execution                                             | 19         |

|   | 3.2  | ANSA Object Execution                                                    | 20         |

|   |      | 3.2.1 ANSA Computation Model                                             | 20         |

|   |      | 3.2.2 ANSA Engineering Model                                             | <b>21</b>  |

|   |      | 3.2.3 ANSA Object Execution Model                                        | 23         |

|   |      | 3.2.4 ANSA Object Execution Model Deficiencies for Realtime Applications | 23         |

|   | 3.3  | RIDE Objects                                                             | 24         |

|   | 3.4  | Object Invocation                                                        | 26         |

|   | 3.5  | Scheduling                                                               | 26         |

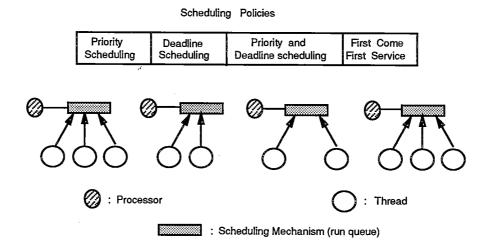

|   | 3.6  | Priority Scheduling Models                                               | 28         |

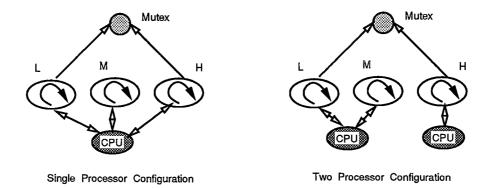

|   |      | 3.6.1 Priority Management and Priority Inheritance                       | 29         |

|   |      | 3.6.2 Resource Allocation and Task Preemption                            | 29         |

|   |      | 3.6.3 Dealing with Priority Inversion                                    | 30         |

|   | 3.7  | Deadline Scheduling Models                                               | <b>3</b> 1 |

|   |      | 3.7.1 Guaranteeing Deadlines                                             | 32         |

|   | 3.8  | Other Scheduling Paradigms                                               | 34         |

|   |      | 3.8.1 Mixed Model Scheduling                                             | <b>3</b> 4 |

|   | 3.9  | The Invocation and Entry Interface                                       | 34         |

|   | 3.10 | Application Controlled Rendezvous                                        | 36         |

|   | 3.11 | End-to-End Scheduling                                                    | 38         |

vi

|   | 3.12           | Summary                                                                                                                                   | 39 |

|---|----------------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4 | $\mathbf{The}$ | e RIDE Communication System 4                                                                                                             | ŧO |

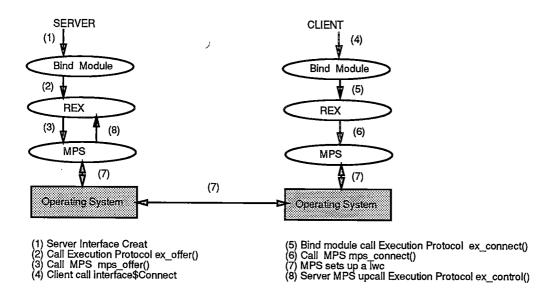

|   | 4.1            | The ANSA Communication System                                                                                                             | 40 |

|   |                | 4.1.1 The Remote Execution Protocol                                                                                                       | 42 |

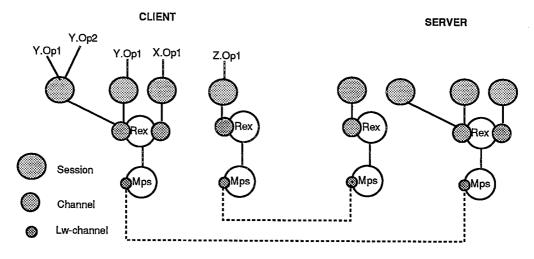

|   | 4.2            | Towards a Parallel Protocol Stack                                                                                                         | 43 |

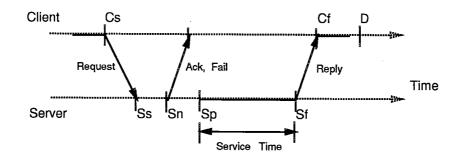

|   | 4.3            | Towards a Timed RPC Protocol                                                                                                              | 46 |

|   |                | 4.3.1 Discussion of Problem                                                                                                               | 47 |

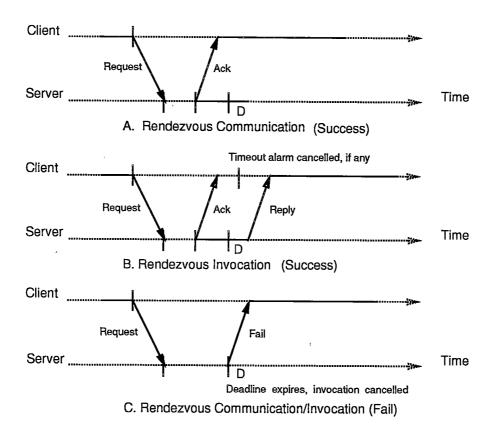

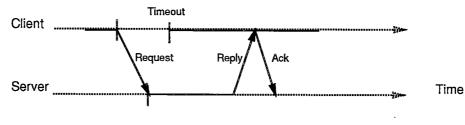

|   |                | 4.3.2 The Protocol                                                                                                                        | 48 |

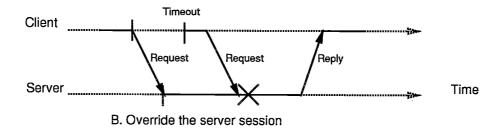

|   |                | 4.3.3 Server Deadline Expiry                                                                                                              | 49 |

|   | 4.4            | Towards a Decomposable RPC Protocol                                                                                                       | 50 |

|   | 4.5            | Summary                                                                                                                                   | 52 |

| 5 | Ten            | poral Synchronization 5                                                                                                                   | 53 |

|   | 5.1            | Timed Automata                                                                                                                            | 54 |

|   | 5.2            | Description of Temporal Constraints                                                                                                       | 55 |

|   |                | 5.2.1 Instantaneous Timing Constraints                                                                                                    | 55 |

|   |                | 5.2.2 Interval Timing Constraints                                                                                                         | 57 |

|   | 5.3            | Timed Automata Synchronization Mechanism                                                                                                  | 59 |

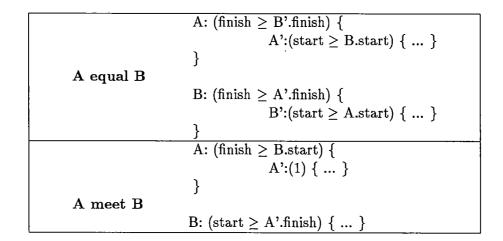

|   |                | 5.3.1 Syntax and Semantics                                                                                                                | 60 |

|   |                | 5.3.2 Embedded Code                                                                                                                       | 64 |

|   | 5.4            | Virtual Time $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                 | 64 |

|   | 5.5            | Implementation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                           | 36 |

|   | 5.6            | Summary                                                                                                                                   | 66 |

| 6 | A P            | Prototype Implementation 6                                                                                                                | 88 |

|   | 6.1            | Systems Environment                                                                                                                       | 68 |

|   | 6.2            | WANDA Extensions                                                                                                                          | 69 |

|   |                | 6.2.1 Scheduling $\ldots \ldots \ldots$ | 69 |

|   |                | 6.2.2 Thread Synchronisation and Priority Inheritance                                                                                     | 70 |

|   |                | 6.2.3 Monitoring Scheduling                                                                                                               | 72 |

|   | 6.3            | Implementation of RIDE Tasking                                                                                                            | 72 |

|   |                | 6.3.1 Tasks and Threads in the ANSA Testbench                                                                                             | 72 |

vii

|   |      | 6.3.2 Preemptive Tasking Implementation               | 1        |

|---|------|-------------------------------------------------------|----------|

|   |      | 6.3.3 Thread Scheduling 75                            | 5        |

|   | 6.4  | Implementation of the RIDE Communication System       | 3        |

|   |      | 6.4.1 Parallel Protocol Stacks                        | 3        |

|   |      | 6.4.2 Timed RPC Protocol                              | 7        |

|   |      | 6.4.3 Decomposable RPC Protocol                       | 9        |

|   | 6.5  | Implementation of the Timed Automata                  | <b>)</b> |

|   | 6.6  | Summary                                               | )        |

| 7 | Per  | formance Measurement and Evaluation 81                | L        |

|   | 7.1  | WANDA Basic Performance                               | 1        |

|   | 7.2  | Controlled Priority Inversion                         | 2        |

|   | 7.3  | Hartstone Benchmark 84                                | 1        |

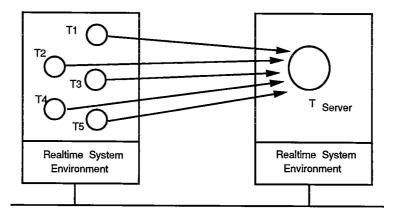

|   | 7.4  | Distributed Hartstone Benchmark 88                    | 3        |

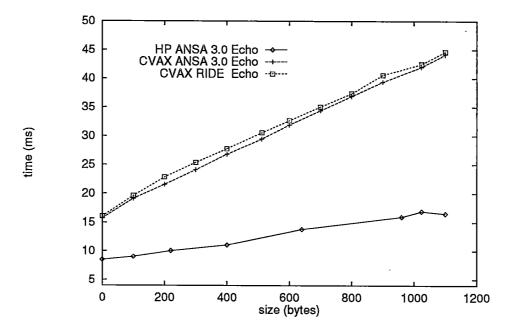

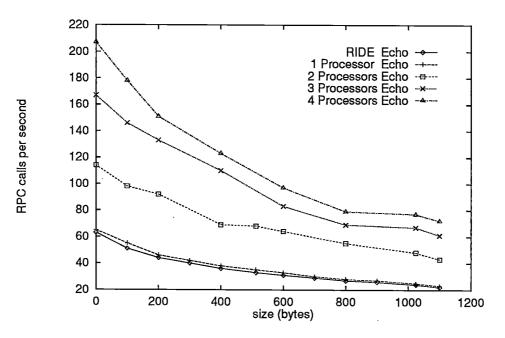

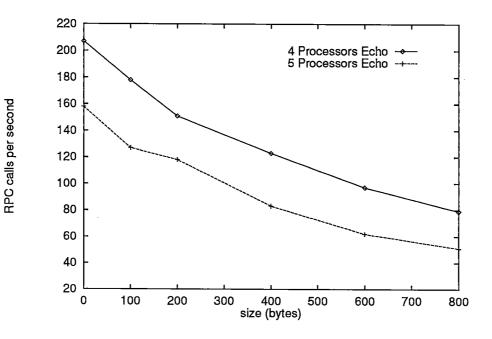

|   | 7.5  | Parallel Protocol Stack and Multiprocessor Speedup 92 | 2        |

|   |      | 7.5.1 Basic Performance                               | 3        |

|   |      | 7.5.2 Multiprocessor Speedup 94                       | 1        |

|   | 7.6  | Summary                                               | 3        |

| 8 | Rela | ated Research 97                                      | 7        |

|   | 8.1  | Ada 9X                                                | 7        |

|   |      | 8.1.1 Realtime in Ada 9X 97                           | 7        |

|   |      | 8.1.2 Distribution in Ada 9X 98                       | 3        |

|   |      | 8.1.3 Ada 9X and RIDE                                 | )        |

|   | 8.2  | Alpha                                                 | )        |

|   | 8.3  | ART                                                   | )        |

|   |      | 8.3.1 ART and RIDE                                    | )        |

|   | 8.4  | CHAOS                                                 | )        |

|   | 8.5  | ESTEREL                                               | l        |

|   | 8.6  | MARUTI                                                | 2        |

|   | 8.7  | MARS                                                  | 2        |

|   | 8.8  | IMAC                                                  | 2        |

|   | 8.9  | Summary                                               | 3        |

.

.

| 9 | Con | clusion       |   |   |     |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |     | 10 | 4 |

|---|-----|---------------|---|---|-----|---|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|-----|----|---|

|   | 9.1 | Contributions | • |   |     | • | • | • | • | • | • | •   |   | • |   | • | • | 0 | • | • | • | • |     |   | • |   | • | ۰ | • | • |   |     | 10 | 4 |

|   | 9.2 | Future Work   | • | • | • • | • | • | • | • | ٠ | • | • • | • |   | • | • | • | • | • | • | • | • | • • | • | • | • | ۰ | ۰ | • | • | • | ••• | 10 | 5 |

|   | Bib | liography     |   |   |     |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |     | 10 | 6 |

# List of Tables

| 2.1 | A Set of Tasks with 82% Utilization     | 13 |

|-----|-----------------------------------------|----|

| 4.1 | ANSA MPS vs RIDE MPS                    | 44 |

| 4.2 | ANSA REX vs RIDE REX                    | 44 |

| 6.1 | Timed Remote Execution Protocol Packets | 78 |

| 7.1 | The Basic WANDA Performance             |    |

| 7.2 | DSHcl Series Task Set                   | 89 |

| 7.3 | DSHpq Series Task Set                   | 89 |

| 7.4 | DSNpp Series Task Set                   | 90 |

| 7.5 | DSHcb Series Task Set                   | 91 |

| 7.6 | RIDE vs ARTS Performance                | 91 |

| 7.7 | Multiprocessor Speedup of RPC           | 96 |

# List of Figures

| 2.1  | The COOL Architecture                              | 10 |

|------|----------------------------------------------------|----|

| 2.2  | The Distributed Computing Environment Architecture | 11 |

| 2.3  | Priority Inversion                                 | 14 |

| 3.1  | Engineering Model                                  | 22 |

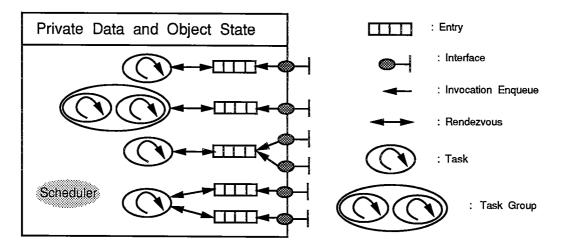

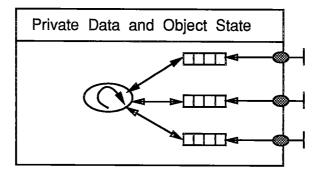

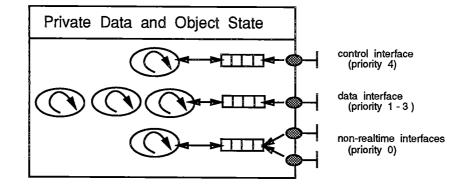

| 3.2  | RIDE Object Illustration                           | 24 |

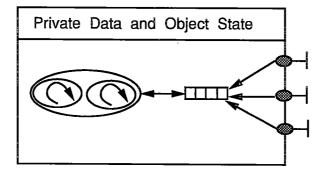

| 3.3  | Shared Single Entry (ANSA) Configuration           | 25 |

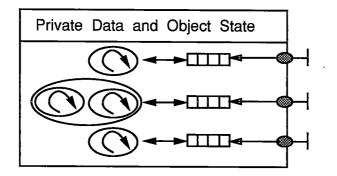

| 3.4  | Multiple Single Entries Configuration              | 25 |

| 3.5  | Single Task Multiple Single Entry                  | 26 |

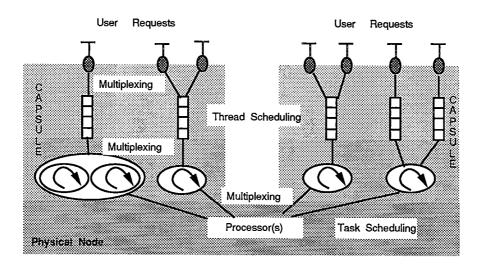

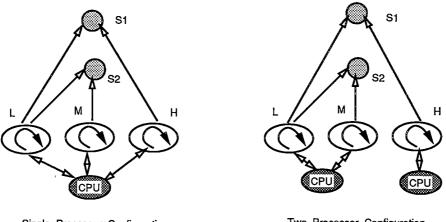

| 3.6  | Threads, Tasks and Processor(s) Multiplexing       | 27 |

| 3.7  | Layered Management of Priorities                   | 30 |

| 3.8  | Priority Inversion in RIDE Objects                 | 31 |

| 3.9  | A Deadline Guarantee Algorithm                     | 33 |

| 3.10 | IDL and PREPC Example                              | 35 |

| 3.11 | A Bounded Buffer                                   | 37 |

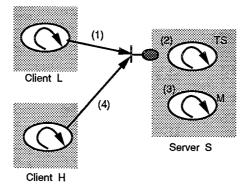

| 3.12 | End-to-End Scheduling                              | 39 |

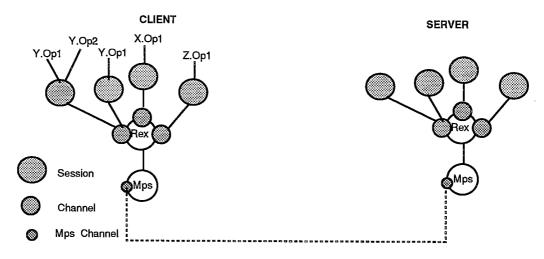

| 4.1  | ANSA Communication System                          | 41 |

| 4.2  | Multiplexing in the Testbench                      | 42 |

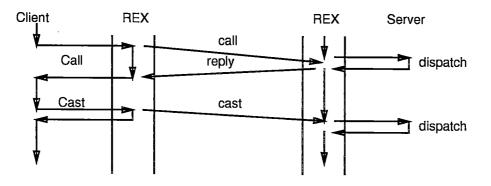

| 4.3  | A Simple Call and Cast                             | 43 |

| 4.4  | Private Lightweight Channel Connection             | 45 |

| 4.5  | Parallel Protocol Stack                            | 46 |

| 4.6  | Timed RPC Communication Sequence                   | 47 |

| 4.7  | Rendezvous Communication/Invocation Interaction    | 49 |

| 4.8  | Server Thread Deadline Expire                      | 50 |

| 4.9  | REX Functions Layers                               | 51 |

| 4.10 | A Decomposable RPC Protocol                      | 51  |

|------|--------------------------------------------------|-----|

| 4.11 | RIDE Communication System                        | 51  |

| 5.1  | Description of a Maximum Timing Constraint       | 56  |

| 5.2  | Description of a Minimum Timing Constraint       | 57  |

| 5.3  | Combining Maximum and Minimum Timing Constraints | 57  |

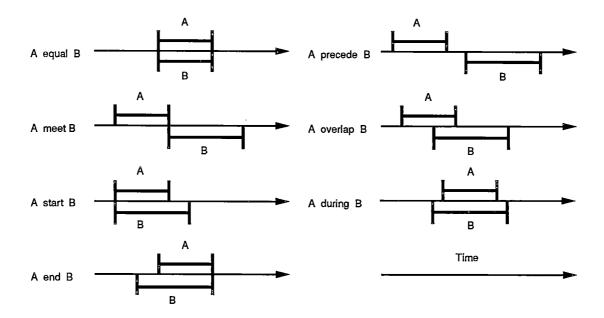

| 5.4  | Interval Binary Relations                        | 58  |

| 5.5  | FLEX Constraint Blocks                           | 58  |

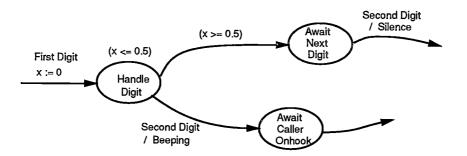

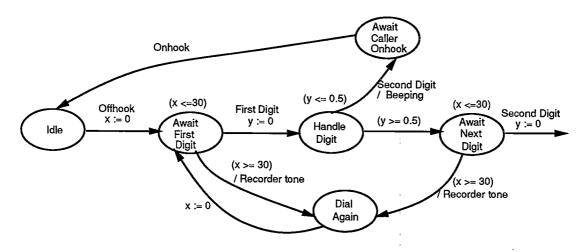

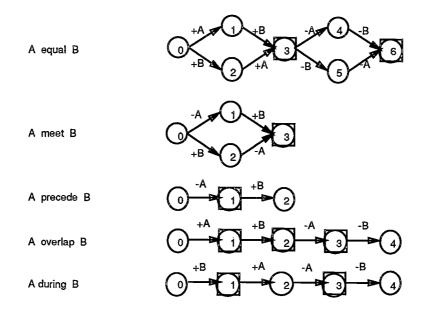

| 5.6  | Transition Graphs for Interval Binary Relations  | 59  |

| 5.7  | Timed Automata Specification Language Syntax     | 61  |

| 5.8  | Radar States                                     | 62  |

| 5.9  | The Specification of a Timed Automaton           | 63  |

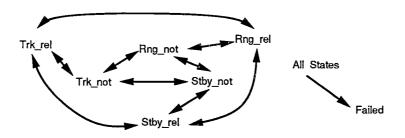

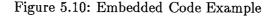

| 5.10 | Embedded Code Example                            | 65  |

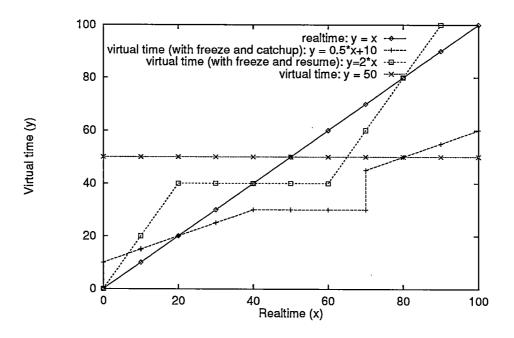

| 5.11 | Virtual Time vs. Realtime                        | 66  |

| 6.1  | The New Kernel Scheduler                         | 70  |

| 6.2  | Fine Grain Synchronization and Deadlock          | 74  |

| 6.3  | Deadlock Resolution                              | 75  |

| 6.4  | Session Timeout Recovery Illustration            | .78 |

| 7.1  | Controlled Priority Inversion                    | 82  |

| 7.2  | Strictly Controlled Priority Inversion           | 83  |

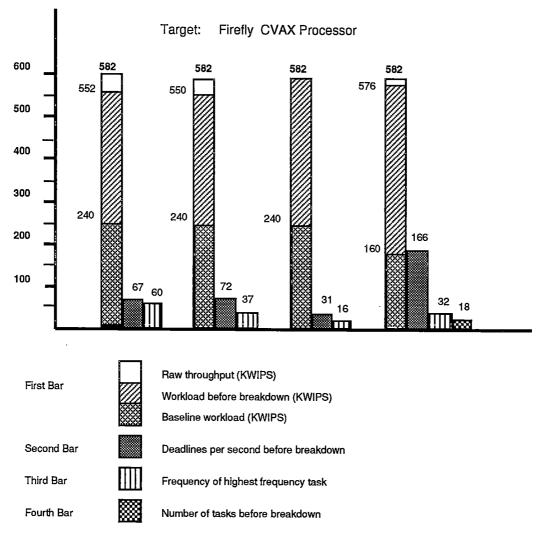

| 7.3  | Summary Results: Firefly WANDA                   | 85  |

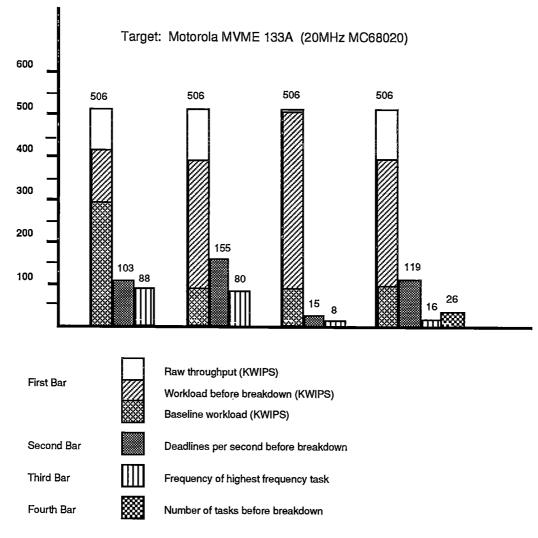

| 7.4  | Summary Results: Verdix VADS                     | 86  |

| 7.5  | Hartstone Benchmark                              | 87  |

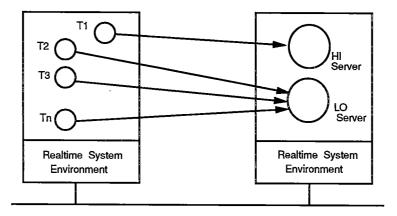

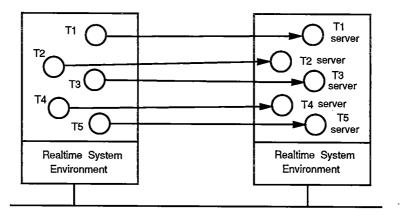

| 7.6  | Five Clients with Single Server                  | 88  |

| 7.7  | N Clients with Multiple Servers                  | 90  |

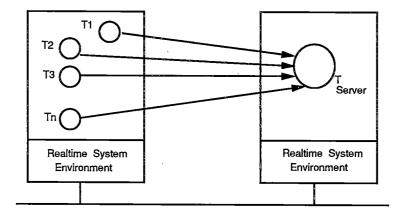

| 7.8  | N Clients with Single Server                     | 92  |

| 7.9  | Basic RPC performance                            | 93  |

| 7.10 | Experiment Setup of Multiprocessor Speedup       | 94  |

| 7.11 | Multiprocessor Speedup                           | 95  |

| 7.12 | Adverse Effect of the Fifth Processor            | 95  |

.

# Glossary

ANSA Advanced Networked Systems Architecture

${\bf ACM}$  ANSA Computational Model

AEM ANSA Engineering Model

AOEM ANSA Object Execution Model

ATM Asynchronous Transfer Mode

BNF Backus-Naur Form

DCE Distributed Computing Environment

DHB Distributed Hartstone Benchmark

**DSE** Distributed System Environment

FCFS First Come First Service

**GEX** Group EXecution Protocol

HB Hartstone Benchmark

HDB Hartstone Distributed Benchmark

**IDL** Interface Definition Language

**IPC** Inter Process Communication

ISO International Standards Organisation

KWIPS Kilo-Whetstone Instructions Per Second

LAN Local Area Network

LANCE The Am7990 Local Area Network Controller for Ethernet

LWC Light-Weight Channel

MIPS Millions of Instructions Per Second

MPS Message Passing Service

MSNL Multi-Service Network Level

GLOSSARY

$\mathbf{ODP} \ \ \mathbf{Open} \ \ \mathbf{Distributed} \ \mathbf{Processing}$

**OSI** Open Systems Interconnection

**OSF** Open Software Foundation

PCP Priority Ceiling Protocol

**PIP** Priority Inheritance Protocol

**POSIX** (IEEE Standard) Portable Operating System Interface for Computer Environments

**PREPC** PREProcessor of C

QoS Quality of Service

**REX** Remote EXecution Protocol

**RPC** Remote Procedure Call

TA Timed Automata

**TCP** Transmission Control Protocol

TREX Timed Remote EXecution Protocol

TRPC Timed Remote Procedure Call

**UI** Unix International

# Chapter 1

# Introduction

This dissertation is concerned with the design and construction of a distributed system environment for supporting realtime applications. The perspective and scope of this research is the entire system environment, rather than being focussed on the more narrow subsystems or algorithms. The contributions range from high-level programming abstractions down to an operating system kernel interface through the detailed engineering tradeoffs required to create, implement, and integrate the mechanisms within the environment.

#### 1.1 Problem

Computers have been used for realtime systems for almost 50 years [90]. However, it is only recently that computer research institutions are becoming interested in realtime computing, realizing the significance of realtime systems and their increasing practical importance. Realtime systems engineering still faces many challenges [94]: current systems concepts and functions are unfavourable for the development of a general and consistent framework for realtime systems engineering. The realtime problem domain has also been further complicated by the rapid spread of distributed computing.

There are specific functional, economical and technology reasons for the use of distributed computing in realtime contexts. An application may be inherently spatially dispersed, and its realtime performance requirements do not permit the latency of the requisite communications which would be needed between these locations and a centralized computing facility. Other functional reasons for distribution are reliability and availability. Enhanced reliability and continued availability are better achieved by distribution — replication and partition of both data and function — rather than by centralization. Economically, the rapid increases in microprocessor performance and decreases in cost make it more costeffective to have many small computers working together in place of one large computer of equivalent power. On the technology aspect, there is an increasing interest to equip modern workstations with more realtime devices. For example, the Cambridge Desk Area Network [47] uses a switching fabric to connect multimedia devices (video cameras and audio microphones) within a workstation environment. Such systems exhibit physically distributed realtime computing properties as well. It also raises the potential for distributed realtime services, such as multimedia conferencing. Consider a distributed computing environment, in which autonomous machines communicate via various shared communication media. Processing requests can originate at any node in this network. The actual processing of the requests makes use of the resources within this environment. Such distributed realtime processing requests place a set of unique requirements including *predictability*, user control, timeliness, mission orientation, and performance. These features do not exist in today's computing environments, and must be addressed by future systems research.

- **Predictability** is the tendency of a system to perform a set of operations in a welldefined, or *determined* fashion, so that each of these operations' timing requirements are satisfied. A fully predictable system performs operations in the same amount of time, every time, independent of surrounding conditions. Conversely, a fully nondeterministic system is one in which operation times have no guaranteed upper bound. Predictability applies to every level of the components of a realtime distributed system environment. Such an environment must provide a certain degree of predictability, even though it is not always possible to be fully predictable, to support any useful realtime performance guarantee.

- User Control means a user has ultimate control of the behaviour of a system. This feature comes from the fact that many realtime applications are embedded systems (which are often static systems, and therefore it is possible to control the systems' behaviour) and that realtime applications have immense behaviour diversity (therefore it is impossible to use one fixed system behaviour for many realtime applications). The simplest method of user control on system behaviour is probably the choice of priorities for realtime tasks. By allowing a user to indicate the relative priorities of tasks, the user can affect throughput and/or responsiveness goals for the system on a much finer granularity than by a "do the best you can overall" approach. Users may also be allowed to select the scheduling policy, preallocation of system and application resources to critical services and so on.

- Timeliness Realtime applications are different from the no-realtime paradigm of computation in that they impose strict requirements on the timing behaviour of the system. The correctness of a realtime system depends not only on the functional behaviour of the system, but also depends on the temporal behaviour as well. A realtime system environment must provide mechanisms which take these time related issues into account and must help application programs to meet these time constraints. A simple example is to allow an application to associate deadlines with realtime activities, and the system employs a deadline based scheduling policy to help the deadlines be met or to identify and cancel obsolete operations. Other required functions include the description and enforcement of temporal relations among related computational activities.

- Mission Orientation means that an entire distributed computer system is dedicated towards accomplishing a specific purpose through the cooperative execution of one or more application programs distributed across its nodes. In the realtime sense, mission orientation also means mission critical the degree of mission success is strongly correlated with the extent to which the overall system can achieve the maximum dependability regarding realtime constraints. In its simplest form, mission orientation requires that a priority or deadline associated with a mission has

global meaning when it spans over the network. More generally, global importance and urgency characteristics are propagated through the system, for use in resolving contention over system resources according to application defined policies.

**Performance** Realtime applications have stringent raw performance requirements. The optimised integration of application software and its supporting environment is desirable. This is in contrast with the popular layered design for non-realtime applications. Also, realtime applications often require trading off modularity, flexibility and functionality to maximize performance.

#### 1.2 Scope

Realtime systems span a wide variety of field of applications, including military, industry, commerce, medicine and so on. This indicates a wide spectrum of possible problems.

The scope of this research for realtime applications is *supervisory control* [86] as opposed to low-level, synchronous sampled data loop functions like sensor/actuator feedback control, signal processing, priority interrupt processing and so on. Supervisory control is a middle-level function, above the sampled data loop functions and below the human interface/management functions. This type of system does not do much direct polling of sensors and manipulation of actuators, nor does it provide extensive man/machine interfaces; rather, it deals with subsystems which provide these functions. The realtime response requirements of a supervisory control system are closer to the millisecond than either the microsecond or second ranges. Some treatments of interrupt processing (specifically, the communication interrupt processing for multi-media data) in the Computer Laboratory can be found in [23] and [61].

#### 1.3 The Proposed System

This dissertation describes  $RIDE^1$  — a distributed system environment developed for the task of programming and executing large realtime applications. Predictability, user control, timeliness, mission orientation, and efficiency are important attributes of the system.

The approach taken is to view RIDE as functional extensions and elaborations of a nonrealtime system environment. This approach permits reuse of a large amount of existing knowledge, infrastructure and software for writing distributed applications. It is also manageable within the work for one dissertation.

The RIDE design is based on an existing distributed environment, namely the Advanced Networked Systems Architecture (ANSA) [5]. The implementation is based on the Cambridge Systems Environment. It has an experimental microkernel WANDA, and runs ANSA Testbench 3.0. The environment is composed of networked 680x0, VAX, ARM, and MIPS machines.

RIDE inherits many of the advantages of modularity, configurability, maintainability, and

<sup>&</sup>lt;sup>1</sup>Real tIme Distributed system Environment

openness of the ANSA architecture. In the long term, the architectural concepts explored in RIDE are designed to be incorporated into the ANSA architecture itself as part of the ANSA phase III workprogramme.

#### 1.4 Outline of the Dissertation

The dissertation is structured as follows:

Chapter 2 discusses the research background and addressed issues.

Chapter 3 outlines the RIDE realtime programming model.

Chapter 4 presents the RIDE communication system.

Chapter 5 discusses an approach for the description of temporal relations.

Chapter 6 presents some of the implementation details.

Chapter 7 shows various experimentations and the system performance.

Chapter 8 reviews related research.

Chapter 9 outlines the conclusions and future work.

### Chapter 2

# **Background and Issues**

This research aims to gain new experience of distributed realtime systems environment in a modern context. Specifically, microkernel and distributed system environment technologies have been chosen as the design and implementation basis, due to their acceptance as the enabling technology in modern operating system practice [39, 50].

This chapter first reviews the current work on microkernels, distributed system environments, realtime scheduling and realtime communication; and then discusses the issues addressed by this dissertation.

#### 2.1 Microkernel Architecture

Microkernel architecture has been the subject of operating system research for the last decade, illustrated by such projects as: Amoeba [27], Chorus [34], Mach [30], the V-system [15], QNX [53] and WANDA [23]. Microkernel architecture is an approach for operating system implementation, which structures an operating system as a modular set of system servers sitting on top of a minimal microkernel, rather than using the traditional monolithic structure. This approach promises to help meet systems and platform builders' needs to support sophisticated and varied environments that can cope with growing complexity and new architectures. One of the main aims is the ability to integrate realtime applications, with new hardware technologies and distributed environments, all within an open system environment.

A microkernel provides generic services independent of a particular operating system, such as fast context switches, realtime scheduling, and memory management. A microkernel also provides a simple Interprocess Communication (IPC) facility that allows system servers to call each other and exchange data independently of specific system configurations.

#### 2.1.1 Microkernel and Realtime Systems

From the viewpoint of realtime applications, microkernels have three (potentially) important features — *performance*, *scale* and *preemptivity*.

- **Performance.** The stress on minimal generic low-level services, rather than a full operating system Application Programming Interface (such as UNIX), enables a microkernel to be executed in an efficient and *policy-free* way, that delivers nearly the full, device-level performance of the underlying hardware.

- Scale. The combination of the generic services of a microkernel forms a standard base which can support all other system-specific functions. These system-specific functions can then be configured into appropriate system servers managing the other physical and logical resources of a computer system. By including or excluding various resource managers (for example, a file system) either statically or at run time, microkernel architecture can be *scaled down* for single board computer-based targets, or *scaled up* to encompass many processors connected by various networks.

- **Preemptivity.** Time-consuming operating system services are performed by system servers. These server tasks can be scheduled at *client-driven* priorities, such that high priority user level tasks can preempt operating system work done on behalf of other, lower priority, user tasks. This permits high priority realtime activities with fast response time.

#### 2.2 Current Microkernels

This section presents a brief review of the Chorus, Mach and QNX microkernels. They represent the state of the art of microkernel research.

#### 2.2.1 Chorus

The Chorus architecture is based on a minimal realtime distributed *Nucleus* that integrates distributed processing and communication at the lowest level. The Nucleus provides generic mechanisms to sets of independent servers called *subsystems*, which coexist on top of the Nucleus. The Nucleus is divided into four major components:

- a realtime multi-tasking executive. It controls the allocation of local processors, manages priority-based preemptive scheduling of Chorus threads, and provides primitives for fine grain synchronization of, and low-level communication between, threads.

- a virtual memory manager. It is responsible for managing memory requirements of the system.

- a low level hardware **supervisor** which dynamically dispatches external events such as interrupts, traps and exceptions to dynamically defined routines or ports.

- an **IPC manager.** It provides the global communication services (exchange of messages through ports).

The Chorus/Mix subsystem has been provided as a server above the Nucleus to provide system builders with a standards-based (UNIX System V), realtime and distributed UNIX environment.

#### 2.2.2 Mach

The Mach microkernel provides facilities for the management of CPU, communication, virtual memory and devices. The key features are:

- Task and Thread Management. A task is a passive resource abstraction, consisting of an address space and communication access. Computation within a task is performed by one or more threads sharing resources in the address space. Threads are scheduled to processors, and may run in parallel on a multiprocessor. Two classes of scheduling policies are provided: fixed priority and timesharing. The schedulability of tasks, their threads, and processors can be controlled by user level programs.

- IPC is via the port mechanism: a communication channel implemented as a message queue. All services, resources, and facilities within the Mach kernel, as well as those exported by particular Mach tasks or servers, are represented as ports and are manipulated by sending messages to these ports. Ports are protected by a capability mechanism.

- Memory Object Management. The address space of a task is represented as a set of mappings from linear addresses to offsets within Mach memory objects. The Mach virtual memory service manages physical memory as a cache of the contents of memory objects. Memory object backing storage is implemented by a user level server.

- Device Support. Mach provides low-level device support. Each device is represented as a port to which messages can be sent to transfer data or control the device.

Traditional operating systems are implemented as Mach applications. Some example applications are 4.3BSD UNIX, MS-DOS, and the OSF/1.

#### **Realtime Mach**

Realtime Mach [101] has been developed by the Advanced Realtime Technology group at Carnegie Mellon university, based on the experience of the ARTS [100] distributed realtime kernel. The objective of the realtime Mach project has been to develop a realtime version of Mach that can support a predictable realtime computing environment and to develop an associated realtime tool set. Realtime Mach has the following realtime features:

- a Realtime Thread Model. The realtime-thread model supports a predictable realtime scheduler and provides a uniform interface to both realtime and non-realtime threads. Apart from priority, timing attributes may be associated with a realtime thread, which include deadline, deadline type (hard or soft deadline), worst case execution time, and periodic properties (start time, period, phase offset etc.).

- an Integrated Time-Driven Scheduler. The scheduler has two layers policy and mechanism. A scheduling policy is a self contained object, and can be associated with a processor or a processor set. Different policies can be assigned to different

processor sets. Apart from providing traditional realtime scheduling policies such as fixed priority, the scheduler also provides rate monotonic scheduling policies (see Section 2.5). The mechanism layer manages the actual thread context switch within the kernel.

- Realtime Thread Synchronization. The synchronization mechanism in realtime Mach is based on mutual exclusion using a lock variable. The lock acquire and release operations provide a priority inheritance mechanism (see Section 2.5) in order to avoid the unbounded priority inversion problem.

- a Memory Resident Object Manager. This mechanism eliminates the unpredictable page fault handing delay associated with the Mach memory object management by using *eager* evaluation rather than the Mach *lazy* evaluation technique.

#### 2.2.3 QNX

The QNX architecture, like Chorus and Mach, is composed of a small microkernel surrounded by a team of cooperating processes that provide higher-level operating system services. Realtime performance has been a main driving force for the development of QNX. The QNX microkernel implements four services:

- IPC. The microkernel provides process to process synchronous message-passing mechanisms. Message queues are implemented as servers based on this lower-level service. Processes can request that messages be delivered in priority order, and that process execution proceeds at the priority of the highest-priority blocked process waiting for service.

- Process Management. The process scheduling primitives conform to the IEEE POSIX 1003.4 (realtime thread) draft standard [59]. QNX provides preemptive, prioritised context switching with round-robin and FIFO scheduling.

- Low-level Network Communication. Low-level network communication is provided by an optional kernel-resident process, the network manager. When present, the network manager provides the microkernel with the facilities needed to move messages to and from other microkernels on a network, transparently to other processes.

- Interrupt Dispatch. QNX allows user processes to connect a handler within a user process to an interrupt vector within the kernel. The connected handler can then be called by the kernel in response to physical interrupts. Such interrupt handlers can be dynamically added and removed from a running system.

#### 2.3 Distributed System Environment

A distributed system environment (DSE) is a run-time system that provides a set of abstractions and tools to support the writing of programs in a distributed environment. The effect of using a DSE is that applications are automatically supported by a run-time environment which incorporates a set of *distribution transparency* mechanisms. These shield application designers and users from the technological complexities involved in distributed application programs. Remote Procedure Call (RPC) [12] and client-server interactions are widely accepted as DSE technical apparatus.

It is now recognised [50] that distribution transparency can be broken down into a number of individual transparency issues:

- location transparency masking off the physical location of services.

- access transparency masking any differences in representation and operation invocation mechanism.

- concurrency transparency masking overlapped execution.

- replication transparency masking redundancy.

- failure transparency masking recovery of services after failures.

- resource transparency masking changes in the representation of a service and the resources used to support it.

- migration transparency masking movement of a service from one application to another.

- federation transparency masking administrative and technology boundaries.

DSE's have been a central subject of distributed system research for the last ten years. Many DSE's have been proposed to handlé various aspects of distribution transparency. Some are dedicated systems to extend low-level operating system abstractions (such as message passing) with support for distributed objects, as illustrated by COOL [68] and MachObjects [44]. Some are special systems for a particular application area like faulttolerance or persistence, as illustrated by the ISIS [11] and OPERA [32] projects. Others are more general systems that handle many transparency issues; these are illustrated by the OSF DCE [38], UI Atlas [56] and the ANSA systems.

#### 2.3.1 Realtime Distributed System Environment

Despite the relative maturity of DSE research, realtime DSE remains a neglected, if not unaddressed, topic. The result is that even if low-level microkernels provide realtime services, a DSE provides no corresponding abstractions to use these services. Even worse, a DSE often mask off the realtime features of microkernels. This is unfortunate because realtime performance has been one of the two main driving forces (along with distribution) behind microkernel architecture research. The main aim of this research is therefore to extend the realtime features of a microkernel to the DSE level.

One common misconception is perhaps that DSE is not the suitable technology for realtime applications because RPC (as one of the main technique basis of DSE) is often criticised for providing poor performance or is not fast enough. This is a misconcept because the objective of realtime computing is to meet the timing requirements of an application, rather than being fast. The most important property of a realtime system is *predictability* (see Section 1.1). On the other hand, fast is a relative term. As technology progresses, there will be faster and faster RPC systems. Even now it is not difficult to provide milliseconds level RPC calls (as the required performance for the *supervisory control* targeted by RIDE, also see Section 1.2). For example, there are already reports of systems that can provide hundreds of microseconds level RPC calls [10] [63]. Fast computing is helpful in meeting stringent timing constraints, but fast computing alone does not bring realtime properties.

#### 2.4 Example Distributed System Environments

This section presents a brief overview of the Chorus COOL, Mach MachObjects, DCE and ODP distributed system environments.

#### 2.4.1 COOL

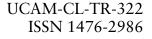

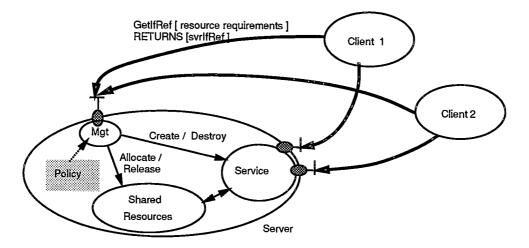

The Chorus Object-Oriented Layer (COOL) is a system designed to provide generic support for distributed object-oriented programming. The system was developed by Chorus systems and INRIA. The architecture of COOL is shown in Figure 2.1.

Figure 2.1: The COOL Architecture

The COOL base layer is designed as a generic support platform for object based systems. The layer provides a set of abstractions mapped directly on to the Chorus microkernel which extend the microkernel interface to include the notions of objects and object management. The layer supports the creation of typed objects and the subsequent invocation of operations on objects. The layer also manages the mapping of objects into Chorus virtual address spaces (referred to as contexts in COOL) and the saving of such contexts as a form of coarse grained persistence.

The COOL run-time layer provides mapping from a language or system level object model to the COOL base facilities. The current system has been focused on a run-time layer for C++. This layer transparently maps C++ objects on to COOL base facilities thus providing C++ programmers with the ability to develop dynamic distributed applications. The COOL/C++ objects may be persistent, and can be invoked both locally and remotely.

The ANSA Testbench has been used by the COOL environment as an RPC mechanism for remote object invocations.

#### 2.4.2 MachObjects

MachObjects is an object-oriented run-time environment on top of the "pure" Mach microkernel. It provides dynamic typed objects, delegation, and a generic transparent RPC mechanism. Transparent access to remote objects is the key feature of MachObjects.

The Mach system servers are written using MachObjects. All the entities of the system, like files, directories, etc., are represented by objects. The interface presented by the system is defined as the set of operations exported by the operating system objects. Serverside objects are represented at the client by a proxy which completely hides distribution from the user code. Proxies may forward invocations to the server or may themselves perform some work.

#### 2.4.3 DCE

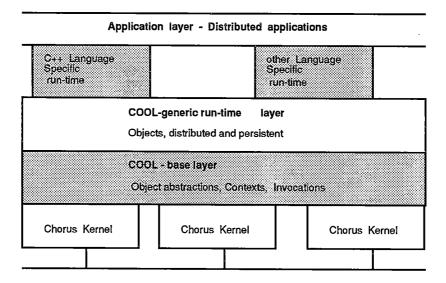

The Distributed Computing Environment (DCE) from the Open Software Foundation addresses the problem of interoperability by providing a distributed platform, a run-time system, that may span multiple architectures, protocols, and operating systems. DCE is a layer between the operating system and network on the one hand, and the distributed application on the other. The architecture of DCE is shown in Figure 2.2.

Figure 2.2: The Distributed Computing Environment Architecture

DCE's services are organized into two categories: Fundamental Distributed Services and Data-Sharing Services. The Fundamental Distributed Services are: RPC service, naming (directory) service, time service (distributed time reference), threads service, and the security service. The DCE threads service is conceptually a part of the operating system layer. If the host operating system already supports threads, DCE can use this, otherwise DCE presents a user-level threads package instead. The DCE Data-Sharing Services are based on the Fundamental Distributed Services, and include distributed file system service, diskless support service and personal computer integration service.

#### 2.4.4 Open Distributed Processing

The ISO standards community have established a work program to define a Basic Reference Model of Open Distributed Processing (RM-ODP) [61] The primary goal of ODP is interworking between applications and sharing of data between organizations. The RM-ODP is organized as a set of five languages, called the enterprise, information, computational, engineering and technology languages, for describing different *views* of distributed systems.

The enterprise and information languages are introduced as the means to make the link between technical solutions and user requirements. The computational language is a formalization of a programming language based on abstract data types suitable for specifying distribution in functional terms. The engineering language focusses on the structural aspects of the support for distribution. **Declarative**, selective and modular distribution transparency is the main characteristic of the engineering language. The technology language is used to map the logical architecture to product architectures.

APM's Advanced Networked Systems Architecture (ANSA) is a refined model for ODP. APM also developed a prototype DSE for ODP, called the ANSA Testbench.

The ODP community has not made any serious attempt at supporting realtime applications, but there is some ongoing work to incorporate stream interfaces with ODP for multimedia applications [31]. Realtime is currently an important issue in the development of ANSA Phase III at APM.

#### 2.5 Realtime Scheduling

Resource scheduling plays a central role in any non-trivial realtime system. Substantial research has focused on the performance of realtime systems in terms of schedulability analysis — the feasibility of scheduling the required workload onto the available resources (processors and so on).

A scheduling approach that allows schedulability analysis is considered a basic requirement for designing hard realtime systems [45]. *Hard realtime systems* are those realtime systems in which the time constraints of a task set play a major role; not meeting such time constraints may lead to catastrophe results. *Soft realtime systems* are those realtime systems in which meeting the time constraints of a task set are desirable, but failing to do so does not cause a system failure. A system is said to be *schedulable* if it meets all deadlines of a task set.

Cyclic executive and rate monotonic scheduling are two most popular scheduling approaches in current realtime applications. There is also an increasing interest in using deadline based scheduling for practical realtime systems.

Cyclic Executive Scheduling. Cyclic executive scheduling [7] was a common technique used before concurrent programming became popular, and is still used where concurrent programming is not supported. This approach offers a framework for scheduling periodic tasks. It performs a sequence of actions during a fixed time period. The execution is divided into two parts. The major cycle schedules computations to be repeated indefinitely, and is composed of minor cycles. Each task is divided into subcomponents so that the execution of each subcomponent fits into a minor cycle in a way that satisfies the task timing constraints. In other words, this approach forces a programmer to *pre-schedule* programs based on their static knowledge to ensure predictable execution timing.

**Rate Monotonic Scheduling**. Rate monotonic scheduling [76] uses a preemptive fixedpriority scheduling algorithm that assigns higher priority to the tasks with shorter periods. This approach is *optimal* among fixed-priority scheduling schemes. The CPU utilization of a task, U(i) is calculated by U(i) = C(i)/T(i), where C(i) and T(i) are the execution time and period of task i, respectively. Assume a task's deadline is the same as its period, n independent periodic tasks can meet their deadlines if the following formula holds:

$$\sum_{i=1}^{n} U(i) \le n \left( 2^{1/n} - 1 \right) \qquad (\approx 0.69)$$

This formula is very simple but pessimistic. In the case of a harmonic task set where all periodic tasks start at the same time and all periods are harmonic, the CPU utilization is schedulable up to 100 percent. More precise schedulability analysis of the rate monotonic algorithm is discussed in [70]. Rate monotonic scheduling does not require programmers to split tasks manually as the cyclic executive does, but the tasks must be preemptive and there is some overhead for context switching.

| Tasks | Period | Execution       | Utilization |

|-------|--------|-----------------|-------------|

| T1    | 50     | $1\overline{2}$ | 24%         |

| T2    | 40     | 10              | 25%         |

| T3    | 30     | 10              | 33%         |

Table 2.1: A Set of Tasks with 82% Utilization

**Deadline Based Scheduling**. Deadline based scheduling uses explicit information about application supplied deadlines. With the earliest (or shortest) deadline scheduling, the scheduler runs the task with the closest deadline. Deadline based scheduling is a *dynamic* scheme that allows priority to change with time. It was shown in [76] that earliest deadline scheduling is *optimal* among all scheduling schemes. This approach which is preemptive will feasibly schedule a periodic task set as long as:

$$\sum_{i=1}^{n} U(i) \le 1$$

As a comparison, the task set shown in Table 2.1 with 82% CPU utilization cannot be scheduled by the rate monotonic scheme, but can be scheduled by the earliest deadline scheme. Another attractive feature of earliest deadline scheduling is that it deals well with systems that are mainly composed of aperiodic tasks. The disadvantage of earliest deadline

scheduling is that during a transient overload, deadlines are missed in an unpredictable fashion [92].

It must be emphasized that predictable scheduling in a hard realtime system with general resource (such as multiprocessors and networks) constraints and processing constraints (such as processing orders) is very complex and a subject of much research [106]. General solutions are not possible in polynominal time and therefore are not appropriate for practical applications. Current realtime scheduling still relies heavily on manually tuning programs in an application-based style.

#### 2.5.1 Scheduling Task Synchronization

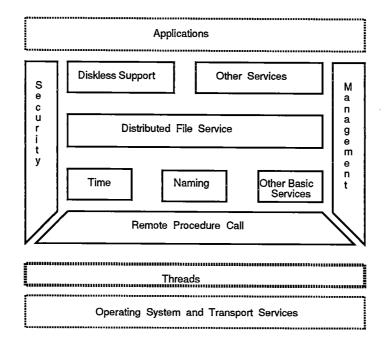

When tasks interact via a synchronization primitive, they may become blocked in the middle of their execution. In order to calculate their worst-case (or average) execution time it is necessary to know the potential length of this blocking time. A static priority scheme is no longer adequate because it gives no bound for the period of time a task can be blocked. This is known as the *unbounded priority inversion* problem. Similar problems exist for the earliest deadline scheme.

**Priority Inversion Problem Illustration**. Suppose a low-priority task L is preempted inside a critical region which is guarded by a binary semaphore. A high-priority task H then attempts to enter the critical region and blocks. H cannot continue until L leaves the critical region, and runnable tasks with priorities in the gap (see Figure 2.3) between H and L prevent L from running. H blocks for an unpredicatable and possibly lengthy period of time.

low priority

Figure 2.3: Priority Inversion

To address the problem, Sha et al [93] proposed two protocols based on binary semaphores (mutexes). They are called the basic **priority inheritance protocol** (PIP) and the **priority ceiling protocol** (PCP). The PCP provides better worst-case bound which is the duration of execution of a single critical section of a lower priority task. Both PIP and PCP have been adopted by the POSIX 1003.4a [59].

The idea of the PIP is that when a task blocks higher priority tasks, it executes its critical section at the highest priority level of all the blocked tasks. After exiting its critical

section, the task resumes its original priority level.

The **priority ceiling** of a mutex S is defined to be the highest priority of all the tasks that may acquire S. The priority ceiling value is assigned to a mutex at initialization time. Under the PCP a task t is allowed to acquire a mutex only if t's priority is greater than the highest priority ceiling of all the mutexes that are locked by other tasks in the system. Otherwise, t is blocked and the task which has locked the mutex with the highest priority ceiling inherits t's priority until it releases the mutex.

Like the case for resource constrained realtime scheduling, general-purpose solutions for predictable realtime synchronization are not possible in polynomial time. Mok [82] showed that the problem of deciding the schedulability of periodic precesses using semaphores for mutual exclusion is NP-Hard. Most practical approaches impose some constraints on interprocess synchronization. For example, the PCP allows only mutual exclusion and not condition synchronization between tasks.

#### 2.6 Realtime Communication

Ensuring message-level timing correctness for interprocess communication is difficult using current technology and a substantial research challenge. There are at least *media*, *protocol* and *network scheduling* problems to be solved before a predictable realtime communication system become possible.

The problem of temporally (periodicity, jitter) and spatially (bandwidth) constrained communication has been studied in several directions. In the context of embedded realtime systems, these efforts have been directed mainly towards designing media access protocols for multi-access networks [57]. For example, Strosnider and Marchok [96] use a variation of the rate-monotonic scheduling algorithm to control access to a token-ring network. Priorities are assigned to message sources at design time based on the periodicity of message generation and the message schedulability can be checked then. This approach, however, works only for simple and static communication requirements and does not scale to internets.

In the context of multi-media communication systems, these efforts have been mainly conducted on the Asynchronous Transfer Mode (ATM) networks [78]. Media such as video and voice have both temporal and spatial communication requirements, and therefore their transportation needs to be done in realtime. ATM networks transfer data in small packets, known as cells, allowing fine granularity bandwidth sharing and reducing the delays due to contention and routing. ATM has been adopted as the basis for the Broadband Integrated Services Digital Network (B-ISDN) [58].

ATM communication is connection-oriented at the lowest level. All information is transferred in a Virtual Circuit assigned for the complete duration of the connection. Both network and operating system resources can be reserved for individual virtual circuits at connection setup time to guarantee their communication requirements which are commonly referred to as the desired Quality of Service (QoS). QoS specification, management and guarantee are still ongoing research topics in the network area, and there are no viable solutions currently. A survey by [64] shows various QoS definitions in terms of traffic characteristics. Dixon [23] discussed system mechanisms to support QoS in the Cambridge ATM environment. Nicolaou [84] discussed the QoS management within the ANSA environment to extend QoS from operating systems to the applications. Sreenan [94] discussed QoS requirements for multimedia synchronization services.

QoS communication is not addressed in this dissertation. Rather, connection oriented IPC communication — virtual circuits that allow QoS associations — are assumed to exist on underlying operating systems. This allows the dissertation to concentrate on the integration of realtime communication with computation.

#### 2.7 Summary of Background

Microkernel architecture structures an operating system as a modular set of system servers sitting on top of a minimal microkernel. From the viewpoint of realtime applications, the architecture offers three (potentially) important features — *performance*, *scale* and *preemptivity*. Realtime performance and distribution have been the two main drive forces in microkernel architecture research.

A DSE provides a set of *distribution transparency* mechanisms. These shield application designers and users from the technological complexities involved in distributed application programs. Despite the relative maturity of DSE research, realtime DSE remains a neglected topic.

Cyclic executive and rate monotonic scheduling are the two most popular scheduling approaches in current realtime applications. There is also an increasing interest in using deadline based scheduling for practical realtime systems.

ATM networks are considered to be of fundamental importance to real time communications.  $\space{-1.5}$

#### 2.8 Addressed Issues

The RIDE system developed in this dissertation is concerned with the design and construction of a DSE for supporting realtime applications. The main issues addressed by RIDE are as follows:

- realtime programming model.

- timed remote procedure calls.

- description of temporal behaviours.

- empirical validation.

The following subsections provide a brief overview for each of the four major issues.

#### 2.8.1 Realtime Programming Model

The essence of a realtime programming model is to provide the basic abstractions so that stringent timing constraints of realtime activities are respected (guaranteed at best). A serious difficulty is that the actual timing characteristics of software are determined not only by the raw processor speed, but also by the sharing policy for scarce resources. For example, the realtime response of a time-shared system depends heavily on the processor scheduling policy of its operating system. In most high level languages, this dependency is considered as non-essential detail that is to be hidden from the programmer. As a result the performance of software implemented in these languages becomes sensitive to system resource allocation strategies (in a dynamic system, this means performance depends on system load), and outside the control of individual programmers. More complex resources such as the communication subsystem of distributed systems further accentuate the problem with the introduction of (sometimes distributed) resource allocation algorithms which are usually inaccessible to the application programmer.

The RIDE realtime programming model is based on the ANSA computation and engineering models. As in the ANSA system, objects provide the basis for distribution, interfaces of objects provide service access points, and named operations of an interface provide the actual services. Abstractions, mechanisms and policies are developed to allow a programmer to access and control the resource allocation of the supporting environment. Tasks (representing processor resources, see Chapter 3) and communication channels (representing communication resources, see Chapter 4) are considered the most important system resources. Both static resource allocation — the allocation of system resources to interfaces — and dynamic resource allocation — the allocation of system resources to invocations are supported. **Predictability, user control** and **mission criticality** are the main concerns of the RIDE realtime programming model.

#### 2.8.2 Timed Remote Procedure Calls

ANSA is an RPC based system. A basic goal of many RPC systems is to make the semantics of a remote call as close as possible to that of a local call. As already mentioned, this is known as distribution transparency. However, distribution cannot be completely ignored: applications will have to deal with the possibilities of concurrent access to shared resources, variable latency in accessing resources and communication failures disturbing access to resources. The semantics of remote calls are implemented by RPC protocols. Perhaps the weakest semantics are to provide no guarantee when a failure occurs; an invocation might result in the actual program being called zero, one, or more times. Stronger semantics are more useful and are difficult to achieve. Two often referred to semantics are *exactly-once* and *at-most-once* executions. Realtime applications add another dimension to the problem: timeliness — arbitrary delays associated with synchronous RPC invocations cannot be tolerated.

The RIDE solution to the timed RPC is the design of a dependable RPC protocol through which reasonable timing constraints (representing different tradeoffs between consistency and strictness) of a remote invocation can be specified clearly and enforced. This relieves the additional burden of having to monitor and manage timing constraints by application programmers during remote calls. This is discussed in Chapter 4.

#### 2.8.3 Description of Temporal Behaviours

Realtime systems and especially distributed realtime systems usually consist of many realtime activities with different but related time constraints. These activities must be temporally related to each other so all time constraints can be met. A realtime programming system therefore must provide a *temporal synchronization* facility. Some important requirements of this facility are as follows.

- the capacity to express different types of timing requirements.

- provision of a useful abstraction. This is better achieved by being based on a model that makes it easier to ensure the program's temporal correctness.

- preserve the separation of concerns so that the cooperative computations do not have to share assumptions about one another.

- provide mechanisms for run-time systems to enforce timing constraints.

The approach taken is to keep in-line with the ANSA Computational Model. The temporal synchronization facility is represented as a kind of special service accessible through well defined ANSA interfaces. Normal invocations on the interfaces are used to notify and enforce temporal synchronization conditions. The model used is **timed automata** as discussed in Chapter 5.

#### 2.8.4 Empirical Validation

Given that there are few technology-independent lessons to be learned in systems research, it is important to evaluate some of the basic premises of systems design through actual design and implementation efforts. It seems clear that computer systems research must be validated by empirical studies — it is impossible to do credible systems research without actually building and using systems.

The systems concepts described in this thesis have been validated through the construction of a working system based on extensions and elaborations of a microkernel and a distributed system environment on bare hardware (see Chapter 6). This approach exposes many technology-driven, low-level engineering details that are critical to the validation of high-level concepts and are often not considered or neglected in other concept study, emulation or simulation approaches.

The Distributed Hartstone Benchmark [79] has been ported to the RIDE run-time system and used to evaluate the synthetic performance of RIDE. The multiprocessor effects on RIDE are also evaluated. These are discussed in Chapter 7.

#### 2.9 Summary

This chapter has examined the background relevent to realtime distributed system environment and found it a neglected topic. The goal of this dissertation is to construct such a system environment which can better support distributed realtime applications.

## Chapter 3

# The RIDE Realtime Programming Model

RIDE inherits an object-based programming model from the ANSA architecture. This chapter discusses the realtime aspects of RIDE objects. The structure of RIDE objects is examined along with object invocation mechanisms, the handling of priorities and deadlines, resource allocations, scheduling mechanisms and policies, and the application's control over scheduling.

General distributed object execution is discussed first. This is followed by a discussion of the ANSA object execution model in terms of tasking and scheduling. The RIDE counterparts are then presented.

#### 3.1 Distributed Object Execution

The use of an object-oriented data model and the client-server execution model makes the distribution of data and the processing implicit in nature. In non-realtime environments, object-oriented design has been successful in simplifying the design, implementation, and maintenance of software in many distributed systems such as Comandos [53], EMER-ALD [29] and ANSA.

Object interdependence can be classified into two categories: *static* interdependence — the structural relationships between objects, and *dynamic* interdependence — the interactions between objects. Many useful results are known about the static relationships between distributed objects [50] [13]. Related concepts, such as abstract data typing, type checking and subtyping, are accepted and used widely. On the other hand, little consensus has been achieved on the execution view of objects. Many approaches to object execution have been proposed, some of which are the *active object* model [29], the *passive object* model [1], and the *actor object* model [6].

For realtime applications, this execution aspect is of vital importance — it has fundamental impact on the *predictability* of computational activities. Realtime object execution models are required to address not only how the computational activities are carried out, but also how shared resources are used (i.e. the manner in which contention for system resources is resolved taking into account timing constraints of realtime activities). The latter issue is often neglected and considered irrelevant engineering detail in non-realtime computing. Distributed realtime systems must provide support for the specialized requirements of realtime communication, tasking, scheduling, and control. These requirements must be explicitly addressed in an object execution model, if the object-oriented approach is expected to be applicable to a realtime world.

#### **3.2 ANSA Object Execution**

The ANSA Object Execution Model (AOEM) is defined by the ANSA Computation Model (ACM) and ANSA Engineering Model (AEM). ACM and AEM are reviewed first before AOEM is discussed.

#### 3.2.1 ANSA Computation Model

A computation model is a framework for describing the structure, specification and execution of programs. The principle behind and the concepts underlying the ANSA architecture are articulated via the ACM [87]. This subsection briefly summarises the overall concepts of the ACM.

The key ACM concepts are:

- (Computational) Object: a unit of program modularity having state and *operations* for initializing, accessing and updating that state. Object state may contain references to the interfaces of itself and other objects.

- Interface: a view of an object as an abstract service. An interface is specified as a set of operations together with synchronization and ordering constraints on the use of these operations.

- **Operation:** part of an interface. An operation has a *signature* and a body which defines the effect and outcome from an *invocation* of the operation.

- Signature: a specification of the name of an operation, the number and interface types of the argument parameters and, optionally, a set of *terminations* which specify the possible outcomes from the operation.

- Activity: the agency by which computations make progress. An activity may pass from one object to another by the first *invoking* an operation on an interface of the second. Activities may split into parallel sub-activities and later recombine. New activities can be initiated to proceed in parallel, these may be able to communicate with other activities but are not dependent upon their initiating activity.

- **Termination:** the specification of a set of possible outcomes from *invocations* of an operation. A termination has a name and specifies the *interface types* of the result parameters from an outcome with that name.

Interface type: the signature of the operations in an interface of the type.

- (**Operation**) **Invocation:** the execution of the body of an operation defined by a reference to an interface and an operation name in a context established by the referenced interfaces and a set of arguments.

- Server: in the context of an invocation, the object which provides the interface containing the operation being invoked.

Client: in the context of an invocation, the object from which the invocation was initiated.

The ACM is in two parts:

- an interaction model defines permitted forms of interaction and a type scheme within which potential interactions are to be classified. The interaction model consists of an invocation scheme and a type scheme.

- the construction model defines elements from which the interacting objects may be constructed.

The invocation scheme defines how clients may use interfaces provided by servers. Two kinds of operation, *interrogation* (call) and *announcement* (cast), are permitted. Invocation of an interrogation is a synchronous request/response style. Invocation of an announcement is an asynchronous request only style, a new activity is created in the server and the invoking activity continues in the client.

The type scheme provides a set of types into which interfaces are classified and defines a relation over interface types that allows the detection of the possibility of interaction errors before the interaction commences.

The ANSA construction model provides the elements necessary to construct objects that conform to the ANSA interaction model.

#### **3.2.2 ANSA Engineering Model**

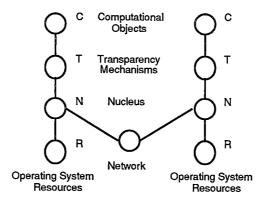

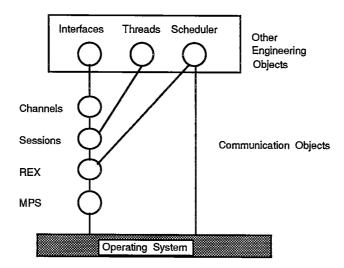

The AEM provides a framework for the specification of mechanisms to support distribution of application programs that conform to ACM. The details of AEM can be found in [48]. The AEM contains a number of sub-components and supports a number of applicationlevel components as shown in Figure 3.1.

- **Transparency Mechanisms** provide a uniform interface for distributed applications that address the problems and benefits of distribution. The transparency mechanisms communicate with one another via the nucleus and the network to achieve the desired transparency.

- Nucleus is the part of the AEM which provides minimal and sufficient support for the implementation of distribution. It encapsulates all of the heterogeneity of processor and memory architectures. The Nucleus itself is not distributable.

The main concepts of the AEM may be summarised:

Figure 3.1: Engineering Model

- Capsule: the collection of computational objects (in engineering form), transparency mechanisms and nucleus forming a virtual node of a network. It can be seen as the abstraction of an address space in a local operating system to provide the unit of protection and failure atomicity.

- **Thread:** a sequence of instructions modelling a computational model activity within a capsule. It represents a unit of potentially concurrent activity that can be evaluated in parallel with other threads, subject to synchronization constraints.

- Task: a virtual processor which provides a thread with the resources (e.g. a stack) it requires to progress. Tasks<sup>1</sup> provide the resources for real concurrency. An ANSA task is conceptually equivalent to an operating system *thread*.

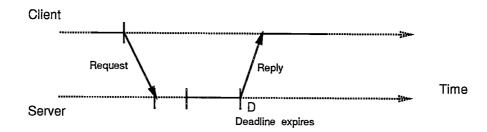

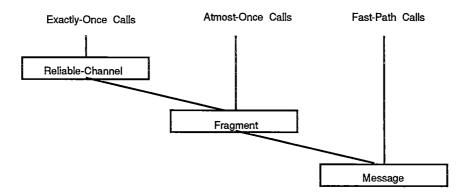

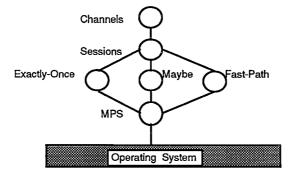

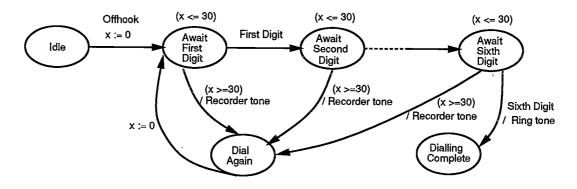

- Interface Reference: an interface reference is an identifier which contains sufficient information to allow the holder (the client) to establish communication with the interface denoted by the reference (the server). Interfaces have types (corresponding to their code component) which may be instantiated multiple times with different state (corresponding to their data component). Such instantiations are called interface instances, and interface references always refer to interface instances.