Number 317

# Femto-VHDL: the semantics of a subset of VHDL and its embedding in the HOL proof assistant

John Peter Van Tassel

November 1993

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

## © 1993 John Peter Van Tassel

This technical report is based on a dissertation submitted July 1993 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Gonville & Caius College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

#### **ABSTRACT**

The design of digital devices now resembles traditional computer programming. Components are specified in a specialised form of programming language known as a hardware description language. Programs written in such languages are then executed to simulate the behaviour of the hardware they describe. These simulations cannot be exhaustive in most situations, so result in high, yet incomplete, confidence that the proper behaviour has been achieved.

The formal analysis of programming languages provides ways of mathematically proving properties of programs. These properties apply to behaviours resulting from all possible inputs rather just than a subset of them. The prerequisite for such an analysis is a formal understanding of the semantics of the language.

The Very High Speed Hardware Description Language (VHDL) is currently used to specify and simulate a wide range of digital devices. The language has no formal mathematical semantics as part of its definition, hence programs written in it have not been amenable to formal analysis.

The work presented here defines a structural operational semantics for a subset of VHDL. The semantics is then embedded in a mechanical proof assistant. This mechanisation allows one not only to reason about individual programs but also to express equivalences between programs. Examples which highlight the methodology used in this reasoning are provided as a series of case studies.

#### **ACKNOWLEDGEMENTS**

None of this would have been possible without the financial assistance provided by Dr. John Hines at Wright-Patterson AFB through the United States Air Force Office of Scientific Research. John also gave generously of his time whenever help was needed with anything pertaining to VHDL. Additional financial support in the form of a bursary from Smith System Engineering was also appreciated.

The members of the Cambridge Hardware Verification Group have been instrumental in the successful completion of this work. Particular thanks go to Mike Gordon for supervising and putting up with me. Mike's ability to listen to the most silly ideas and slog through my horrible grammar is an argument for his immediate canonisation. Members of the group that should also be singled out are Juanito Camilleri for initial instruction in operational semantics and helping in getting to grips with how it might be applied to VHDL and Tom Melham for providing not only a sounding board for my strange ideas, but also some of the tools that made working with this stuff in HOL relatively painless. Thanks also to Juanito Camilleri, Mike Gordon, David Hemmendinger of Union College, Beth Levy of Aerospace and Bill Young of CLI who read parts of this opus and provided comments on making it better.

Last, but by no means least, the highest accolades should go to my parents for believing in and putting up with me over the years. Their unflagging support has been a great comfort both during the research and the writing up.

# **CONTENTS**

| CHAPTER 1 | INTRODUCTION1                       |

|-----------|-------------------------------------|

|           | 1.1 Motivation1                     |

|           | 1.2 Philosophy2                     |

|           | 1.3 Language History2               |

|           | 1.4 Application Areas3              |

|           | 1.5 Evaluation of VHDL Programs3    |

|           | 1.6 Formalisation6                  |

|           | 1.7 Automation6                     |

|           | 1.8 Examples                        |

|           | 1.9 Accomplishments7                |

| CHAPTER 2 | RELATED WORK9                       |

|           | 2.1 Simulation-Time Validation9     |

|           | 2.2 Semantics-Based Verification10  |

|           | 2.2.1 Denotational Work10           |

|           | 2.2.2 Operational Work11            |

|           | Use of an Oracle11                  |

|           | Secure Formalisations11             |

|           | 2.2.3 Other Approaches12            |

| CHAPTER 3 | STATIC SEMANTICS13                  |

|           | 3.1 Femto-VHDL13                    |

|           | 3.2 Definitional Style16            |

|           | 3.3 Syntactic Well-Formedness17     |

|           | 3.3.1 Multiple Drivers17            |

|           | 3.3.2 Signal Relationships19        |

|           | Signal Extraction19                 |

|           | Well-Formedness of Design Signals22 |

|           | 3.3.3 Overall Well-    | Formedness                              | 23 |

|-----------|------------------------|-----------------------------------------|----|

| CHAPTER 4 | DYNAMIC SEMANT         | ICS                                     | 25 |

|           | 4.1 Operational Seman  | ntics                                   | 25 |

|           | 4.1.1 Inductive Def    | finitions                               | 25 |

|           | 4.1.2 Inductive Def    | finitions and Femto-VHDL                | 26 |

|           | 4.2 Information Organ  | isation                                 | 27 |

|           | 4.2.1 Delay Extract    | ion                                     | 28 |

|           | 4.2.2 Well-Formed      | ness                                    | 29 |

|           | 4.2.3 Equivalence      |                                         | 30 |

|           | 4.3 Rules of the Seman | tics                                    | 32 |

|           | 4.3.1 Rules for Boo    | lean Expressions                        | 32 |

|           | 4.3.2 Rules for Sequ   | uential Statements                      | 33 |

|           | 4.3.3 Rules for Con    | ncurrent Statements                     | 38 |

|           | 4.3.4 Rules for Initi  | ialisation                              | 41 |

|           | 4.3.5 Rules for the    | Simulation Loop                         | 42 |

|           |                        | <u>^</u>                                |    |

| CHAPTER 5 | MECHANISING FEM        | TO-VHDL                                 | 49 |

|           | 5.1 HOL                |                                         | 49 |

|           |                        |                                         |    |

|           | 5.1.2 The Logic        |                                         | 50 |

|           | _                      |                                         |    |

|           | 5.1.4 Theories         |                                         | 51 |

|           | 5.1.5 Definitions      |                                         | 52 |

|           | 5.1.6 Proof            |                                         | 52 |

|           | 5.1.7 Libraries and    | Tools                                   | 54 |

|           | 5.2 Femto-VHDL in H    | OL                                      | 55 |

|           | 5.2.1 Embedding        |                                         | 55 |

|           | Syntax                 |                                         | 55 |

|           | Semantics              |                                         | 56 |

|           |                        |                                         |    |

|           | The Conversi           | on ONCE_AROUND                          | 59 |

|           |                        | on finish_GAMMA                         |    |

| CHAPTER 6 | CASE STUDIES           | *************************************** | 63 |

| 6.1          | A NAND Gate63                                                    |

|--------------|------------------------------------------------------------------|

|              | 6.1.1 Behaviour of the Specification65                           |

|              | 6.1.2 Behaviour of the Implementation67                          |

|              | 6.1.3 Equivalence69                                              |

| 6.2          | DeMorgan Property69                                              |

|              | 6.2.1 Negation of a Conjunction vs. a Disjunction of Negations70 |

|              | Behaviour70                                                      |

|              | Equivalence71                                                    |

|              | 6.2.2 Negation of a Disjunction vs. a Conjunction of Negations71 |

|              | Behaviour72                                                      |

|              | Equivalence72                                                    |

|              | 6.2.3 Non-equivalence73                                          |

| 6.3          | Parity Checker74                                                 |

|              | 6.3.1 Specification74                                            |

|              | Initialisation75                                                 |

|              | General Behaviour76                                              |

|              | 6.3.2 Implementation77                                           |

|              | Initialisation80                                                 |

|              | General Behaviour80                                              |

|              | 6.3.3 Equivalence81                                              |

| 6.4          | A Counter Cell83                                                 |

|              | 6.4.1 Specification84                                            |

|              | 6.4.2 Implementation85                                           |

|              | 6.4.3 Equivalence88                                              |

| CHAPTER 7 CO | NCLUSIONS89                                                      |

| 7.1          | The Semantics89                                                  |

| 7.2          | The Methodology90                                                |

|              | The Future90                                                     |

| BIBLIOGRAPHY | <i>/</i> 93                                                      |

| APPENDIX A H | OL PROOFS97                                                      |

| A.1          | Theorem 3.3.2.1                                                  |

| A.2          | Theorem 3.3.3.198                                                |

| A.3          | Theorem 4.2.3.198                                                |

| A.4 Theorem 4.2.3.2                   | 98  |

|---------------------------------------|-----|

| A.5 Theorem 4.3.3.1                   | 98  |

| A.6 Theorem 4.3.3.2                   | 98  |

| A.7 Theorem 4.3.3.3                   | 99  |

| A.8 Theorem 4.3.3.4                   | 99  |

| A.9 Theorem 4.3.3.5                   | 99  |

| A.10 Theorem 4.3.3.6                  | 99  |

| A.11 Theorem 4.3.5.3                  | 100 |

| A.12 Theorem 4.4.1                    | 100 |

| APPENDIX B A WORKED EXAMPLE           | 107 |

| B.1 Derivation for the Specification  | 107 |

| B.2 Derivation for the Implementation | 111 |

| B.3 Equivalence Proof                 | 120 |

## **CHAPTER 1**

#### INTRODUCTION

This dissertation is devoted to the definition of a structural operational semantics for a subset of the Very High Speed Integrated Circuit (VHSIC) Hardware Description Language (VHDL) and its embedding in the HOL proof assistant. The research is presented in seven chapters. The current one gives some motivation for the work, some background on the language and its uses, and acts as a synopsis of the material that follows in the rest of the document. The second chapter gives an overview of past and present research that is of a complimentary nature to that described here. Chapter 3 presents the subset while Chapter 4 defines its operational semantics. The fifth chapter contains an overview of the proof assistant being used and a discussion of how the semantics is embedded in it. Chapter 6 is made up of a series of case studies that show various ways of working with the embedded semantics. Finally, Chapter 7 finishes the exposition by making some concluding remarks and posing questions for future research.

#### 1.1 Motivation

The complexity of current real-time systems such as those contained in modern avionics systems is so great that they cannot be completely tested. In many cases, there is no direct mechanical link between the pilot and the control surfaces. Onboard computers must interrupt the inputs being made by the pilot, match them against the current condition of the aircraft and make the necessary adjustments to these surfaces – hence the name "fly by wire". While the success of a mission or the lives of passengers depend on these computers, current testing methods cannot explicitly show that the equipment will respond correctly to all possible inputs.

The silicon integrated circuits used in inflight controls and most other modern applications are becoming so complex that exhaustive simulation of their behaviour before fabrication is a practical impossibility. In the case of aircraft controllers, this means that the devices are only functionally checked over critical inputs. While

current design and engineering practices tend to eliminate problems before they reach the marketplace, bugs do get into systems. It is becoming evident that a more secure way of creating electronic devices is needed in the future.

When VHDL arrived on the hardware design scene, it was described as the solution to many existing industry problems. Chief among these was to bring some order to the collection of languages and tools then in current use. But when VHDL itself was designed, very little thought was given to its formal semantics, much less to using such a semantics to reason about individual programs. The result has been a recent upsurge in research efforts addressing precisely these problems. The rest of this document is a discussion of research into the semantics of a subset of VHDL and ways to reason about program texts written in that subset using a mechanical proof assistant.

# 1.2 Philosophy

Emphasis has been placed on formalising the meaning of VHDL constructs as specified in the Language Reference Manual [21]. The relationship between these constructs and the simulation engine that evaluates them has been investigated. While taking this approach may seem overly pragmatic, it not only reflects the actual simulation behaviour of VHDL, but also corresponds intuitively to the way in which VHDL users think about the language. A different approach to characterising the semantics might have destroyed this link. For purposes of the current research, it has been necessary to utilise only a subset of full VHDL. Nevertheless, that subset is sufficient to demonstrate the most salient features of that model, and to provide methodological clues as to how such a formalisation might be used in practice.

# 1.3 Language History

VHDL is a hardware description language (HDL) currently in use by a large segment of the design community. It is a verbose, event-driven simulation language whose semantics is defined, at least informally in the Language Reference Manual, by the way in which the various language constructs are evaluated by the simulation engine [21].

To better understand VHDL and its place in current design practice, one should consider the evolution of the language:

early-1980's: Chaos

A time period characterised by the existence of many proprietary hardware description languages and simulators. Furthermore, no one HDL is used throughout the entire design process. In many cases, ad-hoc mechanisms are developed to translate between the tools and languages in use at different stages of the design. This leads to increased confusion and provides a further avenue for the introduction of bugs.

mid-1980's: VHSIC programme

The United States Air Force, a large consumer of custom electronics obtained from a variety of vendors, is faced with the need to rationalise its procurement process. The primary concern is that all designs submitted as a part of the bidding process are written in the same non-proprietary HDL, and meet certain design and documentation standards. VHDL emerges as the language, and is made a requirement for all Air Force designs.

late-1980's: IEEE VHDL (STD 1076)

As a part of the VHSIC programme, large vendors such as IBM and Texas Instruments take an interest in VHDL. That interest, coupled with the growing need for an industry standard HDL, causes VHDL to go through the IEEE standardisation process and emerge as the language in use today.

# 1.4 Application Areas

Since its introduction, the use of VHDL has spread to many areas of digital design. While most of these applications deal directly with design itself, there has also been recent interest in synthesis directly from VHDL. The language in its current state is not generally amenable to this task, but it is anticipated that modifications to the standard (VHDL'92) will overcome many of these problems. A number of commercial CAD vendors now support the language, and its use has spread from being a military systems language to one used and supported by a wide variety of design houses.

# 1.5 Evaluation of VHDL Programs

Given that a large part of the work to be presented is centred around the formalisation of the VHDL simulation loop, an informal description of the workings

of that loop and its associated parts is in order. It should however be noted that the discussion of VHDL which follows is rudimentary, and some familiarity with the language is assumed. The first step is to introduce a few definitions:

**Signal:** The name given to a communication channel in VHDL. For purposes of the presentation here, a signal is a wire.

Event: A change in the value of a signal

**Transaction:** The value that a signal should have at a particular time in the future. A transaction may (or may not) be converted into an event at that time.

**Point of Computation:** The point at which a particular collection of transactions is processed.

**Process:** A VHDL concurrent statement equipped with a set of signal names called a sensitivity list guarding its activation.

**Simulation Cycle:** The evaluation of all the processes in a VHDL program text at a particular point of computation.

**Simulation Loop:** Moving from point of computation to point of computation executing simulation cycles.

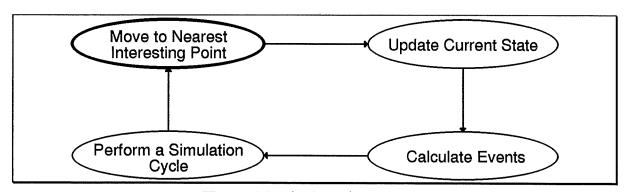

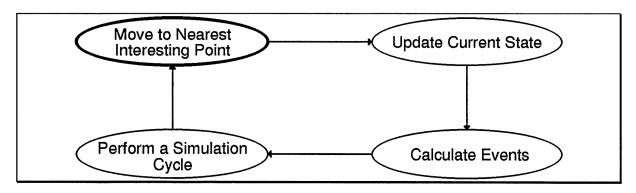

The top-level simulation loop of VHDL may be viewed as a four step sequence, and is illustrated in Figure 1.1. An iteration of the loop starts by moving forward to the nearest interesting point of computation (i.e. one where there are transactions to process), and setting the current simulation time, expressed as a natural number, to be the physical time unit associated with that point of computation. The state of the signal values is then modified to reflect those that they are supposed to take on during the present point of computation. Note that signals must have unique values in any given state. Those signals for which the update represents a change in value are then tagged as events, and a simulation cycle is performed making use of the new information. The loop is repeated until there are no more events or transactions to process, at which stage the simulation is said to have *quiesced*.

Figure 1.1: The Simulation Loop

The graphical description just presented may be summarised by the following pseudo-code description of the simulation loop:

while transactions remain to be processed

- 1. go to the nearest point of computation with transactions to process

- 2. update the state from the current transactions

- 3. determine which updates represent events

- 4. perform a simulation cycle based on the new state and events end while

Emphasis should be placed on the use of the phrase "point of computation" in the above description. While one could often equate a point of computation with a time slice, it is frequently more than that within the context of the particular simulation model of VHDL. One could, for instance, say that the points of computation  $P_1$  through  $P_n$  represent the time units 1 through  $P_n$ . Alternatively, they could represent 1 through  $P_n$  0-length delays between two major time units.

The concept of  $\delta$ -delay is the way in which VHDL deals with these 0-length delays. They result from 0-delay signal assignments. A static state of the world is being used during each iteration through the simulation loop, and transactions are being scheduled to occur at some future point of computation whenever a signal assignment is encountered. This scheduling applies to any transaction, whether it is to occur at a delay offset zero units from now, or at some larger one. Each time around the simulation loop (Figure 1.1) in zero time is called a  $\delta$ -delay. An individual  $\delta$  step does *not*, therefore, represent a quantifiable unit of time. Rather it is simply a simulator artefact that ensures consistency in the ordering of events.

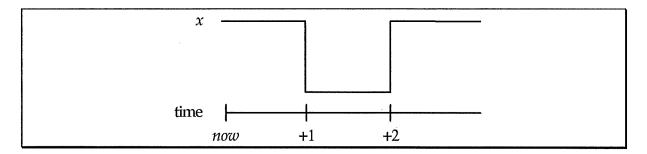

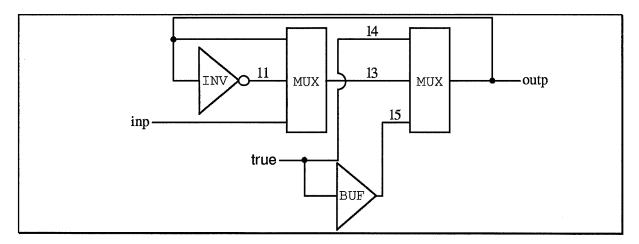

As mentioned earlier, a component of the simulation loop is the performance of a "simulation cycle". The execution of such a cycle is illustrated in Figure 1.2. Each cycle begins with the activation of those processes that are sensitive to any of the current events. All the active processes are then run in parallel, each taking a copy of the static simulation environment with it. During its execution, each process may schedule transactions to be processed in the future. When all the processes have terminated, the futures that have been calculated by the individual processes are gathered together into an amalgamated view of future behaviour.

Figure 1.2: Progression of a simulation cycle

The above steps are again more concisely stated as:

- determine which processes are active based on current events

- run the active processes in parallel

- merge all processes' scheduled transactions into a collective whole

#### 1.6 Formalisation

6

The above informal description of the simulation model of VHDL has been translated into an operational semantics and embedded in a mechanical proof assistant. Due to the size of the language and a desire to emphasise the workings of the simulation model of VHDL, a subset has been chosen. In following this course of action, it has not only been possible to prove theorems about individual program texts, but also to demonstrate properties of the semantics itself that increase one's confidence in it. Some of these theorems will be presented in later chapters, and were developed with the aid of the HOL proof assistant. Because of their mechanical nature the proofs of these theorems are not readily understandable, and are therefore not given in the text. Where necessary, a proof sketch will be given to argue for the correctness of the result. The scripts that were used to prove the theorems are presented in Appendix A.

Operational semantics, as the name implies, allows for the specification of and reasoning about dynamic systems. Specifically, it makes it possible for one to define an abstract representation of an interpreter for a particular language. Given the interpreter, it is not only possible to reason about individual programs, but also infer properties for groups of similar programs. In the context of a semantics for VHDL, an operational framework makes for an easier correspondence between the informal and formal descriptions of the simulation model of the language.

#### 1.7 Automation

Once defined, the syntax and semantics of the VHDL subset is embedded in the proof assistant. In order to make use of the embedding a suite of proof tools was developed to animate the semantics via proof. In essence, this leads to a very slow simulator for the subset.

This simulator itself is not, however, a typical VHDL simulator. Certainly, one may use it to execute programs containing concrete values for signals. The difference lies in the fact that one may also use it to perform simulations with symbolic values for these same signals. In that case, the execution of the simulation

model is providing information on the behaviour of a program over all values. A discussion of the proof assistant and the embedding appears in Chapter 5.

## 1.8 Examples

By embedding the semantics in a proof assistant, it has been possible to explore more fully the relationships between VHDL programs. This exploration has led to a way of combining symbolic simulation with proof to give stronger assurances than is usually possible in a pure simulation environment about the equivalence of designs. While large designs are impractical to analyse at present in the described manner, the methodology still gives useful insight into the workings of the VHDL simulation engine.

The examples themselves are presented as a series of case studies in Chapter 6. They range in complexity from the analysis of a simple NAND gate to a parity-checking device. In each of the case studies, the following pattern is used:

- 1. Specify a high-level (i.e. algorithmic) representation of the device.

- 2. Derive, using the semantics, a general behaviour for the specification.

- 3. Specify a low-level implementation of the device.

- 4. Derive a general behaviour for the implementation in the same fashion as 2.

- 5. Prove that the two behaviours are the same.

Why perform several examples of exactly the same form? The answer lies in the points that each raises about the simulation model and the kind of results one can expect from it. The issues range from how  $\delta$ -steps are resolved to compromises that must be made in order to get a meaningful result from the embedded semantics.

# 1.9 Accomplishments

The work in the chapters that follow represents research in establishing a formal semantics for a subset of VHDL. The semantics is useful in and of itself as an unambiguous specification of the language. Furthermore, the semantics has been embedded in a mechanical proof assistant to provide insight into how it might be used in reasoning about VHDL designs. This reasoning will be seen as a change from traditional simulation in that it moves the examination of programs from validation based on concrete inputs to verification based more general, symbolic ones.

## **CHAPTER 2**

#### **RELATED WORK**

Efforts at applying formal methods to VHDL programming fall into two categories. The first deals strictly with increased support for simulation-time validation of programs. The second pertains to the search for and use of a tractable semantics for a reasonable subset of the language. The rest of this chapter presents a broad overview of these approaches.

#### 2.1 Simulation-Time Validation

The late 1980's was a period of great activity in research surrounding the development of simulation-based validation tools. This particular type of system was meant to provide the designer with additional assurance that a given program was behaving in the intended way through clever use of the simulator itself. Because it followed shortly after the introduction of VHDL as a standard in the United States, the research into these methods was carried out there.

One of these investigations led to the development of the VHDL Annotation Language (VAL) at Stanford [4,5]. VAL allowed the user to decorate a program with specifications about its operation. These annotations appeared as comments in the VHDL program text, and were expanded by a pre-processor before the program was compiled and simulated. When the program was executed, the annotations triggered warning messages if the design differed in its execution from the implicit specification that they provided. This particular methodology was not only a way of getting more useful information out of a simulation, but also made it easy for clear specifications of the behaviour of various parts of a design to be embedded in program texts.

Another early project, conducted by the author, attempted to automatically generate VHDL assertions characterising the behaviour of programs [36,37]. The philosophy was much the same as in the VAL effort. The difference was that it was based on automatically ascertaining the characteristic statement of behaviour for a

10 RELATED WORK

particular program. These assertions could then be embedded in the text of the program for use during simulation in much the same way as VAL specifications. The notion was that once the behaviour of the canonical version of a device had been agreed upon, a statement describing its behaviour could be extracted automatically and embedded in any other program purporting to be the same device. Any exception raised during simulation would therefore indicate some divergence from the accepted norm which needed to be investigated.

Both these projects were based on the respective researcher's interpretation of the semantics of VHDL. No formal statement about the semantics of the language was available at the time beyond that given in the Language Reference Manual. Furthermore, they relied on traditional simulation practice. While this was not a bad thing in that it brought a degree of rigour to the examination of the simulation model of VHDL, these research efforts did not result in any definitive mathematical statement about the semantics of the language.

#### 2.2 Semantics-Based Verification

More recent research has been directed at the verification, rather than validation, of VHDL programs. To accomplish their goals, all the projects involved in this area have necessarily had to build up a formal notion of the semantics of VHDL. The research efforts currently under way vary not only in their approaches to the particular problem of semantics, but also in their implementation of it. Furthermore, they are characteristic of emerging international interest in the field. One camp bases their approach on primarily denotational methods. The other is grounded in a more dynamic intuition.

#### 2.2.1 Denotational Work

Early work in discerning a semantics for signal attributes emerged from IMAG in Grenoble [33]. The emphasis was to statically understand the simulation behaviour associated with the attributes of individual signals. The work eventually led to a prototype system for reasoning about a subset of VHDL similar to that chosen here. A drawback was that because of its insistence on a unit-time model, 0-delay signal assignments could pose problems in the framework.

Promising early work on a full denotational description of the VHDL simulation kernel is underway at the University of Cincinnati [16]. The research is again based upon a small subset of VHDL that is not dissimilar to that presented

here. The work in Cincinnati has lead to the development of valuation functions for initialisation and state transformation during a simulation. There have, however, been no proofs of properties of the semantics to emerge from the effort as of yet.

# 2.2.2 Operational Work

Research closer in flavour to that presented here is underway at several sites. These projects focus on an operational formalisation of what is specified in the Language Reference Manual. Even within this unanimity of spirit, the approaches differ in practice. One type of formalisation is based on extra-logical manipulation of the semantics which passes the results to a proof assistant for additional manipulation. The other does all the work in whatever logical system has been chosen.

#### Use of an Oracle

Research at Siemens [35] is characteristic of the first approach. The simulation model of VHDL is written in the functional language ML. The results of working with a program inside this specification of the simulator are then passed to the LAMBDA is a proof assistant from Abstract LAMBDA system for reasoning. Hardware, Ltd. that is based on the same logic as the system used here. difference is that it has been specially tailored for reasoning about hardware. In essence, the ML program is being used as an oracle providing a statement of behaviour for the theorem-prover to use in subsequent proofs. The goal of the Siemens project has been to provide an industrial-strength tool, and the subset of the language is therefore very large. The approach chosen, while not strictly formal in that the semantics of the language is specified by an interpreter written in a functional language rather than securely inside the logic of LAMBDA, has merits in that it provides an efficient environment for working with VHDL programs. The limitation is that one must be convinced of the correctness of the external oracle before trusting any results that arise from it and the subsequent proof process.

## **Secure Formalisations**

The other approach, namely that of modelling the semantics of VHDL inside the mechanisation of the particular logical system being used, is much closer in flavour to the work that follows in later chapters. The important difference between it and the material summarised here is that the formalisations are expressed in (and are

12 RELATED WORK

therefore perhaps limited by) the particular logic of the given proof environment. The research presented in this document makes use of a semantics that has been developed in an accepted semantic formalism without regard as to how it is to be mechanised. The generality of the target proof environment then allows one to seamlessly embed the semantics to reason not only about it but VHDL programs as well.

The most substantial piece of work in this field is the result of research at the Aerospace Corporation. The semantics of the simulation kernel have been implemented in the State Delta Verification System. SDVS is a framework for describing the execution of individual program steps based on the way that they affect the overall state in which the program executes [1]. The subset implemented is also large [17]. The idea is much the same as in the Siemens project (i.e. develop the meaning of a particular program based on a specification of the simulation model and then reason about it). Again, the contrast here is that the work is being carried out without recourse to an external oracle. The problem is not therefore in trusting both the oracle and the interface between two systems, but in gaining confidence in the formal specification of the VHDL simulation kernel.

Other similar research is just beginning at Computational Logic, Inc. [39]. The idea is much the same as in the Aerospace project. The system will be implemented in the Boyer-Moore logic [11] as realised in the NQTHM theorem-prover [12]. The Boyer-Moore system differs from both SDVS and the proof development environment that will be used later in that it is a much more automatic system, requiring less user intervention.

# 2.2.3 Other Approaches

Research into verification environments for VHDL is not limited to those methodologies given in Sections 2.2.1 and 2.2.2. Other projects make use of either custom-designed or existing formal languages for their implementations. One is underway at Royal Holloway and Bedford New College where a language called FUNNEL is being developed [34]. The language is intended as a descriptive medium for many different hardware description languages, and therefore provide a framework for reasoning about designs irrespective of the language in which they were specified. Another approach is being taken at IRISA [7] using the language SIGNAL to describe the simulation kernel of VHDL and to rationalise its timing model.

#### **CHAPTER 3**

## STATIC SEMANTICS

Before embarking on a formal discussion of the way VHDL simulates, the subset of the language that will be addressed needs to be identified. Furthermore, it will be necessary to define a way of checking that particular programs written in that subset are properly constructed. The exposition that follows begins by introducing the syntax of the subset and informally discussing the kind of restrictions that have been placed upon it. The chapter concludes with a suite of definitions that formalise the restrictions about the well-formedness of VHDL programs written in the subset.

#### 3.1 Femto-VHDL

VHDL is a language that can best be thought of as one whose execution is based upon that of concurrent blocks. The most basic of these is the process statement. Each block contains sequential statements that describe the algorithm that it is supposed to be implementing. To a large extent, these sequential statements are exactly those of sequential Ada<sup>1</sup>. Only one particular class of sequential statements, signal assignments, is essential for driving the simulation. The emphasis in the definition of the subset will therefore be to highlight these two important types of statement (processes and signal assignments), and to provide enough other syntactic machinery to ensure that the semantics fully exercises them.

The VHDL subset for which a semantics has been defined is therefore rather small. Its name is derived from the smallest user-addressable unit of time in full VHDL – the femtosecond. Femto-VHDL does, however, contain enough constructs of the full language to illustrate the important features of the simulation model. As just discussed, only one kind of VHDL concurrent statement is supported, namely process statements. These are further restricted to those equipped with explicit sensitivity lists of signal names, which can be thought of as guards on their

<sup>&</sup>lt;sup>1</sup>Ada is a registered trademark of the U.S. Government – Ada Joint Program Office.

activation. The sequential statements addressed are the if-then-else conditional, as well as inertial and transport delay signal assignments. Architectural hierarchies allow the user to group concurrent statements into large blocks with specific inputs and outputs. When simulated, these hierarchies will be flattened out into a sea of concurrent processes. For purposes of the subset, the architectures here are limited to those without VHDL generic [21] statements. Furthermore, the following assumptions are made:

- Signals may only be Boolean-valued. This is for simplicity, and does not materially affect the exposition of the simulation model.

- Resolved (multiply driven) signals are not allowed. The implication is that constructs such as wired-and's and wired-or's are not permitted.

Why these particular assumptions? The first one is understandable in that assignment to Boolean-valued signals is the same as assignment to signals of any other value. The focus here is on the act of assignment, not on the type of the assigned-to signal. The second assumption is a bit more cryptic. In essence, it ensures that no signal may be assigned to from more than one process statement. If this was allowed, two active processes might try to assign to the same signal at the same time causing a clash over which value that signal should take on. Full VHDL provides a way of dealing with this eventuality through the use of user-defined resolution functions [21]. In an effort to keep the discussion of the simulation model simple, these particular types of actions have been dis-allowed. As will be seen in Chapter 4, it is possible to add resolved signals to the semantics, but an extension is required.

Given the above listing of supported statements and assumptions, one can ask what physically constitutes a Femto-VHDL program. At the outermost level, a program text again is made up of one or more architectural components. Each component is comprised of either one or more concurrent statements, or the nesting of more components. The concurrent statements in turn contain sequential statements. The following abstract syntax for Boolean expressions, sequential statements and concurrent statements in Femto-VHDL may be given:

```

bexp ::= signal \mid signal ' delayed(n) \mid signal ' event \mid not \ bexp \mid bexp \ and \ bexp \mid bexp \ or \ bexp \ nand \ bexp \mid bexp \ nand \ bexp \mid true \mid false

ss ::= ss ; ss \mid null \mid bexp \Rightarrow ss \mid ss \mid string := (bexp,n) \mid signal := (bexp,n)

cs ::= cs \mid cs \mid sl : ss

sl ::= \{s_1, ..., s_n\}

```

The symbol *bexp* ranges over Femto-VHDL Boolean expressions. These are made up of single signal names, attributed signals ('event and 'delayed), or compound expressions using the various VHDL Boolean operators. Attributes allow the user to access properties of signals. The ones in Femto-VHDL are used for ascertaining whether or not a signal has an event on it now ('event) and for looking at the value of a signal delayed by *n* units of time expressed as a natural number ('delayed). Sequential statements (*ss*) may be either two statements in sequence (;), a null statement, a conditional statement guarded by some Boolean expression, an inertial delay signal assignment statement, or a transport delay signal assignment statement. Each type of signal assignment statement maps a Boolean value to a signal after some delay also expressed in terms of the naturals. Concurrent statements (*cs*) are either two such statements in parallel, or a single process statement made up of a sensitivity list and some sequential statements. Sensitivity lists (*sl*) are simply sets of signal names.

The overall structure of design hierarchies is expressed as:

```

\begin{array}{ll} design ::= & \text{arch } string_e \ string_a \ ports \ decls \ cs \mid \text{dpar } design \ design \\ decls \ ::= & \text{signal } \{s_1, \ldots, s_n\} \end{array}

```

Local signal declarations may be made (*decls*), and do not have associated directions. Ports (*ports*) are the external interfaces for VHDL architectures. They have associated directions, and are represented in Femto-VHDL, by a triple of sets. Signals of direction in (inputs) are in the first part of the triple, out signals (outputs) are in the second part and inout signals (bi-directionals) are in the final part. A design is composed of either a stand-alone component or a nested hierarchy of them. It should be noted that neither || nor dpar have any corresponding construct in the concrete syntax of VHDL. They are given here simply as a means of grouping together language constructs.

VHDL components may be specified at different levels of abstraction. To this end, the concept of design *entity* and design *architecture* are available to the designer. An entity is nothing more than a specification of connections to the outside world via ports. For purposes of Femto-VHDL, an architecture groups together concurrent statements that express the behaviour of a particular component (e.g. an ALU). Two particular architectures may actually represent the same component at different levels of abstraction. In that case the architectures are really part of the same entity, as they make use of the same ports to plug into the outside world irrespective of their internal construction. The two strings *string*<sub>e</sub> and *string*<sub>a</sub> in the **arch** part of the

definition of *design*, represent the name of the entity and the name of the architecture respectively. It is therefore entirely possible for individual components to have the same entity name, but different architecture names.

The following tables give the relationship between the abstract syntax and the concrete syntax for various syntactic classes of Femto-VHDL. No mapping will be shown for Boolean expressions, as the abstract and concrete syntaxes are the same. For reasons of brevity the abstract syntax will be used in describing the semantics of Femto-VHDL.

| design                                                      |                                                                                                                                                |  |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| arch string <sub>e</sub> string <sub>a</sub> ports decls cs | entity $string_e$ is port $ports$ ; end $string_e$ ; architecture $string_a$ of $string_e$ is signal $s_1,, s_n$ ; begin $cs$ end $string_a$ ; |  |

|                           | CS                           |  |

|---------------------------|------------------------------|--|

| $\{S_1,\ldots,S_n\}$ : SS | process $(S_1, \ldots, S_n)$ |  |

|                           | begin                        |  |

|                           | SS                           |  |

|                           | end process;                 |  |

|                      | SS                                                   |

|----------------------|------------------------------------------------------|

| signal := (bexp, n)  | $signal \leftarrow bexp after n;$                    |

| signal := (bexp, n)  | $signal \leftarrow transport bexp after n;$          |

| null                 | null;                                                |

| $bexp => ss \mid ss$ | if <i>bexp</i> then <i>ss</i> else <i>ss</i> end if; |

# 3.2 Definitional Style

When defining functions and relations associated with the semantics, recourse will be made to the following definitional style. The symbol  $\equiv$  indicates a definition. The function name, when first defined, will appear in **bold sans serif** typeface. Variables will be shown in *math italic*. Internal functions and variables will be defined using let ... (and ...) in constructions. As an example, the function foo may defined as:

```

foo x \equiv

let a = x + 1 and b = x - 1 in

let c = a + b in

(x,c)

```

The function takes a natural number as its argument and returns a pair of naturals. The nesting of let-expressions allows for the calculation of c. Scoping is such that a and b are not visible to one another, but are visible in the second let-expression when c is formed. If one expanded the first let-expression, the result would be:

```

foo x \equiv

let c = (x+1)+(x-1) in

(x,c)

```

Use will also be made of the form if x then ... (elseif y then ...) else ... to express conditionals. Lists will be required in some of the definitions that come later, and list processing functions such as hd (head), tl (tail) and . (cons) will therefore be needed as well. Finally, it will be necessary to make use of tuples in some definitions, and the functions fst and snd will be used to respectively access the first and second elements of them.

## 3.3 Syntactic Well-Formedness

What constitutes a syntactically valid Femto-VHDL program? First, output signals must not have multiple drivers. This means that a signal must not be assigned to from more than one source. Next, the signals used in the program text must be only those that happen to be declared as ports or as local signal declarations. Finally, those signals must also be assigned to in an appropriate manner (i.e. signals of direction in must not be driven, and signals of direction out must not be read). The rest of the chapter involves a series of definitions leading up to the function well\_formed\_design which encompasses these properties. Readers not interested in the details of these definitions may safely progress to Chapter 4.

# 3.3.1 Multiple Drivers

To check the multiple driver condition, it is necessary to determine that a given signal name appears on the left-hand side of the signal assignments of only one process in the program text. In other words, if the set of assigned-to signal names for one process of the design has a non-empty intersection with a similarly derived

set for any other process in the design, the program text is not well-formed. At the lowest level of this check, one needs to extract a set of signal names that are assigned a value in the statements of a given process. Having done so, the requirement is then to make sure that these signals are not being assigned to in any other process.

As the first step in the check, one defines the function well\_formed\_Femto\_ss over the structure of sequential statements:

```

well_formed_Femto_ss ss \equiv

if (ss = ss'; ss'') \lor (ss = e \Rightarrow ss' \mid ss'') then

(well_formed_Femto_ss ss') \cup (well_formed_Femto_ss ss'')

elseif \left(ss = s := (e, dly)\right) \lor \left(ss = s := (e, dly)\right) then \{s\}

else \{\}

```

The function returns, as a set, the signal names that appear on the left-hand side of any assignment statement. For instance, well\_formed\_Femto\_ss would return the set  $\{a,b\}$  if given the conditional statement  $e \Rightarrow a := (x,2) \mid b := (y,0)$ .

Use may now be made of well\_formed\_Femto\_ss in gathering together a collection of assigned-to signals for all the processes in a given architecture. The function well\_formed\_Femto\_cs, again defined recursively on structure, does just that. It returns a tuple of sets. The first element of the pair represents the intersection that is of interest, while the second is the set of all assigned-to signals.

```

well_formed_Femto_cs cs \equiv

if cs = (sl : ss) then ({}, well_formed_Femto_ss ss)

else let (cs' || cs'') = cs in

let a = \text{snd}(\text{well_formed_Femto_cs } cs')

and b = \text{snd}(\text{well_formed_Femto_cs } cs'') in

(a \cap b, a \cup b)

```

If the two processes  $\{x\}: a := (x,2) || \{y\}: b := (y,0)$  were used as an example, the function would return the pair  $(\{\},\{a,b\})$ . However, had both signal assignments been addressing signal a, the resulting pair would have been  $(\{a\},\{a\})$ .

Having defined the two previous functions, all that remains to be done is ascertain the emptiness of the first element of the pair returned by well\_formed\_Femto\_cs. The function wfF\_csss is defined as a top-level interface, and makes the desired comparison:

```

wfF_csss cs = (fst(well\_formed\_Femto\_cs cs) = {})

```

If the just-used concurrent statements were passed as arguments to wfF\_csss, it is clear from the above results that an invocation on the processes which assign to both a and b would fulfil the multiple driver restriction, while one where both processes address the signal a would not.

In order to make use of wfF\_csss for larger components, it will be necessary to flatten out architectural hierarchies into a sea of processes. To this end, the function dflat has been defined. The function takes one or more Femto-VHDL components, and returns only the processes associated with each one. In the case of multiple architectures, the processes of each are glued together in parallel.

```

dflat design \equiv

if design = arch ent arch ports decls cs then cs

else let (dpar d' d'') = design in (dflat d') || (dflat d'')

```

For instance, the design dpar (arch e' a' p' d' cs') (arch e'' a'' p'' d'' cs'') would, when passed through dflat, be reduced to  $cs' \parallel cs''$ .

# 3.3.2 Signal Relationships

The other restrictions on the syntactic well-formedness of Femto-VHDL programs hinge heavily on the interrelationships of the signals as they are found in individual components. In order to make any statement about those relationships, it will first be necessary to extract the necessary signals from a program text. Having done so, it is then possible to go on to make a definition of what is required of those signals in the overall design.

# **Signal Extraction**

When dealing with Femto-VHDL designs, two kinds of signals are of interest. One group is the external ports. The other is the locally declared signals. The function get\_sigs\_decls accesses the set of locally declared signals in a stand-alone component.

```

get\_sigs\_decls (signal sigs) \equiv sigs

```

For instance, if the function were applied to the declarations of  $\operatorname{arch} e \ a \ p$  (signal d) cs, it would return the set d. The ports of a design may be extracted with  $\operatorname{get\_ports}$ . The function is defined recursively over the structure of designs in an analogous manner to dflat.

```

get_ports design \equiv

if design =arch ent \ arch \ ports \ decls \ cs then

(fst ports) \cup (fst (snd ports)) \cup (snd (snd ports))

else let (dpar d' \ d'') = design in (get_ports d') \cup (get_ports d'')

```

The whole idea of the function is to remove any reference to directionality, and return as a set only the names of the ports of a particular design.

The above functions extract the declared signals in a design. However, in order to make the kind of checks that are necessary, functions that return the signals that are actually used in the concurrent statements of a design are also required. A series of functions that extract these signals, paying particular attention to their intended direction, are now defined.

At the lowest level, the signals will need to be returned from Boolean expressions. Because these expressions are only capable of holding input signals (i.e. they are always read, but never written to), all that is required in get\_sigs\_bool is to gather together any signal names found in a Boolean expression, and return them as a set.

Sequential statements contain both input and output signals. The only output signals are those on the left-hand side of signal assignment statements. All other signals are assumed to be inputs. The function get\_sigs\_ss returns a pair of sets, the first of which is the set of input signals (including those found in any Boolean expressions), while the second is the set of output signals.

```

get_sigs_ss ss =

if (ss = ss'; ss'') \lor (ss = e \Rightarrow ss' \mid ss'') then

let (is', os') = \text{get}_sigs_ss ss' and (is'', os'') = \text{get}_sigs_ss ss''

and bools = \text{if } (ss = e \Rightarrow ss' \mid ss'') then \text{get}_sigs_bool } e \text{ else } \{\} in

(is' \cup is'' \cup bools, os' \cup os'')

elseif \left(ss = s := (e, dly)\right) \lor \left(ss = s := (e, dly)\right) then \left(\text{get}_sigs_bool } e, \{s\}\right)

else \left(\{\}, \{\}\right)

```

Finally, it is necessary to traverse an entire sea of concurrent processes gathering the same information. The function get\_sigs\_cs does this, and returns a pair of sets of the same form as those created by get\_sigs\_ss.

```

get_sigs_cs cs \equiv

if cs = (sl : ss) then get_sigs_ss ss

else let (cs' || cs'') = cs in

let (is', os') = \text{get}_sigs_cs cs' and (is'', os'') = \text{get}_sigs_cs cs'' in

(is' \cup is'', os' \cup os'')

```

As an example of the behaviour of this suite of functions, take the Femto-VHDL processes:

```

\{x\}: a := (\text{not } x, 2) || \{y'\}: b := (y' \text{ and } y'', 0) || \{z\}: c := (z, 0)

```

When get\_sigs\_cs is run over them, the pair  $(\{a,b,c\},\{x,y',y'',z\})$  is returned.

A companion function to get\_sigs\_cs is get\_sigs\_design. It extracts all the signal names from a design without regard for their associated direction by making use of get\_sigs\_cs.

In a similar fashion to the previous example, the architectures

```

dpar \left( \begin{array}{l} \operatorname{arch} e' \ a' \ p' \ d' \left( \{x\} : a := (\operatorname{not} x, 2) \right) \\ \operatorname{dpar} \left( \begin{array}{l} \operatorname{arch} e'' \ a'' \ p''' \ d'' \left( \{y'\} : b := (y' \ \operatorname{and} \ y'', 0) \right) \\ \operatorname{arch} e''' \ a''' \ p''' \ d''' \left( \{z\} : c := (z, 0) \right) \end{array} \right) \right)

```

would yield the single set  $\{a, b, c, x, y', y'', z\}$  when put through get\_sigs\_design.

## Well-Formedness of Design Signals

In order to ensure the well-formedness of the signals in a Femto-VHDL program, the various constraints on signals mentioned earlier must be met. To reiterate, they were:

- Only declared signals may be used in the program text.

- Directionality of assignments must be preserved.

The function well\_formed\_design\_sigs uses the just defined functions to express these goals for the well-formedness of the signals in a Femto-VHDL design.

```

well_formed_design_sigs design \equiv

if design = arch \ ent \ arch \ ports \ decls \ cs then

let ip = fst \ ports and op = fst \ (snd \ ports) and op = snd \ (snd \ ports)

and (isigcs, osigcs) = get\_sigs\_cs \ cs and d = get\_sigs\_decls \ decls in

let p = (ip \cup op \cup iop) and sigcs = (isigcs \cup osigcs) in

let pId = (p \cap d = \{\}) and oIi = (op \cap isigcs = \{\}) and iIo = (ip \cap osigcs = \{\}) in

(sigcs = p \cup d) \land pId \land oIi \land iIo

else

let (dpar \ d' \ d'') = design in

let (P', S') = well\_formed\_design\_sigs \ d''

and (P'', S'') = well\_formed\_design\_sigs \ d'' in

(P' \land P'')

```

In the case of stand-alone components, ip are the in ports, op are the out ports and iop are the inout ports. isigs represents the signals that are used as inputs in the concurrent statements of the component, whilst osigs are those used as outputs. d are the locally declared signals. The variable p holds all the ports, and sigcs contains all the signals of the concurrent statements. pId states that the ports and locally declared signals must be disjoint, oIi says that the output ports must not be used as inputs, and iIo ensures that input ports are not being used as outputs. Conjoining these last three with the statement that the ports of the component are the same as the signals used by the concurrent statements ensures that the all the signals of that component are well-formed.

A useful consequence of the definition of well\_formed\_design\_sigs when reasoning about the dynamic semantics of Femto-VHDL in Chapter 4, will be the knowledge that if the signals in a design display the proper interrelationships, then the ports of the design are a subset of all the signals in that design.

#### Theorem 3.3.2.1:

$\forall dsgn.$  (well\_formed\_design\_sigs dsgn)  $\supset$  (get\_ports  $dsgn \subseteq get_sigs_design <math>dsgn$ )

The proof was performed in the theorem prover by induction on the structure of designs. This proof, because of its mechanical nature, is not given here; but the argument is fairly straightforward. The interested reader is referred to Appendix A for the actual proof script. The base case follows from an expansion of the definition of well\_formed\_design\_sigs. Once done, one observes that the ports and declarations of the component must be the same as the signals of its concurrent statements (derived by get\_sigs\_cs). This of course means that the ports are a subset of the total signals. The induction step is also a based on a straightforward expansion of definitions. Once those of well\_formed\_design\_sigs, get\_ports and get\_sigs\_design have been applied to composite designs one arrives at an instance of the induction hypothesis.

#### 3.3.3 Overall Well-Formedness

It is now possible to make an overall definition about the syntactic well-formedness of any Femto-VHDL design. Simply stated, the signals of the design must exhibit the appropriate relationships, and the concurrent statements must not contain multiply driven signals. These requirements are formally defined in the function well\_formed\_design:

```

well_formed_design design \equiv (well_formed_design_sigs design) \land (wfF\_csss (dflat <math>design)))

```

A simple fact arising from the definition of well\_formed\_design is:

```

Theorem 3.3.3.1: \forall design. well_formed_design_sigs design

```

The intuition for the proof is to assume well\_formed\_design design, expand the definition and take the first conjunct.

## **CHAPTER 4**

## **DYNAMIC SEMANTICS**

The only official specification of the meaning of VHDL is the Language Reference Manual. It describes the semantics of the language in an informal manner through recourse to terms such as "elaboration" and "execution". These are words that implicitly lead to a formulation of meaning in terms of simulation. The material that follows is a formalisation of the semantics of Femto-VHDL that reflects this dynamic intuition. The discussion will begin by presenting a short overview of operational semantics, and will continue with a presentation of how information will be structured in the semantics. The definitions concerning the well-formedness and equivalence of some of those structures will then follow. The chapter will conclude with the definitions and rules that make up the semantics of the language.

# 4.1 Operational Semantics

The semantics of Femto-VHDL will be given in an operational manner [32]. As alluded to earlier, operational semantics it is a formalism that allows for the specification of and reasoning about dynamic systems. Since VHDL is defined even in the informal context of [21] by means of the simulation process, the idea of using this particular semantic approach is intuitively appealing. In order to define the semantics in an operational way, it will be essential to understand a special form of definition. An example taken from [20] is perhaps the easiest way of coming to grips with what is required.

#### 4.1.1 Inductive Definitions

If one rephrases mathematical induction as a more generally applicable form of induction, the set N of natural numbers satisfies the following conditions (or rules):

- 0 ∈ N

- if  $x \in N$  then  $x + 1 \in N$

Many other sets also have these properties. Examples are the set of integers (positive and negative), the set of rational numbers and the set of real numbers. However, these properties have special significance for N; N is the *least* set which has both these properties. This means that if X is any other set with these properties then  $N \subseteq X$ . To prove this one uses mathematical induction to show that  $n \in X$  for every natural number n. More precisely, mathematical induction is employed to show the property P(n) is true for every natural number n where P(x) is defined by:

#### P(x) iff $x \in X$

The base case,  $0 \in X$ , is trivially true because X satisfies the first property. The fact that X satisfies the second property means that the inductive step is also true:  $k \in X$  implies  $k+1 \in X$ . One can therefore conclude that  $n \in X$  for every natural number n, i.e.  $N \subseteq X$ . In general many sets, relations, etc. will be defined as the least ones satisfying a set of conditions or rules. Each such definition gives rise to a form of induction, called *Rule induction*, for proving properties of the sets, relations, etc. For this reason these are called *inductive definitions*.

#### 4.1.2 Inductive Definitions and Femto-VHDL

The definitions that will be used in the semantics of Femto-VHDL are made up of sets of rules expressed as conditionals:

#### if premises then conclusion

Where the premises may take on one of two forms, those associated with the relation being defined and other truths which must be known. These other truths are known as *side conditions*. When writing the rules of the semantics, the following form will be used:

# <u>premises</u> side conditions

Any rule without premises is known as an axiom.

The form that each of the premises and the conclusion will take on in the rules is:

$$env \vdash a \xrightarrow{eval} b$$

which should be read, "a evaluates to b in the environment env using the relation  $\xrightarrow{eval}$ ." The environment is the static state of the evaluation (i.e. the current time, the state of the signals, etc.). The turnstile (+) separates the environment from the operation of evaluation from a into b.

## 4.2 Information Organisation

The information needed to make the semantics work is really very simple. The way it is presented here was conceived to correspond to the intuition of VHDL users about the structuring of information in VHDL itself. Much use will be made of set notation in what follows.

Time will be represented by the natural numbers, values by Booleans, and signal names by strings. Whenever there is an event on signal x, its name will be included in a set of events  $(\gamma)$ . The state of signals  $(\sigma)$  is given as a set of namevalue pairs. Future transactions  $(\tau)$  is a function from time to  $\sigma$ , and will provide the framework for scheduling. The trace of past behaviour  $(\theta)$ , which is necessary for proper interpretation of attributed signals, is also a function on time, but maps it to a  $\gamma$ - $\sigma$  pair. The environment in which an individual simulation cycle runs  $(\rho)$  holds the current time,  $\sigma$ ,  $\gamma$ , and  $\theta$ . The overall simulation environment  $(\mu)$  augments  $\rho$  with an ordered list of times representing the delays associated with the signal assignments of the Femto-VHDL program in question.

time = N value = Boolean name = string

$$\gamma = (\text{name}) \text{set} \quad \sigma = (\text{name} \times \text{value}) \text{set} \quad \tau = \text{time} \rightarrow \sigma \quad \theta = \text{time} \rightarrow (\gamma \times \sigma)$$

$$\rho = (\text{time} \times \sigma \times \gamma \times \theta) \qquad \qquad \mu = ((\text{time}) \text{list} \times \rho)$$

The delays are added to the overall simulation environment to allow the simulation loop to move forward to the next point of computation. Recall that the loop should progress to the nearest point of computation where there are transactions to process. The way that these transactions are created is through the execution of signal assignment statements. So by gathering together all the delays associated with the signal assignments of a given program into an ordered list, we provide a way of knowing the only reachable offsets from the current time.

## 4.2.1 Delay Extraction

Bearing in mind the usefulness of the just mentioned delays, functions are now defined to extract them from Femto-VHDL programs. Before doing so, two functions that ensure the ordering of lists of delays are given. The first function is list recursive, and adds a new delay to the existing list of delays. It guarantees that any such addition preserves the order of the list.

```

add_one_delay dly dlys \equiv

if nil dlys then [dly]

elseif dly = (hd dlys) then dlys

elseif dly < (hd dlys) then (dly \cdot dlys)

else (hd dlys \cdot add_one_delay delay (tl dlys))

```

The next function is also list recursive, and merges together two lists of delays. Use is made of add\_one\_delay to preserve the ordering. merge\_delays is really doing nothing more than a sorted appending operation that deletes duplicate elements.

```

merge_delays dlys' dlys" ≡

if nil dlys' then dlys"

else merge_delays (tl dlys) (add_one_delay (hd dlys') dlys")

```

As an example, merge\_delays [2,5,1][4,5,8] would yield the list [1,2,4,5,8].

Having defined both add\_one\_delay and merge\_delays, the functions that actually extract the delays from Femto-VHDL program texts may be defined. It is assumed that any design hierarchies have been flattened out into a sea of concurrent processes. The first function extracts delays from sequential statements. As anticipated, delays are only to be found on signal assignment statements, and are added to the running list by calls to add\_one\_delay.

```

get_delays_ss ss l \equiv

if (ss = ss'; ss'') \lor (ss = e \Rightarrow ss' \mid ss'') then get_delays_ss ss' (get_delays_ss ss'' l)

elseif \left(ss = s := (e, dly)\right) \lor \left(ss = s := (e, dly)\right) then add_one_delay dly l

else l

```

The second function extracts delays from the collection of parallel processes. Any delays that are found in individual processes through the use of get\_delays\_ss, are merged with those found on any other processes via calls to merge\_delays.

```

get_delays_cs cs \equiv

if cs = (sl : ss) then get_delays_ss ss []

else let (cs' || cs'') = cs in merge_delays (get_delays_cs cs') (get_delays_cs cs'')

```

An example of the use of this suite of functions may be had by taking some example processes used in Chapter 3,

```

\{x\}: a := (\text{not } x, 2) || \{y'\}: b := (y' \text{ and } y'', 0) || \{z\}: c := (z, 0)

```

and running get\_delays\_cs over them to return the list [0,2].

## 4.2.2 Well-Formedness

A well-formed  $\sigma$  has two essential parts. The first being that there are no signal-value pairs that have the same signal name as their first element (i.e. signals have unique values). The second criterion is that if an architecture simulates with a particular  $\sigma$  in its environment, then all the signals in the architecture must have an associated value in that  $\sigma$ . The definition of well\_formed\_ $\sigma$  encapsulates these properties:

```

well_formed_\sigma \sigma design \equivlet sigs = image fst <math>\sigma incard \sigma = card sigs \land\forall sig.(sig \in (get\_sigs\_design design)) \supset \exists val.(sig,val) \in \sigma

```

The function uses card to calculate the cardinality of a finite set (i.e. card  $\{a,b\}=2$  and card  $\{\}=0$ ), and image to extract the set of signal names from the given  $\sigma$  (i.e. image fst  $((x,a),(y,b),(y,c))=\{x,y\}$ ). The first conjunct simply states that the  $\sigma$  in question must have the same number of elements as the set of signal names associated with that  $\sigma$ . The second conjunct stipulates that any signal that is in the set of signal names extracted from the design, must have a value associated with it in  $\sigma$ .

When dealing with the well-formedness of traces of past behaviour ( $\theta$ ), two constraints must be met. Both will apply at any time rather than at specific offsets associated with a particular program. The reason is twofold. First, it makes little intuitive sense to have a past which is only applicable at certain time points. Second, a 'delayed signal attribute may attempt to sample the past at a time offset which is not one of the signal assignment delays. The semantics, particularly the definition of

the top-level simulation loop, will ensure that traces of past behaviour are constructed to contain intervals rather than time points.

The function well\_formed\_ $\theta$  is defined to encapsulate the two requirements on the proper construction of individual  $\theta$ . These constraints apply, as in well\_formed\_ $\sigma$ , with respect to the design that a particular  $\theta$  is associated with. The first of the two constraints is that any signal found as an event in the trace must be one of the signals of the design in question. The second requires that for any time point mentioned, the  $\sigma$  found there must be well-formed.

```

well_formed_\theta \theta design \equiv

\forall t \ sig. (sig \in (fst(\theta t)) ⊃ sig \in (get\_sigs\_design design)) \land

(well_formed_\sigma (snd(\theta t)) design)

```

It will be necessary in later reasoning to know about membership in a trace of past activity based on the well-formedness of that history:

```

Theorem 4.2.2.1: \forall \theta \ dsgn. well_formed_\theta \theta \ dsgn \supset \forall t \ s.s \in \text{get\_sigs\_design} \ dsgn \supset \exists v. \ (s,v) \in \text{snd}(\theta \ t)

```

If one assumes well\_formed\_ $\theta \theta dsgn$ , expand its definition (as well as that of well\_formed\_ $\sigma$ ), reduce the resulting internal let expressions, and take the second conjunct, the required result is obtained after discharging the initial assumption and generalising both  $\theta$  and dsgn.

# 4.2.3 Equivalence

Equivalence for  $\gamma$ ,  $\sigma$ ,  $\tau$  and  $\theta$  is not a straight equality. Rather it is predicated on the user supplying some signals of interest. The reasoning behind this is perhaps best illustrated by example. Assume that one wished to compare the simulation  $\gamma$  associated with architecture A with that for architecture B. Both A and B have the same external ports, but differ in their internally declared signals. Since any comparison of A with B is only meaningful on externally visible signals, it is essential that the internal signals be factored out of each  $\gamma$  before making the equality test on the two sets. So, the relation  $\stackrel{\gamma}{=}$  is defined in the following way:

```

\gamma' = \gamma'' \equiv (\{s : s \in \gamma' \land s \in sigs\} = \{s : s \in \gamma'' \land s \in sigs\})

```

It is an equivalence relation, and obviously exhibits the required properties of reflexivity, symmetry and transitivity. A similar relationship, may be defined for  $\sigma$ :

$$\sigma' = \sigma'' \equiv \left( \left\{ (s, v) : s \in \sigma' \land s \in sigs \right\} = \left\{ (s, v) : s \in \sigma'' \land s \in sigs \right\} \right)$$

Both  $\tau$  and  $\theta$  are a bit more involved when defining equivalence. This is due to the fact that they are functions of time. Therefore, the simple approach taken above must be augmented to check that the sets are the same for all times. For  $\tau$ , the relation  $\stackrel{\tau}{=}$  may is defined as:

$$\tau' = \tau'' \equiv \forall t . \left( \left\{ (s, v) : s \in (\tau' t) \land s \in sigs \right\} = \left\{ (s, v) : s \in (\tau'' t) \land s \in sigs \right\} \right)$$

The definition of a relation on  $\theta$  is much the same. Note that the definition of  $\stackrel{\theta}{=}$  takes both the trace of  $\gamma$  and the trace of  $\sigma$  into account.

$$\theta' = \theta'' \equiv \forall t. \left( \left\{ s : s \in (\text{fst}(\theta' t)) \land s \in sigs \right\} = \left\{ s : s \in (\text{fst}(\theta'' t)) \land s \in sigs \right\} \right) \land$$

$$\left( \left\{ (s, v) : s \in (\text{snd}(\theta' t)) \land s \in sigs \right\} = \left\{ (s, v) : s \in (\text{snd}(\theta'' t)) \land s \in sigs \right\} \right)$$

Later on in the presentation of the semantics it will become necessary to reason about membership of signal value pairs in equivalent  $\tau$ 's. The following complementary theorems will aid in that reasoning. They merely state that if two  $\tau$ 's are know to be equivalent on a set of ports, then given any signal named in those ports which is in one of  $\tau$ 's the same signal-value pair must appear the other one as well.

#### Theorem 4.2.3.1:

$\forall \tau' \tau'' t \text{ sig val ports.}$

$$\left(\left(\tau'\mathop{=}\limits_{ports}^{\tau}\tau''\right)\wedge\left(sig\in ports\right)\wedge\left(sig,val\right)\in\left(\tau't\right)\right)\supset\left(sig,val\right)\in\left(\tau''t\right)$$

#### Theorem 4.2.3.2:

$\forall \tau' \tau'' t \text{ sig val ports.}$

$$\left(\left(\tau' \underset{ports}{\overset{\tau}{=}} \tau''\right) \land \left(sig \in ports\right) \land \left(sig, val\right) \in \left(\tau'' t\right)\right) \supset \left(sig, val\right) \in \left(\tau' t\right)$$

The definition of  $\stackrel{\tau}{=}$  makes it clear that any signal named in *ports* will have the same signal-value pair in both  $\tau'$  and  $\tau''$  at any chosen time. Each of the desired implications is a consequence of this.

#### 4.3 Rules of the Semantics

The rules that define the operational semantics of the Femto-VHDL subset fall under five broad headings – rules for Boolean expressions, rules for sequential statements, rules for concurrent statements (the simulation cycle), rules for initialisation and rules for the top-level simulation loop. The presentation of these rules now follows, beginning with those defining the evaluation of Boolean expressions. Their format is based on the presentation discussed in Section 4.1.2.

## 4.3.1 Rules for Boolean Expressions

The rules that define the semantics of Boolean expressions are numerous, but are conceptually very simple. They are, in essence, describing an evaluator for Boolean expressions. A key component of that evaluation will be the determination of the value of actual signals – a task accomplished by the function valcalc:

**valcalc**  $sig \sigma \equiv choice \{val: (sig, val) \in \sigma\}$

The function calculates the value of a signal sig in a state  $\sigma$ , by making use of the function choice which selects an arbitrary element from a non-empty set. The use of choice is possible in this context because the set from which the choice is made will always be a singleton set. This is due to the fact that signals have unique values in any  $\sigma$  as long as they are well-formed. For example, valcalc  $x\{(y,a),(x,b)\}=b$ .

In the rules, the symbol  $\xrightarrow{bool}$  denotes the evaluation relation for Femto-VHDL Boolean expressions. The type of  $\xrightarrow{bool}$  is  $bexp \to Boolean \to Boolean$ , and is given in the upper left-hand corner of the box displaying the rules. This type information will be a recurrent pattern in the presentation of the other rule sets. Axioms are provided for the evaluation of individual signals, the values of the constants true and false, the calculation of the delayed value of a signal and the determination of whether or not there is an event occurring on a signal. The other inference rules define the relationship between Femto-VHDL Boolean operators, and the logical Boolean expressions that they evaluate to. For instance, rule  $b_6$  states that if some Femto-VHDL Boolean expression e evaluates to the logical value e, then the