Technical Report

Number 300

**Computer Laboratory**

# Formal verification of VIPER's ALU

Wai Wong

April 1993

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

© 1993 Wai Wong

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Contents

| 1            | Introduction                                           |           |  |

|--------------|--------------------------------------------------------|-----------|--|

| 2            | The ALU models                                         | 4         |  |

|              | 2.1 An informal description $\ldots$                   | 5         |  |

|              | 2.2 Creating the formal model                          | 9         |  |

|              | 2.3 Representation of words                            | 10        |  |

|              | 2.4 A formal ALU model in HOL                          | 12        |  |

|              | 2.5 Logical connectives—the theory LOGIC               | 12        |  |

|              | 2.6 Declare required word sizes—the theory WORD_WIDTHS | 15        |  |

|              | 2.7 Common definitions-the theory COMMON               | 15        |  |

|              | 2.8 Specification of the ALU—the theory ALU            | 18        |  |

|              | 2.9 ALU bit slices—the theory ALUBIT                   | 20        |  |

| 3            | The goal                                               | 27        |  |

| 4            | The proof                                              | 28        |  |

|              | 4.1 The first stage                                    | 29        |  |

|              | 4.2 Stage 2: bitwise operations                        | 35        |  |

|              | 4.3 Stage 2: arithmetic operations                     | 42        |  |

|              | 4.4 Stage 2: shift left operations                     | 48        |  |

|              | 4.5 The final theorem                                  | 54        |  |

| 5            | Benchmark                                              | 57        |  |

| 6            | Conclusion                                             | 59        |  |

| A            | Notes on proof management and document production      | 61        |  |

| в            | ALU models in NODEN                                    | 63        |  |

|              | B.1ALU specification in NODEN_HDLB.2ALU implementation | 63<br>66  |  |

|              |                                                        | 00        |  |

| $\mathbf{C}$ | ALU specification in the VIPER project                 | <b>72</b> |  |

1

# List of Figures

| 1        | A 32-bit ALU                                    |

|----------|-------------------------------------------------|

| 2        | A 4-bit ALU                                     |

| 3        | A 16-bit ALU constructed from four 4-bit slices |

| 4        | A 32-bit ALU constructed from two 16-bit ALUs 8 |

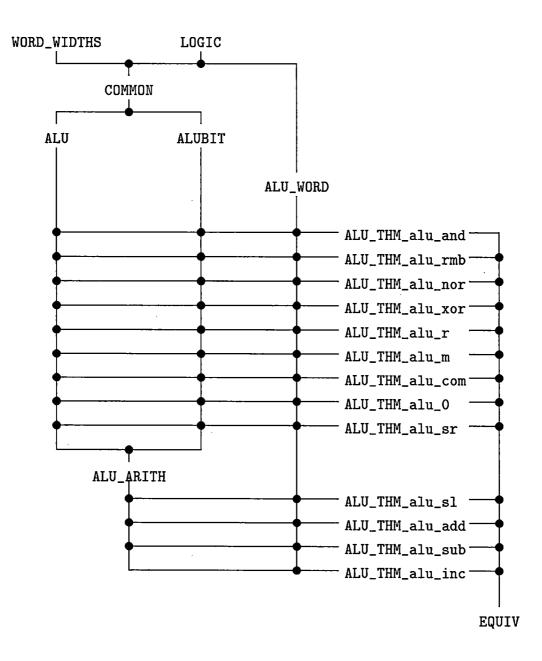

| <b>5</b> | Theory hierarchy of the ALU definitions         |

| 6        | Theory hierarchy of the whole verification      |

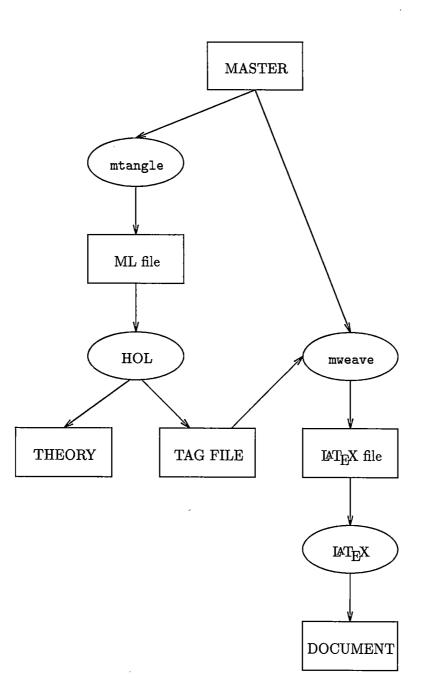

| 7        | Processing the proof script master file         |

# List of Tables

| 1 | ALU operations                            | 9  |

|---|-------------------------------------------|----|

|   | Pre-defined constants in the word library |    |

| 3 | Timing results                            | 58 |

# Acknowledgement

The research described in this report was supported by a grant No. CTA T7 from the Defence Research Agency (Malvern) (formly RSRE). This report first appeared as the final report of the above contract.

The author would like to thank Dr. C. Pygott of DRA(Malvern) who provided the opportunity for me to carry out the research, and gave valuable comments to the work througout the whole period. I would also like to thank Dr. M. J. C. Gordon who carefully guided me through the whole project and commented on a draft of this report. Dr. P. Curzon also commented on a draft of the report. Furthermore, I would like to thank everyone in the Hardware Verification Group who had helped me during the project.

# Abstract

This research report describes the formal verification of an arithmetic logic unit of the VIPER microprocessor. VIPER is one of the first processors designed using formal methods. A formal model in HOL has been created which models the ALU at two levels: on the higher level, the ALU is specified as a function taking two 32bit operands and returning a result; on the lower level, the ALU is implemented by a number of 4-bit slices which should takes the same operands and returns the same result. The ALU is capable of performing thirteen different operations. A formal proof of functional equivalence of these two levels has been completed successfully. The complete HOL text of the ALU formal model and details of the proof procedures are included in this report. It has demonstrated that the HOL system is powerful and efficient enough to perform formal verification of realistic hardware design.

# 1 Introduction

This report describes the verification of the Arithmetic Logic Unit (ALU) of the VIPER microprocessor. VIPER is one of the first microprocessors which has been designed using formal methods. The functional behaviour of VIPER was specified in three separate levels with increasing details: the high-level specification, the host machine level and the electronic block level [4] [3]. Formal verification using the HOL theorem prover was carried out by Cohn who showed the equivalence between the high-level and the host machine level, and between the high-level and the electronic block level [1] [2]. Throughout this verification the ALU was treated as a black box whose functional behaviour was specified as a function in the HOL logic. However, the ALU was implemented by a number of bit slices in the design. Since the correctness of the ALU function is crucial to the correct functioning of VIPER, it is very interesting to see whether the bit slice implementation of the ALU is functionally correct. A manual proof of this correctness has been carried out by Pygott in NODEN\_HDL. He concluded in [6] that although it was not a complete formal proof, it shown convincingly that the NODEN\_HDL ALU specification and implementation are functionally equivalent. Nevertheless, it is still worthwhile to perform a formal proof to confirm the functional equivalence between the specification and the implementation. This will be of benefit to anyone who wishes to use the microprocessor in any critical applications as one will have more confidence in the correct functioning of the device.

This report describes the formal proof of the ALU in the HOL theorem prover. The functional equivalence between the two levels of the ALU model is confirmed. This report contains sufficient details for the designers to follow the proof and for any independent experts to check its validity.

The report begins by describing the ALU informally, and this is followed by a description of the ALU formal model. The strategy of the proof is then outlined, and some typical operations are described in detail. A conclusion is drawn based on the proof. Some notes on the notations used in the report, listings of original NODEN\_HDL description can be found in the appendices.

# 2 The ALU models

The ALU has been defined in two levels: the *specification* and the *implementation*. They were written in the hardware specification language NODEN\_HDL. This section begins with an informal description of the ALU, a discussion on how to represent this model in HOL follows, and then the formal description of the ALU is presented.

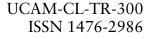

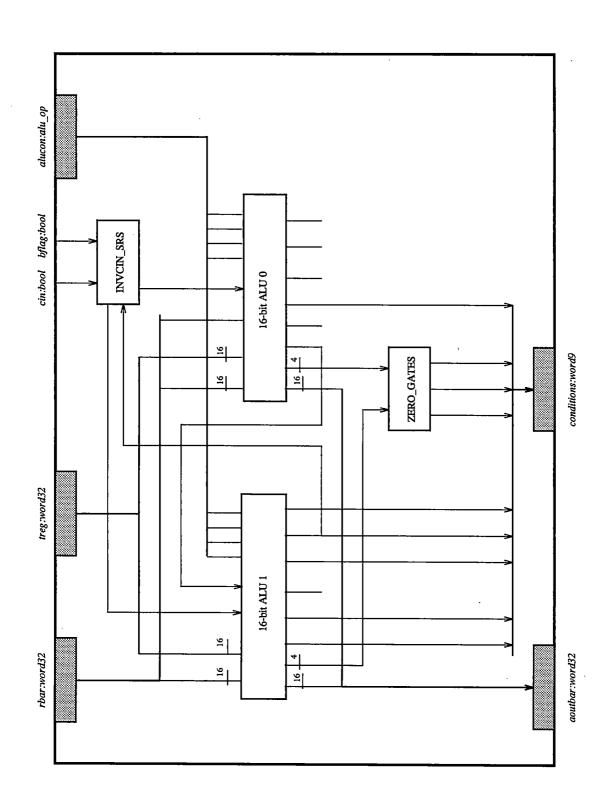

Figure 1: A 32-bit ALU

### 2.1 An informal description

At the specification level, the ALU is viewed as a black box which is capable of performing thirteen different operations. It is specified as a function which takes as its inputs two 32-bit words, namely *rbar* and *treg*, as the operands, two boolean flags *cin* and *bflag*, and a value *alucon* specifying the required operation. It delivers a 32-bit word *aoutbar* as the result of the operation and a 9-bit word *conditions* indicating various status values. This view of the ALU is shown in Figure 1.

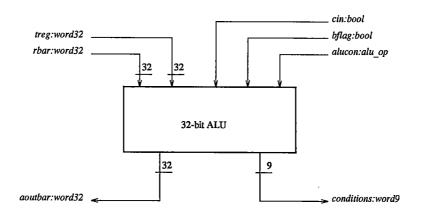

At the implementation level, the ALU is constructed from eight 4-bit slices. Each of these slices is capable of performing the same set of operations as the specification but on smaller operands, namely 4-bit words. Each of these 4-bit slices is treated as a black-box in this verification. A block diagram of the slice is shown in Figure 2. It takes two 4-bit words as its operands, namely *rabr* and *treg*, two boolean flag inputs *cin* and *srbar*, and a value *alucon* indicating the required operation. It outputs the main result of operation as a 4-bit word *aoutbar*, a carry *pg* and six boolean flags (*aout*4, *r*4, *r*3, *r*1, *rm*31, *zero*) indicating various status values.

Following conventional design found in many ALUs, these eight slices are organized into a two tier structure: the lower tier consists of groups of four slices, each group forming a 16-bit unit; the upper tier consists of two 16-bit units.

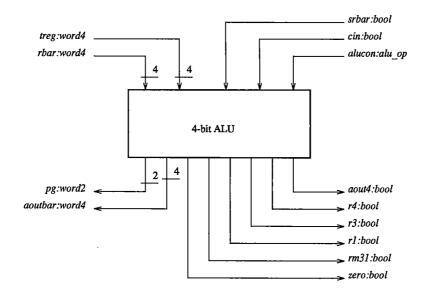

A schematic block diagram showing the interconnection of the 4-bit slices within a 16-bit unit can be found in Figure 3. On the input side of a 16-bit unit, there are two 16-bit words *rbar* and *treg* as its operands, two boolean flags *srbar* and *cin*. Then, there are four inputs indicating the required operation of each of the slices ( $alucn_0$  through  $alucn_3$ ). In theory, each of the slices may perform a different operation at the same time if the values to the inputs  $alucn_i$ are different. In fact, such situations should never happen. As can be seen in

5

Figure 2: A 4-bit ALU

the formal description, the same value is always passed to these four inputs at the same time. The block labelled 'LOOK AHEAD' in the figure implements the carry lookahead circuitry. It combines the carry output pg from each slice and the carry input *cinbar* into this unit and distributes the appropriate carry input back to each slice. This appears to involve a feedback loop. When translating literally into HOL, it requires mutually dependent local variables in function definitions. This is not supported in the HOL system. This problem is solved by breaking down the 'LOOK AHEAD' block into four smaller blocks, one for each slice. Each smaller block then takes input only from its least significant slice(s), so the mutual dependence is eliminated.

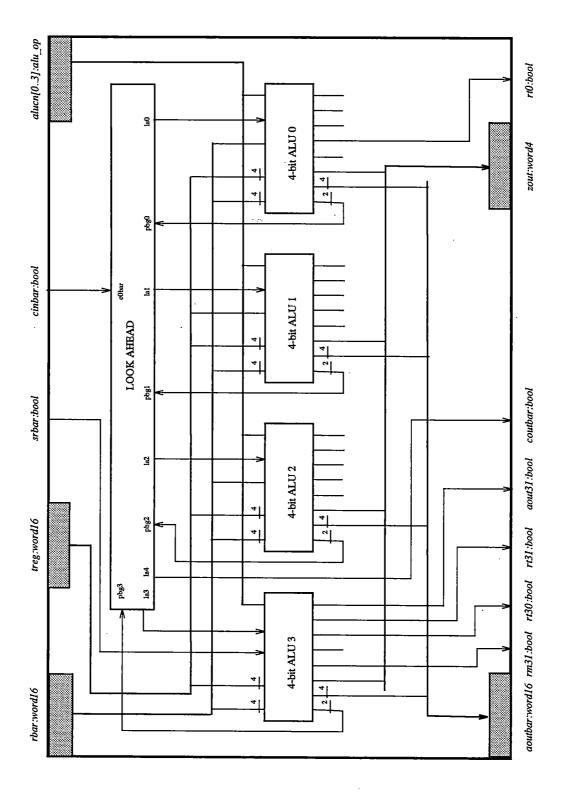

A schematic block diagram showing the 32-bit ALU implementation constructed from two 16-bit units can be found in Figure 4. This implementation has exactly the same inputs and outputs as the specification. The block labelled 'INVCIN\_SRS' provides the *srbar* inputs to the 16-bit units. Like the carry lookahead block in the 16-bit unit, this also appears to involve a feedback loop. In fact, this loop is even tighter than the one in the 16-bit unit. From the diagram, it can be seen the output rt31 of the more significant 16-bit unit '16-bit ALU 1' is combined in the 'INVCIN\_SRS' block with the input *cin* and *bflag*, and the output of this block is routed back to the same unit as the *srbar* input. This input is only used by the most significant slice, but the output rt31 is also generated from the same slice. Therefore, the loop is actually around the most significant 4-bit slice. However, when examining the original definition further, it is discovered that rt31 is only the most significant bit of the first operand *rbar*. Based on this

Figure 3: A 16-bit ALU constructed from four 4-bit slices

ALU VERIFICATION

Figure 4: A 32-bit ALU constructed from two 16-bit ALUs

8

| bitwise AND $r$ and $m$      |

|------------------------------|

| bitwise AND $r$ and NOT $m$  |

| bitwise XOR $r$ and $m$      |

| bitwise NOR $r$ and $m$      |

| complement $m$ (bitwise NOT) |

| always return $m$            |

| always return $r$            |

| always return 0 (zero)       |

| shift $r$ to the right       |

| shift $r$ to the left        |

| $r+m+c_{in}$                 |

| subtract $m$ from $r$        |

| increment r                  |

|                              |

Table 1: ALU operations

observation, the loop can be eliminated by connecting the most significant bit of the first operand directly to the 'INVCIN\_SRS' block.

The ALU is capable of performing the thirteen different operations which are listed in Table 1. The left column lists the mnemonic names of the operations and the right column describes the operations. The variables r and m are the first and second operand, respectively, and  $c_{in}$  is the carry input. The operations can be divided into two groups: *bitwise* and *arithmetic* operations. The latter groups contains the addition, subtraction, increment and shift-left operations. These are more complicated than the bitwise ones. The subtraction is actually specified as adding the negated second operand to the first, and the increment operation is specified as adding the carry input bit to the operand.

### 2.2 Creating the formal model

After the informal description of the ALU in Section 2.1, a discussion of how to formally represent the ALU in HOL will help the reader to understand the formal model and the proof described in subsequent sections.

The most important problem in creating the formal model is to preserve the meaning of the original design or description in whatever language it has been written. If it has been written in a formal language which has a well-defined and well-understood semantics, the problem can be solved relatively easily. If the verification is to be carried out in the same language as the original description there may even not be a problem. In practice, this will be very rare since almost all engineering requirements and designs will first be described in natural language.

These will then be translated or re-written in more formal language(s) such as programming languages and hardware description languages. How accurate the translation is largely depends on how precise the source description is and how well understood.

In the current project, the description of ALU model provided by Defence Research Agency (Malvern) was written in the hardware description language NODEN\_HDL. This is a well-defined language with very little ambiguity. Since the verification is to be carried out in a mechanical theorem prover, the HOL system, which does not support NODEN\_HDL, the translation is necessary.

Although NODEN\_HDL is a hardware description language whereas HOL implements simple typed lambda calculus, many features are very similar, that is there are one-one correspondences between some similar features in these two languages. Both languages are well typed: all variables must possess a type. Similar basic built-in types exist in both languages, such as booleans, natural numbers and tuples. Both languages allow user-defined functions and local variables in these functions. Taking advantage of this similarity, the basic principle in translating the ALU description from NODEN\_HDL into HOL is to keep the new description as close to the original as possible using corresponding features in the two languages. In addition, the same names are chosen for all functions and variables with only a few exceptions. For example, the function ALU that is the ALU specification in NODEN\_HDL is translated into HOL as a function of the same name which has the same number of inputs and outputs in the same order. It is believed that this principle and naming convention will help to ensure that the translation is faithful to the original model. Any discrepancies between the two descriptions will be pointed out clearly and reasons given when the formal model is presented in Section 2.4.

### 2.3 Representation of words

Words or bit vectors are one of the fundamental data objects one has to deal with in hardware design, specification and verification. They are ubiquitous. Words in NODEN\_HDL are represented by the type wordn where n is the size, for example, 8-bit words are of type word8. These types are represented as boolean vectors of the appropriate length. Every vector has a fixed length at compile time. There are built-in vector operations which can be applied to vectors of any length. For example, the bits can be accessed using the indexing operation. Two words of size m and n can be concatenated to form a new word of size (m + n)using the vector concatenation operator CONC.

When the original VIPER verification project was carried out, there was no high level support for modelling words in the HOL system, and there was not even proper support for defining recursive types. In the original VIPER verification, words were modelled by simply introducing into the HOL logic a new type named :wordn for each required word size n together with a number of new constants which stand for the basic operators of the new type. Axioms describing the basic properties of words had to be added to the system to allow reasoning about word operations. This was not very satisfactory and against the common practice of using only definitional extension to the logic which has since been established in the HOL user community.

One possible approach is to define a type :wordn for every required size of words and a number of operators of each of the newly defined types. However, unlike NODEN\_HDL, list operators may not be used on these words even if their underlying representation is list. Considering word concatenation as an example, an operator is required for every combination of m and n. This is not quite satisfactory either.

As part of the work carried out, a new HOL library word has been developed which takes a more pragmatic approach and provides a generic and flexible infrastructure for modelling bit vectors. This is used in the verification of the ALU. The major features in this library are:

- a polymorphic type : (\*)word to represent all words;

- using restricted quantifiers to simulate dependent types for different word sizes;

- a number of generic word operators;

- many theorems about the basic properties of bit vectors.

The polymorphic type :(\*)word allows the user to create instances which are better suited to particular applications. In this project, boolean words, i.e., words of type :(bool)word are used exclusively. This also allows words of different sizes to have the same basic properties and to share the same operators. For example, WNOT is the bitwise negation operator which can be applied to a word of any size.

Restricted universal quantifier is defined by the following equation:

$$\vdash (\forall x :: P. Q x) = (\forall x. P x \supset Q x)$$

where the double colon (::) indicates that the universal quantified variable x is restricted by the predicate P. This has the same meaning (by definition) as the implication on the right hand side. The syntax of restricted quantifiers closely resembles the syntax of types.

The predicate PWORDLEN n is defined in the library to discriminate words of different sizes. This predicate evaluates to T when applied to a word w if and only if w is of size n. Using restricted quantifiers with this predicate, one can express the statement 'for all words w of size  $n, \ldots$ ' as

$$\forall w :: \mathsf{PWORDLEN} n. \ldots$$

Most of the theorems in the library are restricted quantifications like this.

The user can also define predicates for specific word size in terms of the predefined function PWORDLEN, such as defining word32 by the equation

#### $\vdash$ word32 = PWORDLEN 32

Then, one can write expressions like  $\forall w :: \text{word32...}$  Other useful constants defined in the library are listed in Table 2. For convenience and readability, all these constants in the 'Basic word operations' group may be used in the definition of the ALU model, but in the proof, these will be converted into a smaller canonical set of basic operations. This set includes only the following: WCAT, SEG and BIT.

### 2.4 A formal ALU model in HOL

This section describes a formal model of the ALU in HOL. This is based on the original NODEN\_HDL description. The translation from NODEN\_HDL to HOL follows the principle described in Section 2.2 and uses the word library. This model consists of two levels: the specification and the implementation. After comparing the HOL description with the original NODEN\_HDL description, it is believed that they are faithful to each other.

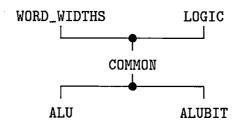

The HOL description of the ALU model is organized into a hierarchy of five theories. Figure 5 shows the ancestry of these theories. Details of the theories will be described in the following sections<sup>1</sup>, meanwhile, a brief outline of the theories is given here:

LOGIC — definitions of several logical connectives;

WORD\_WIDTHS — definitions of predicates for required word sizes;

COMMON — definitions of type and functions common to both levels;

ALU — the ALU specification model;

ALUBIT the ALU implementation model.

#### 2.5 Logical connectives—the theory LOGIC

This file contains definitions of a number of basic logical connectives. They are either synonyms of HOL built-in constants or simple combinations of them. (This was taken from the original VIPER verification. They were defined to improve readability.)

There are several theorems in this theory which assert the facts that these connectives are equivalent to the built-in constants.

<sup>&</sup>lt;sup>1</sup>Text in these sections are generated from the master file using the utility program mweave. Appendix A will explain this process briefly.

| PWORDLEN       | Basic word operations<br>:num -> (*)word -> bool<br>:num -> (*)word -> num | word size discriminator<br>word size          |

|----------------|----------------------------------------------------------------------------|-----------------------------------------------|

|                |                                                                            | word segment<br>a single bit                  |

|                | :(*)word -> *<br>:(*)word -> *                                             | most significant bit<br>least significant bit |

| WCAT<br>WSPLIT | :(*)Word # (*)Word -> (*)Word # (*)                                        | word concatenation                            |

|                | 11                                                                         | named and any state of the Orean state        |

| PBITOP         | word -> (**)word)                                                          | predicate for bitwise unary operators         |

| PBITBOP        | :((*)word -> (**)word -> (***)word) -> bool                                | predicate for bitwise binary operators        |

|                | :* -> (*)word -> ((*)word # *)                                             | shift right                                   |

|                | :(*)word -> * -> (* # (*)word)                                             | shift left                                    |

| WNOT           | :(bool)word -> (bool)word                                                  | bitwise NOT                                   |

| WAND           | :(bool)word -> (bool)word -> (bool)word                                    | bitwise AND                                   |

|                | :(bool)word -> (bool)word -> (bool)word                                    | bitwise OR                                    |

| WXOR           | :(bool)word -> (bool)word -> (bool)word                                    | bitwise exclusive-OR                          |

|                | Word-natural number conversion                                             | sion                                          |

|                | :bool -> num                                                               | convert a bit to a number                     |

|                | :num -> bool                                                               | convert a number to a bit                     |

| BNVAL          | :(bool)word -> num                                                         | convert a word to a number                    |

| NBWORD         | :num -> num ->(bool)word                                                   | convert a number to a word                    |

### ALU VERIFICATION

Table 2: Pre-defined constants in the word library

13

Figure 5: Theory hierarchy of the ALU definitions

2.5.1 XOR — exclusive OR HOL Definition (XOR\_DEF)

$\vdash \forall b_1 \, b_2 . \, b_1 \, \mathsf{XOR} \, b_2 = b_1 \wedge \neg b_2 \vee b_2 \wedge \neg b_1$

2.5.2 NOT HOL Definition (NOT\_DEF)

$\vdash \forall b$ . NOT  $b = \neg b$

2.5.3 OR

HOL Definition (OR\_DEF)

$\vdash \forall b_1 \, b_2 . \, b_1 \, \mathsf{OR} \, b_2 = b_1 \lor b_2$

2.5.4 XNOR — exclusiv NOR

HOL Definition (XNOR\_DEF)

$\vdash \forall b_1 \, b_2 \, b_1 \, \mathsf{XNOR} \, b_2 = (b_1 = b_2)$

2.5.5 AND

HOL Definition (AND\_DEF)

$\vdash \forall b_1 \, b_2 \, . \, b_1 \, \mathsf{AND} \, b_2 = b_1 \wedge b_2$

**2.5.6 Theorems** We can now prove some simple theorems to equate the new connectives to HOL built-in constants so they can be used in the proof to rewrite these new constants.

HOL Theorem (NOT\_THM1)  $\vdash$  NOT = \$¬ HOL Theorem (OR\_THM1)  $\vdash$  \$OR = \$∨ HOL Theorem (AND\_THM1)  $\vdash$  \$AND = \$∧ HOL Theorem (XNOR\_THM1)  $\vdash$  \$XNOR = \$= HOL Theorem (XOR\_THM1)  $\vdash$  b1 XOR b2 = ¬(b1 = b2)

#### 2.6 Declare required word sizes—the theory WORD\_WIDTHS

In this theory, several predicates are defined for discriminating words of different sizes.

**2.6.1** Function for declaring word size The ML function declare\_word\_sizes is defined which takes a list of numbers and defines a HOL constant for each of the elements in the list. The names of the constants are word n. It represents a predicate which will be T if its boolean word argument is of size n. The new constants are defined in terms of PWORDLEN in the word library. The definition is stored under the name wordn\_def.

**2.6.2** Declare required word sizes For the ALU proof, predicates of the following word sizes are needed: [4;16;32]. The ML function defined above is called, and the resulting definitions are listed below:

HOL Definition (word4\_def)

#### $\vdash$ word4 = PWORDLEN4

HOL Definition (word16\_def)

$\vdash$  word16 = PWORDLEN16

HOL Definition (wor32\_def)

$\vdash$  word32 = PWORDLEN 32

#### 2.7 Common definitions-the theory COMMON

This theory contains a number of definitions which are common to both the specification and the implementation of the ALU.

**2.7.1** The type :alu\_op The enumeration type ":alu\_op" represents the possible ALU operations. There are 13 operations defined. The names and their semantics are listed in the table below where r and m are the operands,  $c_{in}$  is the carry input and b is a status flag.

| alu_and | bitwise AND $r$ and $m$      |

|---------|------------------------------|

| alu_rmb | bitwise AND $r$ and NOT $m$  |

| alu_0   | always return 0 (zero)       |

| alu_m   | always return $m$            |

| alu_com | complement $m$ (bitwise NOT) |

| alu_r   | always return r              |

| alu_sr  | shift $r$ to the right       |

| alu_xor | bitwise XOR $r$ and $m$      |

| alu_nor | bitwise NOR $r$ and $m$      |

| alu_si  | shift $r$ to the left        |

| alu_add | $r+m+c_{in}$                 |

| alu_sub | $r + (NOT m) + c_{in}$       |

| alu_inc | $r + c_{in}$                 |

The ML function define\_type in the type definition package is used to defint the type ":alu\_op". The type specification passed to this function is

**2.7.2 IS\_BITOP\_DEF** The predicate  $|S\_B|TOP$  is defined to discriminate the ALU operations. For any operation *aluop*, it is a bitwise operation if it satisfies this predicate, i.e.,  $|S\_B|TOP \ aluop = T$ .

HOL Definition (IS\_BITOP\_DEF)

$$\begin{array}{l} \vdash (IS\_BITOP \ alu\_and = T) \land (IS\_BITOP \ alu\_rmb = T) \land \\ (IS\_BITOP \ alu\_0 = T) \land (IS\_BITOP \ alu\_m = T) \land \\ (IS\_BITOP \ alu\_com = T) \land (IS\_BITOP \ alu\_r = T) \land \\ (IS\_BITOP \ alu\_sr = T) \land (IS\_BITOP \ alu\_xor = T) \land \\ (IS\_BITOP \ alu\_nor = T) \land (IS\_BITOP \ alu\_sl = F) \land \\ (IS\_BITOP \ alu\_add = F) \land (IS\_BITOP \ alu\_sub = F) \land \\ (IS\_BITOP \ alu\_add = F) \land \\ (IS\_BITOP \ alu\_sub = F) \land \\ \end{array}$$

**2.7.3 GET\_RM31\_DEF** This function is used in the definition of the ALU. The argument  $t_{31}$  is the most significant bit of the second operand, i.e., the sign bit if it is interpreted as a 2's complement integer. Depending on the operation *alucon*, it returns  $t_{31}$  or negated  $t_{31}$  or F.

HOL Definition (GET\_RM31\_DEF)

$\vdash \forall t_{31} alucon. \text{GET}_RM31 t_{31} alucon = \\ ((alucon = alu\_sub) \Rightarrow \text{NOT} t_{31} \mid \\ ((alucon = alu\_add) \Rightarrow t_{31} \mid F))$

2.7.4 Projection operatores This section defines a number of projection operators for extracting bits and fields from the values delivered by the two ALU functions. The ALU delivers a pair: the first field AOUT is the result of the computation which is a 32-bit word, and the second field COUT is a 9-bit word indicating various conditions. Two functions GET\_AOUT and GET\_COUT return these two fields, respectively.

HOL Definition (GET\_AOUT\_DEF)

$\vdash \forall aout cout. GET\_AOUT (aout, cout) = aout$

**HOL Definition** (GET\_COUT\_DEF)

$\vdash \forall aout cout. \mathsf{GET}_COUT(aout, cout) = cout$

For the condition word returned by GET\_COUT, each bit can be accessed using a function whose name is the name of the required bit prefixed by COND\_. The definitions of these functions are listed below while the meanings of the condition bits will be described in Section 2.8.5.

HOL Definition (COND\_AOUT31\_DEF)

$\vdash \forall cond. COND\_AOUT31 cond = BIT 8 cond$

HOL Definition (COND\_R0\_DEF)

$\vdash \forall cond. COND_R0 cond = BIT 7 cond$

**HOL Definition** (COND\_R30\_DEF)

$\vdash \forall cond. COND_R30 cond = BIT 6 cond$

HOL Definition (COND\_R31\_DEF)

$\vdash \forall cond. COND_R31 cond = BIT 5 cond$

HOL Definition (COND\_RM31\_DEF)

$\vdash \forall cond. COND_RM31 cond = BIT 4 cond$

HOL Definition (COND\_COUTBAR\_DEF)

$\vdash \forall cond. COND\_COUTBAR cond = BIT 3 cond$

HOL Definition (COND\_NZTOP12\_DEF)

$\vdash \forall cond. COND\_NZTOP12 cond = BIT 2 cond$

**HOL Definition** (COND\_ZMID4\_DEF)

$\vdash \forall cond. COND_ZMID4 cond = BIT1 cond$

HOL Definition (COND\_NZBOT16\_DEF)

$\vdash \forall cond. COND_NZBOT16 cond = BIT0 cond$

#### 2.8 Specification of the ALU—the theory ALU

**2.8.1 ADD32\_DEF** The function ADD32 performs the 32-bit word addition operation. It is specified in terms of the natural number addition +. The operands are converted to natural numbers first. If the carry input *cin* is set, a 1 is added to the sum. The result is then converted back to a 33-bit word to accommodate the possible carry.

HOL Definition (ADD32\_DEF)

F

$$\forall r t :: word 32. \forall cin.$$

$ADD32 r t cin =$

$(cin \Rightarrow NBWORD 33 (BNVAL r + BNVAL t + 1) |$

$NBWORD 33 (BNVAL r + BNVAL t))$

**2.8.2 ADD32BIT\_DEF** This is the top level 32-bit word addition function. It takes two 32-bit words and a carry input, and returns a pair consisting of to a 32-bit sum and a carry ouput as the result.

**HOL Definition** (ADD32BIT\_DEF)

$\vdash \forall r t :: word32. \forall cin.$  ADD32BIT r t cin =  $let sum_{33} = ADD32 r t cin in$   $let aout = SEG 320 sum_{33} in$   $let carry = MSB sum_{33} in$  (aout, carry)

**2.8.3** FIND\_SR\_DEF This function works like a two-input multiplexer. It is called by BITOP to work out the value to be padded to the MSB of the result of a shift right operation.  $r_{31}$  is the MSB of the operand. If *cin* is set, FIND\_SR returns  $r_{31}$ , the shift right operation implements an arithmetic shift, i.e., the sign bit is copied.

HOL Definition (FIND\_SR\_DEF)

$\vdash \forall cin \, bf lag \, r_{31}.$ FIND\_SR (cin, bf lag, r\_{31}) = (cin \Rightarrow r\_{31} \mid bf lag)

**2.8.4 BITOP\_DEF** This is the function specifying the actual operation performed by the ALU. The first two arguments are the operands. The next three, bflag,  $r_{31}$  and cin are boolean flags, they are used only in arithmetic and shift operations. The last argument op indicates what operation is to be performed. It returns a pair whose first field is the operation result and whose second field is the carry bit if the operation is arithmetic. Otherwise, it should be don't care, i.e. the value ?bool in NODEN\_HDL. However, there is no such value in the built-in boolean type ":bool" in HOL, so the value F is returned instead. This changes the meaning of the specification, but it is compensated for in the final goal (see Section 3).

#### HOL Definition (BITOP\_DEF)

$\vdash \forall r t :: word32. \forall b f lag r_{31} cin op.$  $BITOP r t b f lag r_{31} cin op =$ let  $cout_x = F$  in let tbar = WNOT t in let rbar = WNOTr in let  $sr = FIND\_SR(cin, bflag, r_{31})$  in let  $r\_xor\_t = r$  WXOR t in let  $shift_right = FST(SHRFsrr)$  in  $((op = alu_and) \Rightarrow r WAND t, cout_x |$  $((op = alu_rmb) \Rightarrow r WAND tbar, cout_x |$  $((op = alu_0) \Rightarrow NBWORD 320, cout_x |$  $((op = alu_m) \Rightarrow t, cout_x \mid$  $((op = alu\_com) \Rightarrow tbar, cout\_x |$  $((op = alu_r) \Rightarrow r, cout_x \mid$  $((op = a|u_sr) \Rightarrow shift_right, cout_r|$  $((op = a|u_xor) \Rightarrow r_xor_t, cout_x|$  $((op = alu_nor) \Rightarrow WNOT (r WOR t), cout_x |$  $((op = alu_sl) \Rightarrow ADD32BIT rr cin |$  $((op = alu_add) \Rightarrow ADD32BIT r t cin |$  $((op = alu_sub) \Rightarrow ADD32BIT r tbar cin |$

**2.8.5 ALU\_DEF** This function is the specification of the 32-bit ALU. It takes five inputs: *rbar* is the first operand which has been complemented, *treg* is the second operand, *cin* is the carry input, *bflag* is the status flag, and *alucon* specifies the required operation. The output is a pair whose first field is the operation result and whose second field is a 9-bit word indicating various conditions. The names of these bits and their meanings are described in the table below:

| aout31  | MSB of the result                                      |

|---------|--------------------------------------------------------|

| r0      | LSM of the first operand                               |

| r30     | 30th of the first operand                              |

| r31     | MSB of the first operand                               |

| rm31    | MSB of the second operand if addition                  |

|         | negated MSB of the second operand if subtraction       |

|         | otherwise, this is F                                   |

| coutbar | negated carry output                                   |

| nztop12 | T if any of the most significant 12 bits are non-zero  |

| zmid4   | T if the middle 4 bits are all zero                    |

| nzbot16 | T if any of the least significant 16 bits are non-zero |

#### HOL Definition (ALU\_DEF)

$\vdash \forall rbar treg :: word32. \forall cin b flag alucon.$

```

ALU r bar treg cin b f lag a lucon =

let r = WNOT r bar in

let t_{31} = MSB treg in

let rm_{31} = \text{GET}_RM31 t_{31} alucon in

let r_0 = \text{LSB} r in

let r_{30} = BIT 30 r in

let r_{31} = MSBr in

let a_c = BITOP r treg b f lag r_{31} cin alucon in

let aout = GET_AOUT a_c in

let aoutbar = WNOT aout in

let coutbar = NOT(GET_COUT a_c) in

let aout_{31} = MSB aout in

let nzbot_{16} = NOT (BNVAL (SEG 160 aout) = 0) in

let zmid_4 = (BNVAL (SEG 4 16 aout) = 0) in

let nztop_{12} = NOT (BNVAL (SEG 1220 aout) = 0) in

let conditions = WORD [aout_{31}; r_0; r_{30}; r_{31}; rm_{31}; coutbar; nztop_{12}; zmid_4; nzbot_{16}] in

(aoutbar, conditions)

```

#### 2.9 ALU bit slices—the theory ALUBIT

This theory defines the ALU implementation constructed from 4-bit slices.

**2.9.1 SRSELECT\_DEF** This is just a multiplexer function with inverting output.

**HOL Definition** (SRSELECT\_DEF)

$\vdash \forall cin b f lag rt_{31}.$ SRSELECT cin b f lag rt\_{31} = (cin  $\Rightarrow$  NOT rt\_{31} | NOT b f lag)

2.9.2 INVCIN\_SRS\_DEF As mentioned in Section 2.1, the block labelled 'INVCIN\_SRS' represented by the function of the same name in NODEN\_HDL has been broken down, so we do not need to translate this into HOL.

**2.9.3 ZERO\_LS16\_DEF** The arguments to this function are two 4-bit words. They are the zero condition words returned by the 16-bit ALU units. Each bit indicates whether the operation result from a 4-bit slice is equal to zero. A T represents a zero result. The function ZERO\_LS16 returns T if and only if the least significant sixteen bits are *not* all zero.

HOL Definition (ZER0\_LS16\_DEF)

$\vdash \forall lszeros mszeros.$

$ZERO\_LS16 \ lszeros \ mszeros = NOT \ (lszeros = WORD \ [T; T; T; T])$

20

2.9.4 ZERO\_MID4 The arguments to this function are the same as ZERO\_LS16. The function ZERO\_MID4 returns T if and only if the middle four bits, i.e., bit 16 to 19, are all zero.

**HOL Definition** (ZER0\_MID4\_DEF)

$\vdash \forall lszeros \, mszeros. \\ \mathsf{ZERO\_MID4} \, lszeros \, mszeros = \mathsf{BIT0} \, mszeros$

**2.9.5 ZERO\_MS12** The arguments to this function are the same as ZERO\_LS16. The function ZERO\_MS12 returns T if and only if the most significant twelve bits are *not* all zero.

HOL Definition (ZER0\_MS12\_DEF)

⊢ ∀lszeros mszeros.

ZERO\_MS12 lszeros mszeros =

NOT (SEG 31 mszeros = WORD [T; T; T])

2.9.6 ZERO\_GATES\_DEF This function combines the previous three functions to produce a triple of values indicating the zero condition of the operation result. It is used in the 32-bit ALU definition.

#### **HOL Definition** (ZERO\_GATES\_DEF)

⊢ ∀lszeros mszeros.

ZERO\_GATES lszeros mszeros = ZERO\_LS16 lszeros mszeros, ZERO\_MID4 lszeros mszeros, ZERO\_MS12 lszeros mszeros

**2.9.7 Carry lookahead funtions** The carry look ahead functions  $LOOKAHEAD_n$  compute the carry input for the *n*th slice in a 16-bit ALU unit. Each 4-bit slice produces a pair of boolean values indicating the carry generation and propagation status. If the generation bit is set, a carry is generated in this slice. Likewise, if the propagation bit is set, a carry input to this slice should be propagated to the next more significant slice. In the original NODEN\_HDL description, this carry status is represented as a 2-bit word. In the HOL description, the type :cla is defined to represent this carry look ahead value to avoid confusion in bit ordering. This type has two fields: the propagation field and the generation field. Both are boolean. The type constructor is CLA. Two projection operators CPRO and CGEN are defined to access these fields, respectively.

HOL Definition (CPRO\_DEF)

$\vdash \forall p g. \mathsf{CPRO}(\mathsf{CLA} p g) = p$

HOL Definition (CGEN\_DEF)

$\vdash \forall p g. \mathsf{CGEN}(\mathsf{CLA} p g) = g$

2.9.8 LOOKAHEAD\_0\_DEF This is the carry lookahead function for slice 0. It simply negates the carry input.

**HOL Definition** (LOOKAHEAD\_0\_DEF)

$\vdash \forall c_0 bar.$

$LOOKAHEAD_0 c_0 bar = NOT c_0 bar$

**2.9.9 LOOKAHEAD\_1\_DEF** This is the carry lookahead function for slice 1. It takes the carry input to the unit and carry lookahead value from slice 0, and computes the carry input for slice 1.

#### HOL Definition (LOOKAHEAD\_1\_DEF)

$$\forall c_0 bar pbg_0.$$

LOOKAHEAD\_1  $c_0 bar pbg_0 =$

let  $p_0 bar = CPRO pbg_0$  and  $g_0 = CGEN pbg_0$  in

$g_0 OR (NOT p_0 bar AND NOT c_0 bar)$

**2.9.10** LOOKAHEAD\_2\_DEF This is the carry lookahead function for slice 2. It takes the carry input to the unit and carry lookahead value from slice 0 and 1, and computes the carry input for slice 2.

#### HOL Definition (LOOKAHEAD\_2\_DEF)

$\vdash \forall c_0 bar \ pbg_0 \ pbg_1. \\ \mathsf{LOOKAHEAD\_2} \ c_0 bar \ pbg_0 \ pbg_1 = \\ \mathsf{let} \ p_0 bar = \mathsf{CPRO} \ pbg_0 \ \mathsf{and} \ g_0 = \mathsf{CGEN} \ pbg_0 \ \mathsf{in} \\ (\mathsf{let} \ p_1 bar = \mathsf{CPRO} \ pbg_1 \ \mathsf{and} \ g_1 = \mathsf{CGEN} \ pbg_1 \ \mathsf{in} \\ (\mathsf{let} \ c_1 = g_0 \ \mathsf{OR} \ (\mathsf{NOT} \ p_0 bar \ \mathsf{AND} \ \mathsf{NOT} \ c_0 bar) \ \mathsf{in} \\ g_1 \ \mathsf{OR} \ (\mathsf{NOT} \ p_1 bar \ \mathsf{AND} \ c_1)))$

**2.9.11** LOOKAHEAD\_3\_DEF This is the carry lookahead function for slice 3. It takes the carry input to the unit and carry lookahead value from slice 0, 1 and 2, and computes the carry input for slice 3.

HOL Definition (LOOKAHEAD\_3\_DEF)

$\vdash \forall c_0 bar \ pbg_0 \ pbg_1 \ pbg_2.$   $\mathsf{LOOKAHEAD\_3} \ c_0 bar \ pbg_0 \ pbg_1 \ pbg_2 =$   $\mathsf{let} \ p_0 bar = \mathsf{CPRO} \ pbg_0 \ \mathsf{and} \ g_0 = \mathsf{CGEN} \ pbg_0 \ \mathsf{in}$   $(\mathsf{let} \ p_1 bar = \mathsf{CPRO} \ pbg_1 \ \mathsf{and} \ g_1 = \mathsf{CGEN} \ pbg_1 \ \mathsf{in}$   $(\mathsf{let} \ p_2 bar = \mathsf{CPRO} \ pbg_2 \ \mathsf{and} \ g_2 = \mathsf{CGEN} \ pbg_2 \ \mathsf{in}$   $(\mathsf{let} \ c_1 = g_0 \ \mathsf{OR} \ (\mathsf{NOT} \ p_0 bar \ \mathsf{AND} \ \mathsf{NOT} \ c_0 bar) \ \mathsf{in}$   $(\mathsf{let} \ c_2 = g_1 \ \mathsf{OR} \ (\mathsf{NOT} \ p_1 bar \ \mathsf{AND} \ c_1) \ \mathsf{in}$   $g_2 \ \mathsf{OR} \ (\mathsf{NOT} \ p_2 bar \ \mathsf{AND} \ c_2)))))$

2.9.12 LOOKAHEAD\_4\_DEF This is the carry lookahead function for a 61-bit unit. It takes the carry input to the unit and carry lookahead value from all the slices, and computes the carry output of the whole unit.

HOL Definition (LOOKAHEAD\_4\_DEF)

$\vdash \forall c_0 bar pbg_0 pbg_1 pbg_2 pbg_3.$   $LOOKAHEAD_4 c_0 bar pbg_0 pbg_1 pbg_2 pbg_3 =$   $let p_0 bar = CPRO pbg_0 and g_0 = CGEN pbg_0 in$   $(let p_1 bar = CPRO pbg_1 and g_1 = CGEN pbg_1 in$   $(let p_2 bar = CPRO pbg_2 and g_2 = CGEN pbg_2 in$   $(let p_3 bar = CPRO pbg_3 and g_3 = CGEN pbg_3 in$   $(let c_1 = g_0 OR (NOT p_0 bar AND NOT c_0 bar) in$   $(let c_2 = g_1 OR (NOT p_1 bar AND c_1) in$   $(let c_3 = g_2 OR (NOT p_2 bar AND c_2) in$   $NOT (g_3 OR (NOT p_3 bar AND c_3))))))))$

**2.9.13 ADDER4\_DEF** The function ADDER4 performs the 4-bit word addition operation. It is specified in terms of natural number addition '+'. The operands are converted to natural numbers first. If the carry input *cin* is set, a 1 is added to the sum. The result is then converted back to a 4-bit word. Unlike the specification model (see definition of 2.8.1), this conversion will lose a possible carry bit. However, this does not matter since the carries are computed by the carry lookahead function PG4.

HOL Definition (ADDER4\_DEF)

$\vdash \forall r m :: word4. \forall cin.$ ADDER4r m cin =  $(cin \Rightarrow SEG40 (NBWORD5 (BNVALr + BNVALm + 1)) |$ SEG40 (NBWORD5 (BNVALr + BNVALm)))

2.9.14 PG4\_DEF The function PG4 calculates the carry look ahead value for a 4-bit slice.

HOL Definition (PG4\_DEF)

$\vdash \forall r \ m :: \text{ word4.}$   $\mathsf{PG4} \ r \ m =$   $\mathsf{let} \ p = r \ \mathsf{WOR} \ m \ \mathsf{and} \ g = r \ \mathsf{WAND} \ m \ \mathsf{in}$   $(\mathsf{let} \ p_0 = \mathsf{BIT} \ 0 \ p \ \mathsf{and} \ p_1 = \mathsf{BIT} \ 1 \ p \ \mathsf{and} \ p_2 = \mathsf{BIT} \ 2 \ p \ \mathsf{and} \ p_3 = \mathsf{BIT} \ 3 \ p \ \mathsf{in}$   $(\mathsf{let} \ g_0 = \mathsf{BIT} \ 0 \ g \ \mathsf{and} \ g_1 = \mathsf{BIT} \ 1 \ g \ \mathsf{and} \ g_2 = \mathsf{BIT} \ 2 \ g \ \mathsf{and} \ g_3 = \mathsf{BIT} \ 3 \ g \ \mathsf{in}$   $\mathsf{CLA} \left(\mathsf{NOT} \ (p_0 \ \mathsf{AND} \ (p_1 \ \mathsf{AND} \ (p_2 \ \mathsf{AND} \ p_3)))\right)$   $(g_3 \ \mathsf{OR} \ (p_3 \ \mathsf{AND} \ (g_2 \ \mathsf{OR} \ (p_2 \ \mathsf{AND} \ (g_1 \ \mathsf{OR} \ (p_1 \ \mathsf{AND} \ g_0)))))))))))$

**2.9.15 ADD4BIT\_DEF** The function ADD4BIT is the top level addition function for 4-bit words. It returns a pair: the first field is the sum and the second field is the carry.

#### **HOL Definition** (ADD4BIT\_DEF)

$\vdash \forall r m :: word4. \forall cin.$ ADD4BIT r m cin = ADDER4 r m cin, PG4 r m

**2.9.16** FOURBITOP This is the function specifying the actual operation performed by the ALU slice. The first two arguments are the operands. The third argument *srbar* supplies the bit to be padded onto the most significant bit when a shift-right operation is performed. This should be the least significant bit shifted out of the next more significant slice. The fourth argument *cin* is the carry input. The last one, *op*, specifies what operation is to be performed. It returns a pair: the first field is the main operation result and the second field is the carry output. In cases where the operation is bitwise, the carry output is irrelevant, it was a *don't care* value in NODEN\_HDL. Since there is no such value in HOL, the value (CLAFF) is returned. Because this carry output will not be used in bitwise operation, this change should not affect the correctness of the model.

#### HOL Definition (FOURBITOP\_DEF)

$\vdash \forall r m :: word4. \forall srbar cin op.$ FOURBITOP r m srbar cin op =let mbar = WNOT m and rbar = WNOT r in (let  $r_3 = BIT 3r$  in  $(let shift_right = FST (SHRF(NOT srbar)r) in$ (let shift Jeft = SND (SHLFr cin) in $((op = alu_and) \Rightarrow r WAND m, CLAFF |$  $((op = alu_rmb) \Rightarrow r WAND mbar, CLAFF |$  $((op = alu_0) \Rightarrow NBWORD40, CLAFF)$  $((op = alu_m) \Rightarrow m, CLAFF)$  $((op = alu\_com) \Rightarrow mbar, CLAFF |$  $((op = alu_r) \Rightarrow r, CLAFF |$  $((op = alu\_sr) \Rightarrow shift\_right, CLAFF |$  $((op = alu\_xor) \Rightarrow r WXOR m, CLAFF |$  $((op = alu_nor) \Rightarrow WNOT(r WOR m), CLAFF$  $((op = alu_sl) \Rightarrow shift_left, CLA(NOT(r = WORD[T; T; T; T]))r_3|$  $((op = alu_add) \Rightarrow ADD4BIT r m cin |$  $((op = alu_sub) \Rightarrow ADD4BIT r mbar cin |$

2.9.17 ALU\_4BIT The function ALU\_4BIT represents the 4-bit slice. It takes the same arguments as FOURBITOP and returns an 8-tuple. The fields in the return value are listed in the following table:

| pg4    | :cla        | carry lookahead output                                                                                              |

|--------|-------------|---------------------------------------------------------------------------------------------------------------------|

| aout   | :(bool)word | the main result (a 4-bit word)                                                                                      |

| zero   | :bool       | T if and only if the result equals zero                                                                             |

| t4     | :bool       | MSB of the second operand if addition<br>negated MSB of the second operand if subtraction<br>otherwise, this is $F$ |

| r0     | :bool       | LSM of the first operand                                                                                            |

| r2     | :bool       | bit 2 of the first operand                                                                                          |

| r3     | :bool       | MSB of the first operand                                                                                            |

| aout31 | :bool       | MSB of the result                                                                                                   |

HOL Definition (ALU\_4BIT\_DEF)

$\vdash \forall r_4 bar t_4 reg :: word4. \forall srbar cin_4 bit alucon.$

$ALU_4BIT r_4 bar t_4 reg srbar cin_4 bit alucon =$

```

let r = WNOT r_4 bar in

```

$(let aout_pg = FOURBITOP r t_4 reg srbar cin_4 bit alucon in$

$(let aout = FST aout_pg in$

$SND a out_p g, WNOT a out, (a out = NBWORD 40),$

$GET_RM31$  (BIT 3  $t_4reg$ ) alucon, BIT 0 r, BIT 2 r, BIT 3 r, BIT 3 aout))

2.9.18 ALU\_16BIT The function ALU\_16BIT represents a 16-bit unit. It specifies how to assemble four ALU\_4BIT's to form such a unit. It takes eight arguments: the first two are the 16-bit operands; the third *srbar* is a bit to be used to pad the most significant bit when doing shift right; the fourth one is the carry input; and the remaining four specify the required operation for each slice. It returns a triple: the first field is the operation result which is a 16-bit word; the second is a 4-bit word indicating the zero status of the results from each slice; and the last is a 6-bit word indicating various conditions. The names and meanings of the condition word are listed in the following table:

| c4bar  | carry output                                      |

|--------|---------------------------------------------------|

| rm31   | the output bit t4 from the most significant slice |

| rt0    | LSM of the first operand                          |

| rt30   | bit 14 of the first operand                       |

| rt31   | MSB of the first operand                          |

| aout31 | MSB of the result                                 |

Here, we have some difficulty in handling feedback from a single block definition. The LOOK\_AHEAD in the original NODEN\_HDL description takes input from the bit slices and drives the slices as well. To overcome this, we unfold the LOOK\_AHEAD block into a separate lookahead circuit for each individual slice. This is why the LOOK\_AHEAD definition is not needed.

**HOL Definition** (ALU\_16BIT\_DEF)

$\vdash \forall r_{16} bar t_{16} reg :: word 16. \forall srbar cin_{16} bar alucn_0 alucn_1 alucn_2 alucn_3.$

$ALU_16BIT r_{16} bar t_{16} reg srbar cin_{16} bar alucn_0 alucn_1 alucn_2 alucn_3 =$

let  $rb_{00-03} = SEG 40 r_{16} bar$  and  $rb_{04-07} = SEG 44 r_{16} bar$  in

$(\text{let } rb_{08-11} = \text{SEG} 48 r_{16} bar \text{ and } rb_{12-15} = \text{SEG} 412 r_{16} bar \text{ in}$

$(\text{let } m_{00-03} = \text{SEG 40} t_{16} reg \text{ and } m_{04-07} = \text{SEG 44} t_{16} reg \text{ in}$  $(let m_{08-11} = SEG 48 t_{16} reg and m_{12-15} = SEG 412 t_{16} reg in$  $(\text{let } rbar_{04} = \text{BIT} 4 r_{16} bar \text{ and } rbar_{08} = \text{BIT} 8 r_{16} bar \text{ in}$  $(\text{let } rbar_{12} = \text{BIT } 12r_{16}bar \text{ in})$  $(let c_0 = LOOKAHEAD_0 cin_{16} bar in$  $(let alu_0 = ALU_4BIT rb_{00-03} m_{00-03} rbar_{04} c_0 alucn_0 in$  $(let pg_0 = FST alu_0 and$  $aoutbar_{-0} = FST(SND alu_0)$  and  $zout_{-0} = FST(SND(SNDalu_0))$  and  $rt_0 = FST(SND(SND(SND(SNDalu_0))))$  in  $(\text{let } c_1 = \text{LOOKAHEAD}_1 cin_{16} bar pq_0 \text{ in})$  $(let alu_1 = ALU_4BIT rb_{04-07} m_{04-07} rbar_{08} c_1 alucn_1 in$ (let  $pg_1 = \mathsf{FST} alu_1$  and  $aoutbar_{-1} = FST(SND alu_1)$  and  $zout_{-1} = FST(SND(SNDalu_1))$  in (let  $c_2 = LOOKAHEAD_2 cin_{16} bar pg_0 pg_1$  in  $(let alu_2 = ALU_4BIT rb_{08-11} m_{08-11} rbar_{12} c_2 alucn_2 in$  $(let pg_2 = FST alu_2 and$  $aoutbar_{-2} = FST(SND alu_2)$  and  $zout_{-2} = FST(SND(SND alu_2))$  in  $(let c_3 = LOOKAHEAD_3 cin_{16} bar pg_0 pg_1 pg_2 in$  $(let alu_3 = ALU_4BIT rb_{12-15} m_{12-15} srbar c_3 alucn_3 in$  $(let pg_3 = FST alu_3 and$  $aoutbar_{-3} = FST(SND alu_3)$  and  $zout_{-3} = FST(SND(SND alu_3))$  and  $rm_{31} = FST (SND (SND (SND alu_3)))$  and  $coutbar = FST(SND(SND(SND(SNDalu_3))))$  and  $rt_{30} = FST (SND (SND (SND (SND alu_3))))$  and  $rt_{31} = FST (SND (SND (SND (SND (SND alu_3))))) and$  $aout_{31} = SND(SND(SND(SND(SND(SND(SNDalu_3))))))$  in  $(\text{let } c_4 bar = \text{LOOKAHEAD}_4 cin_{16} bar pg_0 pg_1 pg_2 pg_3 \text{ in})$ WCAT (WCAT (aoutbar<sub>-3</sub>, aoutbar<sub>-2</sub>), WCAT (aoutbar<sub>-1</sub>, aoutbar<sub>-0</sub>)),  $WORD[zout_3; zout_2; zout_1; zout_0],$

2.9.19 ALU\_32BIT\_DEF This is the 32-bit ALU implementation function. It specifies how to assemble two ALU\_16BIT's to form the 32-bit ALU. It takes exactly the same arguments as the specification ALU and returns the same results. The name of this function in NODEN\_HDL was ALU\_C. It has been changed to ALU\_32BIT so that it has the same format as the 4-bit slice ALU\_4BIT and 16-bit units ALU\_16BIT.

We have the same feedback problem here as in the 16-bit block. It occurs in the INVCIN\_SRS block in the NODEN\_HDL description. This block can be unfolded into two simpler blocks:

SRSELECT and cinbar. Even after unfolding, we still have the feedback in the SRSELECT block which takes one of the conditional bit output of the higher 16-bit block, namely rt31, and sends its output back to the same block as the srbar input. After some analysis, we find that rt31 is equivalent to the negated most significant bit of the first operand rbar. So, we added the local variable rb31 and equate it to NOT (BIT 31 rbar).

#### HOL Definition (ALU\_32BIT\_DEF)

$\vdash \forall rbar treg :: word32. \forall cin b flag alucon.$

ALU\_32BIT rbar treg cin bf lag alucon = let  $(rb_{16-31}, rb_{00-15}) = WSPLIT 16 rbar$  in  $(let (m_{16-31}, m_{00-15}) = WSPLIT 16 treg$  in  $(let rbar_{16} = BIT 16 rbar$  in  $(let rb_{31} = NOT (BIT 31 rbar)$  in  $(let srbar = SRSELECT cin bf lag rb_{31}$  in (let cinbar = NOT cin in  $(let (aoutbar_{-0}, lszeros, cond_{-0}) =$

$ALU_{-16}BIT rb_{00-15} m_{00-15} rbar_{16} cinbar alucon alucon alucon in$

$(\text{let } cin_m s = \text{BIT } 5 cond_0 \text{ and } rt_0 = \text{BIT } 3 cond_0 \text{ in}$

$(let (aoutbar_{-1}, mszeros, cond_{-1}) =$

$\mathsf{ALU\_16BIT}\, rb_{16-31}\, m_{16-31}\, srbar\, cin\_ms\, alucon\, alucon\, alucon\, in$

$(let coutbar = BIT 5 cond_{-1} and rm_{31} = BIT 4 cond_{-1} in$

$(\text{let } rt_{30} = \text{BIT } 2 \text{ cond}_{-1} \text{ and } rt_{31} = \text{BIT } 1 \text{ cond}_{-1} \text{ in}$

```

(let aout_{31} = BIT 0 cond_{-1} in)

```

$(let (nz\_bot_{16}, z\_mid_4, nz\_top_{12}) = ZERO\_GATES lszeros mszeros in WCAT (aoutbar_1, aoutbar_0),$

# 3 The goal

The goal of the verification is to prove that the two levels of the ALU formal model representing by the functions ALU and ALU\_32BIT are functionally equivalent, i.e., both functions should deliver the same result for all possible combinations of inputs. This may be expressed in HOL as

```

\forall r t :: word32. \forall c_{in} b alucon. ALU r t c_{in} b alucon = ALU_32BIT r t c_{in} b alucon.

```

However, a goal of this form is unprovable since one of the condition bits has been arbitrarily assigned a return value of F which should really be don't care when the operation is bitwise. What needs to be proved is really that, for all possible combinations of inputs, if the operation is not bitwise, these functions return identical results, otherwise, they return two results which are piecewise identical except for the don't care bit. Based on this analysis, a predicate named  $IS\_ALU\_IMP$  is defined. When applied to a function f of the same type as ALU, it returns T if and only if f is an implementation of ALU. Hence, the goal to be proved will be

#### ? - IS\_ALU\_IMP ALU\_32BIT

The definition of this predicate and the details of the proof will be described in next section.

# 4 The proof

Since every ALU operation involves different combination of word and/or arithmetic operations and there are not too many operations, it is possible to carry out case analysis on the operations. Thus, for each ALU operation, i.e., for every possible value of the input *alucon* to the ALU functions, two expressions representing the operation result can be derived: one for the specification and one for the implementation. If these two expressions can be reduced to an identical form minus the field which has the *don't care* value, then the goal will be proved by combining all the cases.

Although every ALU operation is different, the underlying structure of the resulting expressions should be similar since they are derived from the same function definitions, namely the function ALU and ALU\_32BIT. Therefore, it is possible to write programs to implement some proof procedures to carry out the proof mechanically.

The proof has been performed in three stages:

1. unfolding the definitions to derive two expressions for each ALU operation, such as

$$ALU r t c_{in} b op = E_{spec}$$

$$ALU_{32}BIT r t c_{in} b op = E_{imp}$$

where the expressions  $E_{spec}$  and  $E_{imp}$  on the right hand side of the equations consist of only basic word operations in the canonical set, bitwise word operations, word-natural number conversion and natural number addition '+';

- 2. manipulating  $E_{spec}$  and  $E_{imp}$  to unify them to an identical expression E in cases of non-bitwise operations, or to derive two expressions  $E'_{spec}$  and  $E'_{imp}$  whose corresponding fields are identical except for the conditional bit coutbar in all bitwise cases;

- 3. proving the final goal by combining all cases.

The proof employs both forward and backward (goal-directed) proof techniques. The program implementing the proof procedure of Stage 1 is common to all thirteen cases. Details of this program will be described in Section 4.1.

In Stage 2, the ALU operations can be divided into two groups: the bitwise operations and non-bitwise operations. The latter consists of the following operations: alu\_add, alu\_sub, alu\_inc and alu\_sl. The last operation in this group is slightly different to the other three, it requires some special facts about the relation between addition and shift of binary words. In the bitwise group, operations can be further divided into four subgroups:

binary which consists of alu\_and, alu\_rmb, alu\_nor and alu\_xor;

**unary** which consists of alu\_r, alu\_m and alu\_com;

constant which consists of a single operation alu\_0;

shift which also consists of a single operation alu\_sr.

As examples, three typical operations alu\_and, alu\_add and alu\_sl will be described in detail in the following subsections. The result of this stage is a set of theories, one for each operation. For non-bitwise operations, there is only a single theorem stored in their theories. This theorem asserts the equivalence between the two ALU functions in the following form

$$ALU \, r \, t \, c_{in} \, b \, op = ALU \, 32BIT \, r \, t \, c_{in} \, b \, op \tag{1}$$

where op is one of the non-bitwise operations. For bitwise operations, two theorems will be derived and stored; one for each ALU function in the following form:

$$ALU \, r \, t \, c_{in} \, b \, op = E'_{spec} \tag{2}$$

$$ALU_32BIT r t c_{in} b op = E'_{imp}$$

(3)

These theories are then used in the last stage to derive the final theorem. The final result of the proof is stored in the theory EQUIV which will be described in Section 4.5. The complete theory hierarchy including the model definitions is shown in Figure 6.

### 4.1 The first stage

The task in the first stage is to unfold the ALU definitions to obtain the expressions  $E_{spec}$  and  $E_{imp}$ . What needs to be done is to substitute instances of the lower level functions into the top level ALU functions ALU and ALU\_32BIT. For the specification, the functions BITOP and FIND\_SR are instantiated with a specific ALU operation op, and these are substituted into the ALU specification

Figure 6: Theory hierarchy of the whole verification

ALU which is also instantiated with the same operation op. The manipulation is carried out by the function ALU\_CASE\_RULE which is listed in Section 4.1.1. The resulting theorem is bound to the ML identifier ALU\_SPEC. The expression  $E_{spec}$  is in the form

$$(w_{spec}, \mathsf{WORD}[B_8; B_7; B_6; B_5; B_4; B_3; B_2; B_1; B_0])$$

where  $w_{spec}$  is the operation result and the  $B_i$ 's are the condition bits. Taking alu\_and as an example,

$E_{spec}(alu\_and) = (WNOT (WNOT rbar WAND treg),$ WORD [MSB (WNOT rbar WAND treg);LSB (WNOT rbar);BIT 30 (WNOT rbar);MSB (WNOT rbar);F;T; $<math>\neg(BNVAL (SEG 12 20 (WNOT rbar WAND treg)) = 0);$ BNVAL (SEG 4 16 (WNOT rbar WAND treg)) = 0;  $\neg(BNVAL (SEG 160 (WNOT rbar WAND treg)) = 0)])$

For the implementation, the process of unfolding the definitions is more complicated. This is because there is much more detail. The process is carried out in three steps by three functions whose names are ALU4BIT\_CASES\_RULE, ALU16BIT\_CASES\_RULE and ALU32BIT\_CASES\_RULE. The first function produces an expression representing the output of a 4-bit ALU slice for the given operation *op*. This is used in the next step, in which the function ALU16BIT\_CASES\_RULE produces an expression representing the output of a 16-bit unit. This is in turn used in the final step by the function ALU32BIT\_CASES\_RULE. The theorem returned by this final step is bound to the ML identifier ALU32BIT\_THM. The right hand side of this theorem is in the following form

$$(w_{imp}, \mathsf{WORD}[b_8; b_7; b_6; b_5; b_4; b_3; b_2; b_1; b_0])$$

which is similar to  $E_{spec}$  in structure, but it is much more complicated. The main operation result  $w_{imp}$  has the following tree-like structure in general:

WCAT(

WCAT(

WCAT(

$$(op r_{4,28} t_{4,28}), (op r_{4,24} t_{4,24})),$$

WCAT( $(op r_{4,20} t_{4,20}), (op r_{4,16} t_{4,16}))),$

WCAT(

WCAT( $(op r_{4,12} t_{4,12}), (op r_{4,8} t_{4,8})),$

WCAT( $(op r_{4,4} t_{4,4}), (op r_{4,0} t_{4,0}))))$  (4)

where  $x_{i,j}$  is an *i*-bit segment of the word *x* starting from *j*th bit and *op* is a combination of word operations. Since the ALU is constructed in two tiers, the operand segments are actually expressed in a nested SEG term, for example,  $r_{4,20}$  is SEG 4 4(SEG 16 16 *r*). It may be prefixed by a word negation operator WNOT. For the alu\_and operation,  $w_{imp}(\text{alu_and})$  is the following expression:

| WCAT                                                                                       |

|--------------------------------------------------------------------------------------------|

| (WCAT                                                                                      |

| (WCAT                                                                                      |

| (WNOT                                                                                      |

| (WNOT (SEG 4 12 (SEG 16 16 <i>rbar</i> )) WAND SEG 4 12 (SEG 16 16 <i>treg</i> )),<br>WNOT |

| (WNOT (SEG 48 (SEG 16 16 <i>rbar</i> )) WAND SEG 48 (SEG 16 16 <i>treg</i> ))),            |

| WCAT                                                                                       |

| (WNOT                                                                                      |

| (WNOT (SEG 44 (SEG 16 16 rbar)) WAND SEG 44 (SEG 16 16 treg)),                             |

| WNOT                                                                                       |

| (WNOT (SEG 40 (SEG 16 16 <i>rbar</i> )) WAND SEG 40 (SEG 16 16 <i>treg</i> )))),           |

| WCAT                                                                                       |

| (WCAT                                                                                      |

| (WNOT                                                                                      |

| (WNOT (SEG 4 12 (SEG 16 0 rbar)) WAND SEG 4 12 (SEG 16 0 treg)),                           |

| WNOT                                                                                       |

| (WNOT (SEG 48 (SEG 160 <i>rbar</i> )) WAND SEG 48 (SEG 160 <i>treg</i> ))),                |

| WCAT                                                                                       |

| (WNOT                                                                                      |

| (WNOT (SEG 4 4 (SEG 16 0 <i>rbar</i> )) WAND SEG 4 4 (SEG 16 0 <i>treg</i> )),             |

| WNOT                                                                                       |

| (WNOT (SEG 40 (SEG 160 rbar)) WAND SEG 40 (SEG 160 treg)))))                               |

Similarly, many condition bits  $b_i$  are also involved with very large expressions.

The ML functions implementing the proof procedures described in this section are common to all operations, they are stored in the file alu\_funs.m. This file is loaded when the proof of each operation is performed. The subsections below are the contents of this file.

4.1.1 Function for unfolding the ALU specification The function ALU\_CASES\_RULE unfolds the ALU specification for each operation. It takes a list of theorems and a string op as

its arguments. The string should be the name of one of the ALU operations. The theorems in the list are used in rewriting. It returns a theorem in the form:

word 32 *rbar*, word 32 *treg*  $\vdash$  ALU *rbar treg cin b f lag op* =  $E_{spec}$

where  $E_{spec}$  consists of only basic word operations and possibly the function ADD32 in arithmetic operations.

```

let ALU CASES RULE =

let get defs = map (definition 'COMMON') ['GET AOUT DEF'; 'GET COUT DEF'] in

let defthm = ALU THM1 in

let ALUCON RULE = \opthms th.

(CONV RULE (DEPTH CONV COND CONV)

(PURE ONCE REWRITE RULE [REFL CLAUSE] (SUBS opthms th))) in

let notths = t1 (CONJUNCTS NOT_CLAUSES) in

let opconst =

let 1st = CONJUNCTS (theorem 'COMMON' 'alu op const dist') in

(map (\t. MATCH MP NOT F t) (1st @ (map NOT EQ SYM 1st))) in

\thms op.

(let tm = mk const(op, ":alu op") in

let opthms = filter (\t. ((lhs o lhs) (concl t)) = tm) opconst in

let bthm = ALUCON RULE opthms (SPEC tm BITOP THM1) in

let rmthm = RIGHT CONV RULE (TOP DEPTH CONV COND CONV)

(PURE ONCE REWRITE RULE [REFL CLAUSE]

(SUBS opthms (SPECL ["MSB(treg: (bool)word)";tm]

(definition 'COMMON' 'GET RM31 DEF')))) in

(PURE_REWRITE_RULE (rmthm . thms)

(repeat1 8 (RIGHT_CONV_RULE let_CONV)

(PURE ONCE REWRITE RULE get defs

(RIGHT_CONV_RULE ((RAND_CONV (REWR CONV bthm)) THENC let CONV)

(SPEC tm ALU_THM1)))));;

```

4.1.2 Function for unfolding the 4-bit ALU slice The function ALU4BIT\_CASES\_RULE unfolds the 4-bit ALU implementation for each operation. It takes two arguments: the first is a list of theorems to be used in rewriting, and the second is a string specifying the operation. let ALU4BIT\_CASES\_RULE =

```

let ALUCON_RULE = \opthms th.

(CONV_RULE (DEPTH_CONV COND_CONV)

(PURE_ONCE_REWRITE_RULE [REFL_CLAUSE] (SUBS opthms th))) in

let def_thm = (GEN_RR_RULE (definition `ALUBIT` `ALU_4BIT_DEF`)) in

let notths = tl (CONJUNCTS NOT_CLAUSES) in

let opconst =

let lst = CONJUNCTS (theorem `COMMON` `alu_op_const_dist`) in

(map (\t. MATCH_MP NOT_F t) (lst @ (map NOT_EQ_SYM lst))) in

\ths op. (

let tm = mk_const(op, ":alu_op") in

let opthms = filter (\t. ((lhs o lhs) (concl t)) = tm) opconst in

let rmth = GEN_ALL(ALUCON_RULE opthms (SPECL ["t31:bool";tm]

(definition `COMMON` `GET_RM31_DEF`))) in

let bthm = ALUCON_RULE opthms (SPEC tm FOURBITOP_THM1) in

```

```

let wthm = GEN_ALL (SYM (AP_THM

(definition `WORD_WIDTHS` `word4_def`)"w:(bool)word")) in

let thm1 = UNDISCH_ALL (SPEC "r4bar:(bool)word"

(PURE_ONCE_REWRITE_RULE[wthm](RESQ_HALF_SPEC

(SPEC "4" (MATCH_MP (RESQ_HALF_SPEC PBITOP_PWORDLEN) PBITOP_WNOT))))) in

(GEN_ALL (RESQ_GEN_ALL (PURE_REWRITE_RULE (rmth . ths) (LET_LAM_RULE

(RIGHT_CONV_RULE (RAND_CONV (RESQ_REWRITE1_CONV [thm1] bthm))

(RIGHT_CONV_RULE let_CONV

(SPEC_ALL(RESQ_SPEC_ALL(SPEC tm def_thm))))))))));;

```

4.1.3 Function for unfolding the 16-bit ALU definition This function unfolds the 16-bit ALU implementation for each operation. It takes three arguments: the first is a theorem returned by the function ALU4BIT\_CASES\_RULE of the same operation; the second is a list of theorems to be used in rewriting, and the last is a string specifying the operation.

```

let ALU16BIT_CASES_RULE =

let defthm = GEN ROR BLOCK RULE 4 (definition 'ALUBIT' 'ALU 16BIT DEF') in

\th4 thms op.

(let tm = mk_const(op, ":alu_op") in

let thm1 = (SPECL (replicate tm 4) defthm) in

let thm2 = (repeat1 7 (RIGHT CONV RULE let CONV)

(SPEC ALL (RESQ SPEC ALL thm1))) in

let unfold4 = k th.

(repeatl 2 (RIGHT CONV RULE let CONV)

(PURE REWRITE RULE [FST; SND] (RIGHT CONV RULE let CONV

(RIGHT_CONV_RULE (RAND_CONV

(RESQ_REWRITE1_CONV

(map (SEG PWL CONV "4" k "16")

["r16bar: (bool)word"; "t16reg: (bool)word"]) th4)) th)))) in

GEN ALL (RESQ GEN ALL (PURE REWRITE RULE thms

(itlist unfold4 ["12"; "8"; "4"; "0"] thm2))));;

```

4.1.4 Function for unfolding the 32-bit ALU implementation This function unfolds the 32-bit ALU implementation for each operation. It takes three arguments: the first is a theorem returned by the function ALU16BIT\_CASES\_RULE of the same operation; the second is a list of theorems to be used in rewriting, and the last is a string specifying the operation.

```

let ALU32BIT_CASES_RULE =

\thm16 thms op.

let OP = mk_const(op, ":alu_op") in

let unfold16 = \k th.

(repeatl 2 (RIGHT_CONV_RULE let_CONV)

(RIGHT_CONV_RULE (RAND_CONV (RESQ_REWRITE1_CONV

(map (SEG_PWL_CONV "16" k "32")

["rbar:(bool)word"; "treg:(bool)word"]) thm16)) th)) in

(PURE_REWRITE_RULE (thms)

(RIGHT_CONV_RULE (let_CONV THENC (DEPTH_CONV BIT_CONV))

(PURE_ONCE_REWRITE_RULE [definition `ALUBIT` `ZERO_GATES_DEF`)]

(repeatl 2 (RIGHT_CONV_RULE let_CONV)

```

(itlist unfold16 ["16"; "0"] (SPEC OP ALU 32BIT THM1))))));;

### 4.2 Stage 2: bitwise operations

This section describes Stage 2 of the the proof for bitwise operations. As a typical operation of this group, the results of the bitwise AND operation alu\_and is shown as an example. At the end of Stage 1, as described in Section 4.1, two theorems stating the operation results have been derived. The expression  $E_{imp}$ representing the result at the implementation level is very large. The aim of this stage is to simplify this expression using the properties of word operations so that each corresponding fields between  $E_{imp}$  and  $E_{spec}$  will be equivalent, i.e.,  $w_{imp}$  becomes  $w_{spec}$  and  $b_i$  becomes  $B_i$  for i = 0, 1, 2, 4, 5, 6, 7, 8. In essence, the difference between  $E_{spec}$  and  $E_{imp}$  is that the bitwise operators are applied to their 32-bit operands directly in the former expression while the same combination of operators are applied to a number of 4-bit segments and the results are concatenated to form a 32-bit word in the latter. The strategy for proving the equivalence of these two methods of performing the same operations relies on the basic properties of word operations. The word library provides all the required theorems which assert these general properties of words and operations on words.

The strategy for unifying these two expressions is common to all bitwise operations. It is implemented as an ML function simp\_bitop which will be listed in Section 4.2.1, but before looking at the details of the function, the strategy is explained first. This can be divided into five steps:

1. Reduce the nested SEG introduced by the two tier structure of the ALU implementation using the theorem SEG\_SEG.

HOL Theorem (SEG\_SEG)

- $\vdash \forall n. \forall w :: \mathsf{PWORDLEN} n. \forall m_1 k_1 m_2 k_2. \\ k_1 + m_1 \le n \land k_2 + m_2 \le m_1 \supset \\ (\mathsf{SEG} m_2 k_2 (\mathsf{SEG} m_1 k_1 w) = \mathsf{SEG} m_2 (k_1 + k_2) w)$

- 2. Move the bitwise operators, such as WNOT, WAND and so on, inside SEG. This is possible because they all satisfy the predicate PBITOP or PBITBOP and have the property stated in the theorems PBITOP\_SEG and PBITBOP\_SEG.

HOL Theorem (PBITOP\_SEG)

$\vdash \forall op :: \mathsf{PBITOP}.$

$\forall n. \forall w :: \mathsf{PWORDLEN} n. \forall k m.$

$k + m \le n \supset (op (\operatorname{SEG} m k w) = \operatorname{SEG} m k (op w))$

#### HOL Theorem (PBITBOP\_SEG)

$\vdash \forall op :: \mathsf{PBITBOP}.$

$\forall n. \forall w_1 w_2 :: \mathsf{PWORDLEN} n. \forall k m.$

$k+m \leq n \supset (op \left(\mathsf{SEG}\,m\,k\,w_1

ight)\left(\mathsf{SEG}\,m\,k\,w_2

ight) = \mathsf{SEG}\,m\,k\,(op\,w_1\,w_2)

ight)$

3. Remove WCAT at three nested levels using the theorem WCAT\_SEG\_SEG.

HOL Theorem (WCAT\_SEG\_SEG)

$\vdash \forall n. \forall w :: PWORDLEN n. \forall k m_1 m_2.$   $k + m_1 + m_2 \le n \supset$  $(WCAT (SEG m_2 (k + m_1) w, SEG m_1 k w) = SEG (m_1 + m_2) k w)$

4. The result of the above three steps is that the expression representing the main operation result  $w_{imp}$  becomes

### SEG 32 32 w

where w involves only bitwise operators and the operands. More specifically, the expression for alu\_and operation is

SEG 32 32 WNOT (WNOT *rbar* WAND *treg*).

According to the theorem SEG\_WORD\_LENGTH, this can be reduced to w which should be identical to  $w_{spec}$ .

HOL Theorem (SEG\_WORD\_LENGTH)

$\vdash \forall n. \forall w :: \mathsf{PWORDLEN} n. \mathsf{SEG} n \, \mathsf{0} \, w = w$

As the result of this step,  $w_{imp}$  has been reduced to equal  $w_{spec}$ . At the same time, the expressions representing the conditional bits  $b_i$ 's have also been simplified to certain extent. The remaining steps work only on the condition bits.

5. use the theorem BIT\_SEG to simplify the condition bits aout31, r0, r30 and r31.

HOL Theorem (BIT\_SEG)

$\vdash \forall n. \forall w :: PWORDLEN n. \forall j k m.$  $k + m \le n \supset (j < m \supset (BIT j (SEG m k w) = BIT (j + k) w))$

The expression representing aout31 for alu\_and before this step is

BIT 0(SEG 40  $w_{spec}(alu\_and))$

which will be simplified to BIT 0  $w_{spec}(alu\_and)$ .

6. The remaining condition bits, namely nztop12, zmid4 and nzbot16, indicates the zero condition of the operation result. On the specification level, they are expressed in terms of equality test between the value of the appropriate segments of the result and 0(zero). The expressions for alu\_and are:

$$B_0 = \neg (BNVAL(SEG 160 ((WNOT rbar) WAND treg)) = 0)$$

$$B_1 = BNVAL(SEG 416 ((WNOT rbar) WAND treg)) = 0)$$

$$B_2 = \neg (BNVAL(SEG 1220 ((WNOT rbar) WAND treg)) = 0)$$

Whilst on the implementation level, they are expressed in terms of equality test between segments of the results and a zero valued word NBWORD 40. The expression for alu\_and are:

$$b_0 = \neg (WORD[SEG 4 12 w = NBWORD 4 0;SEG 48 w = NBWORD 4 0;SEG 44 w = NBWORD 4 0;SEG 40 w = NBWORD 4 0] = WORD[T; T; T; T])$$

$$b_1 = SEG 4 16 w = NBWORD 4 0b_2 = \neg (WORD[SEG 4 28 w = NBWORD 4 0;SEG 4 24 w = NBWORD 4 0;$$

SEG 4 20 w = NBWORD 4 0] = WORD[T; T; T])

where w is the expression ((WNOT *rbar*) WAND *treg*). The general theorems required to unify the corresponding bits between the two levels are ZERO\_WORD\_VAL and EQ\_NBWORDO\_SPLIT.

HOL Theorem (ZERO\_WORD\_VAL)

$$\vdash \forall n. \forall w :: PWORDLEN n.$$

$$(w = NBWORD n 0) = (BNVAL w = 0)$$

HOL Theorem (EQ\_NBWORDO\_SPLIT)

$$\vdash \forall n. \forall w :: PWORDLEN n.$$

$$\forall m. m \le n \supset$$

$$((w = NBWORD n 0) =$$

$$(SEG (n - m) m w = NBWORD (n - m) 0) \land$$

$$(SEG m 0 w = NBWORD m 0))$$

The first theorem states that an equality test between an *n*-bit word and a zero valued word of the same size is equal to a test between the value of the word and zero. The second theorem states that an equality test between an *n*-bit word and a zero valued word of the same size can be split into two parts. Since the indexes in the expressions  $b_i$ 's and  $B_i$ 's are all constants, three theorems matching these expressions are obtained by instantiating the general theorems. They are stored in the theory ALU\_WORD so they can be used in all proofs for bitwise operations.

The proof script for the bitwise group is organized into several files. ML functions implementing proof procedures common to all bitwise operations and theorems required for all bitwise operations are stored in the file alu\_bitop\_funs.m. There is a separate file, the driver file, for each operation. They are named by prefixing the operation name to '\_thm.m'. For instance, the file for the alu\_and operation is alu\_and\_thm.m. These driver files contain function calls and instances of theorems specific to each operation. The first subsection below shows the function simp\_bitop in the file alu\_bitop\_funs.m. The remaining subsections lists the file alu\_and\_thm.m.

**4.2.1** The function simp\_bitop This is the function for simplifying the result of the bitwise operations. It takes three arguments: the first *thm1* should be the theorem derived from unfolding the ALU implementation, i.e., ALU\_32BIT\_THM; the second *sthms* is a list of theorems to be substituted into *thm1* to simplify the latter, the last argument *tm* is the expression representing the main result specified in the ALU\_SPEC, i.e., the term  $w_{spec}$  which is the target of the simplification.

```

let simp binop =

let eqT = GEN ALL (el 2 (CONJ LIST 4 (SPEC_ALL EQ CLAUSES))) in

let cond1_lem = GEN_ALL (DISCH_ALL (PURE REWRITE RULE[IMP CLAUSES]

(CONV_RULE ( (ONCE_DEPTH_CONV ADD CONV) THENC

(LHS_CONV LESS_EQ_CONV) THENC ((RAND CONV o LHS CONV) LESS CONV))