Number 245

# System support for multi-service traffic

Michael J. Dixon

January 1992

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 http://www.cl.cam.ac.uk/

#### © 1992 Michael J. Dixon

This technical report is based on a dissertation submitted September 1991 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Fitzwilliam College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# **Preface**

Except where otherwise stated in the text, this dissertation is the result of my own work and is not the outcome of work done in collaboration.

This dissertation is not substantially the same as any I have submitted for a degree or diploma or any other qualification at any other university.

# Acknowledgements

I would like to thank my supervisor, Jean Bacon, for her encouragement and advice during my time as a research student. Special thanks are due to Mike Burrows, Mark Hayter, Derek McAuley, Cosmos Nicolaou and many other members of the Computer Laboratory for helpful discussions over the years. I would like to thank Roger Needham, Head of the Computer Laboratory, for his support, and for allowing me time to spend one summer as an intern at the DEC Systems Research Centre, Palo Alto. Thanks are also due to Sape Mullender and his colleagues at CWI for providing access to the Amoeba source code. The starting point they provided has been invaluable. The WANDA system as presented is the result of contributions by many people. However, Mark Hayter, Glenford Mapp and Tim Wilson deserve special mention. I am grateful to Andy Hopper for encouraging the close ties that exist between the Computer Laboratory and Olivetti Research Limited. In particular, David Greaves at Olivetti has been a source of help on all matters concerning the Cambridge Backbone Network. The dissertation has benefitted from inspection by the careful eyes of Jean Bacon, Richard Black, Andy Gordon, Andy Harter, Mark Hayter, Derek McAuley and Cosmos Nicolaou. The work was supported by a studentship from the Science and Engineering Research Council. Finally, I am grateful for support from the Fairisle project in my final year.

# Summary

Digital network technology is now capable of supporting the bandwidth requirements of diverse applications such as voice, video and data (so called multi-service traffic). Some media, for example voice, have specific transmission requirements regarding the maximum packet delay and loss which they can tolerate. Problems arise when attempting to multiplex such traffic over a single channel. Traditional digital networks based on the Packet- (PTM) and Synchronous- (STM) Transfer Modes prove unsuitable due to their media access contention and inflexible bandwidth allocation properties respectively. The Asynchronous Transfer Mode (ATM) has been proposed as a compromise between the PTM and STM techniques. The current state of multimedia research suggests that a significant amount of multi-service traffic will be handled by computer operating systems. Unfortunately conventional operating systems are largely unsuited to such a task. This dissertation is concerned with the system organisation necessary in order to extend the benefits of ATM networking through the endpoint operating system and up to the application level. A locally developed micro-kernel, with ATM network protocol support, has been used as a testbed for the ideas presented. Practical results over prototype ATM networks, including the 512 MHz Cambridge Backbone Network, are presented.

# Contents

| Glo | ossary of Terms                        | v  |

|-----|----------------------------------------|----|

| 1   | Introduction                           | 1  |

| 2   | The Multi-Service Network Architecture | 5  |

| 3   | WANDA MSNA Implementation              | 17 |

| 4   | The Cambridge ATM Backbone             | 33 |

| 5   | Quality of Service Issues              | 39 |

| 6   | Quality of Service Extensions          | 51 |

| 7   | Experimental Programme                 | 67 |

| 8   | Related Work                           | 87 |

| 9   | Further Work                           | 93 |

| 10  | Conclusion                             | 99 |

| Ri  | Bibliography                           |    |

# Glossary

**AAL** ATM Adaptation Layer

ANSA Advanced Networks Systems Architecture

ATM Asynchronous Transfer Mode

**B-ISDN** Broadband Integrated Services Digital Network

CBN Cambridge Backbone Network

CBR Constant Bit Rate

CCITT Comitée Consultatif International Télégraphique et Téléphonique

CDCS Cambridge Distributed Computing System

CFR Cambridge Fast Ring

COW Copy On Write

**DAN** Desk Area Network

**DARPA** Defence Advanced Research Projects Agency

**DMA** Direct Memory Access

**EOF** End Of Frame

FCS Frame Check Sequence

FCFS First Come First Serve

FIFO First In First Out

FIQ Fast Interrupt reQuest

FPC Fairisle Port Controller

FTP File Transfer Protocol

FQ Fair Queueing

**HOL** Head Of Line

IMAC Integrated Multimedia Applications Communications architecture

IOP Input/Output Processor

IP Internet Protocol

IPC Inter-Process Communication

IPI Inter-Processor Interrupt

IRQ Interrupt ReQuest

ISDN Integrated Services Digital Network

ISO International Standards Organisation

IPL Interrupt Priority Level

ISR Interrupt Service Routine

LAN Local Area Network

MAC Media ACcess layer

MS-Access Multi-Service media Access

MSDL Multi-Service DataLink

MSN Multi-Service Network

MSNA Multi-Service Network Architecture

MSNL Multi-Service Network Level

MSSAR Multi-Service Segmentation And Reassembly

NAK Negative AcKnowledgement

NCS Network Computing System

ORL Olivetti Research Limited

OSF Open Software Foundation

OSI Open System Interconnection

PDU Protocol Data Unit

PTM Packet Transfer Mode

QOS Quality Of Service

RPC Remote Procedure Call

SAP Service Access Point

SAR Segmentation And Reassembly

SAS Single Address Space

SDU Service Data Unit

**SOF** Start Of Frame

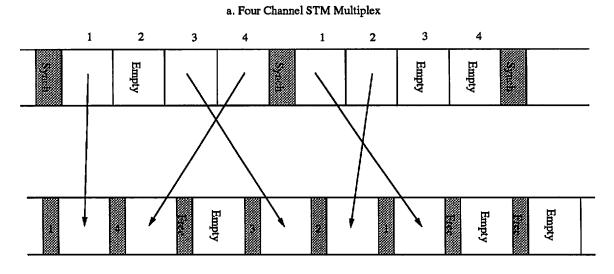

STM Synchronous Transfer Mode

TAS Test And Set

TCP Transmission Control Protocol

TDM Time Division Multiplexing

TLB Translation Lookaside Buffer

VBR Variable Bit Rate

VC Virtual Circuit

VCI Virtual Circuit Identifier

VPI Virtual Path Identifier

# Chapter 1

# Introduction

The last decade has seen the emergence of the Integrated Services Digital Network (ISDN): a network based upon digitally switched, fixed capacity, narrowband circuits. Whilst still being only partially deployed, it is apparent that the original ISDN will be unable to support many future broadband customer requirements. The Broadband ISDN (B-ISDN) [CCITT88] is envisaged as an extension to the original network in order to meet such needs.

The Asynchronous Transfer Mode (ATM) is the transfer mode selected by the CCITT for implementing the B-ISDN. ATM represents a compromise between the Packet- (PTM) and Synchronous- (STM) Transfer Modes of operation. An ATM network is concerned with the transfer of fixed sized data units called *cells*. It is asynchronous in the sense that the recurrence of cells containing information from an individual user is not necessarily periodic. If ATM is to be a successful compromise then it must be able to meet the demands of both traditional STM and PTM clients. In particular STM networks offer guarantees regarding the *Quality of Service* (QOS) that a client can expect, typically in terms of bounded jitter, delay and bandwidth. For an ATM network to accept such a call requires that all network elements, particularly switching nodes, should be able to support the requested QOS for the call path and duration. The situation is complicated by the fact that an ATM network has to support calls with different QOS attributes simultaneously.

This dissertation is concerned with the design and construction of systems components, in particular endpoint and router software, for ATM networks which provide guarantees regarding QOS to users on a per call basis. The work has been carried out over a set of heterogeneous ATM network implementations, all initially developed at the University of Cambridge Computer Laboratory.

# 1.1 The Cambridge ATM Environment

Much of the work described in the dissertation is of a practical nature. This was made possible by the production of ATM hardware by related projects in the Computer Laboratory. In addition, Olivetti Research Limited (ORL), Cambridge, shared an active interest in ATM network and applications research. A summary of the major active projects is given below.

The Pandora project [Hopper90] is a joint undertaking between ORL and the Computer Laboratory. The project aim is to provide multimedia facilities integrated into the workstation environment. It uses an ATM network, the Cambridge Fast Ring (CFR) [Hopper88], for voice and video transport. By late 1990 Pandora workstations were deployed and in everyday use at three sites in Cambridge connected by a single CFR.

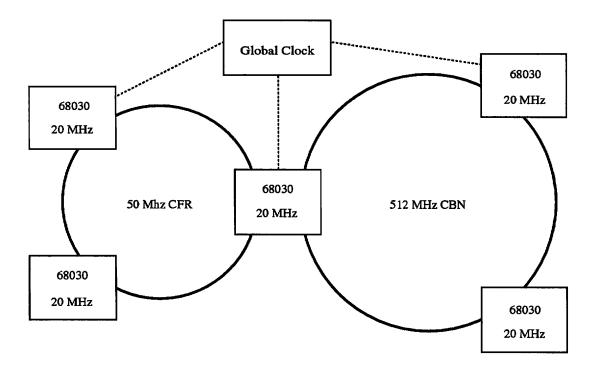

The Cambridge Backbone Network (CBN) [Greaves90], a slotted ring system like the CFR, was designed to interconnect CFR networks in the metropolitan area, and consequently shares the same cell format. By late 1990 a five station CBN with a 512 MHz line rate was operational, though inter-connectivity with other ATM networks had yet to be demonstrated.

The Fairisle project [Leslie91] is a joint undertaking between the Computer Laboratory and HP Laboratories, Bristol. The initial project aim is to build an experimental ATM network based on the Cambridge Fast Packet Switch [Newman89]. The network architecture is based on the Multi-Service Network Architecture (MSNA) [McAuley90]. The aim of MSNA is to support multi-service inter-network applications, particularly over ATM style networks. By late 1990 the first Fairisle hardware was built and being debugged.

The early Pandora infrastructure was incapable of operation outside a single CFR. Whilst this was enough for many useful applications and experiments to be performed, the benefits of inter-networking had yet to be realised. It was clear that the project would soon outgrow the original ring both in terms of aggregate bandwidth required and geographical area covered. As a result early 1990 saw the adoption of the MSN architecture by the project. Although the architecture defined an internetworking facility there was no support for QOS. In order for Pandora applications to inter-network properly it was apparent that routers would have to be constructed that both defined and implemented QOS. The desire to have system servers handle media produced by Pandora leads to the examination, in the next section, of the systems environment then available.

# 1.2 The Cambridge Systems Environment

WANDA is an experimental kernel being developed at the Computer Laboratory in part by the author. It evolved from experience gained with the Amoeba operating system [Tanenbaum87] by the Computer Laboratory Systems Research Group. The kernel is intended primarily for use as a systems research vehicle. It is not envisaged that it should support a conventional operating system environment, e.g. UNIX, or that program development take place over WANDA.

Both kernel and user programs are built on UNIX systems using GNU C cross-compilers. Each WANDA machine contains a set of ROMs which allow it to boot a kernel image from the UNIX file system. Once the kernel is started mechanisms exist to run user applications dynamically, with the executable binary again being downloaded from UNIX.

The kernel was initially developed on the VAX architecture, in particular the DEC SRC Firefly [Thacker87] multiprocessor. By late 1990 it had been ported to 68000, 68020 and 68030 series VME systems and all generations of the Acorn ARM processor [VLSI87]. For each processor at least one of Ethernet, CFR, CBN or Fairisle type host interfaces exist.

The Advanced Network Systems Architecture Testbench [ANSA89], which is available for the UNIX, VMS and MS-DOS operating systems, provides support for distributed programming. In particular it is available on most Computer Laboratory UNIX machines. The Testbench has been ported by the author to run over WANDA. The SUN Remote Procedure Call (RPC) [SUN86] protocol is also supported over WANDA.

Recent systems research at Cambridge [Nicolaou91] suggested that many clients requiring QOS from the network would be software elements in a distributed computing environment. If such clients were to be satisfied then QOS would have to be extended from the network, through the endpoint operating system, to the application.

Given that the WANDA kernel already supported the MSN protocol suite (with drivers for the Ethernet, CFR and CBN already written) and that the Fairisle project had selected WANDA as the basis for their control software it was natural that it be chosen as the vehicle for research into the system requirements for handling multi-service traffic. The ability to support a sophisticated distributed computing environment on elements inside the network promised to be useful if the implementation of complex control and management algorithms proved necessary.

#### 1.3 Outline

Chapter 2 reviews the MSN architecture and examines its relationship to the OSI reference model. The draft B-ISDN architecture is described. It is argued that results derived from experimentation with either architecture are applicable to the other. Subsequently the dissertation concerns itself primarily with the MSN architecture.

Chapter 3 begins with a description of the WANDA system architecture and philosophy. The WANDA networking architecture and the associated MSNA protocol suite implementation, prior to the incorporation of any QOS functionality, is then discussed in detail. Of particular interest is the MSNL router implementation.

Chapter 4 describes the construction of a prototype ATM network. The Cambridge ATM Backbone is used to switch voice, video and data traffic between ORL and the Computer Laboratory. The implementation is based on the work described in the previous two chapters.

Chapter 5 looks at the issues surrounding the incorporation of QOS into a network architecture. The support of multi-service traffic, with QOS guarantees, over ATM style networks is emphasised. Techniques for providing QOS in both the endpoints and routers are examined. It is shown that these techniques display a marked overlap.

Chapter 6 presents the extensions made to the WANDA interface that enable different QOS policies to be supported. The chapter concludes with a discussion of the interface implementation over the networks described in Chapter 2.

Chapter 7 examines the behaviour of the extended WANDA system when handling delay-sensitive traffic. A series of experiments is performed using the CBN and CFR networks. Proposals are made concerning the structure of future ATM network host interfaces.

Chapter 8 places the work described previously in the context of current research. Chapter 9 outlines some areas of further research necessary before building production ATM networks able to provide QOS guarantees. In addition future ATM research planned at the Computer Laboratory and ORL is outlined. Concluding remarks are presented in Chapter 10.

# Chapter 2

# The Multi-Service Network Architecture

The aim of the Multi-Service Network Architecture (MSNA) [McAuley90] is to provide a complete architecture which allows multimedia applications to use the full facilities of ATM networks in an inter-networking environment. The architecture is based upon the virtual circuit model, and so shares many characteristics with the proposed B-ISDN. This chapter describes MSNA and its realisation over a set of heterogeneous networks.

## 2.1 The Virtual Circuit Model

Both B-ISDN and MSNA define a virtual circuit (VC) model of operation. Each packet or cell comprises:

Figure 2.1: Generic virtual circuit cell format

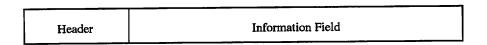

At the very least the header contains a virtual circuit identifier (VCI) which enables the receiver to establish which circuit an incoming cell belongs to. Since a VCI is unidirectional a single hop circuit is described by a pair of VCIs. As the VCI is only interpreted locally it can be made small, an important consideration given the small sizes of ATM cells. An n-hop VC may be formed by the concatenation of n single hop VCs through (n-1) VC gateways.

It is not necessarily the case that the same header encoding is used on heterogeneous networks. However, the contents of the information field must be preserved. The primary function of a VC gateway is header (i.e. VCI) re-mapping on a per cell basis, illustrated in Figure 2.2. A small VCI enables a gateway to use simple techniques, such as table lookup, when performing the translation. Likewise processing in the end system is simplified.

Figure 2.2: Virtual circuit gateway

The simplicity of cell forwarding makes implementation of a hardware router an attractive possibility. The computational part (i.e. not including any queueing delays) of cell processing can be implemented in constant time and therefore a host (end system/router) can gauge its capacity effectively. This is important if it is to make guarantees concerning QOS.

## 2.2 The MSN Architecture

The MSN architecture defines three layers which contribute to the inter-networking service:

- MSDL and MS-Access (datalink level),

- MSNL (network level).

## 2.2.1 The MSDL Layer

The multi-service datalink layer (MSDL) defines lightweight virtual circuits, referred to as associations, over heterogeneous networks. MSDL addressing is in terms of VCIs. Each cell or packet transmitted is accompanied by a VCI which uniquely identifies an association in the context of the receiving MSDL entity. A VCI pair

defines an association over a particular datalink. The MS-Access layer deals with the encodings necessary to transfer MSDL service data units (SDUs) over heterogeneous networks (e.g. VCI format). The header format is guided by the characteristics of the underlying network. The MSDL SDU size bears historical dependencies on the Cambridge Fast Ring (CFR) [Hopper88], upon which it was first defined. Although the MSDL SDU is fixed sized, multiple SDUs (all for the same association) may be presented in a single MS-Access request. The maximum number of SDUs which can be presented is defined by the instance of MS-Access being used. Similarly an MS-Access indication may represent the arrival of several MSDL SDUs (all for the same association).

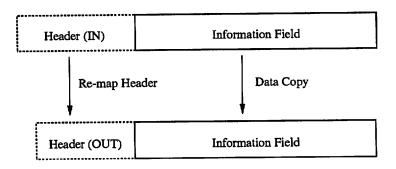

#### MSDL on the CFR/CBN

Figure 2.3: Encoding of MSDL in a CFR slot

Over the CFR the MSDL header is encoded in the Media Access (MAC) -layer source and destination addresses (Figure 2.3). The first 16 bits of the header comprise the destination VCI. At first sight this would seem to allow only one association per interface. However, when operating in bridge mode a CFR interface can accept cells on multiple dynamically assigned addresses. On initialisation each interface is allocated a disjoint portion of the MAC-layer address space from which it can assign VCIs. Intra- and inter-node multiplexing is thus achieved using the same 16 bits of address information. A maximum of 32 octets remains in the CFR slot; this becomes the MSDL SDU size. The Cambridge Backbone Network (CBN) [Greaves90] comprises a fibre optic ring whose bandwidth is partitioned into a number of Time Division Multiplexed (TDM) channels (currently four). Stations of varying cost and bandwidth may be constructed, parameterised by the number of channels they can use concurrently. Media access control is through the empty slot technique, with

transmitting stations able to fill *multiple* slots each ring revolution. Since the CBN has the same slot structure as the CFR, the format of Figure 2.3 was used to define MSDL on the CBN also.

#### CFR Interface

The CFR chip set includes an ECL repeater and CMOS station chip. The repeater chip serialises and de-serialises data from the ring so that the station chip may handle it at an appropriate speed. The station chip contains a single transmit and a single receive FIFO each with a one cell capacity. It is possible to program the station chip to generate an indication of both when the receive FIFO contains a cell and when the transmit FIFO is empty. No interface supporting Direct Memory Access (DMA) has yet been built so all data must be moved between the station chip and host memory using processor cycles.

#### CBN Interface

So far only a single type of CBN interface has been built, which is for the VME bus [Greaves91]. The interface consists of four transmit (one for each CBN channel) and one receive FIFO. Unlike the CFR each FIFO has a capacity of 256 cells. The FIFO RAM array is shared by both the receive and transmit sides of the station and so the interface is limited to a half-duplex mode of operation. The receive interrupt condition is programmable on a per VCI basis. It can be set to interrupt on every cell received or only when a cell with an end of frame bit set is received. Later versions of this interface include support for DMA.

#### MSDL on the Ethernet

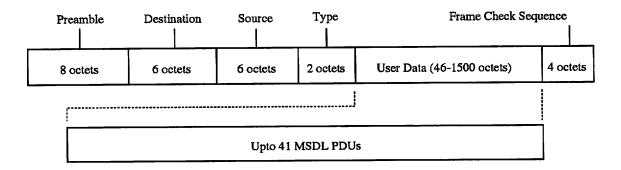

Figure 2.4: Encoding of MSDL in an Ethernet frame

The Ethernet [Metcalfe76] shares few characteristics of the CFR/CBN. In particular it allows variable size packet transmission. In order to use the network effectively multiple MSDL protocol data units (PDUs) must be sent in a single Ethernet packet (Figure 2.4). The peer MSDL host is identified by the 48 bit Ethernet MAC-layer address. The peer MSDL entity is identified by a 16 bit VCI (chosen for convenience to be the same size as the CFR/CBN VCI). The number of MSDL PDUs, all for the same association, can be ascertained from the length of the Ethernet packet.

#### Ethernet Interface

Due to the commercial success of the Ethernet much effort has been expended on producing high performance interfaces. Both the DEQNA [DEC86] and LANCE [AMD85] interfaces are used by WANDA systems in the Computer Laboratory. These interfaces use a ring of transmit and a ring of receive descriptors in main memory. Transmission and reception is done by DMA to and from the regions defined by the descriptor rings. An interrupt may be generated upon the emptying or filling of a buffer by the interface. A protocol is defined to allow concurrent access by the host and interface to the descriptor rings. By using large packets and a suitable memory system a host may achieve close to 100% utilisation of an Ethernet with one of these interfaces.

#### MSDL on the Fairisle network

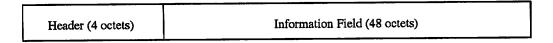

Figure 2.5: Initial Fairisle Cell Format

The Fairisle network [Leslie91] is an ATM network based on fast packet switching. Before a cell is injected into the switching fabric a routing tag must be prepended. Each stage in the fabric strips the first octet from the tag and forwards the cell according to the route specified in it. Upon arrival at the destination port the entire routing tag has been removed. The tag is analogous to the Ethernet MAC-layer address except that the same output port may have a different tag dependent upon which input port it is referenced from. The Fairisle design and hardware allow great flexibility in choosing the cell format. The initial layout is shown in Figure 2.5. As the information field is neither variable size nor an integral number of MSDL SDUs, the initial implementation of MS-Access over Fairisle assigns the first 32 octets of the information field to be the MSDL SDU (the remaining bytes being unassigned). The 33% loss in maximum throughput that this represents is addressed in Section 5.7.

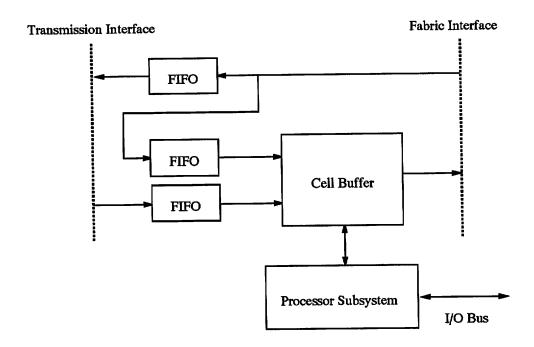

#### Fairisle Interface

The Fairisle Port Controller (FPC) [Hayter91a] is attached to an input and output port on a Fairisle Switch Fabric. The port controller also has input and output interfaces to a transmission system. Cells received from the transmission system are buffered in the FPC cell buffer: thus a Fairisle switch is input buffered. The FPC control processor, an ARM3 [VLSI90], may arrange to be interrupted on receipt of a cell. The processor performs VCI re-mapping (implemented in hardware in later versions) determining which output port (if any) the cell is destined for. The cell is then linked into an appropriate transmit queue in the cell buffer. At no point does the processor need to manipulate the data portion of the cell.

Figure 2.6: Fairisle Port Controller Schematic

Cells received from the fabric are either looped back into the cell buffer (typically for management) or passed through to the transmission system depending on a bit in the port controller portion of the routing tag.

A VME host interface has been designed and built [Beeler91] which attaches to the FPC transmission interface. The interface is half duplex and is only capable of VME slave operation. It supports 32 bit memory mapped accesses on a set of transmit and receive FIFOs. An interrupt is generated when data is received from the port controller and also when either of the FIFOs overrun. In an alternative mode of operation the VME interface is able to attach directly to the synchronous fabric interface.

#### 2.2.2 The MSNL Layer

The previous sections have discussed MSNA at the datalink layer as defined by the MSDL and MS-Access layers. The multi-service network layer (MSNL) extends associations into an inter-networking environment. An MSNL liaison is a concatenation of MSDL associations. Liaisons are not multiplexed over associations. MSNL adds no protocol overhead to the data stream: the MSNL PDU and SDU are equivalent and defined to be the size of the MSDL SDU (32 octets). Once a liaison is established, an MSNL gateway is concerned with the forwarding of MSDL SDUs (although logically this is performed at the MSNL layer). To provide the inter-networking function MSNL defines both MSNL addresses and connection establishment procedures. An MSNL address, representing a service access point (SAP) comprises:

- a 4 octet MSNL identifier,

- a 4 octet MSNL port.

Typically there is a one-to-one mapping between an MSNL identifier and a single host. However, it is possible for several hosts to share the same MSNL identifier or, more commonly, for a single host to have multiple MSNL identifiers. An MSNL port identifier is allocated to an MSNL client either when a client registers an interest in listening for liaisons, or when it requests establishment of a liaison (Section 2.4).

## 2.3 B-ISDN

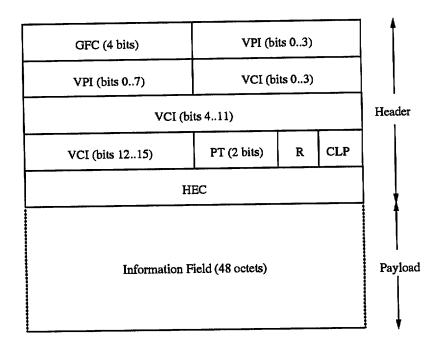

The ATM layer in the B-ISDN architecture provides functionality similar to that of MSNL. Figure 2.7 shows the format of the B-ISDN ATM cell. The Virtual Circuit Identifier above has been split in B-ISDN terminology into the Virtual Path Identifier (VPI) and Virtual Channel Identifier (VCI). The cell loss priority bit (CLP) if not set by the user identifies a cell which could be dropped (in preference to one which has the CLP bit set) during times of congestion. The payload type (PT) field is used to provide an indication of the information field content type. The hardware error control (HEC) field provides single- or multiple-bit error detection capabilities on the cell header.

The B-ISDN definition represents a set of interfaces; it does not specify the implementation of an ATM network. So long as a network conforms to that interface it can be part of a B-ISDN. The MSN architecture should therefore be regarded as complementing rather than competing with B-ISDN. An MSNA network should be able to carry B-ISDN traffic and vice-versa. Chapter 5, in particular Section 5.7, describes some of the issues associated with such an undertaking.

Figure 2.7: B-ISDN Cell Format

A router at the centre of an ATM network will be expected to handle the cells for a large number of connections. This does not imply that a router has to maintain state on each connection. Cells with the same source and destination, but for different circuits, may be multiplexed over a common channel. In B-ISDN this channel is termed a *virtual path*, and is the reason for the VPI in the cell header.

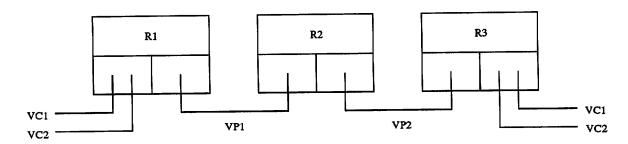

Figure 2.8: Virtual Path Call Multiplexing

The concept is illustrated in Figure 2.8. The virtual circuits VC1 and VC2 utilise a common virtual path (VP1-VP2) for part of their route (R1-R2-R3). R2 is a VPI router, it re-maps the VPI for an incoming cell and forwards it on that basis. The Virtual Channel Identifier is left untouched. The VP approach allows fast connection establishment as the routers internal to any VP used are effectively by-passed. It also has the benefit of simpler network management. For example, if a VP router fails then it may only be necessary to re-route each active VP rather than each

circuit. A virtual path has certain synchronisation properties since it maintains cell sequence integrity across all connections that are multiplexed over it.

## 2.4 Call Establishment

In a virtual circuit network dynamic call establishment requires a mechanism for VCI exchange on a hop by hop basis. The MSN architecture defines the *promiscuous* association mechanism for this purpose. A promiscuous association comprises a well known (public) VCI with which is associated a specific service. It is directly analogous to the pre-assigned virtual circuits of the B-ISDN. Any node on a network may send cells, using a promiscuous VCI, to any other node on the same network. One such promiscuous association is defined to be used for MSNL connection management.

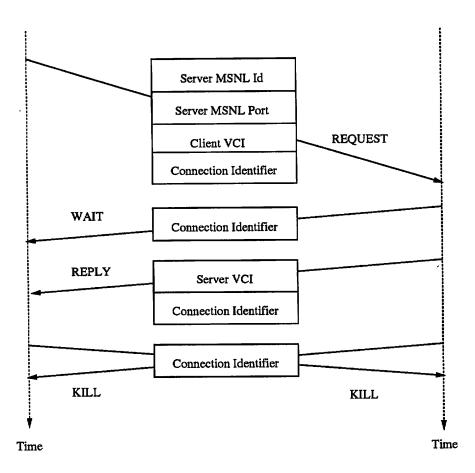

Figure 2.9: MSNL Liaison Establishment and Tear Down

The types of message used in MSNA connection management are illustrated in Figure 2.9. The terms client and server are used to refer to the connection initiator

and acceptor respectively. The protocol considerations are similar to those found in remote procedure call systems. A multi-hop connection will require the connection establishment procedure to be repeated on each intermediate network. The wait facility informs a retrying initiator that a connection is still in the process of being established. This is typically used by routers when setting up a multi-hop liaison.

## 2.5 Higher Levels

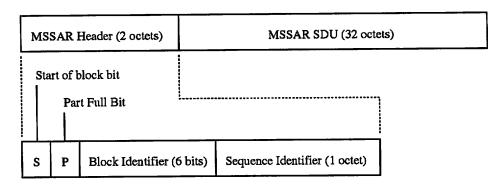

Additional functionality on top of the streamed cell interface that B-ISDN and MSNL provide is required to accommodate various services. The protocol to be used over a particular circuit is agreed upon during call establishment. Any further negotiation required is protocol dependent and in-band. Early implementations of the MSN architecture assumed only a single higher level protocol: the multi-service segmentation and reassembly (MSSAR) protocol. MSSAR is concerned with the transfer of variable sized blocks over MSNL liaisons and is a typical example of a higher level protocol.

Figure 2.10: MSSAR PDU encoding

Figure 2.10 shows the encoding of the MSSAR header. The start of block bit defines the beginning of a new block. The sequence number, which counts down to 1, indicates the total number of SDUs remaining in the block. The block identifier requires at least all the cells for 63 consecutive blocks to be dropped before there is the possibility of a block being incorrectly assembled. If the block is not an integral number of MSSAR SDUs then the last header will have the part-full bit set, in which case the final octet of the MSSAR SDU indicates the number of valid SDU octets present. The B-ISDN architecture defines the ATM adaptation layer (AAL) above the ATM layer. A set of higher level protocols are defined one of which, AAL Type 3, offers similar functionality to MSSAR.

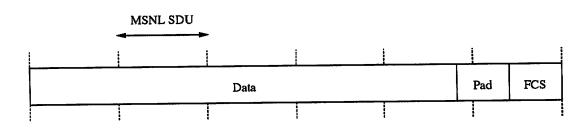

The MSSAR protocol is heavyweight considering that the MSNL interface defines that cell re-ordering or duplication does not occur on a connection. Of course an implementation cannot guarantee that such events do not occur and so any higher level protocol must be robust in their presence. Rather, their occurrence is viewed as extremely unlikely and so recovery from them should not dictate the design of any higher level protocol. A simpler block assembly protocol is illustrated in Figure 2.11.

Figure 2.11: Simplified Block Assembly Protocol

A block is transmitted as a sequence of MSNL SDUs. The final cell, recognised by having an End-Of-Frame (EOF) indicator set, contains the Frame Check Sequence (FCS) field. The FCS is a check on the data octets. In most cases a lost cell will only cause the assembly of a single datagram to fail. If however the cell lost contains the EOF indicator then cells will continue to be assembled until the next EOF indicator, at which point the FCS check should fail. In this way a subsequent block although correctly received will be discarded. The protocol could be made more robust (and complex) by the addition of a Start-Of-Frame (SOF) indicator. No length field is necessary as it is believed that most higher level protocols already encode such information in the data field. If they did not then it could be added. In this way redundancy is avoided.

A protocol similar to the above has been proposed for B-ISDN AAL Type 5. The Simple and Efficient Adaptation Layer (SEAL) [SUN91] is a reaction to what is seen as the unnecessary complexity and overhead of AAL Type 3. SEAL requires the provision of an EOF bit, which does not currently exist, in the B-ISDN header. The proposal is to use PT 10 to signify EOF (values 00 being already assigned and 01 under consideration for other purposes). By eliminating the AAL Type 3 headers from the information field of the B-ISDN cell an additional four bytes of user data are available in each cell. This may reduce the total number of cells required per block by up to 9%. The SEAL FCS comprises a 32 bit CRC (the same computation as in IEEE 802.5). The proposal argues that the frame level checksum is more reliable than the per cell CRC present in AAL Type 3; the belief being that a single strong error check is better than a long series of weaker checks.

## 2.6 Relationship to OSI

The ISO Open System Interconnection (OSI) reference model [Day83] provides a useful framework in which to compare and contrast network architectures. The seven layer model is only intended as a guideline, a fact that becomes apparent when trying to describe most real architectures. An attempt is made to illustrate the relationship of the MSN architecture to OSI in Figure 2.12. The main observation to make is that no multiplexing above that at the datalink layer is necessary when using MSNA. If multiplexing at multiple layers, as allowed by the OSI model, is performed, then higher level guarantees may be compromised. A detailed discussion of the issues surrounding layered multiplexing may be found in [Tennenhouse89].

| ISO OSI Model | MSSAR / MSN |                  |

|---------------|-------------|------------------|

| Application   |             |                  |

| Presentation  |             |                  |

| Session       |             |                  |

| Transport     |             | MSSAR            |

| Network       |             | MSNL             |

|               |             | MSDL / Ms-Access |

| Datalink      |             |                  |

| Physical      |             | Physical         |

Figure 2.12: Relationship of MSNA to the OSI Reference Model

## 2.7 Summary

The Multi-Service Network Architecture (MSNA) has been described, and its relationship to OSI has been established. The draft B-ISDN definition has been outlined. Although differing in detail and complexity, both B-ISDN and MSNA display many similarities at and below the network level (where they are both most fully defined); experimental results derived using MSNA should be directly applicable to the B-ISDN, and vice-versa.

# Chapter 3

# WANDA MSNA Implementation

This chapter begins with a statement of the WANDA system philosophy and design. The features that make WANDA suitable for building high performance dedicated systems are discussed. The WANDA Inter-Process Communication (IPC) interface is then described in detail. A comparison is made with similar support available in other systems. The MSNA protocol suite has been implemented as a WANDA kernel protocol stack and support for building MSNL routers is available. An initial router supported MSSAR block forwarding in user space. The second router supports MSNL cell forwarding in kernel space. In both cases the connection management is controlled by a user space application.

## 3.1 WANDA

One traditional view of an operating system is as a monolithic piece of code running in a privileged mode, functions such as device drivers and the file system being part of the monolith. Inevitably, with logical separation of unrelated components un-enforced, interdependencies arise which make the system difficult to maintain and develop. Distributed systems research is concerned with the operation of physically separated, possibly heterogeneous, interconnected computers. As a result designers have been forced to decompose the single processor monolithic system into separate components which communicate via message passing. The WANDA philosophy represents a continuation of that found in the Cambridge Distributed Computing System (CDCS) [Needham82]. The CDCS has perhaps been the most highly decomposed distributed system attempted to date. The system comprised heterogeneous hardware and operating systems but made progress through a set of homogeneous interfaces. Note that for some applications, such as fault tolerant computing, it can be desirable that such heterogeneity exist in a single system.

Recent years have seen the widespread deployment of distributed systems technology [SUN86, Scheifler86, Sandberg85]. Unfortunately most such systems comprise nodes running operating system kernels whose design was dictated by the demands of time-sharing. A large amount of research [Accetta86, Tanenbaum87, Herrmann88] has been aimed at finding lightweight replacements for such kernels. Lightweight is used to refer to the smaller code size and the higher performance exhibited by such kernels. Two of the most attractive features of lightweight kernels are the relative ease with which they are ported and maintained.

There is a broad range and rapid evolution in the type and capability of processor hardware. This situation has been exacerbated by the emergence of Reduced Instruction Set Computing (RISC) [Patterson80]. It is important that a system be readily ported in order to take full advantage of new hardware. A smaller kernel (it is hoped that the kernel forms the basis of most of the work) helps to ensure a simpler port. The code that has to be altered per port must be well defined and kept to a minimum. Some pieces of code may be implemented in a machine independent, but less efficient, manner. In this way an initial port is made easier. Subsequently they may be re-worked in a machine dependent fashion for performance improvements. A successful example of this approach may be found in the device dependent interface of the X Window System sample server [Angebranndt88]. A further example is that the WANDA kernel is capable of functioning on machines without support for virtual memory (Section 3.1.4). If a quick port to a particular hardware configuration is required, then the code necessary to implement virtual memory may initially be left out.

The WANDA system was perceived as a high performance, lightweight kernel upon which system servers could be run. The WANDA programming interface is not a list of system calls (traps into the micro-kernel) even though a particular kernel implementation might choose to interpret it as such. For example, the user library code for a thread (Section 3.1.1) to determine its own identifier may, on a uniprocessor, simply read a well known location maintained by the micro-kernel thread switching implementation. On a shared memory multiprocessor the same code might involve a system call. Subsequent sections discuss the structure of the WANDA system as currently implemented at the University of Cambridge Computer Laboratory. Whilst not a primary aim, the WANDA interface has been designed so as not to preclude the implementation of a general purpose operating system environment. One possible route to achieving this would be the emulation of another micro-kernel based interface, such as MACH, for which an operating system environment already exists [Golub90].

Subsequent sections describe the support for concurrency and communication in the WANDA kernel. These are the areas most relevant to the dissertation. A detailed account of the virtual memory management system may be found in [Mapp91].

#### 3.1.1 Concurrency

Distributed system servers exhibit natural concurrency due to the fact that a single server will typically handle the requests for multiple clients. Threads [Birrell89, Swinehart85] provide a mechanism for expressing this concurrency. On a uniprocessor they are a convenient structuring technique, but offer no gain in performance over a *suitable* non-threaded implementation. On a multiprocessor, where threads can be executed concurrently, they offer performance improvement compared to the non-threaded case.

A WANDA domain, or process, consists of a set of independently schedulable threads which all share a common address space. On a multiprocessor each thread, unless constrained, may be scheduled on any processor. Reasons for constraint might be the accessibility of a specific piece of hardware (possibly local memory) on a particular processor only. The basic synchronisation mechanism for WANDA threads is the counting semaphore [Dijkstra68]. The traditional P(sem) and V(sem) operations and a facility for waiting on a semaphore subject to a time out are provided. The kernel itself is multi-threaded; for example, in addition to kernel background threads, such as device driver watchdogs, the kernel must be prepared to handle concurrent system calls from multiple user level threads.

The efficiency of the thread switching and synchronisation facilities determines the grain of concurrency that an application will attempt. The WANDA thread switching implementation on a multiprocessor offers the possibility of fast synchronisation. When there are no runnable threads for a processor one approach would be to schedule a kernel "idle" thread which simply executes a dally loop with interrupts enabled. Instead, in WANDA, the last thread to block on a processor spins in the scheduler on its wake up condition. A thread that removes the blocking condition is able to wake the blocked thread by setting the memory location upon which it is spinning. There is no need to invoke a heavyweight inter-processor interrupt (IPI) operation. This technique works best if the threads for a domain are scheduled concurrently on separate processors (so called co-scheduling [Ousterhout82]). However, if there are multiple domains to be scheduled, such an approach may in fact reduce throughput due to the increased percentage of virtual memory context switches necessary upon a re-schedule.

Execution of a process on a multiprocessor is a stringent test of the concurrency correctness of the program. Although semantically the same as uniprocessor execution, subtle differences exist. In many cases the thread pre-emption interval is long enough such that a thread when scheduled will run until it blocks. Even if very fine grain time slicing is enabled most architectures will preserve instruction atomicity in the presence of interrupts (e.g. the timer). On a multiprocessor the execution stream of two threads may be interleaved at the sub-instruction level.

#### 3.1.2 Communication

The WANDA IPC facility supports communication between threads in different domains on the same machine (Section 3.3.2) and on different machines connected by a network (Section 3.3.1). There is no reason why threads in the same domain cannot communicate with each other using the IPC facility. Typically, however, they would use a shared memory paradigm. The WANDA IPC interface (Section 3.2) is at a level unpalatable to most distributed applications programmers. A distributed computing environment, the ANSA Testbench [ANSA89], has been ported to run over WANDA. The Testbench can be viewed at the application level as having the following components:

- Capsule: the run-time system for a Testbench application, including support for threads and communications. A capsule is single instance of this run-time system.

- IDL: the Interface Definition Language which is used to define an ANSA interface. An associated compiler, STUBC, generates C language client and server stub code from an IDL definition. An example IDL specification is presented in Section 3.4.3.

- PREPC: a preprocessor which scans C language source programs for embedded DPL (Distributed Programming Language) statements. These are converted into calls on either the capsule library or the stub procedures generated by STUBC.

- Trader: a capsule which provides the mechanism for separate capsules in a distributed ANSA application to rendezvous. A server exports an interface reference to the trading service to make it accessible to other programs. An import operation is provided so that clients may extract interfaces from the Trader.

The provision of a distributed computing environment enables easy access to many traditional operating system components. For example, the demands placed on the file system by the WANDA applications discussed in this dissertation are relatively light (e.g. a process reading a file for configuration information). An ANSA interface to the UNIX file system provides sufficient functionality and performance.

#### 3.1.3 Process Management

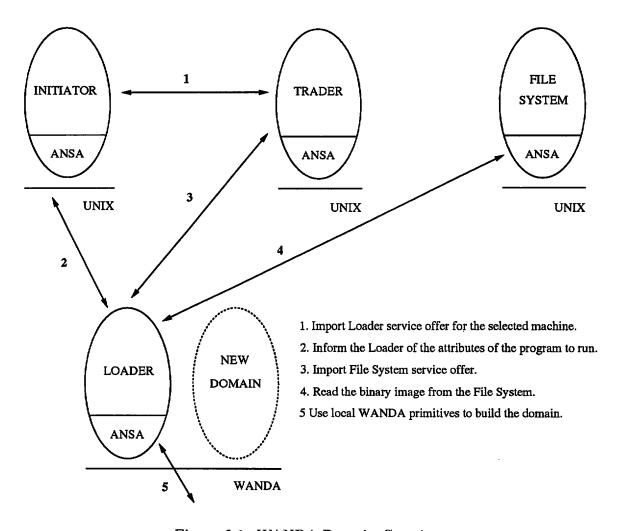

Figure 3.1 illustrates the steps involved in creating a process dynamically to run on a WANDA system. A typical WANDA machine contains a version of the kernel and a single user process in PROM. Upon reset this process will load the current boot file for the machine from a boot server using a simple transport protocol built over MSNL. The WANDA machine will initially have been booted with an image containing a kernel and single user level "loader" process. The loader is an ANSA application and, upon starting, exports an interface to the ANSA Trader. A party interested in creating a process on a WANDA machine first imports the appropriate loader service offer from the Trader.

Figure 3.1: WANDA Domain Creation

The loader interface to create a process is then invoked, one of the parameters being the file name of the image to be executed. The loader imports the appropriate file system offer from the Trader and invokes it to read the contents of the executable file. The domain is then built using privileged WANDA process creation primitives. There is nothing to prevent multiple loaders being run on the same machine. Typically this would be the case if different interfaces were being employed, e.g. one which was implemented to use SUN RPC.

The loader process assumes local responsibility for the management of the new domain. It is possible for the loader to stop the execution of a domain it has created. More typically the domain will stop due to an error, e.g. virtual memory protection violation, or natural program termination. In either case all threads for the domain are stopped in user space. This involves waking all threads for the domain in question which are blocked inside the kernel. The system call exit code contains a test to see if the current domain is stopping. Depending upon the system call that was attempted the thread stops itself with state such that if it were re-started it would either:

- return an error indication for the system call result, or

- re-attempt the system call with the same arguments.

When the domain is fully stopped the creator receives an *event* notification. Local primitives are available to query and alter the state (e.g. thread registers or memory locations) of the stopped domain. The ability to stop a process and query the state enables implementation of the following techniques to be considered:

- remote debugging [Cooper88, Redell88],

- process migration [Powell83, Theimer85, Zayas87].

It is not suggested that process migration be transparent at the system call level. Rather an application that is re-started on a different machine would experience errors upon trying to use kernel level resources which it had allocated on its original machine. If it is a properly coded application then it will handle such errors by re-trying at a higher level. However, the usefulness of a process migration facility for the types of application considered for implementation over WANDA is dubious. This is because many server instances display an affinity for a single machine, e.g. a file server for the disks on a particular machine.

## 3.1.4 Building Dedicated Systems

The WANDA system is designed primarily as a substrate for dedicated high performance servers. When writing an application it should be possible to develop much

of the code in a traditional program development environment, such as UNIX. The next phase is to complete the development and debugging on a WANDA machine that provides as much aid to the programmer as is feasible; examples include:

- virtual memory protection from others and yourself,

- comprehensive kernel checking of user arguments.

Once the developer is happy with the application it can be installed. Many of the above kernel features, desirable during development, now represent runtime overhead for the service. By removing them performance will be improved. This is analogous to turning on compiler optimisation and procedural inlining when building a program for installation. In a kernel which completely disables the memory management unit (and so is capable of running on a machine without one), termed a single address space (SAS) system, further improvements are possible. The overhead of using traps for users to link with the kernel can be avoided by using simple procedure calls. Upon initialisation the package containing assembler stub routines for trapping into the kernel would query the kernel for their procedural entry point replacements. Such an arrangement requires that user space programs run in kernel mode. Savings, depending upon the architecture involved, can include:

- no copying of arguments from user to kernel stack,

- system call entry dispatching eliminated,

- no switching between user and kernel mode.

In a similar fashion it is possible to translate same-machine cross domain remote procedure calls into simple procedure calls. This is similar to Lightweight RPC (LRPC) [Bershad90] except there is no need for passage through the kernel to change virtual memory context. Of course, with memory management disabled, another sink of performance when crossing domain boundaries, Translation Lookaside Buffer (TLB) faults, are eliminated. The penalty to be paid is the loss of virtual memory. This is not a major problem since most dedicated systems will have been written to avoid paging. However some system software techniques, such as asynchronous garbage collection [Ellis88], depend upon virtual memory being enabled. None of the applications described in this dissertation are so constrained.

#### 3.2 The WANDA IPC Interface

The WANDA IPC interface is based upon the Berkeley UNIX socket abstraction [Leffler89]. In particular the need to support multiple protocol domains is recog-

#### nised. The important operations are listed below:

buffer: WandaIOBuffer

socket: WandaIPCDescriptor

address: WandaIPCAddr

socket := WandaIPCSocket(PROTOCOL\_TYPE)

WandaIPCBind(socket, address)

WandaIPCConnect(socket, address, timeout)

WandaIPCOffer(socket, timeout)

WandaIPCAccept(socket)

WandaIPCSend(socket, buffer)

buffer := WandaIPCRecv(socket, timeout)

All of the above operations are synchronous. As the interface is multi-threaded there is no requirement for the equivalent of the UNIX select operation. Incoming connections are established in a two phase process. Firstly, a thread registers an interest in receiving a connection request by invoking the Offer interface. A matching connection request will result in a successful return for the call. The connection is not yet established. The application has available information concerning the embryonic connection e.g. the peer endpoint address. This information is typically used to aid deciding whether or not to Accept the connection. Some call establishment protocols, such as the one for MSNL (Section 2.4), provide mechanisms which may be used to prevent the connection request timing out whilst this decision is being made.

The interesting part of the interface, that concerning buffer management, is elaborated in Section 3.3.3. Lightweight kernel philosophy [Tanenbaum87, Cheriton88] is to have a single IPC facility within the kernel. Additional protocols are implemented in user mode and accessed by interested applications via the kernel-provided protocol. Whilst acceptable for many applications, optimal performance for a particular protocol will always be provided by a kernel implementation. The main performance limitation in supporting multiple protocols in this way is the indirection involved in per socket control structures during the send and receive operations. This is minimal and could always be removed by the addition of a protocol specific interface alongside the generic one.

## 3.3 O/S Support For IPC

Distributed systems cannot exist without communication; its efficiency is one of the major factors determining the performance of the overall system. Many applications find difficulty in realising even a small fraction of the available network bandwidth. It has typically been thrown away by a combination of the host-network interface, system bus, communications protocol and user/kernel networking interface employed. The dominant factor affecting IPC performance is usually the cost of data copying. Approaches to minimising the cost are discussed below. Two classes of IPC can be distinguished, moving data between user space domains across a network and moving data between user space domains on the same machine.

#### 3.3.1 Inter-Machine Communication

Many network interfaces contain DMA hardware which works on contiguous regions of physical memory. Application data however is presented as a linear region of virtual memory which in the general case will not be physically contiguous. If the DMA hardware supports chaining of data then it is possible to avoid copying into a contiguous buffer although at the cost of some software complexity. In a paging system the real pages which comprise the user's message must be marked unpageable whilst the operation is in progress, and unmarked when the transfer completes. The above complexity has forced many systems, in particular UNIX, to copy user data into intermediate kernel buffers before presenting it to the network interface for transmission.

Other systems, such as Amoeba [Tanenbaum87], rely on the backing of contiguous segments of virtual memory by contiguous equivalent arrays of real memory, and the absence of paging, in order for network drivers to access user virtual memory easily. Of course this requires that the user be informed when the transfer operation is completed so the application can re-use the virtual memory. Making the interface synchronous with respect to the transfer or providing some form of upcall into the application both represent additional overhead. Yet another technique, found in the V system [Cheriton88], is to treat small messages as special and arrange for them to be passed into the kernel using registers. This yields limited speedup over copying and introduces a test of message length into the main line code. Finally, a technique used in the Topaz environment [Thacker87, Schroeder89], is to map (with both read and write access) a set of physically contiguous buffers into the address space of each user domain. A lock, shared between the kernel and all users, controls buffer acquisition and release. The problem associated with this interface is that malicious or erroneous clients can overwrite data in buffers allocated to other users, including the kernel.

#### 3.3.2 Intra-Machine Communication

Trends in structuring distributed systems are making the performance of intra-node IPC increasingly important. Consider the case of a domain dedicated to maintaining the client side cache of a remote file system. All file system requests from any domain on that node will go through the domain containing the cache. If the cache is functioning correctly most requests will be satisfied without the need for an internode operation.

When moving data between domains on the same machine several techniques are available. One method is to copy from the sending to the receiving domain. This is non-trivial as the two regions will be in different virtual memory contexts on most architectures. Many implementations copy into an intermediate kernel buffer. When the receiver is woken it copies data from the kernel buffer into its address space. An alternative is to arrange that all physical pages on a machine are always accessible using a fixed range of kernel virtual addresses. Whoever performs the copy, sender or receiver, accesses their own region with normal user space virtual addresses. To access the other region the relevant physical addresses are determined which may be accessed in the current context using the appropriate kernel virtual addresses. As the user page tables no longer protect the copier from page-outs a certain amount of care must be taken when performing this operation.

A second method is to use a virtual memory technique termed copy on write (COW) [Trevanian87, Abrossimov89]. The physical pages representing the message in the sender's address space are marked read only. The physical pages representing the destination region in the receiving domain are replaced by the sender's physical pages marked read only. If either side subsequently attempts to write one of these pages, generating an access control violation, it is replaced by a different physical page which is a copy of the original. Changing the virtual memory management tables is an expensive operation. In addition to the computation involved the TLB must be flushed. This impacts the performance of the processor due to increased subsequent TLB faults. On a shared memory multiprocessor the TLBs of all processors must be flushed. Unfortunately the same thought that has gone into cache coherence protocols for the memory system has not been directed at the TLBs. On most architectures flushing the TLBs requires an IPI to each processor.

## 3.3.3 The WANDA I/O Buffer System

The WANDA I/O buffer system is similar to the DEC SRC Topaz scheme (Section 3.3.1). A stylised version of the interface is given below:

buffer: WandaIOBuffer

buffer := WandaIOBufferAcquire(length, timeout)

WandaIOBufferRelease(buffer)

An I/O buffer is realised as a contiguous region of physical memory; it is uniquely identified by an easily verifiable handle. The attributes of each buffer, such as address and length, are described by a per-buffer structure. In a secure implementation of the interface, an allocated I/O buffer is mapped with read and write access into the acquiring domain's address space. If a domain attempts to access an I/O buffer it does not own then it will address fault.

In addition to the above interface an I/O buffer may be acquired upon receive and released upon send. Thus, the semantics of the IPC and I/O buffer interface dictate that, once sent, data in a buffer is no longer accessible. This means that a client wishing to maintain a copy of any transmitted data, e.g. for re-transmission, must perform a copying operation before transmission; a kernel space copy has been swapped for one in user space. The situation is not so bleak when it is realised that other stages are usually required in the preparation of data for transmission e.g marshalling or encryption. The marshalling code in a remote procedure call runtime system could arrange to marshall directly from client arguments into an I/O buffer. If re-transmission is necessary the arguments are re-marshalled; a small penalty considering this action is only necessary if a time-out occurs. Note that this re-marshalling could be initiated before the time-out if the application has no other work to perform. The important point is that intelligent clients have the opportunity to avoid copying. Not all implementations will adhere to the strict semantics of the interface. In particular, a secure machine supporting dedicated servers may choose to neglect all virtual memory operations. However, client code which depends on this is illegal. Other techniques for building such kernels were discussed in Section 3.1.4.

## 3.4 MSN Architecture Implementation

In an inter-network environment it is important to have rich connectivity [Braden87], this implies many networks having multiple gateways. In the initial WANDA MSNA implementation there was no code that enabled a WANDA machine to act as an MSNL gateway. The requirement for such functionality became apparent with the desire to place machines on the first Pandora CFR.

While the MSN architecture has been designed such that gateways can be built in

hardware it is not the case that all will be. New networks are more quickly supported in software. Not all routes are performance critical, e.g. one used for a mail feed only. Therefore solving the problem with a cheap general purpose processor can be more cost effective than using dedicated hardware. Such software gateways would be configured with downgraded quality of service attributes so that they are only used in response to failure or overload conditions on the primary routes. Even in a hardware gateway it is not envisaged that the hardware understand much more than header re-mapping and simple cell queueing. All protocol control packets would be handled in software and the hardware instructed when a liaison is established or terminated.

The use of a connection oriented protocol enables optimisations to be made at connection set up time. The code to implement intra-node MSNL quickly diverges from that implementing the inter-node case. The dispatch vectors for send and receive in each socket control block are accordingly adjusted when a connection is established.

### 3.4.1 MSSAR User Space Gateway

One approach would have been to put the gateway code into the kernel. This was rejected on the grounds of:

- implementation complexity,

- difficulty of debugging and maintenance,

- limited configurability.

A technique for enabling protocol implementation in user level processes, the *packet filter*, is described in [Mogul87]. However, moving functionality out of the kernel is not a panacea. The design described below attempts to balance the requirement for high performance with that of moving complex code into user space.

The MSNA user space interface already offered the ability to accept incoming and establish outgoing connections. A wildcard MSNL port was defined upon which connection requests for specific destination networks could be accepted. A connection so established has the liaison initiator as the peer address and the intended recipient as the local address of the socket. The gateway process then attempts to establish a connection to the intended recipient, making it look as if the connection request came from the initiator. Data received on the former socket should be forwarded on the latter, and vice-versa. As the receive interface is blocking, two threads will be

required to listen for incoming packets and data received on one socket is forwarded on the other. The code for this is extremely simple:

```

in, out: WandaIPCSocket

forever do

WandaIPCSend(out, WandaIPCRecv(in))

end

except: error handling logic

```

Note that no lookup is required to determine the incoming or outgoing socket indices, it is all part of the thread state. The overhead is in the scheduler thread switching implementation but this is just one piece of code and a candidate for optimisation. No user space synchronisation is required except in handling exceptional error conditions, where the two threads have to agree whose responsibility it is to free user level resources associated with the connection, primarily the two sockets. Consider the code to achieve a similar function over an asynchronous, single threaded interface such as that found in UNIX. Upon reaching the idle condition the process would block inside the kernel, using the select system call, with a list of all I/O descriptors it was interested in. Upon return, for all descriptors that are indicated as having a receive pending, the process makes a receive system call, looks up the outgoing I/O descriptor and does a send system call.

Having a gateway in user space is not cheap in terms of system resources. Each through connection requires two threads and two sockets to be allocated. A typical gateway will consume hundreds of threads although, as can be seen, their user space stack demands are not great. If kernel data structures are not extensible the gateway will have to be configured with large defaults or be forced to refuse connections when not necessarily heavily loaded. The WANDA kernel implementation described here provides extensible thread and socket tables.

When receiving notification of an incoming connection the gateway can adopt one of two strategies. In the first, an incoming connection is not accepted until the outgoing one is established. If all gateways follow this strategy then there is a full round trip delay before the initiator can transmit on the liaison. In the second strategy, an incoming connection is optimistically accepted before the outgoing one is established. The initiator may begin transmitting after the round trip delay between it and the first hop gateway. The danger here is that the data will catch up with the connection establishment request, what happens in such a case is implementation dependent (data may be discarded or buffered). Data transmitted over a multi-hop optimistic liaison can arrive at the destination in the same order of time as if it had been sent over a datagram network. It is feasible to envisage a liaison being established, used and then deleted by the initiator before the destination received any indication.

Performance measurements for the user space gateway yielded an interesting result. It would be expected that the ping delay (time to send a cell and receive a return reply) across a gateway would be the sum of the ping times between the endpoints and the gateway. For the case involving no router a scheduler optimisation ensures that the source processor is idling in the context of the receiver thread when the reply returns. Therefore, no context switch is necessary. In the gateway case the same optimisation ensures that the gateway processor is typically in the context of the thread that received the cell from the source. A context switch is necessary resulting in the ping time through a gateway being longer than might be predicted. In the case of a blast protocol traversing a user space gateway the scheduler optimisation ensures that very little thread switching occurs. Such interactions are an example of the difficulties encountered when attempting to extend QOS from the network up through the endpoint operating system to a user level application.

### 3.4.2 MSNL Cell Forwarding

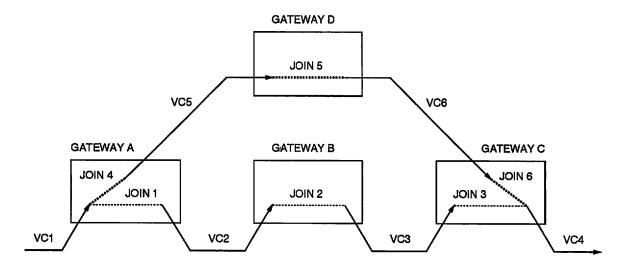

The user space gateway described above suffered from two problems. Firstly, as the WANDA MSNA user interface only dealt with the transmission and reception of MSSAR blocks the gateway was an MSSAR, and not MSNL, router. Secondly, although adequate for Ethernet type interfaces (large packet size and DMA) the user space implementation would have severe performance and/or jitter problems when forwarding cells between ATM networks. In addition, if QOS was to be provided in user space then real-time support would have to be added to the WANDA thread and IPC systems. As a result of these considerations it was decided to add support for MSNL cell forwarding in the kernel with forwarding taking place in network driver interrupt routines. Connection management was still maintained in user space. The IPC interface was extended so that two established liaisons could be joined together:

#### a, b: WandaIPCSocket

WandaIPCJoin(a, b) except: error handling logic

Incoming cells on liaison a are forwarded on liaison b, and vice-versa. Forwarding of MSNL cells in the kernel is relatively straightforward. The easiest situation is when forwarding between homogeneous networks. A single incoming CFR cell maps onto a single outgoing CFR cell. A single incoming Ethernet packet (possibly a collection of cells) maps onto a single outgoing Ethernet packet. The same ease applies to forwarding between similar networks such as the CFR and CBN.

Forwarding from an Ethernet to a CFR/CBN involves invoking the cell forwarding machinery once for each cell in the Ethernet packet. Forwarding cells in the oppo-

site direction is more complicated. Assigning each incoming ATM cell to a single Ethernet packet would exhibit miserable performance. Assigning multiple cells to an Ethernet packet raises the problem of when to forward a partially filled Ethernet packet. Such a decision is dependent upon the higher level protocol involved, of which an MSNL router should be unaware. However fixed bits in the MSDL header are allowed to be set by higher level protocols and may be interpreted by routers. One of these is the EOF bit (Section 2.5) which is used to trigger forwarding. It is interesting to note that the B-ISDN cell header (Section 2.3) includes no such facility. Two threads are still required in user space to wait for either side of the through connection to close (and take the appropriate action).

#### 3.4.3 ANSA Interface

The implementation of gateway management in user space enabled a trivial ANSA control interface to be provided (there is no RPC implementation within the WANDA kernel).

```

Router : INTERFACE =

BEGIN

MSNLAddr : TYPE = RECORD [host, port: CARDINAL];

MSNLConn : TYPE = RECORD [client, server: MSNLAddr];

ConnList : TYPE = SEQUENCE OF MSNLConn;

ListConnections : OPERATION [] RETURNS [ConnList];

DeleteConnections : OPERATION [ConnList] RETURNS [];

END.

```

Figure 3.2: ANSA Interface to MSNL Router

The initial interface to the router (Figure 3.2) simply supported a query on the state of all active connections. In addition, it allowed a client to close a connection(s) remotely. It is expected that the majority of network management software will be built using an RPC paradigm.

## 3.5 Summary

Some of the features which make WANDA a suitable vehicle for building high performance distributed systems components have been discussed. These are:

- easily portable (SAS systems),

- concurrency through threads,

- multiprocessor operation,

- high speed networking (I/O buffer system),

- ability to configure stream-lined versions.

Kernel techniques for the support of high speed networking have been discussed within the framework of the WANDA IPC interface. The WANDA MSNA implementation prior to incorporation of any QOS related functions has been described. The MSNL router connection management code has been implemented in user space without impacting data forwarding performance. In addition to ease of programming, a major benefit is the availability of a sophisticated distributed computing environment (ANSA) at this level.

# Chapter 4

# The Cambridge ATM Backbone

This chapter describes the Cambridge ATM Backbone network which has been built using infrastructure described earlier in the dissertation. At the time of writing this network is used to transport voice, video and data traffic between two sites in the Cambridge area.

## 4.1 Pandora Interworking

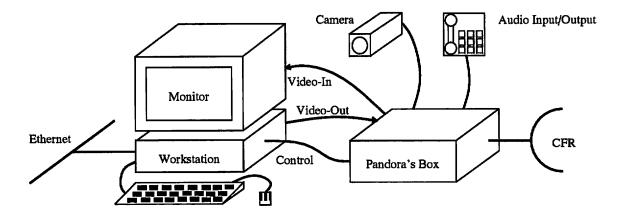

Pandora [Hopper90] is a joint project between Olivetti Research Limited (ORL), Cambridge and the University of Cambridge Computer Laboratory. The project is investigating the use of multimedia workstations in a working environment with particular emphasis on digital video. A Pandora workstation (see Figure 4.1) comprises a standard workstation to which has been attached a multimedia peripheral, called Pandora's Box. The control interface to the box enables most application and management software to run on the workstation. The X11 window system [Scheifler86] is used (with protocol extensions) to provide a programming interface to the video capabilities of the Pandora Box.

The Pandora Box acts as a switch between a set of multimedia input and output devices. The handling of video presents the greatest technical challenge. A video stream is typically sourced from the local camera device or network (CFR). Video stream sinks are typically the workstation monitor or the network. An analogue mixer, under workstation control, is used to display video on the workstation monitor. The network is used to provide a real-time communication path for voice and video streams between boxes. Pandora network protocols are built as an adaptation layer over MSNL virtual circuits. Both video and voice streams are constant bit rate. Popular applications include video-phone and video-mail. A video file server

Figure 4.1: The Pandora Multimedia Workstation

is accessible over the CFR.

The initial network configuration comprised a single CFR, running between the two sites, to which all Pandora boxes were attached. Such a configuration has well known drawbacks:

- a single network failure can disable both sites,

- many management decisions are not local,

- ring bandwidth limits the number of active boxes,

- a single CFR has geographical limitations.

In response to these problems the CFR was split into two rings, one at each site. These were connected using a single CBN. The initial MSNA router hardware comprised one 68030 processor, with a single CFR and CBN interface, at each site. While solving the problems described above it has introduced new considerations concerning component placement. A video file server is required to handle a larger number of concurrent streams than any of the workstations it serves. The fairness properties of the CFR prevent it from acquiring the "unfair" share of the bandwidth it might justifiably desire. In practice the situation is worse due to the poor performance of most CFR network interfaces. Solutions can involve adding more than one interface to a particular file server or having multiple file server instances. The CBN exhibits properties more suitable for the support of a video file server. By moving the video file server to the CBN the threshold above which such solutions have to be considered is raised.

## 4.2 IP/MSNL Protocol Gateway

In addition to MSNA interworking between CFRs, the Pandora system also required Internet Protocol (IP) [Postel81a] connectivity between the Pandora host workstation Ethernets. Three options for connecting the Pandora Ethernets over the backbone were identified. Firstly, an IP gateway could be built that fragmented IP datagrams over ATM cells. This has the disadvantage that most of the information field of each cell would be consumed by the large IP header. In addition IP routers would be required within the ATM network. Secondly, all IP applications could have been rewritten to use MSNL. This is impractical in the amount of effort required and because for many applications the source code is not available.

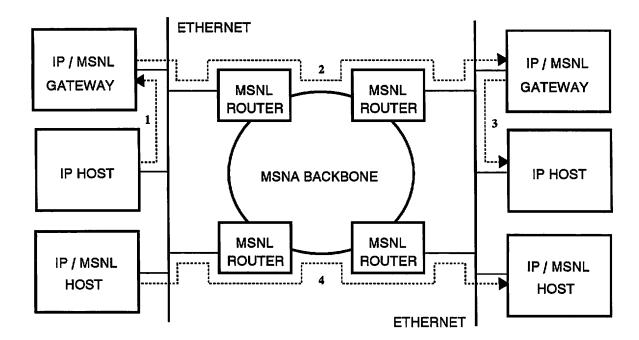

Figure 4.2: Sample IP over MSNL Configurations

Finally, a protocol gateway between IP and MSNL could be built. This was the option selected and is illustrated in Figure 4.2. An incoming IP datagram (1) is forwarded over an MSNL circuit (2) to a peer protocol gateway. If a circuit between the two gateways does not exist then it must be established. The peer gateway will then forward the datagram (3) as appropriate. It is possible to envisage several configurations of switching elements. If each Ethernet had a single IP/MSNL gateway then all IP traffic from one Ethernet to another could use a single virtual circuit. The gateway might attach to the Backbone directly, or use some other mechanism such as an Ethernet/Backbone MSNL router. Any Ethernet host with both IP and MSNL implementations is capable of routing its own IP packets onto outgoing MSNL circuits (4). This involves fewer switching elements between endpoints.

Upon opening an MSNL circuit for carrying IP traffic between sites a QOS should be supplied<sup>1</sup>. This is difficult as IP provides only *limited* information as to what sort of service is expected. A QOS equal to the most stringent required by Ethernet traffic could be allocated. This would be expensive in terms of Backbone resources and certainly undesirable if the Backbone was a charging network. Work on dynamic bandwidth management [Harita91] carried out within the Unison project [Tennenhouse87] would apply directly here. Control on the capacity allocated between two sites could be accomplished by either QOS re-negotiation, opening and closing of multiple circuits or a combination of both.

The IP/MSNL gateway was implemented<sup>2</sup> within the UNIX (specifically Ultrix) kernel. Use was made of the existing IP and MSNL implementations and support for IP gatewaying. In addition to presenting a socket interface the MSNL code was altered to register itself as another IP datalink interface. System administration was possible using existing UNIX network management tools. The MSNA router hardware comprised one 68030 processor, with a single CBN and Ethernet interface, at each site. A large number of Ethernets may be switched using a single CBN, particularly if it is true that most traffic stays local to a single Ethernet.

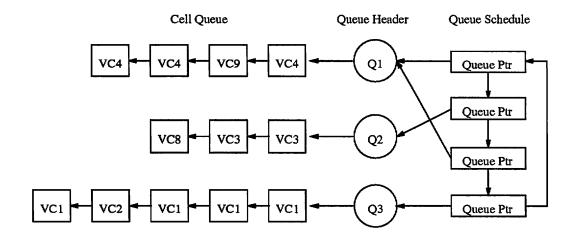

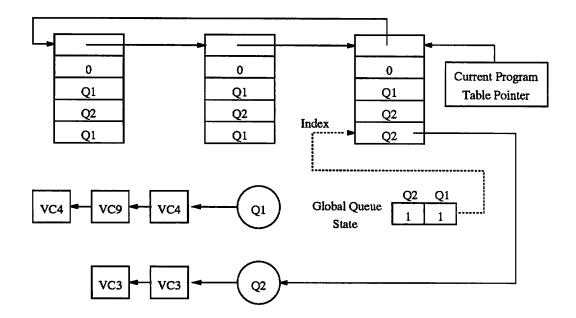

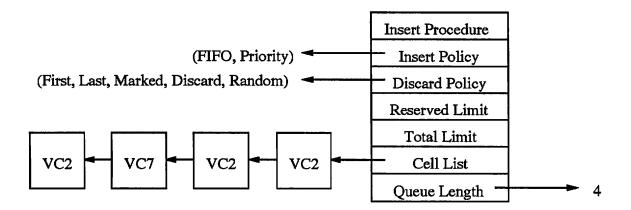

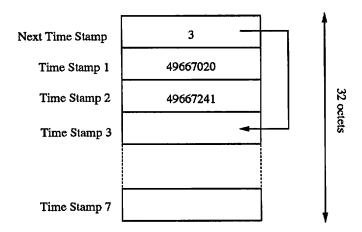

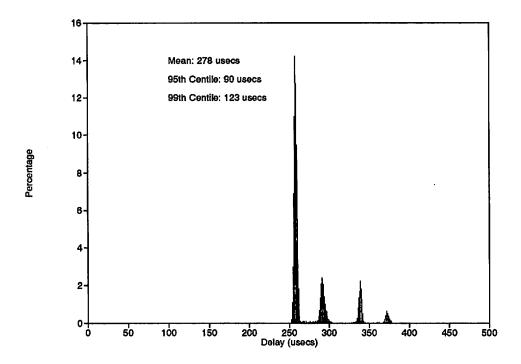

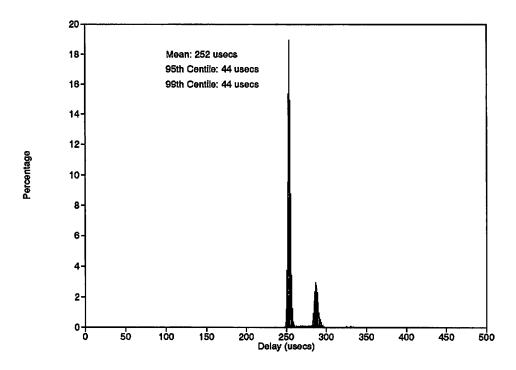

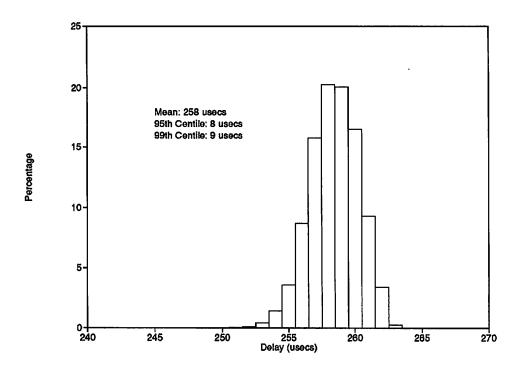

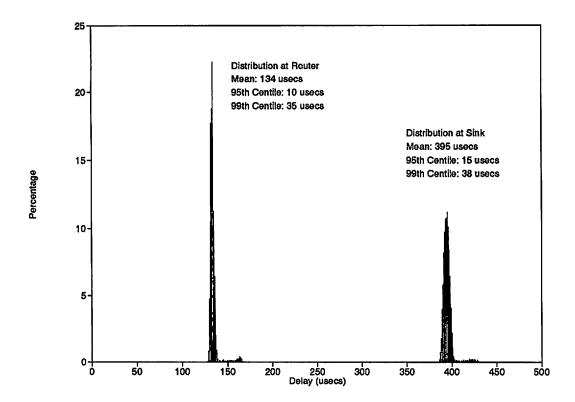

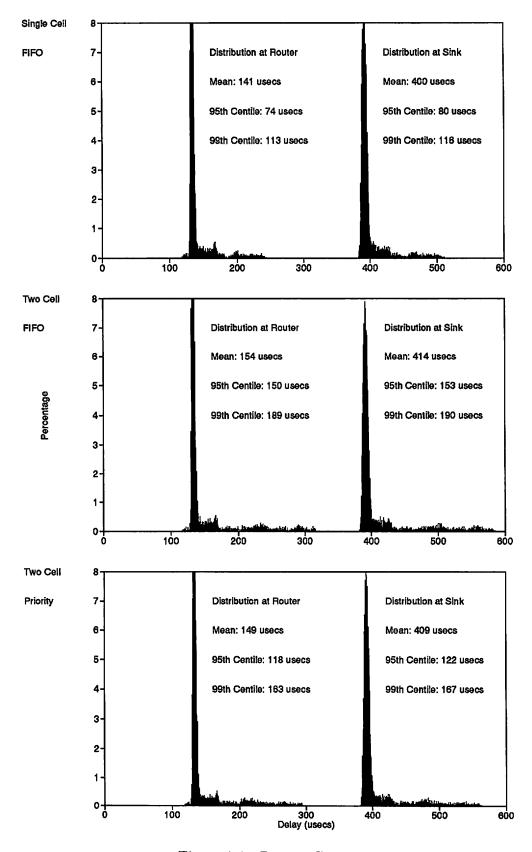

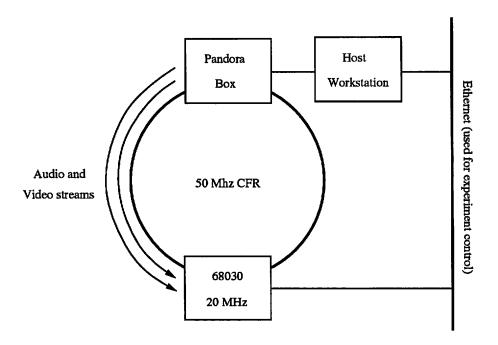

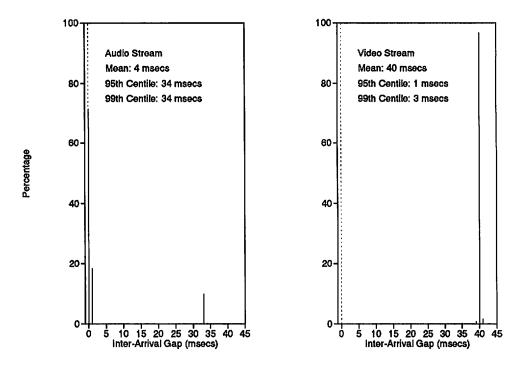

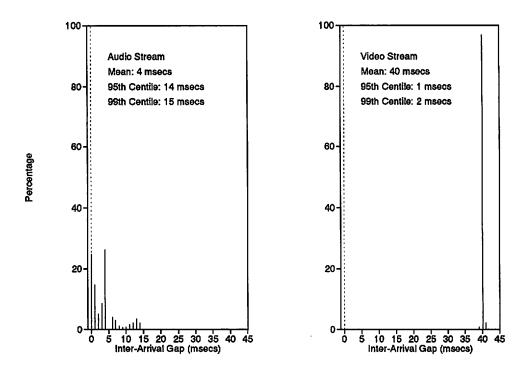

## 4.3 XNS/MSNL Router