Number 242

# An object oriented approach to virtual memory management

Glenford Ezra Mapp

January 1992

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 http://www.cl.cam.ac.uk/

## © 1992 Glenford Ezra Mapp

This technical report is based on a dissertation submitted September 1991 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Clare Hall.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/TechReports/

ISSN 1476-2986

### Summary

Advances in computer technology are being pooled together to form a new computing environment which is characterised by powerful workstations with vast amounts of memory connected to high speed networks. This environment will provide a large number of diverse services such as multimedia communications, expert systems and object-oriented databases. In order to develop these complex applications in an efficient manner, new interfaces are required which are simple, fast and flexible and which allow the programmer to use an object-oriented approach throughout the design and implementation of an application. Virtual memory techniques are increasingly being used to build these new facilities.

In addition, since CPU speeds continue to increase faster than disk speeds, an I/O bottleneck may develop in which the CPU may be idle for long periods waiting for paging requests to be satisfied. To overcome this problem, it is necessary to develop new paging algorithms that better reflect how different objects are used. Thus a facility to page objects on a per-object basis is required and a testbed is also needed to obtain experimental data on the paging activity of different objects.

Virtual memory techniques, previously only used in mainframe and minicomputer architectures, are being employed in the memory management units of modern microprocessors. With very large address spaces becoming a standard feature of most systems, the use of memory mapping is seen as an effective way of providing greater flexibility as well as improved system efficiency.

This thesis presents an object-oriented interface for memory-mapped objects. Each object has a designated object type. Handles are associated with different object types and the interface allows users to define and manage new object types. Moving data between the object and its backing store is done by user-level processes called object managers. Object managers interact with the kernel via a specified interface thus allowing users to build their own object managers. A framework to compare different algorithms was also developed and an experimental testbed was designed to gather and analyse data on the paging activity of various programs. Using the testbed, conventional paging algorithms were applied to different types of objects and the results were compared. New paging algorithms were designed and implemented for objects that are accessed in a highly sequential manner.

## **Preface**

Except where otherwise stated in the text, this dissertation is the result of my own work and is not the outcome of any work done in collaboration.

Furthermore, this dissertation is not substantially the same as any that I have submitted for a degree, diploma or any other qualification at any other university.

No part of this dissertation has already been or is being concurrently submitted for any such degree, diploma or any other qualification.

## Acknowledgments

I wish to express my deep appreciation to my supervisor, Dr. Ian Leslie, for his encouragement, guidance and support during the course of my research. I would also like to thank members of the Wanda Group at the Computer Laboratory, in particular, Joe Dixon, Sai Lai Lo, Tim Wilson, Cormac Sreenan and Paul Jardetzky for many useful discussions.

I am also indebted to the following people who have read and commented upon this dissertation: Ian Leslie, Sue Thompson, Matthew Doar, David Greaves, Andy Harter and Leslie French.

Special thanks to Salome, my wife, for her help in the typing and presentation of this work and more importantly giving her love and support to this effort.

Many thanks to Dr. Malcolm Wilkinson from Anamartic Limited for allowing me to include information on one of their products in this dissertation. Thanks must also go to Martyn Johnson and Chris Hadley, system administrators at the Lab, for all their practical assistance.

Thanks to my graduate colleagues for their encouragement and support. In this regard, special thanks to Peter Newman, Bhaskar Harita and David Greaves with whom I shared some memorable times as a member of the "Back-Room Boys" in the Old Music School.

During my research I received financial support, for which I am most grateful, from the Cambridge Commonwealth Trust, my wife, Salome, Clare Hall, the Computer Laboratory and the Committee of Vice Chancellors.

Finally, my deepest appreciation and praise goes to the LORD whose unfailing love was demonstrated many times during this research. In expression of this, and in the spirit of this effort, I quote the following:

A good man may have many troubles, but the Lord delivers him from them all.

Psalm 34:19

# Contents

| Pı | eface  | e e                                    | i   |

|----|--------|----------------------------------------|-----|

| A  | cknov  | wledgments                             | v   |

| Γε | ıble d | of Contents                            | vii |

| Li | st of  | Figures                                | хv  |

| Li | st of  | Tables                                 | ix  |

| G: | lossa  | ry of Terms                            | xi  |

| Tr | aden   | narks xx                               | iii |

| 1  | Intr   | roduction                              | 1   |

| 2  | Me     | mory Management Units                  | 5   |

|    | 2.1    | Introduction                           | 5   |

|    | 2.2    | Virtual Memory Techniques              | 5   |

|    |        | 2.2.1 Virtual to Physical Translations | 5   |

|    |        | 2.2.2 Control Mechanisms               | 7   |

|    | 2.3    | Implementation Strategies              | 7   |

|   | 2.4 | Specific Architectures                               |           | 9  |

|---|-----|------------------------------------------------------|-----------|----|

|   |     | 2.4.1 The Vax Architecture                           |           | 9  |

|   |     | 2.4.2 The Intel 80286                                |           | 11 |

|   |     | 2.4.3 The MC68851                                    | :         | 13 |

|   |     | 2.4.4 The HP Precision Architecture                  |           | 14 |

|   |     | 2.4.5 The MIPS Architecture                          |           | 15 |

|   | 2.5 | Summary and Conclusions                              |           | 17 |

| 3 | Vir | rtual Memory Management in Operating System Design   | :         | 21 |

|   | 3.1 | Introduction                                         |           | 21 |

|   | 3.2 | Multics                                              |           | 21 |

|   | 3.3 | The Cap Computer System                              |           | 23 |

|   | 3.4 | UNIX                                                 |           | 24 |

|   | 3.5 | BSD Unix                                             |           | 26 |

|   | 3.6 | VMS                                                  |           | 28 |

|   | 3.7 | Pilot                                                |           | 30 |

|   | 3.8 | Operating System/2                                   | . <b></b> | 31 |

|   | 3.9 | Summary and Conclusions                              |           | 33 |

| 4 | Vir | rtual Memory Management In MicroKernel Operating Sys | tems      | 35 |

|   | 4.1 | Introduction                                         |           | 35 |

|   | 4.2 | MACH                                                 |           | 36 |

|   |     | 4.2.1 IPC Mechanism                                  |           | 37 |

|   |     | 422 The Virtual Memory Management System             |           | 37 |

|    |     | 4.2.3  | External Pagers                          |

|----|-----|--------|------------------------------------------|

|    |     | 4.2.4  | Copy-On-Write Sharing in Mach            |

|    |     | 4.2.5  | Unix File Interface                      |

|    | 4.3 | Choru  | s                                        |

|    |     | 4.3.1  | The IPC Mechanism                        |

|    |     | 4.3.2  | The Virtual Memory Management System     |

|    |     | 4.3.3  | Copy-on-Write Mechanisms in Chorus       |

|    | 4.4 | Summ   | ary and Conclusions                      |

| 5  | Dog | ina Al | gorithms 49                              |

| O) | rag |        | gorithms                                 |

|    | 5.1 | A His  | torical Perspective                      |

|    |     | 5.1.1  | New Motivation                           |

|    | 5.2 | Tradit | ional Paging Algorithms                  |

|    |     | 5.2.1  | Combination of Local and Global Policies |

|    | 5.3 | Analy  | tical Paging Models                      |

|    |     | 5.3.1  | Reference String Models                  |

|    |     | 5.3.2  | Phase Transition Models                  |

|    |     | 5.3.3  | Markov Models                            |

|    |     | 5.3.4  | Lifetime Curves                          |

|    |     | 5.3.5  | Criticisms of the Lifetime Curve         |

|    |     | 5.3.6  | Simulation Models                        |

|    |     | 5.3.7  | Empirical Results                        |

|    | 5.4 | Sumn   | nary: New Framework and New Tools        |

| 6 | The | Design of an Object-Oriented Virtual Memory Interface | 65 |

|---|-----|-------------------------------------------------------|----|

|   | 6.1 | Motivation                                            | 65 |

|   | 6.2 | The Design Issues                                     | 65 |

|   |     | 6.2.1 Typed Objects                                   | 66 |

|   | 6.3 | The User Interface                                    | 66 |

|   |     | 6.3.1 Other Issues                                    | 69 |

|   | 6.4 | The Architecture                                      | 71 |

|   | 6.5 | Building An Object Library: A Simple Example          | 71 |

|   |     | 6.5.1 Benefits                                        | 73 |

|   | 6.6 | Using Different Handles                               | 74 |

|   |     | 6.6.1 The Type Interface                              | 74 |

|   |     | 6.6.2 A New Layer                                     | 75 |

|   |     | 6.6.3 A Brief Example                                 | 75 |

|   | 6.7 | Object Managers                                       | 77 |

|   |     | 6.7.1 Object Manager Interface                        | 78 |

|   |     | 6.7.2 Using Default Object Managers                   | 78 |

|   |     | 6.7.3 Benefits                                        | 79 |

|   | 6.8 | Summary                                               | 79 |

| 7 | Im  | olementation                                          | 81 |

|   | 7.1 | Introduction                                          | 81 |

|   | 7.2 | Hardware                                              |    |

|   | 7.3 | Wanda                                                 |    |

|   | •   | 7.3.1 The ANSA Testbench                              | 80 |

|   | 7.4 | New VM Structures                            |

|---|-----|----------------------------------------------|

|   | 7.5 | Object Management                            |

|   |     | 7.5.1 The Monitor Structure                  |

|   | 7.6 | The Interaction Protocol                     |

|   |     | 7.6.1 Created Objects                        |

|   |     | 7.6.2 Benefits                               |

|   |     | 7.6.3 Pagefault Handling                     |

|   |     | 7.6.4 Copy-On-Write Mechanisms               |

|   |     | 7.6.5 Paging                                 |

|   |     | 7.6.6 Object Routines                        |

|   |     | 7.6.7 Synchronisation                        |

|   |     | 7.6.8 Unix File Handling Routines            |

|   | 7.7 | Object Managers                              |

|   |     | 7.7.1 Logger                                 |

|   | 7.8 | Preliminary Performance Measurements         |

|   | 7.9 | Summary 9                                    |

| 8 | Per | formance of Traditional Paging Algorithms 99 |

|   | 8.1 | Introduction                                 |

|   | 8.2 | A Framework For Paging                       |

|   | 8.3 | Design and Implementation of the TestBed     |

|   |     | 8.3.1 PageData Structures                    |

|   |     | 8.3.2 Paging Interface                       |

|   |     | 8.3.3 Remote Paging Specification            |

|   |      | 8.3.4   | Recording Information                     |

|---|------|---------|-------------------------------------------|

|   |      | 8.3.5   | The Recorder                              |

|   | 8.4  | The Pa  | age Fault Algorithms                      |

|   | 8.5  | The P   | rogram Suite                              |

|   | 8.6  | The A   | nalysis of the Results                    |

|   | 8.7  | Result  | s                                         |

|   |      | 8.7.1   | A New Criterion for Lifetime Curves       |

|   |      | 8.7.2   | An explanation                            |

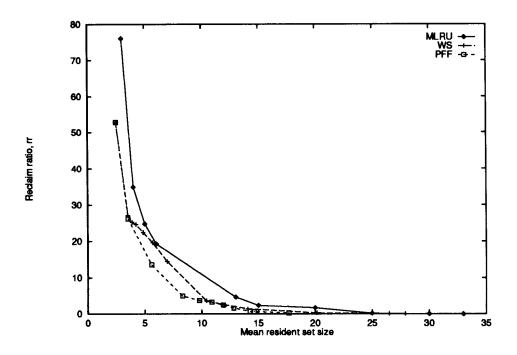

|   |      | 8.7.3   | Comparison of Different Paging Algorithms |

|   |      | 8.7.4   | Conclusions                               |

|   | 8.8  | Other   | Issues                                    |

|   |      | 8.8.1   | Service Time Issues                       |

|   |      | 8.8.2   | Performance of the Pager                  |

|   | 8.9  | Other   | <b>Objects</b>                            |

|   |      | 8.9.1   | Data Objects                              |

|   |      | 8.9.2   | Bss Objects                               |

|   |      | 8.9.3   | File Objects                              |

|   | 8.10 | Summ    | ary and Conclusions                       |

| 9 | Nev  | v Pagi: | ng Algorithms 129                         |

|   | 9.1  | Introd  | uction                                    |

|   | 9.2  | Design  | ı Issues                                  |

|   | 9.3  | Classif | fication and Testing                      |

|   | 9.4  | Result  | s                                         |

|    | 9.5   | Summary and Conclusion                   | 135 |

|----|-------|------------------------------------------|-----|

| 10 | Con   | clusions and Further Work                | 139 |

|    | 10.1  | Conclusions                              | 139 |

|    | 10.2  | Further Work                             | 140 |

|    |       | 10.2.1 Paging Issues                     | 140 |

|    |       | 10.2.2 Extending the User Interface      | 141 |

|    |       | 10.2.3 Evolution to a Distributed System | 142 |

|    | 10.3  | Final Word                               | 143 |

| R  | efere | nces                                     | 144 |

. . . . . . .

# List of Figures

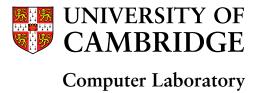

| 2.1 | The Inverted Page Table Technique               | 9  |

|-----|-------------------------------------------------|----|

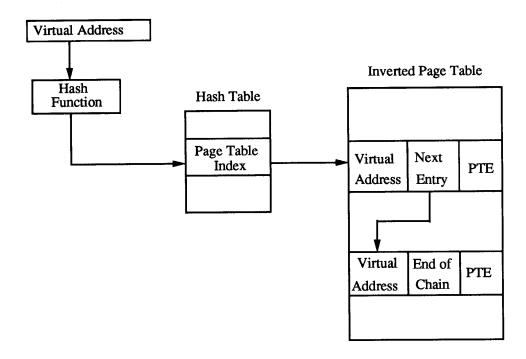

| 2.2 | The Vax Address Space                           | 10 |

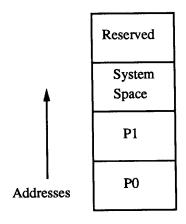

| 2.3 | Address Resolution on the 80286                 | 12 |

| 2.4 | A TLB Entry for the MIPS Architecture           | 16 |

| 4.1 | Management of Copy-On-Write Sharing in Mach     | 41 |

| 4.2 | Copy-On-Write Sharing in Chorus                 | 46 |

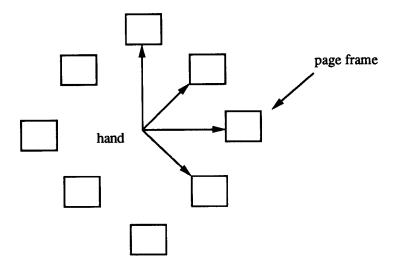

| 5.1 | Clock Algorithm                                 | 52 |

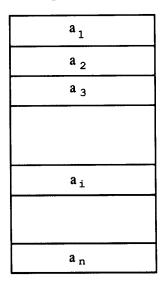

| 5.2 | The LRU Stack Model                             | 57 |

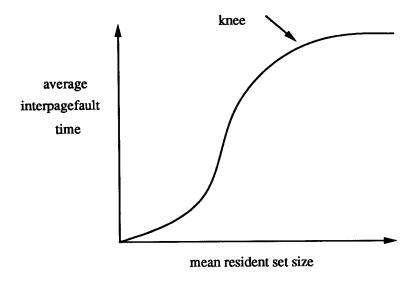

| 5.3 | The lifetime curve                              | 58 |

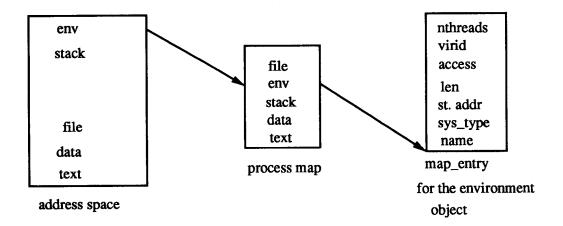

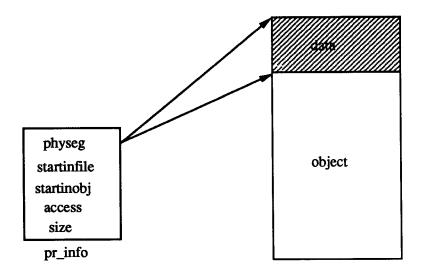

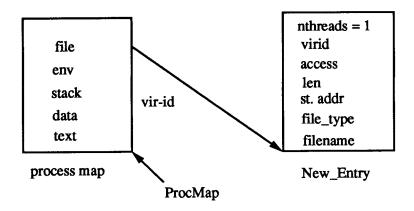

| 6.1 | The process map                                 | 67 |

| 6.2 | The CreateProcObject Call                       | 70 |

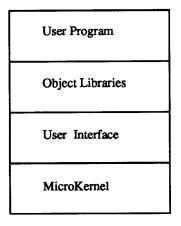

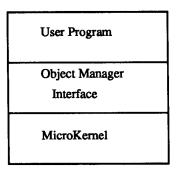

| 6.3 | The Architecture                                | 71 |

| 6.4 | ProcMap after the MapObject call                | 72 |

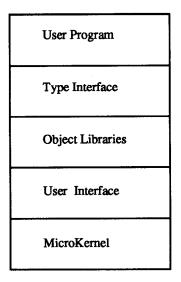

| 6.5 | The Modified Architecture                       | 75 |

| 6.6 | The Architectural Layers for the Object Manager | 79 |

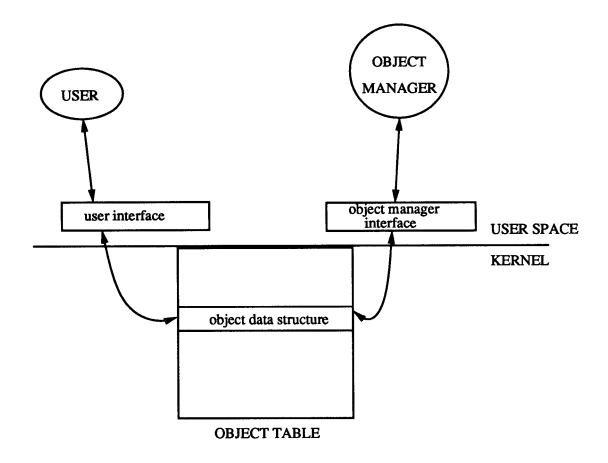

| 7.1 | The Overall System                              | 84 |

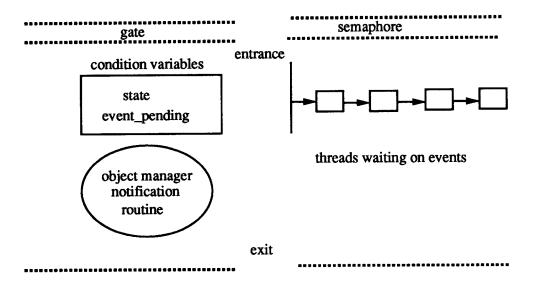

| 7.2  | The Object Monitor                                                                                       |

|------|----------------------------------------------------------------------------------------------------------|

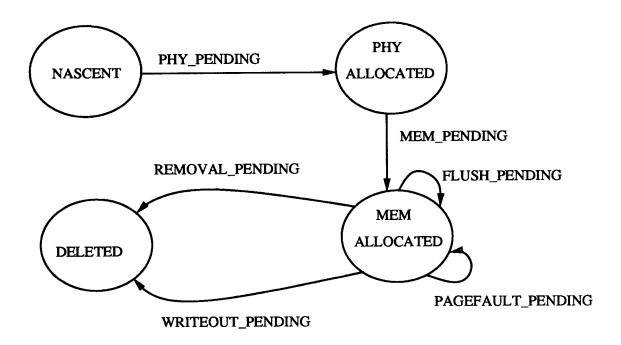

| 7.3  | The Interaction Protocol                                                                                 |

| 7.4  | The Object Manager                                                                                       |

| 8.1  | Paging Activity                                                                                          |

| 8.2  | The Recorder                                                                                             |

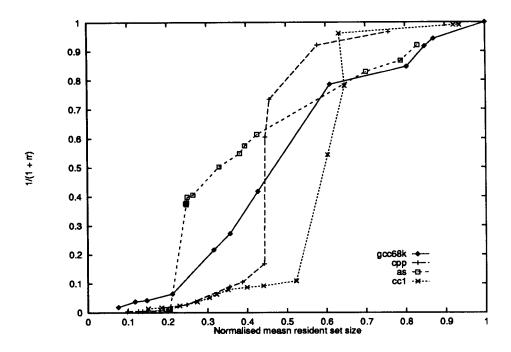

| 8.3  | The Interpagefault Time vs $1/(1+rr)$ for the text segments of the Compiler Suite using the WS algorithm |

| 8.4  | 1/(1+rr) vs Normalised mean resident set size for gcc68k and cpp 108                                     |

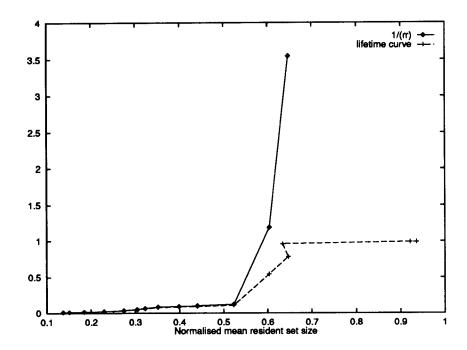

| 8.5  | Comparing $1/(1+rr)$ and $1/(rr)$                                                                        |

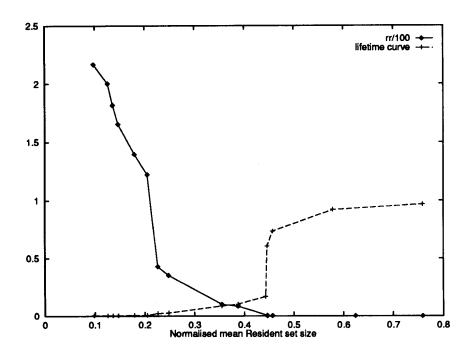

| 8.6  | Comparing $rr/100$ and $1/(1+rr)$                                                                        |

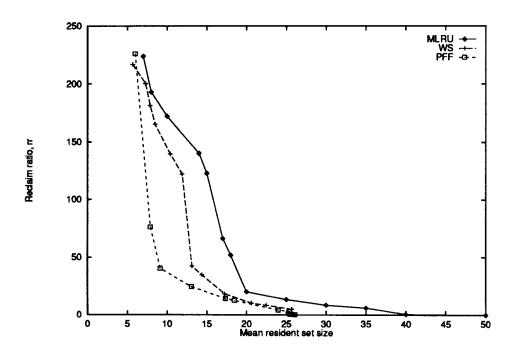

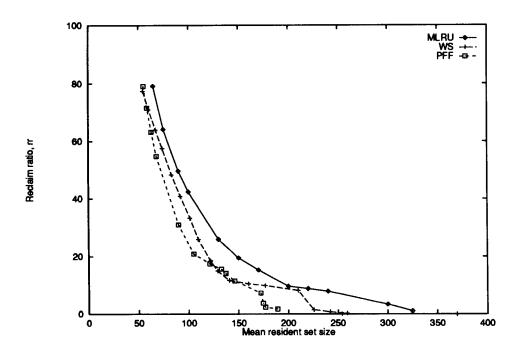

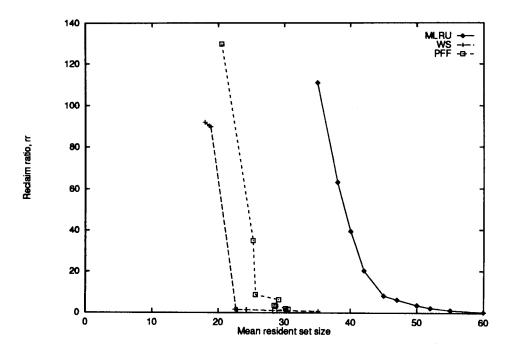

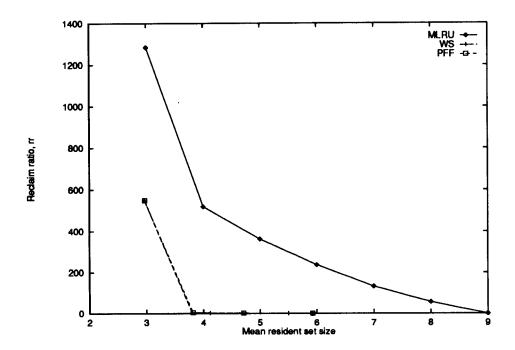

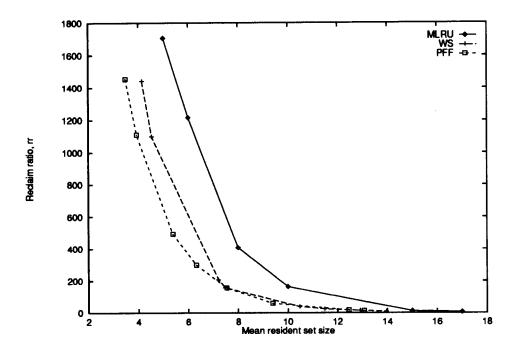

| 8.7  | Results for the text segment of gcc68k                                                                   |

| 8.8  | Results for the text segment of cpp                                                                      |

| 8.9  | Results for the text segment of cc1                                                                      |

| 8.10 | Results for the text segment of as                                                                       |

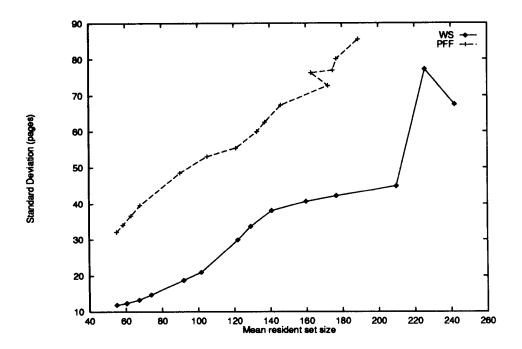

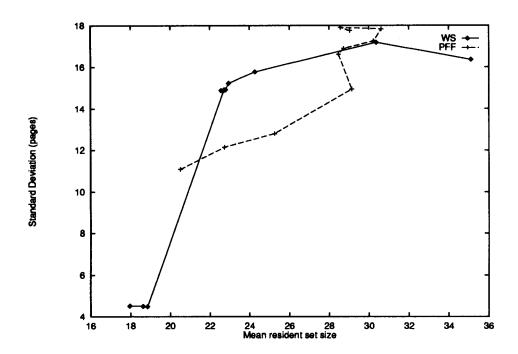

| 8.11 | Standard Deviation vs Mean resident set size for cc1                                                     |

| 8.12 | Standard Deviation vs Mean resident set size for as                                                      |

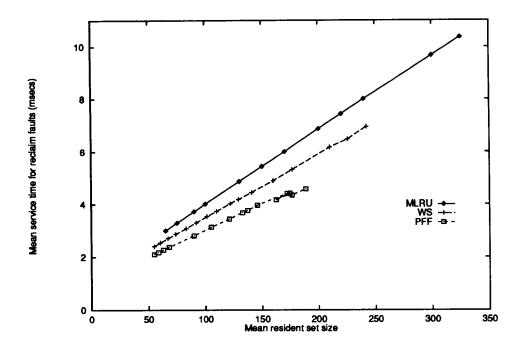

| 8.13 | Service Time Distribution for reclaim faults for cc1                                                     |

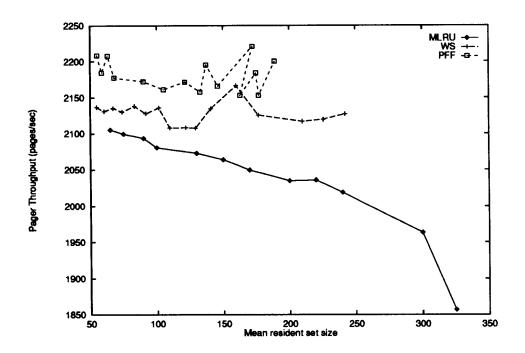

| 8.14 | Pager Throughput vs Mean Resident Set Size                                                               |

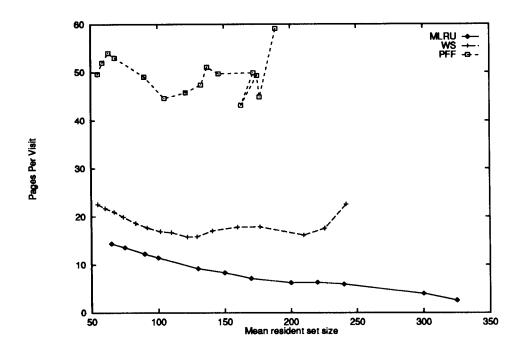

| 8.15 | Page Per Visit vs Mean Resident Set Size                                                                 |

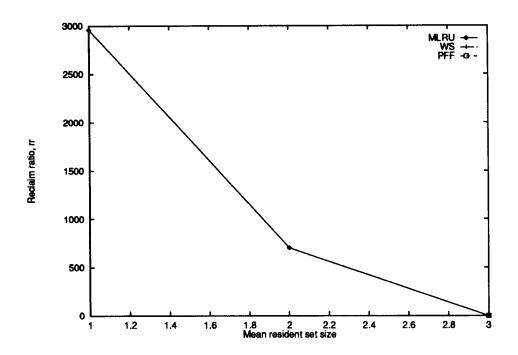

| 8.16 | Results for the data segment of cc1                                                                      |

| 8.17 | Results for the data segment of cpp                                                                      |

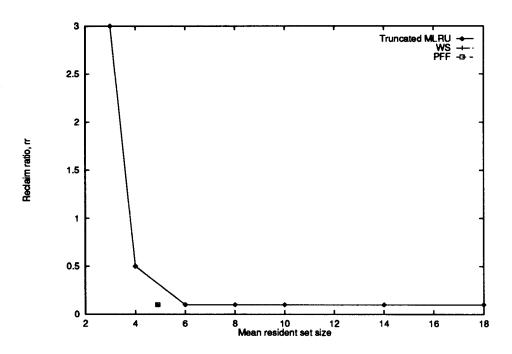

| 8.18 | Truncated Results for the data segment of as                                                             |

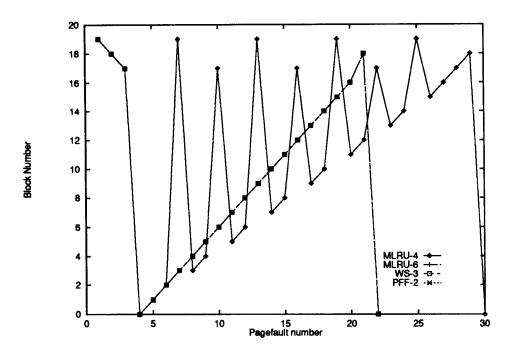

| 8.19 | Block Distribution Curves for the data segment of as                                                     |

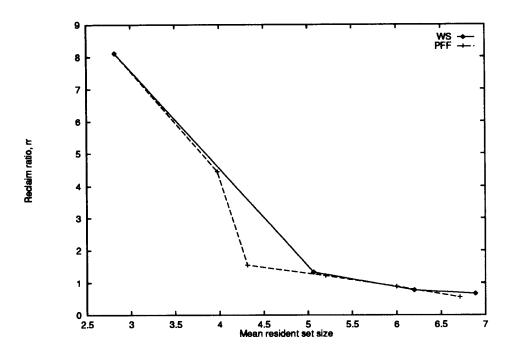

| 8.20 | Results for the bss segment of cpp                          |

|------|-------------------------------------------------------------|

| 8.21 | Results for the bss segment of cc1                          |

| 8.22 | Results for user_types.c                                    |

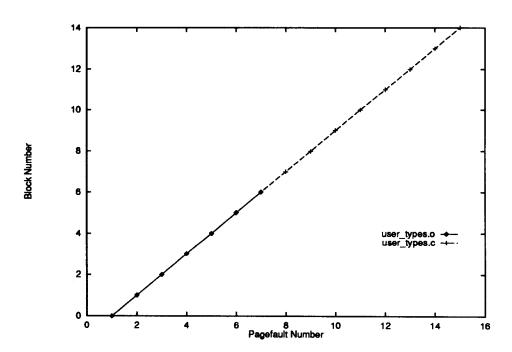

| 8.23 | Block Distribution Curves for user_types.o and user_types.c |

| 8.24 | Results for the intermediate file, test.cpp                 |

| 8.25 | Block Distribution Curves for test.cpp                      |

| 9.1  | A Unix Stream                                               |

| 9.2  | Paging for objects with highly sequential access patterns   |

| 9.3  | Service time for initial faults                             |

| 9.4  | Average Service Time for reclaim faults                     |

| 9.5  | Pager Throughput                                            |

| 10.1 | A Distributed System                                        |

# List of Tables

| 4.1 | The Memory-Mapping Inferface in Mach                    | 38  |

|-----|---------------------------------------------------------|-----|

| 4.2 | Kernel-Memory Manager Interface in Mach                 | 39  |

| 4.3 | The Memory Manager-Kernel Interface in Mach             | 40  |

| 4.4 | The Memory-Mapping Interface in Chorus                  | 44  |

| 4.5 | The Segment Interface in Chorus                         | 44  |

| 4.6 | The Mapper Interface in Chorus                          | 45  |

| 4.7 | The Local Cache Control Interface in Chorus             | 45  |

| 7.1 | Preliminary Performance Results                         | 96  |

| 8.1 | Values of $C_0$ for the GCC Compiler Suite $\ldots$     | 107 |

| 8.2 | Service Time Parameters for Different Paging Algorithms | 116 |

### Glossary of Terms

The number of the page on which the term is introduced appears in parenthesis.

ATC Address Translation Cache (14)

ATM Asynchronous Transfer Mode (2)

BCPL Basic Combined Programming Language (35)

BSPA BufStream Paging Algorithm (133)

CPL Current Privilege Level (12)

CPU Central Processing Ubit (3)

**DEC** Digital Equipment Corporation (23)

DOS Disk Operating System (31)

**DPL** Descriptor Privilege Level (13)

**DST** Descriptor Segment Table (22)

**DWS** Dampled Working Set (54)

GDT Global Descriptor Table (11)

GE General Electric (21)

GLRU Global Least Recently Used (52)

IBM International Business Machines (4)

INRIA Institut National de Recherche en Informatique et en Automatique (42)

I/O Input/Output (3)

ip Interpagefault Time (101)

**IPC** Interprocess Communication (36)

IRIM Inter-Reference Interval Model (62)

IRM Independent Reference Model (56)

KST Known Segment Table (22)

LAN Local Area Network (1)

LDT Local Descriptor Table (11)

LRU Least Recently Used (14)

LRUSM LRU Stack Model (56)

MIT Massachusetts Institute of Technology (21)

MLRU Modified LRU (104)

MMU Memory Managemeny Unit (2)

OS/2 Operating System/2 (31)

PFF Page Fault Frequency (54)

PMMU Paged Memory Management Unit (13)

PTE Page Table Entry (6)

QoS Quality-of-Service (79)

RAM Random Access Memory (1)

RISC Reduced Instruction Set Computer (1)

ROM Read-only Memory (16)

RPC Remote Procedure Call (43)

rr Reclaim ratio (100)

SCSI Small Computer System Interface (51)

SG Shared Globally (14)

SINMAN Systems Internal Names Manager (23)

SSPA SimpleStream Paging Algorithm (133)

SWS Sampled Working Set (53)

TLB Translation Lookaside Buffer (6)

VLSI Very Large Scale Integrated (1)

VSWS Variable-Interval Working Set (54)

WAN Wide Area Network (2)

WS Working Set (53)

WSI Wafer Scale Integration (51)

WSPA WriteStream Paging Algorithm (133)

## **Trademarks**

Unix is a registered trademark of AT&T.

SunOs is a registered trademark of Sun MicroSystems.

Chorus is a registered trademark of Chorus Systems.

## Chapter 1

## Introduction

At present, computer technology is evolving at a rapid rate. The processing power of modern microprocessors is greater than the mainframes of the Sixties, and with the emergence of RISC technology, processors are likely to continue getting faster. In addition, continuing improvements in VLSI techniques will ensure that the cost of producing these units continues to fall. This phenomenon has already made possible the widespread use of workstations and personal computers.

With cheaper processors becoming widely available, multiprocessor architectures are being built using different interconnection networks. These configurations attempt to exploit parallel computing to achieve improved performance which could be sustained as the number of processors is increased. These systems are providing a serious challenge to mainframe architectures in the area of large-scale scientific computing.

Another dramatic development has been the declining cost of random access memory or RAM. New techniques will soon make four Megabyte (MB) RAM chips a commonplace item. Hence, in the near future, most machines will have large amounts (i.e. 64–128 MB) of main memory. Non-volatile memory, though more expensive than RAM, also continues to fall in cost and provides an effective alternative to disk storage in certain computer environments.

Computer networks are also increasing in speed. The standard 10 Megabit-per-second (Mbps) Ethernet local area network or LAN of the Eighties will soon be superseded by 100 Mbps Token Ring systems. In addition, with the appearance of fast packet switching,

wide area networks or WANs are being built to run at speeds of 500 Mbps to one Gigabit per second (Gbps) using Asynchronous Transfer Mode (ATM) techniques. These networks will carry new services, e.g. voice and video, and provide a large number of high bandwidth channels.

Based on these developments, the new computing environment will comprise a multitude of powerful machines, having large amounts of memory connected to fast networks. The software requirements for this new environment are radically different from the computing models of the last three decades. This is especially true in the area of **operating systems**. For example, Unix, one of the most popular operating systems for the last two decades, was developed for the time-sharing environment of the early Seventies. At that time networking was minimal, large amounts of primary memory was a rare occurrence, and disk storage was also limited.

Within the operating systems environment, one of the areas that will be affected is the memory management system. This is because the memory management algorithms for current operating systems are based on the assumption that memory is a scarce resource. With large amounts of cheap RAM becoming readily available, it is possible to adopt a more flexible approach. Perhaps, the most significant influence will come from the faster, more sophisticated memory management units or (MMUs) of modern microprocessors. These MMUs now use sophisticated virtual memory management techniques, which were previously only found on mainframe and minicomputer systems.

Virtual memory techniques will therefore play a major role in delivering the benefits of the new environment to its users. New virtual memory management systems must be designed to give users greater flexibility by providing simple yet powerful user interfaces. At present, users on most systems use one interface when accessing conventional program segments which is defined by the programming language and another interface when accessing objects residing in secondary storage which is defined by the operating system. If these two interfaces can be harmonised then the programmer can access objects in a unified manner, without worrying about the need to move objects to and from secondary storage. These new interfaces should also be designed with the intention of supporting persistent storage for object-oriented languages, such as C++, and object-oriented databases systems since they are becoming important facilities in many computing environments.

The use of the memory-mapped technique, in which objects are mapped into the user's address space on demand, is a key requirement since it hides the existence of the memory hierarchy and makes the system, not the programmer, responsible for the movement of data between main memory and secondary storage. Though memory mapped interfaces have been implemented on several operating systems, they do not give added functionality to the

user as they do not provide the facilities for users to easily implement logical abstractions.

The microkernel approach to operating system design, in which most of the services previously done by a monolithic operating system are now implemented using user-level processes, is also becoming very popular as it enhances the flexibility, portability and modularity of the system. This approach has been adopted in the design of a number of operating systems including Mach and Chorus. It should also be used in this effort since it emphasizes minimal changes to the microkernel with most of the work being done by other user-level processes.

Paging, the movement of the pages of a process between main memory and secondary storage as the process executes, is an important service of virtual memory management systems. Since program sizes are increasing, support for paging will remain an essential function of these systems for some time to come. However, as CPU speeds are increasing much faster than disk speeds, an I/O bottleneck may develop where the CPU spends a significant amount of time waiting for page requests to be satisfied.

To address this problem, it is necessary to review traditional paging techniques including conventional paging algorithms with a view to developing better analytical models of program behaviour. Previously, the development of paging models has been hampered by a poor framework with which to compare different paging algorithms and a lack of data on the paging activity of programs running on modern operating systems. This requires the development of a testbed from which experimental data can be obtained.

To improve overall efficiency of the system, an examination of the use of conventional paging algorithms on different types of objects is needed. It is essential to develop new paging algorithms that better reflect the different access patterns of various objects. Thus, it is necessary to implement paging on a **per-object** basis in which different objects may be paged using different paging algorithms. This will also facilitate the development of new paging algorithms for objects whose access patterns are well understood.

This thesis explores the issues discussed above. A new user interface is proposed and implemented on Wanda, an experimental operating system developed at the University of Cambridge. A new framework for comparing different paging algorithms is described and is used to analyse the performance of traditional paging algorithms using the GCC Compiler Suite. New paging algorithms are designed and implemented for objects that are accessed in a highly sequential manner.

#### **Outline**

An outline of this dissertation is presented below.

Chapter 2 reviews various memory management units highlighting features that affect operating system design.

Chapter 3 outlines the virtual memory management system of several operating systems, ranging from Multics, the ancestor of most present-day operating systems, to OS/2, the new operating system for Intel microprocessors proposed by IBM.

Chapter 4 examines the microkernel approach to operating system design using two prominent microkernels, Mach and Chorus.

Chapter 5 explores the issues in the design, implementation and analysis of paging algorithms and shows the need for a new framework.

Chapter 6 outlines the design of the new user interface while Chapter 7 details its implementation.

In Chapter 8, a new framework for the analysis of paging algorithms is developed and results for different paging algorithms on the GCC Compiler Suite are presented and compared.

Chapter 9 explores the design and implementation of new paging algorithms to support objects that are accessed in a highly sequential manner.

Finally, Chapter 10 details the conclusions and future work that can be derived from this effort.

## Chapter 2

# Memory Management Units

#### 2.1 Introduction

Different approaches to virtual memory management are clearly reflected in the design of various memory management units. This chapter investigates the features of several MMUs, and in particular, aspects of their design that influence the virtual memory management system.

## 2.2 Virtual Memory Techniques

#### 2.2.1 Virtual to Physical Translations

Virtual memory is based on a simple concept. The programmer is given a large, linear set of addresses, commonly called an **address space**. These addresses, known as virtual addresses, are generated irrespective of the physical addresses at which the information is actually stored. The translation from a virtual to a physical address is done as the program is being executed.

Both physical and virtual addresses are divided in small partitions called **pages**, typically from 256 bytes to 8 Kilobytes (KB) in size. A page is the unit of translation between physical and virtual addresses. Each individual page in an address space is represented

by a virtual page number, **vpn**, while each physical page is represented by a physical page number, **ppn**. Translation, therefore, involves taking the virtual address obtaining the vpn and finding the corresponding ppn. **Pagetables** are structures that contain the mapping between the vpn and the ppn and are usually stored in main memory. However, since access to main memory is slower than accessing other parts on the CPU chip, the most recent virtual to physical translations are stored in a fast **Translation Lookaside Buffer** or TLB usually located on or near the CPU chip. When a virtual address is generated, the TLB is first searched. If the translation is found in the TLB, called a TLB hit, the corresponding physical address is put out on the address bus.

If the translation is not found in the TLB, called a TLB miss, the pagetables in main memory are consulted to obtain the corresponding ppn. Translations in the pagetable are valid if a valid bit is set in the corresponding pagetable entry or PTE. If a physical page has not been assigned to the vpn, this condition is known as a pagefault and the operating system assigns a new page and transfers the data from secondary storage to the page. This activity is called paging and forms an integral part of virtual memory management.

The proportion of TLB hits for a given process is called the hit ratio. A very high ratio means that most of the virtual to physical translations are found in the TLB. Thus improved performance can be obtained by increasing the hit ratio of the TLB. In addition, since virtual to physical translations take place while the process is executing, it is possible that a process with a very large address space can be executed on machines with small amounts of physical memory. This is because most processes execute in relatively small regions of their address spaces for relatively long intervals.

This behaviour is referred to as locality of reference. A program spends long periods of time within a locale and shorter periods moving from one locale to the next. The time in a given locale may be represented as a phase in the execution cycle of the program. Thus the amount of physical memory that the process requires to continue execution is small and can be assigned as it executes rather than satisfying its entire requirements beforehand. The working set of each phase comprises the set of pages that the program accesses while in that phase. The resident set is defined as the set of pages in main memory that can be accessed by the program. The same principle can be extended to support a multi-tasking environment where different processes are concurrently executing in different address spaces.

#### 2.2.2 Control Mechanisms

Multi-tasking also requires protection mechanisms which prevent processes from accessing or changing information that would damage or corrupt the system. The need for these mechanisms was realised in the early development of operating systems to protect the supervisor or executive program against unauthorised access by user programs. So, in addition to a physical page number, pagetable entries usually contain bits that govern access to the page. These include the supervisor/user bit, which, when set, indicates that the page could only be accessed in supervisor mode. There are bits to indicate read, write and sometimes execute access modes. Control mechanisms have been extended to cover several aspects of operating system design, including the global sharing of pages by all processes, represented by a global bit, as well as a bit to indicate whether data from the page may be cached by external caches. The reference bit indicates that an address on a page has been accessed while the modified bit indicates that an address on the page has been modified. These bits provide the hardware support for many paging algorithms used in modern operating systems.

## 2.3 Implementation Strategies

The different approaches to implementing hardware support for virtual memory are primarily related to the partitioning of the address space and how the virtual to physical translation is performed. The simplest approach is the **paged** approach in which the address space is divided into pages. There is only one pagetable per process and translation is done by using the vpn as an index into the table. This technique is simple and fast. However, the size of the pagetable is proportional to the size of the address space. In addition, the entire pagetable must be kept in main memory thus limiting the amount of multi-tasking that is possible due to a large amount of memory being used as pagetables.

Another method, which has been employed, is the segmented architecture. Here the address space is divided into large sections called segments. The main advantage in using this approach is that since segments are very large and only a few are needed in memory at the same time, the virtual to physical address translations for active segments can be held in special registers on the CPU. There is no need for a TLB. In addition, an entire segment can be paged in a single operation. However, since segments are associated with large amounts of physical memory, processes that do not use most of the segment will cause the corresponding physical memory to be under-utilised. This phenomenon is known as fragmentation and can severely reduce the performance of the overall system.

The segmented-paged architecture combines the two above approaches. In this scheme, segments are divided into pages so that each active segment has an associated pagetable. This architecture has several advantages. Firstly, paging reduces the fragmentation problem of the segmented architecture as there is no need to reserve physical memory for an entire segment. If a segment is accessed and the corresponding physical page is not there, a pagefault will be generated. In addition, only segments that are currently active in memory, must have pagetables assigned to them. Thus pagetables may be built as required. Finally, since it is possible to provide access control mechanisms for segments as well as pages, a greater degree of sharing can be obtained. Using different access control settings in the segment descriptors, it is possible for different users to share the same object (i.e. same pagetable) with different access rights.

The next approach to be considered is the Inverted Page Table (IPT) technique. With this method, shown in Figure 2.1, a hash function is performed on a virtual address to yield an index into a hash table. The corresponding value in the table is a physical page number referred to as a pagetable index or PTI. The PTI is used to index into an inverted pagetable to yield a virtual address. If the vpn in the IPT matches the vpn of the virtual address, the PTI is the ppn for that translation. This appears to be the reverse of normal translation – hence the term inverted pagetable. The main advantage of this technique is that the size of the IPT is proportional to the amount of physical memory the system supports.

However, different virtual addresses may hash to the same PTI. This is known as a collision. One way to resolve this is to keep the relevant virtual addresses in a linked list in the IPT so that the system follows the chain until it finds the correct virtual address or the chain ends which indicates a pagefault.

The main disadvantages of the Inverted Page Table approach are that the hash table and the IPT must be resident in main memory and two accesses are required for one translation. These effects can be reduced by using a sizeable TLB. In addition, only a limited amount of global sharing, in which an object is located at the same virtual address for all address spaces, can be easily supported. This is because the hash function makes it very difficult to map the same physical address onto different virtual addresses.

The methods described above are typically executed by the hardware once the relevant tables are set up and the corresponding registers are loaded. Another option, which is becoming increasingly popular, is to allow TLB misses to be managed entirely in software. Instructions are provided to obtain the faulted address and load the virtual to physical translation into the TLB, but exactly how the translation is done is a matter for the operating system designer not the hardware engineer. There are obvious advantages to

Figure 2.1: The Inverted Page Table Technique

this approach. Namely, the operating system designer is free to implement unique and specialised solutions to meet the specifications of his system while the amount of hardware design and silicon needed for the MMU may be severely reduced. This scheme may perform worse than a solution implemented in hardware if a significant number of TLB misses occur, thus a high TLB ratio is essential for good performance.

## 2.4 Specific Architectures

In this subsection, we examine several memory management units that use techniques described above giving a detailed description of a design based on each of the above approaches.

## 2.4.1 The Vax Architecture

The Vax is an example [Dig86] of a paged virtual memory architecture with some unique characteristics. The system uses a large pagetable as the system pagetable or spt. The physical address and length of the spt are kept in special registers known as the System

Figure 2.2: The Vax Address Space

Branch Register (SBR) and the System Length Register (SLR) respectively. All virtual address translations are done via the spt.

The address space of a process, shown in Figure 2.2, is divided in four fixed-size regions. P0 and P1 are regions that are specific to the individual process while system space is shared by all processes. The P0 region grows linearly upwards and is used to map the text and data segments of a process. The P1 region grows downwards. The stack as well as other control information are mapped in this region. The Vax supports a four Gigabyte address space in which the P0 and P1 regions occur in the first two Gigabytes with one Gigabyte used for system space and the other Gigabyte reserved for future use. The architecture employs a page size of 512 bytes.

P0 and P1 regions are represented by pagetables which are assigned from the spt. The start of these regions in the spt are indicated by the **p0br** and **p1br** registers while their lengths are placed in the **p0lr** and **p1lr** registers respectively. To translate a virtual address in the P0 region, the virtual page number is added to the p0lr register. The result is used to index into the spt to get the pagetable entry which contains the physical page number. Thus two memory accesses are required to do a translation in the P0 or P1 region. For an address in system space, the spt is used directly. This means that all processes see the same data in system space.

This scheme has a number of drawbacks. Firstly, to support a large virtual address space, the system pagetable must also be large. Secondly, to have small pagetables for the P0 and P1 regions, logically independent segments must be placed very close to each other, making it difficult to dynamically grow segments. Finally, though system space allows processes to share common utilities, it is difficult to provide some form of *limited* access

control where a small number of processes are required to have access to data, possibly with different access rights. The data has to be mapped into the address space of each of the processes involved using different pagetables. This introduces problems in keeping track of modification to pages since a number of pagetables must be simultaneously consulted, resulting in poor performance.

The Vax supports four different modes of privilege, namely, kernel, executive, supervisor and user. The kernel mode is the most privileged followed by the executive and then supervisor modes respectively. The user mode is the least privileged. By combining these privilege modes with read and write controls, it is possible to support a wide range of access control levels. The system works via the following rules:

- 1. The access modes supported by the system are read/write, read-only and none.

- 2. Whichever level has read access, all more privileged levels also have read access.

- 3. Whichever level has write access, all more privileged levels also have write access.

For example, the access mode, supervisor-read-only and kernel-write, means that in kernel mode the page may be read from or written to, in executive or supervisor modes the page is read-only, while in user mode, it is not accessible. The access control modes are represented by four bits in each pagetable entry. There is also a valid bit as well as a modified bit. The Vax 11/780, the first implementation of this architecture, employed a TLB consisting of 128 entries, with a reported hit ratio 98% [Hennessy90, pages 441-444].

#### 2.4.2 The Intel 80286

The segmented approach is seen in several architectures including the Burroughs B5000, PDP series and more recently the 80286 microprocessor [Ciminiera87], [Hennessy90, pages 445–449]. The 80286 supports a one Gigabyte address space and offers a maximum physical size of 16 MB. Segments are 64KB long. A virtual address is comprised of two components, a segment offset, which is 16 bits long, and a segment selector. The address resolution scheme is shown in Fig. 2.3.

Each process has two segment descriptor tables, the local descriptor table or (LDT) and the global descriptor table or (GDT). The T1 bit in the segment selector indicates which table must be accessed to obtain the relevant segment descriptor. Like the Vax, global segments are seen by all processes. The privilege level of a segment is represented by two bits in the segment selector called the RPL field. Segment selectors are loaded into four

Figure 2.3: Address Resolution on the 80286

registers in the CPU. These include the code, data and stack segment registers. The fourth segment register can be used to access another segment. When a context switch occurs, these registers are loaded with the code, data and stack selectors for the next task.

An interesting feature of the 80286 MMU design is its access control mechanism. There are four levels of privilege with level 0 being the highest and level 3 being the lowest. The current privilege level or CPL of a process is the privilege level contained in its stack and code segment selectors. The access rules may be summarised as follows:

- 1. Data segments are accessible only by tasks at the same or higher level of privilege.

- 2. Subroutines can only be called by tasks at the same or lower levels of privilege than the called routine.

Each segment descriptor contains an access control byte which includes a valid or present bit, a read/write bit as well as an executable bit, which is set for code segments. There are bits which indicate the direction segments are expected to grow and an access or reference bit which is set by the hardware when the segment descriptor is accessed. This can be reset periodically by the operating system and hence be used as an indication of how frequently a particular segment is referenced.

In addition, there is a two-bit field in the access control byte that indicates the **descriptor** privilege level or DPL for that segment. When a segment register is loaded with a new value, access control checking is invoked on the DPL field to ensure that unauthorised access does not occur. When a data segment is loaded, the hardware checks that the CPL is the same or less than (i.e. greater privilege) the DPL of the segment.

Transfer of control to other segments is carefully checked to ensure that the transfer address is accessible by the task, the constraints of the privilege level are met, and the transfer destination address is the correct entry point for the routine. This is done using a gate mechanism which handles the transfer of control to another routine via a call-gate. A task gate handles the transfer of control to another task. In addition, an interrupt gate handles interrupts while exceptions are fielded via a trap gate mechanism.

#### 2.4.3 The MC68851

The complexity of the segmented-paged architecture is reflected in the design of the MMUs adopting this scheme. These MMUs therefore require a larger amount of silicon and depending on the number of features that the designers want to support, an off-chip MMU is sometimes built. We examine one such MMU: the paged memory management unit chip of the 68020, the MC68851, also known as the PMMU [Mot86], [Milenkovic90, pages 81–82]. This chip supports a total address space of 32 Gigabytes which is subdivided into eight 4-Gigabyte regions. Each region is associated with a task number or alias and contains the address space of an individual task. A complete virtual address comprises a task alias and the virtual address generated within the address space of that task.

Translations are done using a multi-level translation tree starting from a designated root pointer. The tree may be up to five levels in depth, each level containing a pointer to the next table until the pagetable is reached. At each level of the tree, access control mechanisms can be applied. This allows different tasks to share the same segment with different access control privileges. There are bits in each descriptor table at each level to indicate supervisor/user access as well as read-only access which signifies that the segment or page is protected against writing in both supervisor and user privilege modes.

An interesting feature of the MC68851 is that it supports both long and short segment and page descriptor formats. Essentially, the short descriptors are 2 bytes long and access control is governed by the mechanisms already mentioned above. The long descriptors are 4 bytes long and contain two additional 3-bit fields for various read and write access privileges. This allows the operating system designer as well as application engineers to build very sophisticated access control mechanisms.

The page descriptor also has several control bits including a lock bit, which locks the translation in the TLB, a modified bit and a reference bit. There is also a cache inhibit (CI) bit which, if set, specifies that addresses on the corresponding page may not be stored by external caches. A global bit, which indicates that the translation is shared by all running tasks, is also present.

Another distinguishing feature of the MC68851 is that a page descriptor in one pagetable can point to another descriptor in a different pagetable. This indirection allows the same translation to be shared by all tasks using the page and thus the state of the modified and used bits reflect the use of the page by all the tasks. The PMMU also supports several page sizes, from 256 bytes increasing in powers of 2, to 32 KB. This allows the operating system designer to choose an appropriate page size.

The Address Translation Cache or (ATC), another name for a TLB, contains 64 entries and is fully associative. The logical address part of a TLB entry contains the tag, the logical address and a bit which indicates if the entry is shared globally (SG) by all tasks. If the global bit is set in a page descriptor, then the SG bit is also set in the ATC. When the SG bit is not set, a match occurs if both the task alias and the virtual address match the logical address in the ATC.

However, when the SG bit is set, only the virtual address field is examined and comparison of the task alias field is suppressed. Thus the match will be found by every task and only one entry in the ATC is sufficient. Moreover, since entries in the ATC are replaced using a modified **Least Recently Used** or (LRU) policy, globally shared entries that are frequently accessed will remain in the ATC for long periods, substantially improving performance.

Transfer of control to other routines with different access privileges is achieved using the CALLM instruction. This instruction is executed using special module descriptors or gates. The address of the module descriptor is passed during the CALLM call and is checked to ensure that the corresponding page descriptor has its gate bit set. This bit indicates that the module is valid and prevents a user from maliciously or erroneously using an invalid module descriptor. The instruction may also specify that a stack change must occur. This forces the arguments to be copied onto a separate stack.

## 2.4.4 The HP Precision Architecture

The inverted pagetable approach is gaining popularity because of its simplicity and its ability to efficiently support very large sparse address spaces. The **Precision Architec-**

ture (PA) is a RISC architecture announced by Hewlett-Packard (HP) in 1986 [Hew87], [Mahon86]. The MMU supports three different configurations. Level 0, which uses absolute addressing while Level 1 and Level 2 provide virtual addressing.

The virtual memory system is structured as a set of different address spaces, each comprising 4 Gigabytes. Level 1 contains  $2^{16}$  address spaces while level 2 supports  $2^{32}$  address spaces. The individual address spaces are specified using space registers and are divided into 2 KB pages. There are eight space registers labelled 0 through 7. There are also two TLBs, an instruction TLB (ITLB) and a data TLB (DTLB) – though it is possible to combine the two to form a single TLB. Each TLB entry has a 15-bit access ID field as well as an access type field which forms part of the protection mechanism of the system.

The system uses an inverted pagetable which may have negative offset values. These values are used to indicate the mapping of virtual I/0 devices. The PA also has an elaborate access control mechanism. There are four levels of privilege ranging from level 0 to level 3, with level 0 being the most privileged. Access bits for read, write and execute operations are also provided. There are four control registers that contain protection identifiers associated with the current process. These contain 15-bit fields and one of them must match the access ID field in the TLB before access to the page is granted.

The access type field is subdivided into three fields, a type subfield, privilege level 1 (PL1) and privilege level 2 (PL2). The type subfield contains the access bits mentioned above, but the PL1 and PL2 subfields qualify access. For read access, the current privilege level (CPL) must be at least as privileged as PL1. For write access, the CPL must be at least as privileged as PL2. For execution access, the CPL must be as least as privileged as PL1 but no more privileged than PL2.

Other features of the MMU include reference, valid, and modified bits. There is also a page reference trap bit which, when set, causes a page reference trap interrupt when a data reference is made to the page. This is used for debugging. In addition, there is a break bit which also causes a data memory break trap interrupt when instructions that modify data use this translation.

### 2.4.5 The MIPS Architecture

As previously mentioned, many operating system designers are beginning to favour the software TLB approach as it allows for greater flexibility. The MIPS R2000/R3000 architecture employs such an approach [Kane88].

The architecture supports a 4-Gigabyte address space of which two Gigabytes can be

Figure 2.4: A TLB Entry for the MIPS Architecture

accessed in user mode. When a process is executing in kernel mode, three regions can be accessed. Firstly, there is a 512 MB cached, unmapped segment. This is used to map the first 512 MB of physical memory into the kernel address space. References to this region can be cached but no entries are stored in the TLB. This is normally used for the operating system. Secondly, there is another 512 MB segment which is both uncached and unmapped. This is typically used for I/0 registers, read-only memory (ROM) and disk buffers. Finally, there is a 1-Gigabyte virtual address space that is mapped and is used for setting up pagetables as well as allocating memory for stacks and dynamic data structures. This region allows mapping on a per-page basis.

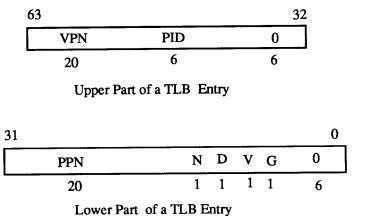

The system supports a page size of 4KB and a TLB containing 64 entries. As shown in Figure 2.4, each entry includes a vpn and a six-bit process identifier (PI) field, which allows multiple processes to share a TLB. The other part of the entry comprises the ppn and bit fields to indicate constraints on the use of the page. The N bit specifies whether data on the page can be cached and the dirty bit indicates whether data has been modified. The valid bit indicates whether the entry in the TLB is valid and the global bit indicates whether the page is globally shared. There are two registers that are used to read, write and probe the TLB. These registers are referred to as the Entry Hi and Entry Lo registers and correspond to the two parts of each TLB entry. When an address translation exception occurs, these registers are loaded with relevant information about the address that caused the exception.

## Exception Handling Using the Software Approach

Two additional registers are used in handling TLB misses. They are the **index** and **random** registers. The architecture provides the exception handler with four instructions to manipulate the TLB. These are:

- Translation Lookaside Buffer Probe (tlbp) this probes the TLB to see if an entry matches the Entry Hi register contents. If a match occurs, the index of the entry is loaded into the index register.

- Translation Lookaside Buffer Read (tlbr) this instruction loads the Entry Hi and Entry Lo registers with the contents of the TLB entry specified by the contents of the index register.

- Translation Lookaside Buffer Write (tlbw) this instruction loads the TLB entry which is specified by the index register, with the contents of the Entry Hi and Entry Lo registers.

- Translation Lookaside Buffer Writer Random (tlbwr) this instruction loads the TLB entry which is specified by the random register with the contents of the Entry Hi and Entry Lo registers.

When a TLB miss occurs, the exception handler first invokes the tlbp instruction to find out if there is a TLB entry for the faulted address. If a TLB entry exists, it checks the state of the bit fields to determine why the translation was not executed. If an entry does not exist, it must replace an entry in the TLB if the TLB is full. To do this, it loads the index register with the TLB entry it is going to replace and then invokes the tlbr instruction. If the TLB entry is being replaced randomly, then the value of the random register is used.

The exception handler stores the contents of this entry in its software data structures. It then puts the contents of the correct translation into the Entry Hi and Entry Lo registers respectively and performs a write index or write random instruction to load the translation into the TLB.

## 2.5 Summary and Conclusions

In this chapter different approaches to the design of MMUs were surveyed and implementations based on each approach were examined. The paged approach has several deficiencies including large pagetables, its inability to manage logically different entities efficiently as well as inadequate mechanisms for sharing objects with different access rights. The segmented scheme has the advantage of not requiring TLB support. However, the problem of fragmentation associated with this scheme represents a serious drawback.

The segmented-paged approach combines the benefits of both the paged and segmented architectures. The added complexities associated with this design are outweighed by the advantages of smaller pagetables, no segment fragmentation problems, and the ability to share objects with different access rights. Improved VLSI techniques now allow these MMUs to be on the CPU chip as seen in the 68030's and 68040's. It is interesting to note that Intel, the manufacturer of the 80286 microprocessor, has switched to the segmented paged-architecture for the 80386's and 80486's.

The inverted pagetable technique allows the total pagetable size to be proportional to the size of physical memory and not the size of the virtual address space. Thus it manages large sparse address spaces with great efficiency and since the size of an address space continues to increase (e.g. 64 address bits for the Precision Architecture), this approach will be increasingly adopted. However, the inability of this scheme to easily support an object that is mapped into several address spaces at different virtual addresses with different access rights is a severe hindrance for systems using the memory-mapped approach.

The software-managed TLB approach is the most flexible of all the schemes. It also requires minimal hardware and allows the system designer to implement software data structures to support new features for building advanced virtual memory management systems. As CPU speeds increase, the cost of handling TLB misses in software will fall and thus this approach will be more frequently used. At present, however, the cost of a TLB miss when using this approach is still about 10 times slower on some architectures [Edenfield90] when compared with the other techniques that use hardware mechanisms to find the correct translation.

In addition to providing sophisticated access control mechanisms, most MMUs have features which aid the implementation of virtual memory management systems. These include reference and modified bits for paging algorithms, TLB support for multi-tasking and the cache inhibit line for cache coherency. There is also support for the global sharing of objects as well as debugging as seen in the Precision Architecture. Given the continuous improvements in VLSI techniques, more features will continue to be introduced.

Using these features, virtual memory management systems can be designed to provide efficient and flexible interfaces that contribute significantly to the design of modern operating systems. The virtual memory management systems of a diverse set of operating systems are examined in the next chapter.

## Chapter 3

# Virtual Memory Management in Operating System Design: An Historical Perspective

## 3.1 Introduction

From its introduction on the Atlas computer system in 1961 [Kilburn62], virtual memory has been employed in the design of the memory management of various operating systems. Initially, the cost of hardware support for virtual memory limited its use to large mainframe environments. However, with the continuous improvements in VLSI design, it has been introduced in minicomputers and, more recently, on microprocessor architectures. This chapter examines virtual memory management in seven operating systems and the facilities provided by these systems using virtual memory techniques.

## 3.2 Multics

Multics was developed as a joint project between MIT, Bell Labs and General Electric (GE) and was conceived of as a computer utility providing support for hundreds of timesharing users [Organick72]. It was developed in the Sixties on the segmented-paged architectures of the GE635 and GE645.

This hardware supported a virtual address space of  $2^{36}$  36-bit words using a page size of 1024 words. The address space was divided into segments, which had a maximum size of 64 Kilowords (KW). Each process had a Descriptor Segment Table (DST), which was indexed by a segment number. The segment descriptor of an active segment also contained the address of the associated pagetable [Bensoussan72]. With such a large address space, the approach adopted was that each segment would represent a logical entity such as a file, procedure or an array. These segments were dynamically mapped into the address space of the process as the process was being executed.

Each segment contained a number of attributes including an access control list, which indicated the users authorised to access the segment. Supervisor calls were used to create a segment, delete a segment, change its access rights or its entry name as well as list its attributes. The name of each segment and its attributes were placed in a catalogue or filing system which was implemented in a hierarchical tree structure, beginning with a root directory. The path name of a segment was specified relative to this directory, while its entry name, the name by which a segment was usually referenced, was the last name in the path name. The current directory was first searched when a process accessed a segment and the path mechanism governed search rules when trying to locate a segment in the catalogue.

When a program first referenced a segment, a dynamic linker routine was invoked to find its path name. The segment was then assigned a unique number in the segment descriptor table. In addition, each known segment was kept in a per-process structure called the Known Segment Table (KST). When the path name and the segment number were obtained, a (path name, segment number) entry was made in the KST. Further references to the segment were resolved using its segment number. The pagetable associated with a segment was actually mapped in by the segment fault handler after a missing segment fault was generated when the segment was first accessed.

The Multics system used ring protection mechanisms to support access control [Saltzer74]. This system comprised a set of concentric rings representing different levels of privilege. Ring 0 was the most privileged and contained essential kernel code, like the interrupt handlers, scheduling routines, etc. Processes executing segments in this ring were non-interruptible until they were finished. Access privilege decreased as one moved further away from the centre. Sixty four rings were supported on the GE645 hardware with user processes usually executing from ring 33 onwards. Each segment descriptor also contained the ring or more commonly a group of rings in which the corresponding segment must be executed. If it was necessary to execute a segment in a more privileged ring, an interring access fault was generated and the operating system invoked access control routines

before the faulting process resumed execution.

Multics introduced many seminal ideas in operating system design which are still adhered to today. It was used at MIT and at approximately 100 other sites. However, because it depended heavily on the GE645 architecture, which was expensive and proprietary technology, it was outside the financial reach of most other computing research environments and universities. In addition, the concept of a general computing utility was increasingly being challenged by the arrival of minicomputers. These were less powerful but also much less expensive than the mainframe systems. They also had good interfacing facilities to numerous devices. Perhaps the most famous minicomputer series is the PDP series developed by Digital Equipment Corporation (DEC).

## 3.3 The Cap Computer System

The Cap Computer System was developed at the University of Cambridge in the Seventies to explore memory protection using hardware mechanisms [Wilkes79]. The design used a segmented architecture with a process having a list of active segments. Unlike conventional systems, where the loading of the base segment registers must be done when the machine is in a privileged mode, with the Cap system, loading of the segment registers was done in any mode, but the hardware carefully restricted the entries that could be loaded. Valid entries were associated with capabilities and access to a segment required a capability for that segment.

The creation and the checking of capabilities was done by a Capability Unit which was controlled by a section of the microprogram [Needham77b]. Capabilities were divided into two types. The D-type or data-type capability was used to access data with read, write and execute. A C-type or capability-type capability was used to access a segment containing a list of capabilities and the access privileges were read capability and/or write capability.

Like Multics, segments and files shared a close relationship and the virtual memory system interfaced directly with the Cap filing system to manage segments being brought into or leaving main memory [Needham77a]. The virtual memory management system comprised a number of system processes namely, the real store manager, the virtual store manager and the System Internal Names Manager, known as SINMAN.

The real store manager was responsible for bringing segments into memory when needed and deciding which ones should be swapped out when memory was required by other segments. When a segment was not in memory the associated capability had a special form known as an outform capability. If a process attempted to access the segment, a trap would occur. The system would then check the capability for the segment and would discover that the segment was not in memory. It would then contact the real store manager to bring it into memory. On accomplishing this task, the real store manager would convert the outform presentation of the capability into a normal one. The real store manager handled single segments no larger than 32 KW. Accessing larger segments or files was done using windowing techniques. It also provided facilities like flushing updates on a segment to disk and allowing users to swap out segments that were no longer in use.

The virtual store manager was involved in detecting whether the segment in memory was no longer in use. The number of processes having a capability for a given segment was reference-counted. This count was incremented when a process was issued with a new capability for the segment and was decremented whenever the virtual store manager received a message from a process indicating that it was no longer interested in the segment.

SINMAN was responsible for permanent storage and was the primary interface between the virtual memory system and the Cap filing system. An integer was associated with every object in the system and was referred to as the **system internal name** for that object. Cap supported three types of virtual objects:

Segments: treated as a linear sequence of bytes.

Directory Segments: related text names to System Internal Names.

Procedure Description Blocks (PDB): templates to construct protected procedures.

SINMAN had the responsibility of keeping track of all the objects in the system that should be kept in existence and marking all objects that should be deleted from the disk. Objects in the former category were either kept in directory segments or procedure description blocks or were being used by current processes. SINMAN deleted a segment once its reference count fell to zero. Directory segments and procedure descriptor blocks were only deleted if the objects they contained were also not referenced. Another duty of SINMAN was to issue capabilities for particular objects to authorised programs.

## 3.4 UNIX

Unix, developed at Bell Labs by Ken Thompson and Dennis Ritchie, has been one of the most popular operating systems of the last two decades [Bach86]. It was first built for

the PDP series but has since been ported to many other architectures. The success of Unix can be traced to many factors including the fact that it was written in C, making it very portable. In addition, it ran on the PDP series which most computer departments could afford and Unix was, for a long time, freely distributed to various university sites along with its source code.

Another design factor that made Unix easily portable was that it had a relatively simple virtual memory management system. A Unix process is composed of three regions: the text region which is fixed, the data region which grows upwards and the stack region which grows downwards. There are system calls to extend the data region and the operating system will extend the stack as required.

Unlike Multics, the original Unix system does not support the idea of memory-mapped files or the dynamic linking of segments. The file system, though it employs the same hierarchical scheme as Multics, is implemented using a buffer cache and disk block structures and is independent of the memory management system. In fact, some physical memory must be allocated exclusively for the buffer cache when the system is booted.

Unix provides an integrated I/O interface in which operations on files as well as devices use the same system calls. Devices such as the monitor and keyboard, are regarded as special files by the file system. This is an elegant abstraction that makes I/O operations easy to perform from the point of view of the end-user since there is no need to be familiar with the actual physical device.

This I/O interface supports two calls that involve the movement of data, namely:

```

read (fd, buffer, n)

write (fd, buffer, n)

where:

fd is a file descriptor.

buffer is the address of a buffer in the caller's address space.

n is the number of bytes to be transferred.

```

The read call involves locating the data on disk, copying it to a buffer in the kernel, then copying from the kernel into the user's address space starting at buffer. This scheme has several disadvantages.

Firstly, two copies are required to move data from the disk into user space, which is expensive. Secondly, since each user has a private copy of the data, it is difficult to share

files concurrently because there is nothing to stop users from simultaneously updating private copies of the same part of the file. In addition, changes made by a user would have to be flushed back to the disk immediately to allow other users to see them and they can only do so by invoking the read operation again!

The file interface in Unix is character-oriented, where a file is basically viewed as a linear sequence of bytes. There are calls to read from and write to a file as well as to move to a given position in a file, thus providing limited random access. Since most users require sequential input, and output data sequentially as well, this abstraction will suffice for most applications. However, for users needing a different data abstraction, (e.g. viewing a file as a set of records), it is necessary to build this abstraction on top of the Unix abstraction or to use the I/O interface directly, which are both inconvenient.

Another feature of Unix is the **fork** and **exec** system calls. The fork call creates another process called the **child**, which is an exact replica of the process invoking the call, called the **parent**. Early implementations of fork involved copying the data and stack regions of the parent into those allocated for the child while the text segment, which is read-only, is shared. Such copying is time-consuming and later versions of Unix used the **copy-on-write** (cow) technique for managing the stack and data regions. These regions are now remapped read-only with the operating system setting a bit in each PTE to indicate copy-on-write sharing. When a child or parent attempts to write to a given page, an access violation fault occurs. The fault handler notices that the region is mapped copy-on-write and the faulted process receives a private copy of the page before continuing. This reduces the amount of copying since only pages that are modified in each region are copied.

The exec call replaces the segments of the calling process with the segments of the process whose name is passed as an argument to the call. This allows the programmer to implement a multi-tasking environment by first forking off the child process and then doing an exec call to start another program. If the parent has opened files before invoking the fork call, these descriptors will also be available to the child. Thus, before the exec call, it is possible to close files which will not be used by the new process as well as redirect its input and output.

## 3.5 BSD Unix

The most influential group outside Bell Labs that has contributed new ideas to the Unix evolution has been the Computer Science Department at the University of California, Berkeley. Contributions include the first Unix implementations of virtual memory, demand

paging and page replacement as well as the IPC socket mechanism and the TCP/IP networking protocol suite [Leffler89]. The BSD Unix memory management system was influenced by Tenex [Bobraw72] as well as Multics and an interface was specified to support memory-mapped files in the 4.2 BSD reference manual.

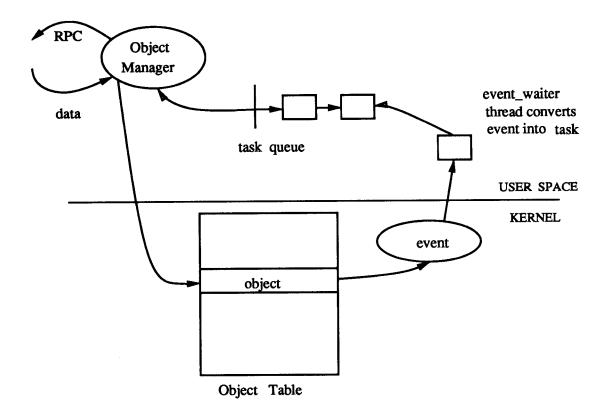

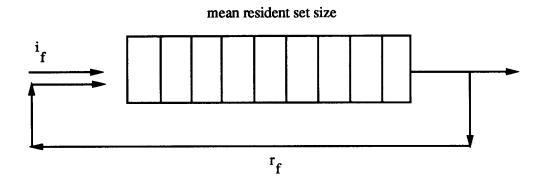

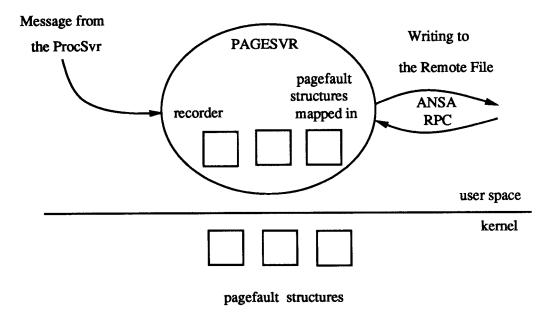

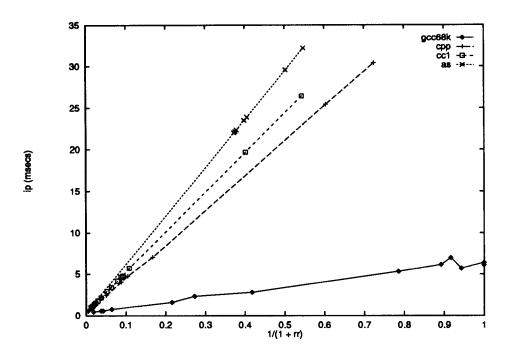

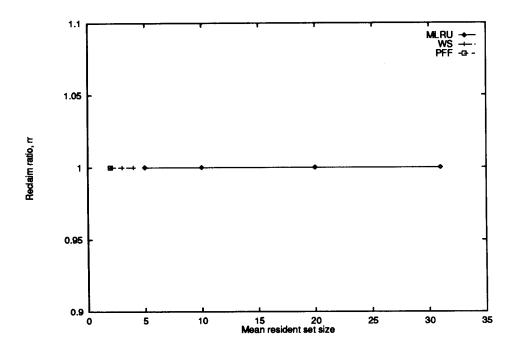

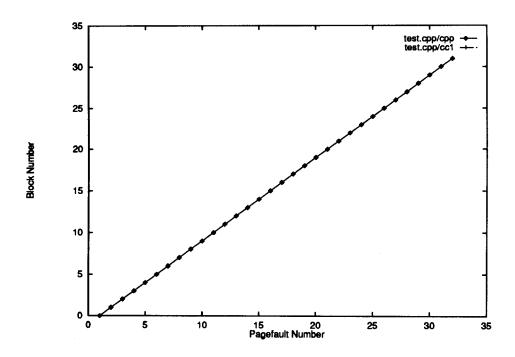

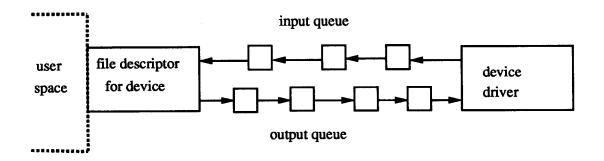

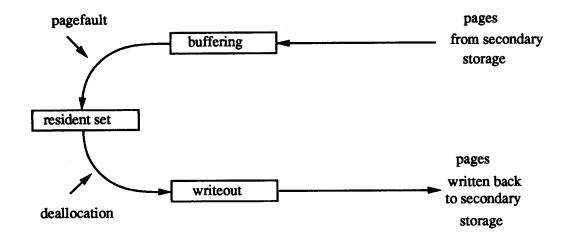

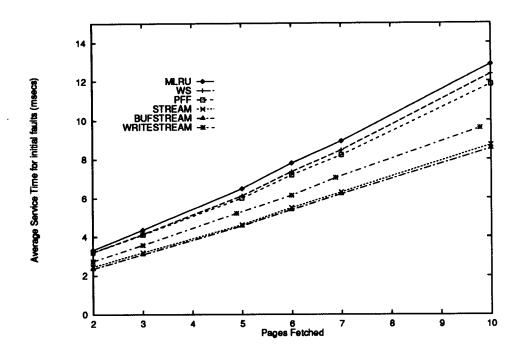

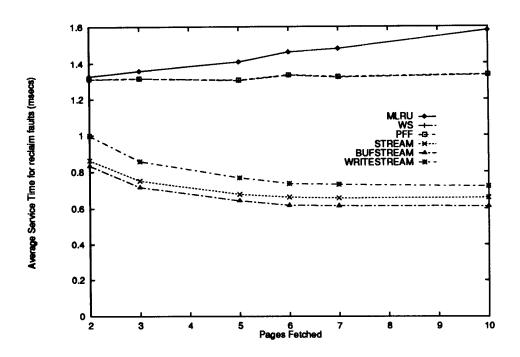

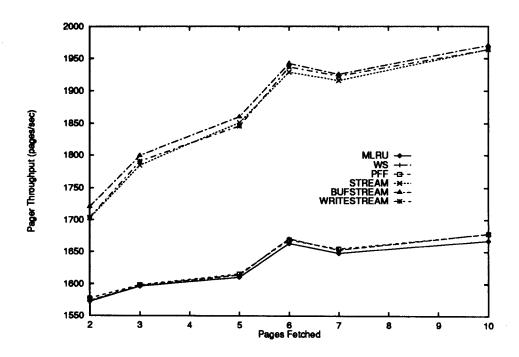

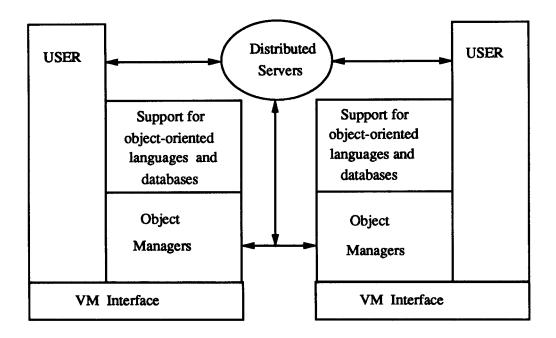

The original interface, known as the mmap interface, allows a user to map a file or portions thereof into the address space of a process. This interface supports options of read, write and execute permissions, while sharing may be specified as private or shared. If sharing is private, indicated by the MAP\_PRIVATE option, changes made to the file by the user are seen only by that user. However, if the MAP\_SHARED option is used, all changes will be seen by other processes sharing the file. There is also a **getpagesize** call which returns the system pagesize. A process can move pages within its own memory using the **mremap** call. In addition, protection of a region can be controlled using the **mprotect** call.