Number 215

# A structured approach to the verification of low level microcode

Paul Curzon

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 http://www.cl.cam.ac.uk/

This technical report is based on a dissertation submitted May 1990 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Christ's College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/TechReports/

ISSN 1476-2986

# **Preface**

This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration. No part of this dissertation has already been, or is concurrently being, submitted for any degree, diploma, or other qualification at any other university.

# Acknowledgements

I am grateful to many people who have given their support, advice and time during the period of this research. In particular, I am deeply indebted to my supervisor Martin Richards for his encouragement and stimulating discussion. I am grateful to the members of the Hardware Verification Group in Cambridge, and in particular to Inder Dhingra, Mike Gordon, John Herbert and Jeff Joyce, for their interesting discussion and advice about various things. Many people suggested improvements to this dissertation and gave general advice including Joe Dixon, Andy Gordon, Phil Hunt, Neil Laws, Tim Leonard and Colin Smith. I would also like to thank the members of Room 205, past and present for providing a lively and interesting working environment, and to Martyn Johnson and Graham Titmus for keeping the machines running. My work was supported by the Science and Engineering Research Council and Christ's College, and a High Level Hardware Orion Microcomputer was provided on Alvey grant number ALV/PRJ/SE/034 for which I am grateful. Finally I would like to thank all my friends for maintaining my sanity over the past three years.

# Summary

Errors in microprograms are especially serious since all higher level programs on the machine depend on the microcode. Formal verification presents one avenue which may be used to discover such errors. Previous systems which have been used for formally verifying microcode may be categorised by the form in which the microprogram is supplied. Some demand that it be written in a high level microprogramming language. Conventional software verification techniques are then employed. Other methods allow the microcode to be supplied in the form of a memory image. It is treated as data to an interpreter modelling the behaviour of the microarchitecture. The proof is then performed by symbolic execution. A third solution is for the code to be supplied in an assembly language and verified at that level. The assembler instructions are converted to commands in a modelling language. The resulting program is verified using traditional software verification techniques.

In this dissertation, I present a new universal microprogram verification system. It achieves many of the advantages of the other kinds of systems by adopting a hybrid approach. The microcode is supplied as a memory image, but is transformed by the system to a high level program which may then be verified using standard software verification techniques. The structure of the high level program is obtained from user supplied documentation. I show that this allows microcode to be split into small, independently validatable portions even when it was not written in that way. I also demonstrate that the techniques allow the complexity of detail due to the underlying microarchitecture to be controlled at an early stage in the validation process. I suggest that the system described would combine well with other validation tools and provide help throughout the firmware development cycle. Two case studies are given. The first describes the verification of Gordon's computer. This example, being fairly simple, provides a good illustration of the techniques used by the system. The second case study is concerned with the High Level Hardware Orion computer which is a commercially produced machine with a fairly complex microarchitecture. This example shows that the techniques scale well to production microarchitectures.

# Contents

| 1 | $\mathbf{Pro}$ | Prologue 1 |                                        |     |  |  |  |

|---|----------------|------------|----------------------------------------|-----|--|--|--|

|   | 1.1            | Discov     | vering Errors in Microprograms         | 1   |  |  |  |

|   |                | 1.1.1      | Testing                                | 1   |  |  |  |

|   |                | 1.1.2      | Program Flow Analysis                  | 2   |  |  |  |

|   |                | 1.1.3      | Formal Verification                    |     |  |  |  |

|   | 1.2            | The P      | Problem                                |     |  |  |  |

|   |                | 1.2.1      | Complex Microarchitectures             | 4   |  |  |  |

|   |                | 1.2.2      | Control Structures                     | 4   |  |  |  |

|   |                | 1.2.3      | Universality                           | 4   |  |  |  |

|   |                | 1.2.4      | Self Modifying Code                    | 4   |  |  |  |

|   | 1.3            | The C      | Contribution of this Dissertation      | 5   |  |  |  |

|   | 1.4            | Termi      | nology                                 | 5   |  |  |  |

| 2 | Mic            | roprog     | gram Verification Systems              | 7   |  |  |  |

|   | 2.1            |            | ous Systems                            |     |  |  |  |

|   |                | 2.1.1      | High Level Microprogram Verification   |     |  |  |  |

|   |                | 2.1.2      | Memory Image Microprogram Verification |     |  |  |  |

|   |                | 2.1.3      | Assembly Language Verification Systems |     |  |  |  |

|   | 2.2            | The S      | POOK System                            |     |  |  |  |

|   |                | 2.2.1      | The Host Program                       |     |  |  |  |

|   |                | 2.2.2      | The Skeleton                           |     |  |  |  |

|   |                | 2.2.3      | The Target Specification               |     |  |  |  |

|   |                | 2.2.4      | The Microprogram                       |     |  |  |  |

|   |                | 2.2.5      | Software Verification Techniques       | 22  |  |  |  |

|   |                | 2.2.6      | Case Studies                           |     |  |  |  |

|   |                | 2.2.7      | Advantages of the SPOOK System         |     |  |  |  |

| 3 | The            | SPO        | OK Language                            | 25  |  |  |  |

|   | 3.1            |            | luction                                |     |  |  |  |

|   |                | 3.1.1      | The Needs of the Host                  |     |  |  |  |

|   |                | 3.1.2      | The Needs of the Skeleton              |     |  |  |  |

|   | 3.2            | SPOO       | OK Programs                            |     |  |  |  |

|   |                | 3.2.1      | The Host Program                       |     |  |  |  |

|   |                | 3.2.2      | The Skeleton                           |     |  |  |  |

|   |                | 3.2.3      | Module Definitions                     |     |  |  |  |

|   |                |            |                                        | ~ 4 |  |  |  |

vi *CONTENTS*

|     | 3.2.4 Predicate Definitions         |       | 27              |

|-----|-------------------------------------|-------|-----------------|

| 3.3 | Declarations                        |       | 27              |

|     | 3.3.1 Names                         |       | 28              |

|     | 3.3.2 Signals                       |       | 28              |

|     | 3.3.3 Types                         |       | 30              |

|     | 3.3.4 Declarations                  |       | 31              |

| 3.4 | Word Expressions                    |       | 32              |

|     | 3.4.1 Word Constants                |       | 32              |

|     | 3.4.2 Local Variables               |       | 33              |

|     | 3.4.3 Ghost Variables               |       | 33              |

|     | 3.4.4 Concatenation                 |       | 33              |

|     | 3.4.5 Selection                     |       | 34              |

|     | 3.4.6 Subscription                  |       | 34              |

|     | 3.4.7 Logical Operators             |       | 35              |

|     | 3.4.8 The Join Operator             |       | 36              |

|     | 3.4.9 The Arithmetic Operators      |       | 36              |

|     | 3.4.10 The Shift Operators          |       | 37              |

|     | 3.4.11 The Relational Operators     |       | 38              |

|     | 3.4.12 Well-definedness             |       | 41              |

|     | 3.4.13 Z_WORD                       |       | 41              |

|     | 3.4.14 Conditional Expressions      |       | 41              |

|     | 3.4.15 Subscription Update          |       | 44              |

| 3.5 | State Word Expressions              |       | 44              |

| 5.5 | 3.5.1 State Word Constants          |       | $\frac{44}{45}$ |

|     | 3.5.2 State Variables               |       | $\frac{45}{45}$ |

|     | 3.5.3 Word to State Word Conversion |       |                 |

|     |                                     |       | 45              |

|     | 3.5.4 MERGE                         |       | 46              |

| 9.0 | 3.5.5 State Word to Word Conversion |       | 47              |

| 3.6 | Time Expressions                    |       | 47              |

|     | 3.6.1 Time Variables                |       | 47              |

|     | 3.6.2 INC                           | <br>• | 47              |

|     | 3.6.3 DEC                           | <br>• | 48              |

| 3.7 | History Expressions                 |       | 48              |

|     | 3.7.1 Input and Output Variables    |       | 48              |

|     | 3.7.2 PUT                           |       | 48              |

|     | 3.7.3 GET                           |       | 49              |

| 3.8 | Assertions                          |       | 49              |

| 3.9 | Commands                            |       | 50              |

|     | 3.9.1 SKIP                          |       | 50              |

|     | 3.9.2 ABORT                         |       | 50              |

|     | 3.9.3 Sequencing                    |       | 51              |

|     | 3.9.4 CHECK                         |       | 51              |

|     | 3.9.5 MI                            |       | 51              |

|     | 3.9.6 Assignment                    |       | 52              |

|     | 3.9.7 Parallel Assignment           | •     | 52              |

| vii |

|-----|

|     |

|   |     | 3.9.8  | Blocks                                |

|---|-----|--------|---------------------------------------|

|   |     | 3.9.9  | Calling Modules                       |

|   |     | 3.9.10 | IF Statements                         |

|   |     | 3.9.11 | Case Statements                       |

|   |     | 3.9.12 | While Loops                           |

| 4 | The | Host   | Program 57                            |

|   | 4.1 | Introd | uction                                |

|   | 4.2 | The E  | xpanded Host Program                  |

|   |     | 4.2.1  | The Block                             |

|   |     | 4.2.2  | Local Assignments                     |

|   |     | 4.2.3  | Well-Defined Checks                   |

|   |     | 4.2.4  | Output Assignments                    |

|   |     | 4.2.5  | The Clock Tick                        |

|   |     | 4.2.6  | Simplicity                            |

|   | 4.3 | The So | ource Host Program                    |

|   |     | 4.3.1  | Block                                 |

|   |     | 4.3.2  | Semicolons                            |

|   |     | 4.3.3  | Time                                  |

|   |     | 4.3.4  | Checks                                |

|   |     | 4.3.5  | State Variable Assignments            |

|   |     | 4.3.6  | Casts                                 |

|   |     | 4.3.7  | Output Assignments                    |

|   |     | 4.3.8  | Inputs                                |

|   |     | 4.3.9  | Defaults                              |

|   |     | 4.3.10 | Constants                             |

|   |     | 4.3.11 | Feedback                              |

|   |     | 4.3.12 | Creating State Storing Devices        |

|   |     | 4.3.13 | Local Declarations                    |

|   |     |        | Automatic Truncation and Zero Padding |

|   | 4.4 |        | ample—A Simple Device                 |

|   |     | 4.4.1  | The Source Host Program               |

|   |     | 4.4.2  | The Expanded Host Program             |

|   | 4.5 |        | ocessing the Host Program             |

|   |     | 4.5.1  | Removing Checks                       |

|   |     | 4.5.2  | Expression Simplification             |

|   |     | 4.5.3  | Other Techniques                      |

|   |     | 4.5.4  | An Example                            |

|   | 4.6 |        | sing the Host Program                 |

|   |     | 4.6.1  | The Algorithm                         |

|   |     | 4.6.2  | An Example                            |

|   |     | 4.6.3  | A Comparison with Other Systems       |

viii CONTENTS

| 5 | The | Skeleton                         |                                                 |  |

|---|-----|----------------------------------|-------------------------------------------------|--|

|   | 5.1 | Introd                           | luction                                         |  |

|   | 5.2 | State                            | Transition Documentation                        |  |

|   |     | 5.2.1                            | Assembly Code                                   |  |

|   |     | 5.2.2                            | State Transition Diagrams                       |  |

|   |     | 5.2.3                            | Skeletons                                       |  |

|   | 5.3 | Facilit                          | ies of SPOOK                                    |  |

|   |     | 5.3.1                            | Structure                                       |  |

|   |     | 5.3.2                            | Nodes                                           |  |

|   |     | 5.3.3                            | Decimal Conversion and Other Bases              |  |

|   |     | 5.3.4                            | Ghost Assignments                               |  |

|   |     | 5.3.5                            | Assertions                                      |  |

|   | 5.4 | Expai                            | nding the Skeleton                              |  |

|   |     | 5.4.1                            | Replacing MI Commands                           |  |

|   |     | 5.4.2                            | Extracting Information from the MI condition 98 |  |

|   |     | 5.4.3                            | Collapsing from a Word Expression               |  |

|   |     | 5.4.4                            | Reusing Collapsed Host Programs                 |  |

|   | 5.5 | Remo                             | ving Unused Variable Assignments                |  |

|   |     | 5.5.1                            | Introduction                                    |  |

|   |     | 5.5.2                            | The Algorithm                                   |  |

|   |     | 5.5.3                            | Local Removal                                   |  |

|   |     | 5.5.4                            | A Comparison with Other Systems                 |  |

|   | 5.6 | Comb                             | ining Successive Microinstructions              |  |

|   |     | 5.6.1                            | The Algorithm                                   |  |

| _ |     |                                  | on and Theorem Proving 109                      |  |

| 6 |     | Verification and Theorem Proving |                                                 |  |

|   | 6.1 |                                  | luction                                         |  |

|   |     | 6.1.1                            | Software Verification Techniques                |  |

|   |     | 6.1.2                            | Goals, Tactics and Tacticals                    |  |

|   |     | 6.1.3                            | Sequents                                        |  |

|   |     | 6.1.4                            | Using the System                                |  |

|   | 6.2 |                                  | cation Condition Generation                     |  |

|   |     | 6.2.1                            | The WP Operator                                 |  |

|   |     | 6.2.2                            | General Commands                                |  |

|   |     | 6.2.3                            | Sequencing                                      |  |

|   |     | 6.2.4                            | CALL_MODULE                                     |  |

|   |     | 6.2.5                            | IF                                              |  |

|   |     | 6.2.6                            | CASE                                            |  |

|   |     | 6.2.7                            | WHILE                                           |  |

|   | 6.3 |                                  | ng Verification Conditions                      |  |

|   |     | 6.3.1                            | Splitting Verification Conditions               |  |

|   |     | 6.3.2                            | Simple Rules                                    |  |

|   |     | 6.3.3                            | Substitutions                                   |  |

|   |     | 6.3.4                            | Expression Simplification                       |  |

|   |     | 6.3.5                            | Condition Simplification                        |  |

*CONTENTS* ix

|   |                       | 6.3.6          | Rematching with the Simple Rules                            | . 120 |  |  |

|---|-----------------------|----------------|-------------------------------------------------------------|-------|--|--|

|   |                       | 6.3.7          | Expanding Predicate Definitions                             |       |  |  |

| 7 | Gordon's Computer 123 |                |                                                             |       |  |  |

|   | 7.1                   |                | arget Level                                                 | . 124 |  |  |

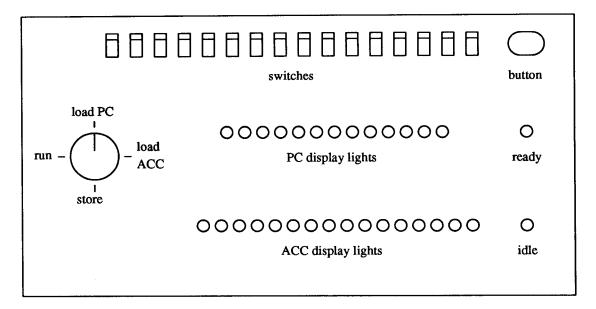

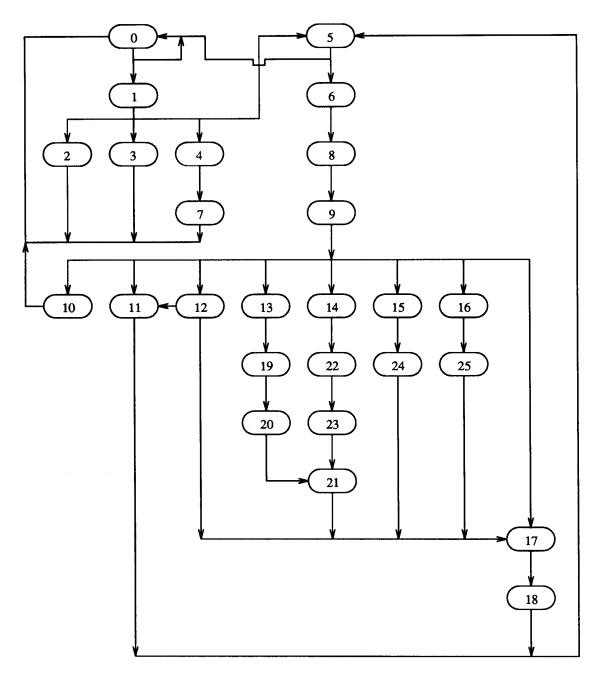

|   |                       | 7.1.1          | Idle Mode                                                   |       |  |  |

|   |                       | 7.1.2          | Run Mode                                                    |       |  |  |

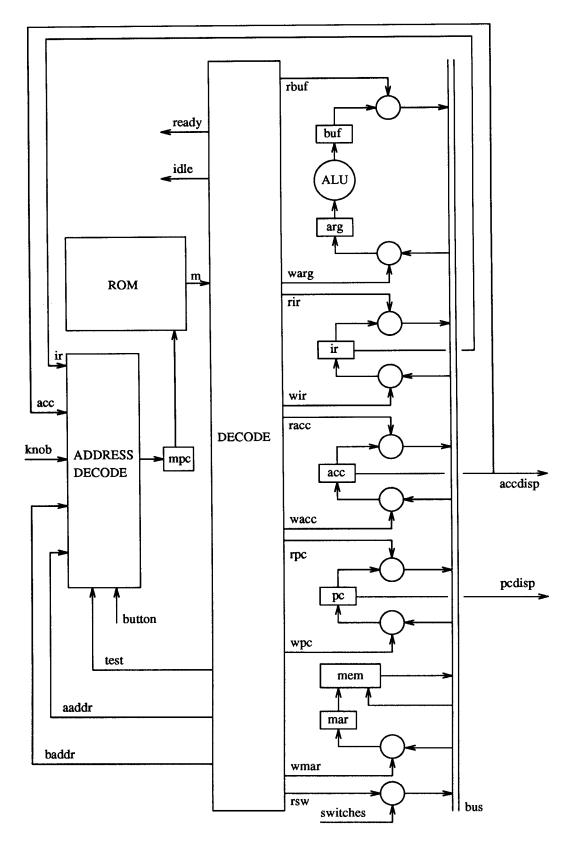

|   | 7.2                   | The He         | ost Level                                                   |       |  |  |

|   | 7.3                   |                | xpanded Host Program                                        |       |  |  |

|   | 7.4                   |                | cessing the Expanded Host Program                           |       |  |  |

|   |                       | 7.4.1          | Expression Simplification                                   |       |  |  |

|   |                       | 7.4.2          | Check Removal                                               |       |  |  |

|   | 7.5                   | The Sl         | keleton for Gordon's computer                               |       |  |  |

|   |                       | 7.5.1          | Idle Cycles                                                 |       |  |  |

|   |                       | 7.5.2          | Run Cycles                                                  |       |  |  |

|   | 7.6                   | Expan          | ding the Skeleton                                           |       |  |  |

|   |                       | 7.6.1          | The SIZE measure                                            |       |  |  |

|   |                       | 7.6.2          | The SIZE measure for Gordon's computer                      |       |  |  |

|   | 7.7                   | The Ta         | arget Specification                                         |       |  |  |

|   |                       | 7.7.1          | The Main Precondition                                       |       |  |  |

|   |                       | 7.7.2          | The Main Postcondition                                      |       |  |  |

|   |                       | 7.7.3          | The Module Specifications                                   |       |  |  |

|   |                       | 7.7.4          | Annotations                                                 |       |  |  |

|   | 7.8                   | Produ          | cing Verification Conditions                                |       |  |  |

|   | 7.9                   |                | g Verification Conditions                                   |       |  |  |

|   |                       | 7.9.1          | Statistics for Measuring the Success of the Theorem Prover. |       |  |  |

|   | 7.10                  | Errors         | found                                                       | . 161 |  |  |

|   |                       | 7.10.1         | The Microprogram                                            | . 162 |  |  |

|   |                       | 7.10.2         | The Host Program                                            |       |  |  |

|   |                       | 7.10.3         |                                                             |       |  |  |

|   |                       | 7.10.4         | The Skeleton                                                |       |  |  |

|   |                       |                | The Annotations                                             |       |  |  |

| _ | 701                   | 0              | Comment                                                     |       |  |  |

| 8 |                       |                | Computer                                                    | 167   |  |  |

|   | 8.1                   |                |                                                             |       |  |  |

|   | 8.2                   |                | rion Host Program                                           |       |  |  |

|   |                       | 8.2.1<br>8.2.2 | Limitations of the Orion Host Program                       |       |  |  |

|   |                       | 8.2.3          | Converting the BSPL Step Function                           | . 170 |  |  |

|   | 8.3                   |                | Expanding and Preprocessing the Host Program                | . 173 |  |  |

|   | 0.0                   | 8.3.1          | ol Flow and the Skeleton                                    | . 174 |  |  |

|   |                       | 8.3.2          | Pipelined Instruction Fetching                              | . 174 |  |  |

|   |                       | 8.3.3          | The System Bus Control Function                             |       |  |  |

|   |                       | 8.3.4          | ALU Function and Source Modifications                       |       |  |  |

|   | 8.4                   |                | The Alternative SIN Functions                               |       |  |  |

|   | 0.4                   | THE OF         | andard Instruction Set                                      | . 177 |  |  |

| x | CONTENTS |

|---|----------|

|   |          |

|              |                  | 8.4.1         | The Stack                          | 177        |  |

|--------------|------------------|---------------|------------------------------------|------------|--|

|              |                  | 8.4.2         | Instruction Fetching               | 178        |  |

| •            |                  |               | nd Instruction                     | 179        |  |

|              |                  | 8.5.1         | The Skeleton                       | 181        |  |

|              |                  | 8.5.2         | Expanding the Skeleton             | 184        |  |

|              |                  | 8.5.3         | Unused Variable Assignment Removal |            |  |

|              |                  | 8.5.4         | The Target Specification           |            |  |

|              | 8.6              |               | eation Conditions                  |            |  |

|              | 0.0              | 8.6.1         | Errors Found                       |            |  |

|              |                  | 8.0.1         | Enfors Found                       | 190        |  |

| 9            | Epilogue         |               |                                    | 199        |  |

|              | $9.1^{-}$        | _             | ary                                | 199        |  |

|              |                  | 9.1.1         | A Comparison of the Case Studies   |            |  |

|              |                  | 9.1.2         | Collapsed Host Programs            |            |  |

|              |                  | 9.1.3         | The Skeleton                       |            |  |

|              |                  | 9.1.4         | The Model of the Microarchitecture |            |  |

|              |                  | 9.1.5         | Theorem Proving                    |            |  |

|              |                  | 9.1.6         | The Advantages of the SPOOK System |            |  |

|              |                  | 9.1.7         | Discussion                         |            |  |

|              | 9.2              | •             | er Work                            |            |  |

|              | 9.4              | 9.2.1         | An Integrated Validation System    |            |  |

|              |                  | 9.2.1 $9.2.2$ | ·                                  |            |  |

|              |                  |               | Examples Considered                |            |  |

|              |                  | 9.2.3         | Theorem Proving                    |            |  |

|              |                  | 9.2.4         | Security                           |            |  |

|              |                  | 9.2.5         | Extending the Language             | . 207      |  |

| Bi           | bliog            | graphy        |                                    | 209        |  |

| Δ            | The              | Hoar          | e Rules                            | 219        |  |

|              |                  | 22041         | 0 104100                           | 210        |  |

| В            | 3 Freeness Rules |               |                                    |            |  |

|              | B.1              | Freene        | ess from U                         | . 221      |  |

|              | B.2              |               | ess from Z                         |            |  |

|              | B.3              |               | ess from X                         |            |  |

|              |                  |               |                                    |            |  |

| $\mathbf{C}$ | Rev              | vrite R       | Rules                              | 225        |  |

|              | C.1              | Expre         | ssion Rewrite Rules                | . 226      |  |

|              | C.2              | Condi         | tion Rewrite Rules                 | . 232      |  |

|              | C.3              |               | nand Rewrite Rules                 |            |  |

| D            | Gor              | don's         | Computer's Source Host Program     | 235        |  |

| $\mathbf{E}$ | Gor              | don's         | Computer's Skeleton                | 241        |  |

|              |                  |               |                                    |            |  |

| $\mathbf{F}$ | The              | urior         | n Source Host Program              | <b>245</b> |  |

# Chapter 1

# Prologue

Errors in microprograms are especially serious, since all higher level programs on the machine depend on the microcode. When used in life-critical circumstances, an incorrect microprogram can have devastating effects. Furthermore, microprogramming errors discovered late in the design cycle can be very expensive in both time and effort to correct, particularly when the microcode is hardwired within a microprocessor.

Generally, an important design issue when writing microcode is that the program be both fast and compact. The result is that microprograms tend to have far more complicated control structures than normal programs. As suggested in the Orion Microarchitecture Manual [HLH 84]:

"It is considered acceptable to employ programming 'tricks' at the microcode level since the system performance will be proportional to the number of microinstructions executed."

The algorithms being coded are becoming more complex with little in the way of development tools to aid the microprogrammer. Consequently, errors are easier to make and much harder to detect.

# 1.1 Discovering Errors in Microprograms

There are several validation techniques which could be employed to discover errors in microcode:

- Testing,

- Program Flow Analysis, and

- Formal Verification.

# 1.1.1 Testing

Exhaustive testing, though desirable, is unfeasible, even for trivial microprograms, due to the large number of cases which must be tested. Inexhaustive testing is the

traditional validation method. Test patterns are used to exercise the program. If it passes all the tests, it is assumed to be correct and released to the public who then proceed to discover further bugs. With inexhaustive testing, confidence that all the errors have been found cannot be attained. Errors can always lie in untested areas. Fixing bugs found after a product has been released can be very expensive and time-consuming. It can also be very annoying for the users of the system. Formal approaches to microprogram testing, which attempt to ensure that the test data selection criteria are sufficient to detect errors, have been suggested to alleviate the problems of inexhaustive testing [Berg 81].

# 1.1.2 Program Flow Analysis

An alternative way to validate microcode is program flow analysis [Bergeretti 85] [Carré 86] [Foster 86]. This analysis finds certain types of errors, such as two instructions following one another illegally. The basic idea is that various relations are computed for each node in the flow graph representing the code. From these, the relations for the paths through the code can be determined. They can then be used to indicate the presence of different kinds of errors on the paths, depending upon how they are interpreted. The algorithms allow one to be certain that no such errors are present if this is so, though only those of the kind looked for will be detected. Also, they could suggest that correct code contains errors. For example, errors on unexecutable paths might be indicated. The redundant register transfer, where the value transferred is overwritten before being referenced, is one type of error commonly detected by this technique. In microprograms this occurs frequently in non-erroneous situations. For example, a carry flag might be set whenever an addition is performed, even though its value will not always be used.

#### 1.1.3 Formal Verification

Formal verification attempts mathematically to prove the correctness of a program from a formal specification. The proof demonstrates the correctness for all inputs, rather than a chosen few as with inexhaustive testing. The requirement of a formal specification for formal verification also forces the client to resolve ambiguities earlier in the design than would an informal specification.

Some degree of automated help is essential for formal verification. Program verification generally involves the proof of large numbers of simple theorems. This can be slow and tedious, and mistakes are easy to make. The situation is exasperated further when proving microprograms correct, due to the additional complexity of the underlying microarchitectures. Single microinstructions may encode many, often redundant, register transfers. Thus, small microprograms may involve large amounts of detail. With software, it is feasible to verify simple algorithms by hand. This is no longer so with microprograms. Automated systems, on the other hand, are very good at coping with large amounts of detail and doing large numbers of simple tasks. The need for mechanical aid to overcome these problems is illustrated in previous hand proofs. Birman originally carried out a hand proof of the S-Machine

[Birman 74]. However, further errors, missed by the hand proof, were found when the proof was repeated with mechanical aid [Carter 75]. Cohn's machine proof of the first level of the VIPER microprocessor using the HOL system [Cohn 87] found errors in an earlier hand proof. For small examples, hand proofs can be used to find errors in microprograms. With machine assistance, more complex programs can be tackled, and a greater degree of confidence that errors will be discovered is gained. Complete automation is not desirable, however. Much of the advantage of formal verification arises from constructing or guiding the proof, rather than in receiving a yes/no answer as to the correctness of the program. The former forces the verifier to examine the code and the reasons for its correctness. When errors are detected, they will consequently be easier to locate and correct.

In general, program verification systems have been used to verify algorithms rather than production programs. Producing a convincing demonstration of the practicality of microcode verification ought to be more feasible than for software verification because of the nature of microprograms. Indeed, verification systems have been used in the verification of production microprograms for commercial computers [Carter 78a] [Patterson 78] [Damm 85b] [May 87] [Crocker 88]. Microprogram verification is more feasible for several reasons.

- Microprograms deal with simple datatypes (bitstrings).

- The microcoded algorithms tend to be numeric.

- The code is short compared to software.

- The microarchitecture is well-defined and fairly simple, leaving less doubt as to the semantics of microinstructions.

- The specification of the code is unlikely to be frequently changed. Firmware does not evolve in the manner of software.

- Microcode does not normally use recursive procedures.

A formally verified program cannot be assumed to be correct. It may still contain errors due to mistakes in the specification, proof, etc. Consequently, formal verification should be used alongside testing and program flow analysis as a tool for finding and correcting errors.

### 1.2 The Problem

In the previous section, I described the techniques available for detecting errors in microprograms. It is with formal verification that this dissertation is primarily concerned. I have suggested that formal verification of production microprograms for commercial microarchitectures is feasible. A number of problems remain.

# 1.2.1 Complex Microarchitectures

If a microprogram verification system is to be a useful tool for commercial architectures, the complexity arising from large amounts of detail due to the microarchitecture must be dealt with. Machine assistance helps greatly in this way. However, if the verifier is to guide the proof, the techniques used must deal with this complexity at an early stage and in such a way that the output is understandable. If this is not done, the verification task will become intellectually unmanageable.

#### 1.2.2 Control Structures

Complexity may also arise due to the volume of code being verified. Microprograms implementing commercial microarchitectures will inevitably be large. They will also tend to have complex and tangled control structures. The use of goto statements in high level languages has long been considered bad programming practice. It generally produces unreadable code which is consequently liable to contain errors and is difficult to verify. However, jumps proliferate in microprograms due to the absence of high level control structures and the need for the microcode to be fast and compact. Ideally, for validation purposes, code should be structured and modular, allowing small portions of code to be independently validated. For microprograms this is unlikely to be the case.

# 1.2.3 Universality

An important feature of any firmware engineering tool is that it be universal in the sense that it may be used with microprograms for any microarchitecture, without the system needing to be rewritten. To achieve this, the system must use a formal description of the microarchitecture semantics. Obviously, it is a great advantage if one set of tools can be used for any microarchitecture. The advantage is greater than it might first appear, since a particular microarchitecture may only have a single microprogram written for it. For this reason, it may not be worthwhile developing a new set of tools. Furthermore, microarchitectures often tend to evolve with the microprogram during the firmware development cycle. If tools are to be useful during this cycle, they must also be capable of adapting. If parts of the tools need to be rewritten whenever such a change is made, either the tools will always be behind, and of little use, or the development cycle will be greatly slowed to allow the tools to keep up to date. This could be disastrous for a product. With technology rapidly advancing, delays in the development cycle could render a new architecture out of date before its release. An additional advantage of using universal tools is that it forces the designers to write a formal specification of the microarchitecture.

# 1.2.4 Self Modifying Code

Self modification, in which the code ceases to be a static object, is a problem unique to the verification of low level code. In the past this has not been a problem since microcode has tended to reside in read-only control stores. However, with the advent

of cheaper memory, writable control stores are commonly used allowing data and program regions to be intermixed. Although the intentional use of self modifying code may be rare, the microcode in a writable control store could inadvertently overwrite itself. A verification system must be capable of coping with self modifying code. At the very least, it should be possible to verify that the code does not modify itself.

### 1.3 The Contribution of this Dissertation

In this dissertation I present a new microprogram verification system which overcomes the problems described in the previous section.

- I describe ways of reducing the complexity arising from commercial architectures at an early stage in the verification process which are amenable to automation.

- I show how the microprogram can be split into intellectually manageable portions that can be verified independently without the microcode being written that way, overcoming the problems of verifying large bodies of code.

- I show how extra formal documentation can overcome the problems of complex control structures and also give additional help in the firmware development cycle.

- I show that the advantages of the various previous kinds of systems can be achieved by adopting a hybrid method.

- I describe universal verification tools which both ease the problems of *post* facto verification and can also be used as an aid in the development process.

- I show that microprograms and microarchitectures do not necessarily have to be designed with verification in mind to make it feasible.

- I suggest that the techniques can cope with microcode which could, intentionally or otherwise, modify itself.

# 1.4 Terminology

There is some confusion in the literature over the terms "host" and "target". Some authors use the term "target" in the sense of retargetable tools, i.e., tools that can be used for different microarchitectures. Thus, "target" is used to refer to microarchitectures. The term "host" is then used to refer to the macroarchitecture. Other authors take the target to be that which is aimed for, i.e., that which is to be implemented—the macroarchitecture. The host is then the microarchitecture since it plays host to the microprogram. Throughout this dissertation, I use the latter meanings, since they are predominant in the firmware verification literature, and seem more natural.

- $\bullet$  Target  $\equiv$  Macroarchitecture

- $\bullet$  **Host**  $\equiv$  Microarchitecture

# Chapter 2

# Microprogram Verification Systems

In this chapter I describe microprogram verification systems from the literature and compare the various approaches adopted. I then outline SPOOK: the new system which is the subject of this dissertation, and suggest the advantages that it has over previous systems. I also outline the remainder of the thesis.

# 2.1 Previous Systems

A number of different formal microprogram verification systems have been described in the literature. These have fallen roughly into three types, according to the form the microprogram takes:

- High Level Microprogram Verification Systems,

- Memory Image Verification Systems,

- Assembler Level Verification Systems.

The advantages and disadvantages of each type of system are discussed below. The individual systems which fall into these categories are also described. Descriptions of some machine code verification systems are given since many of the techniques and problems are related to those of firmware verification. Dasgupta [Dasgupta 88] gives a more detailed overview of many of the systems described.

# 2.1.1 High Level Microprogram Verification

High level microcode verification requires that the code be written in a high level microprogramming language. Standard software verification techniques are then

used to verify this high level code, by, for example, a Hoare proof based on an axiomatic semantics. This approach has several advantages.

- Writing high level code is much easier than writing low level code, so fewer errors occur in the first place.

- The code can be produced hand in hand with a proof of its correctness. This is generally accepted to be simpler than *post facto* verification.

- The programs are easier to document.

- Structured programming techniques can be enforced, simplifying the verification task.

- Axiomatic proof techniques require that the code is formally documented with annotations.

However, there are disadvantages.

- By their very nature microprograms are machine specific. Any particular high level language is unlikely to be suitable for the wide variety of host architectures which exist. Moreover, the cost of producing software engineering tools for a machine dependent language is liable to be prohibitive if they are only to be used to implement a single macroarchitecture, as is commonly so. This would especially be a problem when the microcode was designed in conjunction with the microarchitecture itself. The tools would then have to be constantly rewritten to keep up with the design changes.

- The efficiency of microprograms is crucial. Compilers are unlikely to produce code which is as efficient as hand optimised code. This is especially true when compiling to microcode, owing to the additional problems of packing microinstructions. There are always likely to be time critical tasks for which hand produced code is required.

- The compiler itself may introduce bugs into the code. Some work on compiler correctness has been performed (see for example, [Moore 88] [Joyce 89c]), though it is still a research problem. If an optimising compiler is used, the compiler will be more complex and more likely to introduce errors.

- If changes are made to the resulting code output by the compiler, for example to optimise it, the proof of correctness will be invalidated. There is often a great temptation to hand optimise code in this way.

#### **STRUM**

Patterson's STRUM system [Patterson 79] [Patterson 81] is one such high level microprogramming verification system and is based on the London Software verification system [Igarashi 75]. Microprograms are written in a Pascal like

language which is defined by an axiomatic semantics allowing Hoare proofs to be conducted. The system has been used to verify an emulation of the HP2115 on the Burrough's D-Machine. This consists of a 1700 line source program which compiles into a 940 microinstruction microprogram after optimisation [Patterson 78] [Patterson 81]. The problems of producing efficient code were avoided because the system and language were designed around one particular host architecture. In fact the optimised STRUM emulation was faster than an emulation programmed independently in assembly language. To use the system for a different host architecture would require the rewriting of the declaration and code generation parts of the compiler. Since the language was designed specifically for the D-Machine, it is not clear that the results would be so impressive for different host architectures.

#### S\*

The machine independent language schema  $S^*$  [Dasgupta 80] was developed to overcome the problems of using machine independent high level microprogramming languages.  $S^*$  forms a family of languages for machine design which also includes  $S_A^*$ —an architecture description language [Dasgupta 81].

The schema is instantiated for a particular host machine to give a machine dependent language. This allows a well-structured microprogram to be produced, as with other high level languages. Additionally, it allows the microprogrammer to program using the particular microoperations available and indicate which should be packed into single microinstructions. Alternatively, code optimisation and compaction may be left to the compiler. Consequently, the efficiency of the implementation is not compromised.

Dasgupta and Wagner provided an axiomatisation for the machine dependent instantiation S\*(QM-1), for the QM-1 architecture [Wagner 83] [Dasgupta 84]. This has a two level control store where by the microinstructions are interpreted by an even lower level program. It also makes use of residual control in which part of the control word is stored in registers. A relatively small and uniform set of proof rules were discovered for S\*(QM-1). However, as they state, "the proof rules are far too cumbersome to be used in practical firmware design" [Dasgupta 84]. This is largely due to the many side effects which arise from attempting to divide microinstructions into distinct microoperations. The solution suggested was to use less complex architectures in cases where verification was desirable. A hand proof of the QM-C multiplication routine was described.

Recently Dasgupta has been involved in producing an axiomatic description language for describing computer architectures, S\*M [Dasgupta 86], based on S\*. The language allows separate units within the architecture to be described in a modular, structured fashion in the form of preconditions and postconditions, so amenable to this form of verification. The timing characteristics of each module may be specified in the form of guards. These include conditions which, if true, cause the activation of the module at the start of the indicated clock phase. Modules are thus activated non-procedurally.

### AADL/S\*

The work of Dasgupta and Wagner has been furthered by Damm [Damm 84a] [Damm 85a] [Damm 86]. The AADL/S\* system combines the architecture independent language schema S\* with the architecture description language AADL. AADL is an axiomatic description language similar to S\*M, though is procedurally based. Like S\*M it permits the specification of timing behaviour.

The operations of an architecture, A, are described using AADL. This formally defines the syntax and semantics of a machine dependent language S\*(A), which may then be used to program on the architecture. The AADL specifications for operations are converted into substitutions which are used to form proof rules for that operation. Microprograms are thus written in S\*(A) for a given microarchitecture A, described in AADL. The facilities of S\* again allow the programmer to indicate which microoperations are to be packed into single instructions. Damm has extended the proof rules to allow proofs that microoperations are dynamically disjoint. This means that they are prevented from being concurrent only if they will use the same resources. This contrasts with static disjointness, in which microoperations are considered to interfere if there is any possibility of a resource usage clash, even if run time conditions would prevent it [Damm 84b] [Damm 88]. Unfortunately the proof rules are very complex.

AADL is also used to specify the higher level architecture being implemented. Preconditions and postconditions are derived for each module's specification and so can be used in proofs. This allows the system to be split into a number of hierarchical layers which may be proved independently.

The methodology was applied to the design of an emulation of the NOVA-1200 computer on the MICRODATA 1600; a commercially available architecture which allows limited microcode self modification and uses residual control [Damm 85b]. In the course of this exercise, an I/O handling error was detected in the original code upon which the emulation was based.

#### **INMOS**

The system used by INMOS to formally derive the microcode for the IMS T800 floating point unit is based around the Occam language [May 87] [Shepherd 88]. This has a rich formal semantics in the form of transformational laws [Roscoe 86]. Using these laws, Occam programs may be transformed into other equivalent ones. This notion is the basis of the system. Rather than compiling a high level program into a low level one, the microprogrammer uses the laws to transform it into one. In this way, the problems of compiler correctness and producing efficient code are avoided, though the microprogrammer does much more work.

The specification is first refined into a high level Occam implementation using the methods suggested by Gries [Gries 81]. This high level Occam program is then transformed into a low level one, close to the form of the assembly language. This involves converting test conditions, arithmetic and logical unit operations and control sequencing to forms available on the microarchitecture. The transformation process is not fully automated; instead the system applies transformations as

directed by the user. A pattern matcher then converts the low level Occam into assembler source, which may be assembled into the bit pattern code.

The system was still under development during the coding of the IMS T800 floating point unit. Therefore, the above process was not strictly adhered to. Instead, for most instructions two full versions of the code were written—one high and one low level. The low level code was transformed into the form of the formally verified high level program, ensuring its correctness. A second design was produced in parallel using conventional design techniques. The transformational design was ultimately used, however, as it overtook the conventional design, illustrating the success of the system.

### 2.1.2 Memory Image Microprogram Verification

Other methods of microcode verification take the microprogram in its bitstream form. It is treated as input data to an operational description of the host machine. The verification involves symbolically executing the host machine description, stepping it forwards through some number of microcycles and comparing the resulting symbolic state with that expected for the target machine.

These methods avoid the problems of high level coding.

- Any microcode can be verified, no matter which method was used to produce it.

- Programming methods which compromise the efficiency of the code do not have to be used.

- The actual memory image is verified, so there is no problem of compiler correctness.

- If the description of the host program is given in an executable language, it can be used to perform simulations. This is a major advantage if the microprogram is being developed in tandem with the architecture.

- It allows normal testing to be conducted without needing the underlying hardware to be available.

- It means that a special simulator need not be written for each new architecture.

- It means that changes to the architecture will not require changes to the simulator, only to the architecture's formal specification.

However, there are still disadvantages.

- The verification is performed *post facto*. No help in the development process is provided.

- The microcode is treated as data. Consequently, structuring the proof is less natural, since the higher level concept of the code being a program is lost.

- Since the code can be produced by any means, it is liable to be completely unstructured, involving lots of jumps and possibly self modifying code.

- In general, these systems do not require any documentation of how the code implements the functional specification. The functional specification itself is all that is used.

- Code that is relocatable cannot be verified since a memory image is used as the microprogram source.

#### MCS

MCS [Carter 77] [Carter 78a] originated from the work of Birman [Birman 74]. It is an automated system which was very successfully applied symbolic simulation techniques to production microcode. Macro and micro level specifications are written in LSS—a Language for Symbolic Simulation [Joyner 78] [Carter 79]. A simulation relation is also given. This describes relationships which should hold between the resources of each level machine at particular corresponding control points. Each description is then symbolically executed between these control points, and it is proved that the resulting states correspond, according to the simulation relation. Loops in either host or target code are broken by inductive assertions [Leeman 74]. The automated system provides a problem reduction framework [Birman 76] [Joyner 76] based on the ideas behind the LCF [Gordon 79] theorem prover. The problem of proving simulation is initially set as a goal. This is then refined into simpler and simpler subgoals until it is proved.

The technique was first used to verify code for the S-Machine architecture—a simple hypothetical machine. The microarchitecture was vertically microprogrammed and the proof was performed by hand. Three errors were found in the microcode [Birman 74]. The proof was later repeated using MCS and an additional error was found [Carter 75]. For this automated proof, additional control points were added. However, this involved rewriting the target specification to mirror the microcode control structure so that points in the specification corresponded to control points in the microprogram. Further hand proofs were performed for two implementations of the S-Machine on a horizontal microarchitecture. The first was a naive implementation whereas the other overlapped instruction fetching and execution [Carter 77]. A horizontally microprogrammed extended version of the S-Machine was also proved [Leeman 75]. This implemented a division instruction and allowed up to three levels of indirection. MCS was also used to verify production microcode—that implementing a version of the NASA Standard Spaceborne Computer-2 which supports the 86 standard System/360 instructions and includes a single I/O channel. A number of errors in the code were discovered during the verification attempt [Carter 78a] [Carter 78b]. In connection with this proof, some research was performed using MCS to verify communication protocols [Brand 78]. In particular a simplified version of the HDLC protocol was verified [Brand 82].

#### **SDVS**

The SDVS approach [Crocker 80] [Marcus 84] is similar to that of MCS. In both systems the host, in conjunction with a bit representation of the microcode, and the target specifications are symbolically executed between user supplied stopping points. In SDVS the host and target specifications are given in the programming language ISPS. The system then converts these to a set of temporal logic formulae called "state deltas". These describe state changes in the machine over a time interval. Conceptually, one state delta is created for each ISPS statement. Points in the target program which correspond to points in the execution of the microprogram may be identified. Symbolically executing the sets of state deltas between these points give new state deltas which describe the state changes between Case analysis is performed at branch points, giving separate state deltas incorporating appropriate path conditions. Typically, the stopping points will correspond to the boundaries of a macrocycle and the state deltas will represent the state changes caused by the target level instructions. As with MCS, the proof cannot be subdivided according to the structure of the microprogram unless such subdivisions correspond to points in the target program. This will generally not be so unless the target description is written in a way that mirrors the microcode, or vice versa. The correctness proof involves showing that the target level state deltas are implied by the host state deltas together with the microcode and a map relating target level resources to those of the host.

Initial experiments with the system involved work on a simple GCD Machine [Levy 84], the H-Machine—a simplified version of the AM2901 [Marcus 84], and the Fault Tolerant Spaceborne Computer—a 32 bit machine intended for maintenance free survival in space [van-Mierop 78]. Recent work has included the verification of the BBN C/30, which is used in the packet switched nodes of the Defense Data Network and contains almost 5000 words of microcode [Crocker 88]. Also, a reverification of the FM8501 microcode, originally verified using the Boyer-Moore system described later, has been performed [Crocker 88].

#### **MIDDLE**

The verification method developed by Budkowski et al. [Budkowski 78] also takes a bitstream version of the microprogram. Unlike the other approaches which start with low level code, the microprogram is not just treated as data to the host machine. Instead, it is combined with a description of the hardware to give a microprogram written in the specially designed language MIDDLE [Dembiński 78a] [Dembiński 78b]. This may be transformed to a register transfer level program using syntactic transformations and simplification. The resulting program may then be verified using any conventional software verification technique, not necessarily symbolic simulation.

The MIDDLE program has the same structure as the original microcode. Unless the microcode was written with verification in mind, it is likely to contain many jumps and have a fairly scrambled control structure. Such a control structure greatly complicates the task of verification and does not help make the program intelligible.

Transformations are suggested which could be applied to convert the program to a more suitable form for verification, though the complex control structure will remain [Dembiński 83]. Also, as with the INMOS method these transformations are chosen by hand. The situation is exasperated further, due to the simplistic method used to convert the bitstream version to MIDDLE code. The calculation of possible next addresses is performed by inspection of only the current microinstruction. No account is made of the effect of instructions executed at earlier points on paths through the instruction. This means that many unexecutable jumps may be included in the resulting program, rendering it unnecessarily complicated. This could be a serious hindrance if used on complex architectures.

The method was used to prove several arithmetic microprograms for a floating point arithmetic and logical unit designed at the Warsaw Technical University. These proofs were performed by hand, as the system was not mechanised. The software verification technique used to verify these programs was an algebraic method [Blikle 76]. The semantics of individual MIDDLE commands was described by input-output relations, which were composed to give a relation for the whole program. This was then manipulated algebraically by applying a set of transformations to it until it had the form of the target description.

#### HOL

HOL [Gordon 87] [Camilleri 86] and its forerunner LCF-LSM [Gordon 81a] are LCF [Gordon 79] style theorem proving systems used for hardware verification. The underlying logic of the HOL system is higher order logic which has also been used for hardware verification and specification by Hanna and Daeche [Hanna 86]. In these systems, a structural specification of the implementation of a device and its functional specification are given in the logic. A theorem giving a correctness statement relating these descriptions, with respect to suitable abstractions, is then proved using the theorem prover.

In addition to the proofs of other hardware devices, the HOL system has been used to verify a microcoded machine—Gordon's computer [Joyce 86] [Joyce 88b] [Joyce 89a]. This is a simple toy machine, designed as an example of hardware verification. The proof was originally performed using the LCF-LSM system [Gordon 81b]. The Tamarack microprocessor, which is a version of Gordon's computer, has since been fabricated as a CMOS chip [Joyce 88a] [Joyce 88b]. Recently, a verification of microcode for an extended version of the Tamarack microprocessor, Tamarack-3, has been performed [Joyce 89b]. This computer performs asynchronous interactions with the external environment using a handshaking protocol.

The HOL system has also been used in the verification work performed on the VIPER microprocessor. This is a commercially produced microprocessor developed using formal methods [Cullyer 88]. It is specified in a sequence of decreasingly abstract levels. A HOL proof has shown the equivalence of the top two of these levels [Cohn 87]. Some work has also been performed on a proof of the next level [Cohn 88]. The former proof was originally performed by hand. The HOL proof highlighted discrepancies in this proof, though showed it to be basically sound. The

15

top level specification (the target specification) is a functional specification giving transformations between high level machine states. This was shown equivalent to an implementation on the next level—the major state machine. This implementation executes a series of events which change the machine state. Thus, the major state machine is similar in nature to a microcoded implementation of the functional specification with respect to the proof. The sequences of events define a state transition graph, which takes the place of a program. Execution of events is similar to executing microinstructions. The proofs of Gordon's computer and the VIPER major state machine follow the same basic form. The implementation is symbolically simulated to produce theorems giving the effects of each path through the microcode. This is done by repeatedly expanding the definition of the host under suitable path conditions. The correctness statement is then proved by case analysis of the possible path conditions.

A disadvantage of using HOL is that the logic is not directly executable, preventing simulations of HOL specifications from being performed. This is useful for increasing confidence in the correctness of the specifications. Methods for converting a subset of the logic into an executable form have been suggested, however [Camilleri 88]. A further disadvantage is that HOL requires significant mathematical ability to drive. It is more suited to use by a team of verification specialists rather than by actual programmers.

#### VERIFY

The VERIFY system [Barrow 84b] [Barrow 84a] also evolved from the LCF-LSM approach for verifying digital hardware designs. As with the LCF-LSM and HOL work, the approach is geared to verifying hardware designs in general, rather than microprograms. The emphasis is placed on modularising the proof with respect to the hardware description, rather than the microcode. The user supplies a structural and behavioural specification of the hardware. The structural description is modular, with equations describing the inter-connections between modules for each state variable and output. The structural specification is converted into a behavioural one, and equivalence with the supplied behavioural specification For a microprogrammed implementation, this involves showing that a behavioural specification of the macroarchitecture is equivalent to an unfolded version of the microarchitecture specification. This is done by performing case analysis to produce all paths through the code, and then producing equations giving the effects of each path on each state variable and output. These are then shown to be the same as for the macroarchitecture. The VERIFY system is largely automatic and is implemented as a PROLOG program. It has been used to redo the proof of Gordon's computer, together with proofs of other hardware examples.

#### The Boyer-Moore Theorem Prover

The Boyer-Moore Theorem Prover [Boyer 79] has also been used as a hardware verification system in a similar way to HOL [Hunt 85]. Structural and behavioural specifications are written in the Boyer-Moore logic together with a correctness

statement. This statement is then proved by unrolling the definitions in the specifications and performing case analysis over the paths through the microcode. Unlike the HOL system the Boyer–Moore Theorem prover is intended to be an automatic theorem prover. However, in practice the verifier must guide the system by first proving intermediary lemmas, so knowledge of the heuristics used by the prover is required. A further difference is that the Boyer–Moore logic is executable, allowing specifications to be tested.

The system has been used to prove the correctness of the FM8501 processor. This is a 16 bit microprocessor, similar in size and complexity to a PDP-11 which was specifically designed as a verification case study. The microcode in the FM8501 was very simple, however, consisting of only 16 microwords. A similar though extended machine, FM8502, was also verified.

### 2.1.3 Assembly Language Verification Systems

Some systems verify assembly language code. Typically, the semantics of the assembler instructions are specified by giving a translation of each into some modelling language. This contrasts with the bitstream methods in which a description of a particular host architecture is given in a hardware description language of known semantics. The translation is used to convert the assembly code into a program in the modelling language. This can then be verified using standard program verification techniques.

Practical systems using this approach have been mainly for machine code proof rather than for microcode proof. This is because microinstructions are often horizontal and consequently the translation process is more complex. This problem is partly overcome by splitting the microinstructions into microoperations. Translations are then given for these individually, though as noted from the QM-1 work, splitting microinstructions into individual microoperations is not always straightforward.

Verifying the code in this way gains some of the advantages of each of the previous methods.

- The code is still written at a low level, so the efficiency of the microcode is not necessarily compromised.

- The problems of the compiler introducing errors are largely avoided. Even though an assembler may introduce errors in the same way as a compiler, this is less likely to be a problem. Assemblers are far simpler than compilers, so are less likely to contain errors. Verification of an assembler would be more practical than for a compiler.

- The code is converted to a precise human readable form. This can be checked, allowing bugs to be spotted at an early stage.

- The program is not just treated as data. Consequently, its structure is not lost to the proof effort.

Disadvantages remain.

- The verification is still performed post facto.

- Assembly languages tend to be unstructured, complicating the verification task.

- New problems due to the assembly language, such as aliasing of names, may arise.

- The translation to the modelling language is performed either by hand or by programs specific to individual assembly languages. Errors can be introduced at this point. This would only be a problem if errors in the assembly code were nullified by the translation process. Other errors would just cause the proof attempt to fail so this problem is less critical than for compiler correctness.

- The division of microinstructions into microoperations introduces new problems such as side effects.

#### Ramamoorthy and Shankar

Early work of this nature with respect to microcode was conducted by Ramamoorthy and Shankar [Ramamoorthy 74]. They were concerned with showing the equivalence of microprograms. This is of use, for example, to determine whether two emulations are equivalent. They only considered simply structured code with no loops and at most a two-way branch in any microinstruction. The method involves first converting the microoperation assembler version of the microprogram into atomic microoperations from a standard set. The two microprograms are then split into separate paths, the path conditions for which are determined. Corresponding paths from the two microprograms are paired, equivalent variables from the machines having been identified by the user. Separate sequences of microoperations are extracted from these pairs, for each pair of corresponding outputs of interest. Symbolic manipulation techniques are then used to show that these outputs are given the same values. The microprograms may also be shown to be correct by comparing the symbolic value given to each output with the specification.

#### Brioschi and Scaini

Brioschi and Scaini also proposed a method for proving microcode correctness which takes assembler input [Brioschi 76]. Rather than performing a translation from the assembler code, however, it is symbolically interpreted directly. A path analysis is first conducted and the symbolic interpretation performed on each path separately. The resulting states are then shown to be identical to that required by the target specification. The method was not mechanised, and was only used for small examples on a specially designed simple machine.

#### Maurer

The assembler approach is basically that adopted by Maurer to prove the machine coded flight director program for the Litton C4000 airborne computer [Maurer 76]. This is a simple program with no loops or subscripted variables and only a single subroutine. The proof does deal with overflow conditions, the way the code performs approximate calculations, and scaling problems with fixed point values. Maurer also addresses the problems of potentially self modifying code [Maurer 74]. An IBM 370 assembly language verifier has been produced, and used to verify programs implementing simple algorithms such as Euclid's GCD Algorithm [Maurer 77]. Simple algebraic equivalents were given for each machine code instruction. A variation of Floyd's Inductive Assertions method was then used to prove the code. This proof was computer aided.

#### **SPADE**

Clutterbuck and Carré also use this basic approach for verifying macro level assembly language programs [Clutterbuck 86] [Clutterbuck 88]. In their SPADE system, the algebraic modelling language FDL is used. The transformation into FDL is performed by a translator for each assembly language considered. Once the assembly program has been converted into FDL, the SPADE program analysis tools may be used. These include program flow analysis tools (such as a data flow analyser) as well as tools for formally proving program correctness. In the translation to FDL any structure that the code may have had is lost. The flow analysis tools may be used to rediscover it. The verification method is basically Floyd's [Floyd 67]. The specification is given in terms of preconditions and postconditions. Verification conditions are then generated for each path through the code. In addition to a full program proof, a "shallow" proof that certain run time errors such as overflow do not occur can be separately performed.

Source level restrictions are applied to the code to make the verification task more tractable. This means that a suitable subset of the source language must be identified, and programming is done very much with verification in mind. Using the disallowed techniques is deemed to be bad programming practice and incompatible with safety-critical applications.

The SPADE system is being used commercially to validate both low and high level software. It has been used to verify specially written programs for the Intel-8080. The code was written in SPADE-8080 - the "safe" subset of the Intel-8080 language. A more impressive demonstration of the system is the proof of the LUCOL Z8002 assembly code modules for the fuel control unit of the Rolls-Royce RB211-524G jet engine [O'Neill 88]. As a consequence of the formal verification process, the code of one module was altered to cope with extreme inputs and the informal documentation of 10% of the modules was revised.

# 2.2 The SPOOK System

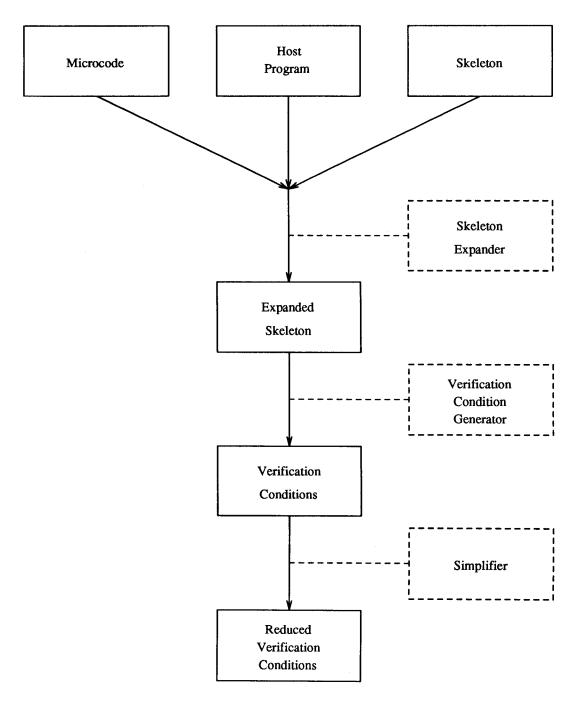

In this dissertation I introduce a new microprogram verification system—SPOOK, an overview of which is shown in Figure 2.1. The SPOOK system is a hybrid of the previous systems, and so it gains many of the advantages of each. The microprogram is initially taken in the form of a memory image. This is transformed into a high level program in a modelling language as with the MIDDLE and assembler systems. Unlike these systems, however, the resulting high level program is structured and modular, gaining the advantages of software verification techniques. This is achieved by making the user supply extra documentation of the code in the form of a structured and modular state transition graph for the microprogram.

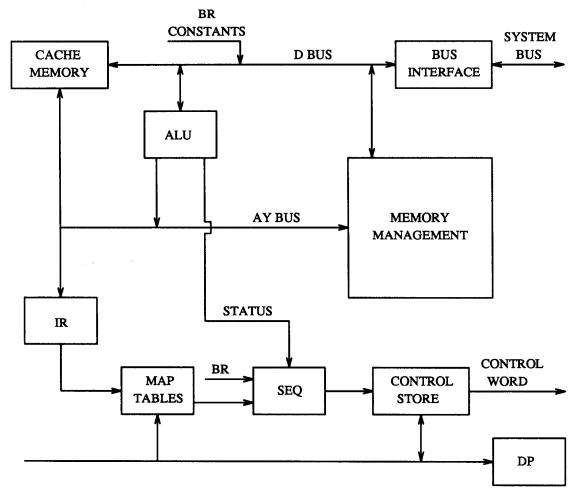

The user of the system supplies four things:

- The Host Program—The Microarchitecture,

- The Skeleton—A State Transition Graph of the Microprogram,

- The Target Specification—The Macroarchitecture, and

- The Microprogram—A Memory Image.

The host program, target specification and microprogram are provided in some form to all memory image systems. The need for the skeleton is unique to the SPOOK system. The SPOOK language, which is a simple imperative language derived from BSPL [Richards 86], is used to describe each of the above. In addition it is also used as the modelling language for the high level version of the microprogram that the system produces. Chapter 3 deals with the syntax and semantics of the SPOOK language. Whilst a familiarity with the language is a prerequisite for the remainder of the dissertation, a detailed understanding is not necessary on a first reading.

# 2.2.1 The Host Program

The host program provides a formal description of the microarchitecture as a clocked finite state machine with a single universal clock. It describes the effects of a single clock cycle on the state and outputs of the machine given the values on the inputs for that cycle. This model is obtained by enforcing a strict structure on the program. It is the use of a host program that allows the system to be universal with respect to the microarchitecture. Only a new host program need be provided to use the system with a different microarchitecture. The use of the host program is described in detail in Chapter 4.

#### Collapsed Host Programs

Information which is known about the state at a particular instant of time can be used to produce a collapsed host program. These are specialised versions of the host program, which describe the effect of running the machine for one clock cycle from a state satisfying the given condition. They are equivalent to a host program for a

Figure 2.1: An overview of the SPOOK system

machine identical to the original, except with the known values hardwired in. A host program is collapsed by substituting in known values for state variables and then performing constant folding and rewriting. This collapsing mechanism is used in the verification process, reducing the complexity at an early stage. It also provides a useful tool to aid the understanding of microinstructions, giving a concise and formal description of their action. It is one of the major features of the system, and is also described in Chapter 4.

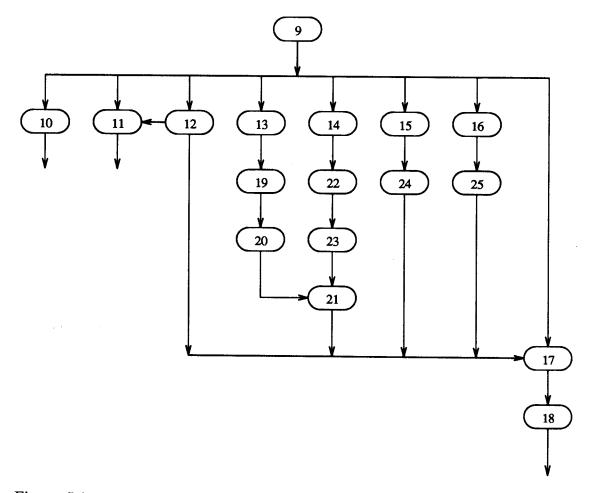

#### 2.2.2 The Skeleton