Number 196

# The semantics of VHDL with Val and Hol: towards practical verification tools

John Peter Van Tassell

June 1990

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

© 1990 John Peter Van Tassell

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

#### **ABSTRACT**

Van Tassel, John Peter. M.S., Department of Computer Science and Engineering, Wright State University, 1989. The Semantics of VHDL with VAL and HOL: Towards Practical Verification Tools.

The VHSIC Hardware Description Language (VHDL) is an emerging standard for the design of Application Specific Integrated Circuits. We examine the semantics of the language in the context of the VHDL Annotation Language (VAL) and the Higher Order Logic (HOL) System with the purpose of proposing methods by which VHDL designs may be converted into these two forms for further validation and verification. A translation program that utilizes these methods is described, and several comprehensive VHDL design examples are shown.

# Contents

| 1 | Intr | oducti  | ion .                        |   | . ' |   |    |     |   | 1  |

|---|------|---------|------------------------------|---|-----|---|----|-----|---|----|

|   | 1.1  | Ration  | nale                         |   | • . |   |    |     |   | 1  |

|   | 1.2  | Langu   | ages                         |   |     |   |    |     |   | 2  |

|   |      | 1.2.1   | VHDL                         |   |     |   |    |     |   | 2  |

|   |      | 1.2.2   | VAL                          |   |     |   |    |     |   | 2  |

|   |      | 1.2.3   | HOL                          |   |     |   |    |     |   | 3  |

|   |      |         |                              |   |     |   |    |     |   |    |

| 2 | VH   | DL ·    |                              |   |     |   |    |     |   | 4  |

|   | 2.1  | Backg   | round                        |   |     |   |    |     |   | 4  |

|   | 2.2  | Simula  | ation Cycle and Timing Model |   |     |   | :. |     |   | 5  |

|   | 2.3  |         | nents                        |   |     |   |    |     |   | 6  |

|   | *    | 2.3.1   | Architectures                |   |     |   |    |     |   | 6  |

|   |      | 2.3.2   | Signal Assignments           |   |     |   |    |     |   | 7  |

|   |      | 2.3.3   | Conditionals                 |   |     |   |    |     |   | 9  |

|   |      | 2.3.4   | Processes and Blocks         |   |     |   |    |     |   | 12 |

|   | 2.4  | Exam    | ple                          |   |     |   |    |     |   | 13 |

|   |      | 2.4.1   | ONE                          |   |     |   |    |     |   | 13 |

|   |      | 2.4.2   | Inverter                     |   |     |   |    |     |   | 13 |

|   |      | 2.4.3   | Register                     |   |     |   |    | . • |   | 15 |

|   |      | 2.4.4   | Multiplexer                  |   |     |   |    |     |   | 15 |

|   |      | 2.4.5   | Parity Checker               | • |     | • | •  |     |   | 17 |

| 3 | VAJ  | C       |                              |   |     |   |    |     |   | 21 |

|   | 3.1  | Overv   | ew                           |   |     |   |    |     | ٠ | 21 |

|   | 3.2  | Transl  | ation Methods                |   |     |   |    |     |   | 21 |

|   |      | 3.2.1   | Architectures                |   |     |   |    |     |   | 21 |

|   |      | 3.2.2   | Signal Assignments           |   |     |   |    |     |   | 22 |

|   |      | 3.2.3   | Conditionals                 |   |     |   |    |     |   | 24 |

|   | 3.3  | Examp   | ble                          |   |     |   |    |     |   | 24 |

|   |      | 3.3.1   | One                          |   |     |   |    |     |   | 25 |

|   |      | 3.3.2   | Inverter                     |   |     |   |    |     |   | 25 |

|   |      | 3.3.3   | Register                     |   |     |   |    |     |   | 25 |

|   |      | 3.3.4   | Multiplexer                  |   |     |   |    |     |   | 26 |

|   |      | 3.3.5   | Parity Checker               |   |     |   |    |     |   | 26 |

|   |      | 3.3.6   | Simulation Results           |   |     |   |    |     |   | 26 |

|   |      | , 3.3.0 |                              | • | •   | • | •  | •   | • | 20 |

| 4                         | но    |                               | <b>2</b> 9 |

|---------------------------|-------|-------------------------------|------------|

|                           | 4.1   | Overview                      | <b>2</b> 9 |

|                           | 4.2   | Types                         |            |

|                           | 4.3   | Statements                    |            |

|                           |       |                               | 31         |

|                           |       |                               | 32         |

|                           |       |                               | 34         |

|                           |       |                               | 35         |

| ,                         | 4.4   | Summary                       |            |

|                           |       |                               |            |

| 5                         | Tan   |                               | 37         |

|                           | 5.1   | Overview                      | 37         |

|                           | 5.2   | Basic Definitions             | 37         |

|                           |       | 5.2.1 Package Tamarack        | 37         |

|                           |       |                               | 43         |

|                           |       | 5.2.3 Words                   | 44         |

|                           | 5.3   | Microcode and ROM             | 45         |

|                           |       | 5.3.1 Package MicroCode       | 45         |

|                           |       |                               | 48         |

|                           | 5.4   | Primitive System Components   | 56         |

|                           | 5.5   | ALU                           | 56         |

|                           | 5.6   | Memory                        | 56         |

|                           | 5.7   | Major Subsystems              | 63         |

| 6                         | Con   | clusions and Further Research | 74         |

| $\mathbf{R}_{\mathbf{c}}$ | efere | nces                          | 76         |

# List of Figures

| 2.1  | An example of the process statement                                                                            | 5        |

|------|----------------------------------------------------------------------------------------------------------------|----------|

| 2.2  | A simulation cycle                                                                                             | 6        |

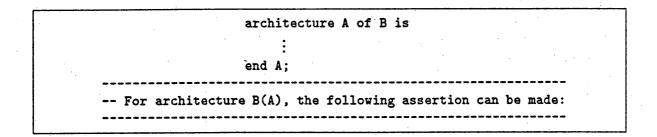

| 2.3  | VHDL architecture skeleton and generated comment                                                               | 7        |

| 2.4  | Inertial delay signal assignment                                                                               | 8        |

| 2.5  | Inertial delay with propagation time                                                                           | 8        |

| 2.6  | Generated assertion for inertial delay                                                                         | 8        |

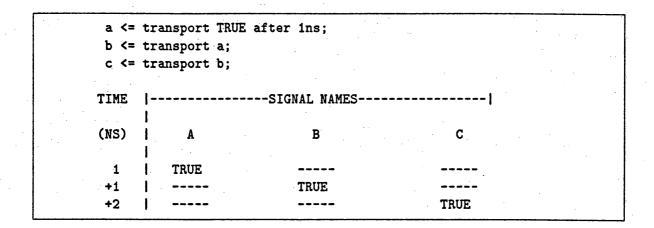

| 2.7  | Signal assignment with transport delay                                                                         | 9        |

| 2.8  | Generated assertion for transport delay                                                                        | 9        |

| 2.9  | General form of the if statement                                                                               | 9        |

| 2.10 |                                                                                                                | 10       |

| 2.11 | General form of the case statement                                                                             | 10       |

| 2.12 | Sample conditional signal assignment statement                                                                 | 10       |

| 2.13 | Generated assertion for a conditional signal assignment                                                        | 11       |

| 2.14 | Sample guarded signal assignment                                                                               | 11       |

| 2.15 | Sample guarded signal assignment                                                                               | 11       |

| 2.16 | Sample loop statement                                                                                          | 12       |

| 2.17 | Generated assertion for sample loop statement                                                                  | 12       |

|      |                                                                                                                | 12       |

|      | - Tarana da Tarana d | 13       |

|      | <del>-</del>                                                                                                   | 14       |

|      |                                                                                                                | 14       |

|      |                                                                                                                | 14       |

|      |                                                                                                                | 15       |

|      |                                                                                                                | 15       |

|      |                                                                                                                | 15       |

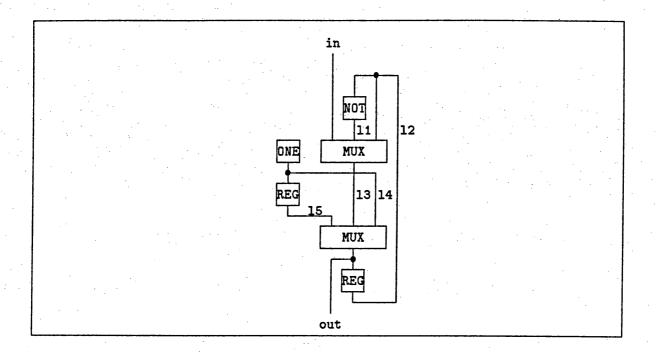

|      |                                                                                                                | 15<br>16 |

|      |                                                                                                                | 10<br>16 |

| 2.21 | Concepted assertion for Multiplemen                                                                            |          |

| 2.20 |                                                                                                                | 16       |

|      |                                                                                                                | 17       |

|      |                                                                                                                | 17       |

|      |                                                                                                                | 17       |

|      |                                                                                                                | 18       |

|      |                                                                                                                | 19       |

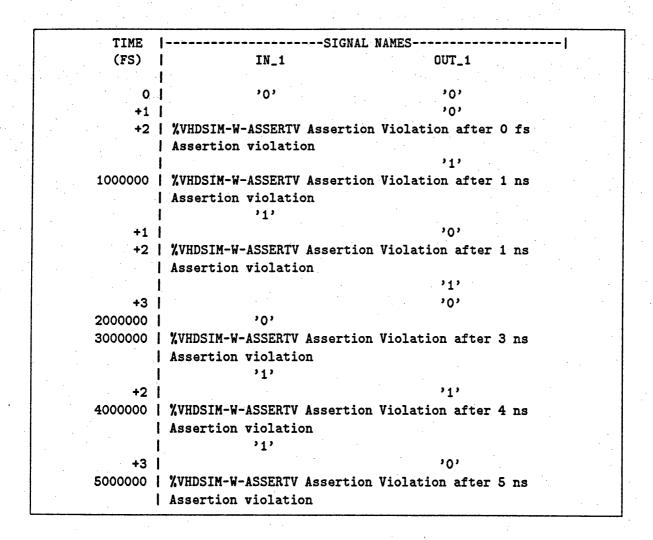

| 2.34 | Simulation results for Parity_Check                                                                            | 20       |

| 3.1  | Inertial delay                                                                                                 | 22       |

| 3.2  | Transport delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.3  | Transport delay conditional signal assignment (VHDL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23 |

| 3.4  | Transport delay conditional signal assignment (VAL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23 |

| 3.5  | Inertial delay conditional signal assignment (VAL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23 |

| 3.6  | Translation of if statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24 |

| 3.7  | Sample loop statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24 |

| 3.8  | VAL translation of loop statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25 |

| 3.9  | VAL translation of a guarded signal assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25 |

|      | VAL version of One                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25 |

| 3.11 | VAL version of Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26 |

|      | VAL version of Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26 |

| 3.13 | VAL version of Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26 |

| 3.14 | VAL version of high-level Parity_Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27 |

|      | Simulation results for sometime version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27 |

|      | Simulation results for finally version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28 |

|      | Simulation results for eventually version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28 |

| 0.1. | Difficulties 101 controlled visit vi |    |

| 4.1  | HOL declarations for BIT and BIT_VECTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30 |

| 4.2  | Translation of a VHDL array type definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31 |

| 4.3  | HOL translation of a VHDL record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31 |

| 4.4  | Translation of entity declaration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32 |

| 4.5  | HOL Specification of 'Stable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32 |

| 4.6  | HOL version of transport delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33 |

| 4.7  | HOL version of inertial delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33 |

| 4.8  | HOL version of conditional signal assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 4.9  | HOL version of a guarded signal assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34 |

|      | HOL translation of if statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | HOL version of a case statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 4.12 | Extracted process and block definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36 |

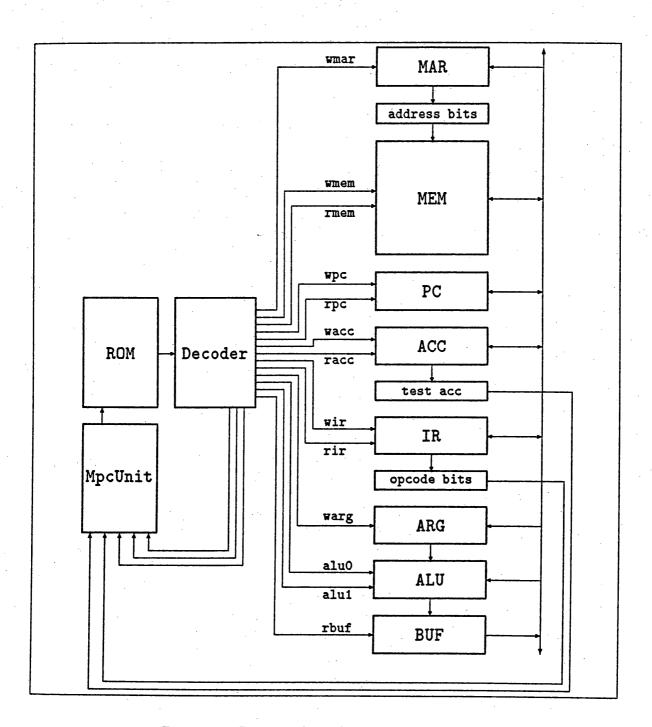

| 5.1  | Register-Transfer Level Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |