Number 195

# Multi-level verification of microprocessor-based systems

Jeffrey J. Joyce

May 1990

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

## © 1990 Jeffrey J. Joyce

This technical report is based on a dissertation submitted December 1989 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Pembroke College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

## Abstract

The idea of using formal logic to reason about small fragments or single layers of a software/hardware system is well-established in computer science and computer engineering. Recently, formal logic has been used to establish correctness properties for several realistic systems including a commercially-available microprocessor designed by the British Ministry of Defence for life-critical applications. A challenging area of new research is to verify a complete system by linking correctness results for multiple layers of software and hardware into a chain of logical dependencies.

This dissertation focuses specifically on the use of formal proof and mechanical proofgeneration techniques to verify microprocessor-based systems. We have designed and verified a complete system consisting of a simple compiler for a hierarchically structured programming language and a simple microprocessor which executes code generated by this compiler. The main emphasis of our discussion is on the formal verification of the microprocessor. The formal verification of the compiler is described in a separate paper included as an appendix to this dissertation.

Combining correctness results for the compiler with correctness results for the microprocessor yields a precise and rigorously established link between the formal semantics of the programming language and the execution of compiled code by a model of the hardware. The formal proof also links the hardware model to the behavioural specification of an asynchronous memory interface based on a four-phase handshaking protocol.

The main ideas of this research are (1) the use of generic specification to filter out non-essential detail, (2) embedding natural notations from special-purpose formalisms such as temporal logic and denotational description, and (3) the use of higher-order logic as a single unifying framework for reasoning about complete systems.

Generic specification, in addition to supporting fundamental principles of modularity, abstraction and reliable re-usability, provides a mechanism for enforcing a sharp distinction between what has and what has not been formally considered in a proof of correctness. Furthermore, it is possible to create generic specifications in a pure formalism with the expressive power of higher-order logic without inventing new constructs.

Natural notations from special-purpose formalisms offer the advantage of concise and meaningful specifications when applied to particular areas of formal description. Semantic gaps between different notations are avoided by embedding them in a single logic. Special-purpose rules based on these notations can be derived as theorems with the aim of implementing more efficient proof strategies.

Finally, it is argued that the primary purpose of using mechanical proof generation techniques to reason about software and hardware is to support the intelligent participation of a human verifier in the rigorous analysis of a design at a level which supports clear thinking.

This dissertation is the result of my own work and, unless otherwise stated in the text, includes nothing which is the outcome of work done in collaboration. No part of this dissertation has already been, or is currently being, submitted for any degree, diploma or other qualification at any other university.

# ${\bf Contents}$

| L | $\mathbf{Intr}$                   | f 4      |                                           |  |  |  |  |  |  |  |  |  |

|---|-----------------------------------|----------|-------------------------------------------|--|--|--|--|--|--|--|--|--|

|   | 1.1                               | Motivati | on                                        |  |  |  |  |  |  |  |  |  |

|   | 1.2                               | Problem  | Definition                                |  |  |  |  |  |  |  |  |  |

|   | 1.3                               | Main Ide | eas                                       |  |  |  |  |  |  |  |  |  |

|   |                                   | 1.3.1 O  | Overview                                  |  |  |  |  |  |  |  |  |  |

|   |                                   | 1.3.2 S  | tructured Computer Organization           |  |  |  |  |  |  |  |  |  |

|   |                                   | 1.3.3 T  | otally Verified Systems                   |  |  |  |  |  |  |  |  |  |

|   |                                   | 1.3.4 G  | Seneric Specification                     |  |  |  |  |  |  |  |  |  |

|   |                                   | 1.3.5 E  | mbedding Other Notation                   |  |  |  |  |  |  |  |  |  |

|   |                                   | 1.3.6 E  | stablished Notations                      |  |  |  |  |  |  |  |  |  |

|   | 1.4                               | The TAN  | MARACK Stack                              |  |  |  |  |  |  |  |  |  |

|   |                                   | 1.4.1 A  | Very Simple Compiler                      |  |  |  |  |  |  |  |  |  |

|   |                                   | 1.4.2 A  | Very Simple Microprocessor                |  |  |  |  |  |  |  |  |  |

|   |                                   | 1.4.3 L  | inking the Compiler to the Microprocessor |  |  |  |  |  |  |  |  |  |

|   | 1.5                               | Related  | Work                                      |  |  |  |  |  |  |  |  |  |

|   |                                   | 1.5.1 M  | Icroprocessor Verification                |  |  |  |  |  |  |  |  |  |

|   |                                   | 1        | .5.1.1 FM8501                             |  |  |  |  |  |  |  |  |  |

|   |                                   | 1        | .5.1.2 VIPER                              |  |  |  |  |  |  |  |  |  |

|   |                                   | 1        | .5.1.3 Other Work                         |  |  |  |  |  |  |  |  |  |

|   |                                   | 1.5.2 V  | Verified Synthesis                        |  |  |  |  |  |  |  |  |  |

|   |                                   |          | Compiler Verification                     |  |  |  |  |  |  |  |  |  |

|   |                                   |          | Verified Systems                          |  |  |  |  |  |  |  |  |  |

|   |                                   | 1        | .5.4.1 The CLI Stack                      |  |  |  |  |  |  |  |  |  |

|   |                                   | 1        | .5.4.2 The SAFEMOS Stack                  |  |  |  |  |  |  |  |  |  |

|   | 1.6                               | Outline  | of this Dissertation                      |  |  |  |  |  |  |  |  |  |

| 2 | Formal Proof in the HOL System 24 |          |                                           |  |  |  |  |  |  |  |  |  |

|   | 2.1                               |          | tion                                      |  |  |  |  |  |  |  |  |  |

|   | 2.2                               |          | L Logic                                   |  |  |  |  |  |  |  |  |  |

|   |                                   |          | $^{\circ}$ erms                           |  |  |  |  |  |  |  |  |  |

|   |                                   |          | Ypes                                      |  |  |  |  |  |  |  |  |  |

|   |                                   |          | Typed Terms                               |  |  |  |  |  |  |  |  |  |

|   |                                   | 2.2.4 A  | axioms and Inference Rules                |  |  |  |  |  |  |  |  |  |

|   |                                   |          | Theories and Definitions                  |  |  |  |  |  |  |  |  |  |

|   | 2.3                               |          | L Proof Generating System                 |  |  |  |  |  |  |  |  |  |

|   |                                   |          | Proving Theorems                          |  |  |  |  |  |  |  |  |  |

|   |                                   |          | orward and Backward Proof                 |  |  |  |  |  |  |  |  |  |

|   |                                   |          | ystem Theories                            |  |  |  |  |  |  |  |  |  |

|   |                                   |          | ecurity                                   |  |  |  |  |  |  |  |  |  |

|   |                                   |          | Extensibility                             |  |  |  |  |  |  |  |  |  |

|   |                                   |          | fore Detailed Descriptions                |  |  |  |  |  |  |  |  |  |

|   | 2.4                               |          | for Mechanized Formal Proof               |  |  |  |  |  |  |  |  |  |

|   |                                   |          |                                           |  |  |  |  |  |  |  |  |  |

| 3 | $\mathbf{A} \mathbf{S}$ | imple  | Microprocessor                               | 34         |

|---|-------------------------|--------|----------------------------------------------|------------|

|   | 3.1                     | Progra | amming Level Model                           | 34         |

|   |                         | 3.1.1  | Basic Data Types and Primitive Operations    | 34         |

|   |                         | 3.1.2  | Externally Visible State                     | 36         |

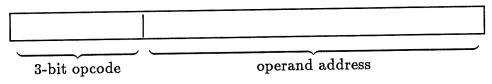

|   |                         | 3.1.3  | Instruction Word Format                      | 36         |

|   |                         | 3.1.4  | Instruction Set Semantics                    | 37         |

|   |                         | 3.1.5  | Hardware Interrupts                          | 39         |

|   | 3.2                     | Memo   | ry Interface                                 | 40         |

|   |                         | 3.2.1  | Fully Synchronous Mode                       | 40         |

|   |                         | 3.2.2  | Fully Asynchronous Mode                      | 41         |

|   |                         | 3.2.3  | Extended Cycle Mode                          | 41         |

|   | 3.3                     | Intern | al Architecture                              | 43         |

|   |                         | 3.3.1  | Register-Transfer Level Structure            | 44         |

|   |                         | 3.3.2  | Overview of Instruction Interpretation       | 44         |

|   |                         | 3.3.3  | Multiple Interpretation Levels               | 47         |

|   |                         |        | 3.3.3.1 Microprogramming Level               | 48         |

|   |                         |        | 3.3.3.2 Phase Level                          | 49         |

|   |                         | 3.3.4  | Some Bottom Level Assumptions                | 53         |

|   |                         |        | •                                            |            |

| 4 | For                     | mal Sp | pecification                                 | <b>55</b>  |

|   | 4.1                     | Gener  | ic Specification                             | 55         |

|   |                         | 4.1.1  | Motivation                                   | 55         |

|   |                         | 4.1.2  | Formal Basis                                 | 57         |

|   | 4.2                     | TAMA   | ARACK-3 Specification                        | <b>5</b> 9 |

|   |                         | 4.2.1  | Specifying Structure and Behaviour           | 60         |

|   |                         | 4.2.2  | Internal Architecture                        | 60         |

|   |                         |        | 4.2.2.1 Primitive Components of the Datapath | 60         |

|   |                         |        | 4.2.2.2 Modelling System Bus Operation       | 61         |

|   |                         |        |                                              | 62         |

|   |                         |        |                                              | 64         |

|   |                         |        | 4.2.2.5 Microcode Source and Micro-Assembler | 66         |

|   |                         |        |                                              | 69         |

|   |                         |        | 4.2.2.7 Control Unit Implementation          | 70         |

|   |                         |        | 4.2.2.8 Top Level Structure                  | <b>71</b>  |

|   |                         | 4.2.3  | Programming Level Model                      | <b>72</b>  |

|   |                         | 4.2.4  | External Memory Specification                | 74         |

| 5 | T23                     | 1 37   |                                              |            |

| o | 5.1                     |        |                                              | 76         |

|   | 9.1                     | 5.1.1  | ation Plan                                   | 76         |

|   |                         |        | Stating Correctness Results                  | 76         |

|   |                         | 5.1.2  | Multi-Level Verification                     | 77         |

|   | <u>د ۵</u>              | 5.1.3  | Symbolic Execution                           | 78         |

|   | 5.2                     |        | RACK-3 Verification                          | 79         |

|   |                         | 5.2.1  | Phase Level                                  | 79         |

|   |                         | 5.2.2  |                                              | 87         |

|   | F ~                     | 5.2.3  | Completing the Proof                         | 95         |

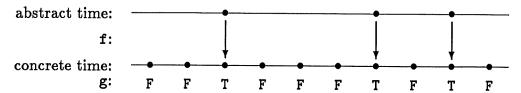

|   | 5.3                     | Synchi | ronizing Multiple Levels of Timing           | 99         |

| 6            | Embadding Other Notations |                           |                                            |   |   |   |     |   |     |   |   |     | 106 |     |

|--------------|---------------------------|---------------------------|--------------------------------------------|---|---|---|-----|---|-----|---|---|-----|-----|-----|

| O            |                           | Embedding Other Notations |                                            |   |   |   |     |   |     |   |   |     |     |     |

|              | 6.1                       |                           | cation Using Temporal Logic Operators      |   |   |   |     |   |     |   |   |     |     | 106 |

|              | 6.2                       |                           | oral Logic in Higher-Order Logic           |   |   |   |     |   |     |   |   |     |     |     |

|              | 6.3                       |                           | and Receiver Specifications                |   |   |   |     |   |     |   |   |     |     | 109 |

|              | 6.4                       | 3.4 Memory Specification  |                                            |   |   |   |     |   |     |   |   |     |     | 110 |

|              | 6.5                       | Verification              |                                            |   |   |   |     |   |     |   |   |     | 113 |     |

|              |                           | 6.5.1                     | Phase Level                                |   |   |   |     |   |     |   |   |     |     | 114 |

|              |                           | 6.5.2                     | Implementation of the Sender Specification |   |   |   |     |   |     |   |   |     |     | 114 |

|              |                           | 6.5.3                     | Collapsing Repeat-Loops to Single Steps    |   |   |   |     |   |     |   |   |     |     | 114 |

|              |                           | 6.5.4                     | Symbolic Execution                         |   |   |   |     |   |     |   |   |     |     |     |

|              |                           | 6.5.5                     | Top Level Correctness Statement            |   |   |   |     |   |     |   |   |     |     |     |

| 7            | Summary                   |                           |                                            |   |   |   |     |   |     |   |   | 118 |     |     |

|              | 7.1                       | What Has Been Proved?     |                                            |   |   |   |     |   | 118 |   |   |     |     |     |

|              | 7.2                       |                           |                                            |   |   |   |     |   |     |   |   |     |     |     |

|              |                           | 7.2.1                     | Lower Levels                               |   |   |   |     |   |     |   |   |     |     |     |

|              |                           | 7.2.2                     | Higher Levels                              |   |   |   |     |   |     |   |   |     |     |     |

|              | 7.3                       | Puttin                    | g Formal Specifications to Work            |   |   |   |     |   |     |   |   |     |     |     |

|              | •••                       | 7.3.1                     | A Fabricated TAMARACK-1 Microchip          |   |   |   |     |   |     |   |   |     |     |     |

|              |                           | 7.3.2                     | Silicon Compiler Interface                 |   |   |   |     |   |     |   |   |     |     |     |

|              | 7.4                       |                           |                                            |   |   |   |     |   |     |   |   |     |     |     |

|              | 1.4                       | Conch                     | ısion                                      | • | ٠ | • | • • | • | •   | • | • | •   | • • | 125 |

| $\mathbf{R}$ | efere                     | nces                      |                                            |   |   |   |     |   |     |   |   |     |     | 126 |

| $\mathbf{A}$ | Apı                       | pendix                    | : Compiler Verification                    |   |   |   |     |   |     |   |   |     |     | 138 |

# Introduction

Life-critical systems are increasingly dominated by microprocessor-based electronics. To increase confidence in the design of these systems, we describe methods based on formal proof and mechanical proof-generation which can be used to link multiple levels of software and hardware description into a chain of logical dependencies.

To demonstrate the use of these methods, we have designed and verified a complete system consisting of a compiler for a hierarchically structured programming language and a microprocessor which executes code generated by this compiler. The formal proof yields a precise and rigorously established link between the formal semantics of the programming language and the execution of compiled code by a model of the hardware. The formal proof also links the hardware model to the behavioural specification of an asynchronous interface to external devices, e.g., off-chip memory, a sensor or actuator in a real-time control system.

Higher-order logic provides a single unifying framework for reasoning about diverse aspects of software and hardware description. The expressiveness of this formalism supports several powerful techniques including the use of generic specification and the ability to embed natural notations from other formalisms such as temporal logic and denotational description.

## 1.1 Motivation

Methods for reliable design encompass a large part of computer engineering, and indeed, systems engineering. The purpose of these methods is to ensure that designs meet very high standards of reliability. For instance, the FAA (Federal Aviation Administration) requires the probability of catastrophic failure to be less than 10<sup>-9</sup> per 10-hour flight for a life-critical civil aviation flight control system. The reliability of these systems is vital in highly integrated systems such as the fly-by-wire flight control system of the Airbus 320 in which almost all of the mechanical and hydraulic controls in the flight deck have been replaced by microprocessor-based electronics.

There are two main approaches for achieving reliability [125]. One approach is fault tolerance which is concerned with building mechanisms into a design to cope with faults when they occur, e.g., component failure. The other approach is design error exclusion which seeks to exclude design errors to the maximum extent possible.

Conventional methods for both fault tolerance and design error exclusion have serious limitations. For instance, recent studies [92] have shown that diverse redundancy may be less effective as a measure for fault tolerance than previously thought. Design error exclusion techniques based on manual verification and validation can expose errors but non-exhaustive methods cannot possibly guarantee that a non-trivial design is free from errors.

A very different approach to design error exclusion is the use of formal proof to increase confidence in the reliability of a design. In particular, these methods can be used to show that a design is free from errors to the extent that formal descriptions of the design and its requirements are related by a formal proof.

## 1.2 Problem Definition

In this dissertation, we consider the use of formal proof as a design error exclusion technique in the design of microprocessor-based systems. These systems typically consist of embedded software running on one or more dedicated microprocessors. They are conceptually organized into multi-layered 'stacks' of software and hardware levels. A reliable design must ensure that the internal design of each layer satisfies its external design and that the external design of each layer fits properly into the stack.

We address the specific problem of building a verified stack<sup>1</sup> in which layers of this stack are linked together by formal proof to form a chain of logical dependencies from software levels down to a formal description of the hardware in terms of elementary components.

The feasibility of building verified stacks for realistic applications has already been demonstrated by a team of researchers at Computational Logic, Inc., [6,7]. Our efforts are based on a much simpler example of a verified stack, but we have dealt with many of the same basic problems. By working on a simpler example and using a more expressive formalism, we have had a greater degree of freedom to explore different approaches to solving some of these basic problems.

From these investigations, we are able to contribute some novel ideas on building verified systems. Our methods rely upon the expressive power of higher-order logic, but they are general enough to use in other formalisms of similar expressive power. Complementary work by Cohn [29,30,31] on verifying the commercially-available VIPER microprocessor (also using higher-order logic and many of same basic proof techniques) suggests that our methods could be scaled upwards to the complexity of a real system.

## 1.3 Main Ideas

This section outlines the main ideas which underlie our approach to verifying multilayered stacks beginning with a brief overview of these main ideas.

#### 1.3.1 Overview

Generic specification plays a dominant role in this dissertation. This is similar in concept to the 'generic mechanism' of the Ada<sup>2</sup> programming language which allows a subprogram or package to be parameterized by types and subprograms as well as values and objects [4]. In programming, this is a powerful technique for reliable re-use of software [51]. In the context of formal proof, genericity offers several more advantages in addition to re-usability. It can be used to filter out non-essential detail from

<sup>&</sup>lt;sup>1</sup>The term 'verified stack' is due to researchers at Computational Logic, Inc., [6,7].

<sup>&</sup>lt;sup>2</sup>Ada is a registered trademark of the U.S. Government - Ada Joint Program Office.

formal descriptions at each level in a design hierarchy. It also reduces the amount of special-purpose infrastructure needed to reason about particular application areas, e.g., hardware-oriented data types. While some formalisms have a built-in facility for generic specification as a primitive construct [52,142], we show how generic specifications can be created in higher-order logic with existing constructs. The key mechanisms for implementing genericity are parameterized specifications and the use of uninterpreted data types and uninterpreted primitives in place of defined data types and defined symbols.

Another important idea is the use of a single unifying framework. This is essential to avoid semantic gaps between different areas of formal description and formal reasoning. However, there is a fundamental difference of style in how a single unifying framework should be used to reason about a multi-layered stack of software and hardware layers. One approach is to re-cast diverse forms of description in one basic mold. The other approach, which we recommend, is to embed natural notations from well-established formalisms such as temporal logic and denotational description. We benefit from the built-in economy of these special-purpose notations when they are applied to particular areas of formal description.

To ensure that formal descriptions fit neatly into a wider context, we emphasize the importance of writing specifications which translate easily into established notations. At hardware levels, these established notations may be machine-readable languages such as VHDL or other conventional forms of description such as timing diagrams for interface protocols. At software levels, these established notations are mainly the natural notations of well-established formalisms such as Hoare logic and denotational semantics.

Finally, we believe that it is necessary, for all practical purposes, to use a formalism with (at least) the expressive power of higher-order logic to support the above recommendations. We also argue that the primary role of mechanical proof-generation is to support the intelligent participation of a human verifier in the rigorous analysis of a design at a level which supports clear thinking.

## 1.3.2 Structured Computer Organization

The structured view of a computing system as a multi-layered stack is well established in computer science and computer engineering. An early example of this concept and its usefulness was the invention of microprogramming by Wilkes in 1951 [71]. The eventual result was a drastic reduction in the complexity of the hardware which was important in the days of vacuum tube electronics. In a modern computing system, the number of levels has grown to typically include [136]:

- Problem-oriented languages

- Assembly languages

- Operating system machine

- Conventional machine

- Microprogramming

- Digital logic

Each of these levels can be thought of as a hypothetical or virtual machine which provides a complete model of computation. For instance, programs can be written in a problem-oriented language such as Ada without knowing anything about lower levels. One of the main reasons for imposing this structure on a computing system is to control the complexity of its design: each level is implemented with facilities provided by the next lower level. Another important reason for imposing this structure is to give greater independence to each layer: ideally, an Ada program should have the same result on different machines and similarly, a machine language program should have the same result on two different implementations of a particular machine architecture.

There are many ways in which this structured view of a computing system can be expanded to reveal details in specialized areas of interest. For example:

- Network models, such as the ISO Reference Model<sup>3</sup>, can be structured into distinct layers [135,145].

- Operating systems are designed as a series of layers extending outwards from the operating system nucleus to the user level [95].

- Compilers are usually divided into a number of layers or *phases* sometimes involving intermediate languages [1].

- Architectural descriptions of a microprocessor can be presented as a hierarchy of interpretation levels which link the semantics of the instruction set to the operation of basic logic components [2].

- Instruction processing is overlapped in a pipelined microprocessor by organizing the internal architecture into several stages [91].

In many cases, the discovery or invention of layers in a complex design is based on well-conceived abstractions. For instance, Zimmerman [145] describes principles used to decide upon the seven layers of the ISO Reference Model for computer networks. Anceau [2] describes principles for the introduction of new interpretation levels in the context of microprocessor design. Katevenis [91] describes the use of extra hardware in pipelined microprocessors for managing special conditions (e.g., internal forwarding) to support higher level views of how instructions are concurrently processed by the hardware.

The fact that well-conceived abstractions are involved is significant when formal methods are employed to reason about multi-layered structures. A clean separation between abstraction levels will mean fewer special cases to consider in the formal proof and fewer ad hoc assumptions in the resulting correctness theorems.

We also suggest that formal methods may be used in the design process itself to demonstrate that the discovery or invention of a new layer is indeed based on a well-conceived abstraction. Birtwistle [9], Davie [40], Fourman [47,48], Hanna [69], Milne [105] and others have also suggested that formal verification may play a useful role in a verification-driven approach to design.

<sup>&</sup>lt;sup>3</sup> International Standards Organization OSI (Open Systems Interconnection) Reference Model.

## 1.3.3 Totally Verified Systems

The idea of using logic to reason about computer programs and computer hardware is also well established in computer science and computer engineering. The use of Boolean logic as a descriptive method for logic circuits is due mainly to Shannon in the 1930's. In the 1960's, pioneering work on the application of logic to software was done by Floyd, Hoare, Landin, McCarthy, Scott, Stratchey and others. The use of logic to verify compilers and language implementations also began in the 1960's with work by McCarthy and Painter.

This early work was generally concerned with small fragments or single layers. However, the idea of a *totally verified system*, that is, the application of logic to every layer in a computing system was described as early as 1969 in a seminal paper by Hoare [75]:

When the correctness of a program, its compiler, and the hardware of the computer have all been established with mathematical certainty, it will be possible to place great reliance on the results of the program, and predict their properties with a confidence limited only by the reliability of the electronics.

The idea of a verified stack provides a strategy for building totally verified systems. Just as the structured view of a computing system controls the complexity of its design, a structured view is also the chief means of controlling the complexity of its formal verification. In the horizontal dimension, correctness results are established for the internal design of each layer with respect to its external design. In the vertical dimension, the external design of every layer is linked together to form a chain of logical dependencies from the highest level of formal description down to the lowest level of formal description.

## 1.3.4 Generic Specification

Generic description is a powerful concept in high level language design. For instance, the 'generic mechanism' of Ada allows a subprogram or package to be parameterized by types and subprograms as well as values and objects. This feature supports fundamental principles of modularity and abstraction as well as provides a convenient mechanism for the reliable re-use of software. Generic description is also a powerful concept in the context of formal proof where modularity, abstraction and re-usability are highly desirable attributes.

In addition to these well-known advantages, generic description can be used in a formal proof to filter out non-essential detail - a modern-day Occam's razor. In the case of verifying a multi-layered stack of software and hardware levels, this use of generic specification is particularly important as a mechanism for enforcing a sharp distinction between what has and what has not been formally considered in the proof.

Each layer in a multi-layered stack is a virtual machine described in terms of operations performed on data. When verifying that the internal design of a particular layer correctly implements its external design, the precise nature of these operations often

<sup>&</sup>lt;sup>4</sup>The principle that the fewest possible assumptions are to be made in explaining an idea [William of Occam, English philosopher, died *circa* 1350].

turns out to be irrelevant. In such cases, defined symbols are only being used as place-holders in the correctness proof. To make it clear when a symbol is just a place-holder, we use uninterpreted primitives in place of defined symbols. For similar reasons, we use uninterpreted data types in place of defined data types.

We argue in this dissertation that verifying the internal design of individual layers is a highly localized concern which should be separated as much as possible from detail only relevant to other levels of proof. In this approach, uninterpreted primitives and uninterpreted data types only become defined when they are linked into the verified stack. This contrasts with the *closed-world* approach to formal verification where every operator and every data type is completely defined within each level.

In addition to forcing a sharp distinction between what has and what has not been formally considered at each level in a verified stack, the use of generic specification avoids much of the infra-structure required in the closed-world approach for reasoning about particular areas of application, e.g., hardware-oriented data types. Because less infra-structure is required, it is easier to reproduce correctness proofs in other formalisms which lack this infra-structure.

The primary example of generic specification in this dissertation is the formal specification of a simple microprocessor called TAMARACK-3. The basic data types and primitive data operations used in the formal specification are uninterpreted data types and uninterpreted primitives respectively.

A second example of generic specification is the specification of a behavioural model for an asynchronous memory device. We first specify a generic model which captures the essential features of how the memory device responds to a memory request and then instantiate this generic model with non-essential details. In addition to achieving a more readable specification, the generic model could be re-used for other external devices such as sensors and actuators in a real-time control system.

A third example, reported elsewhere [81], is the generic specification of a regular structure. For a large regular structure, e.g., the 31Kbit microcode ROM of the MC68000 [2], some form of genericity is essential for controlling the complexity of its structural description. This form of genericity can also be viewed as a synthesis algorithm [87].

## 1.3.5 Embedding Other Notation

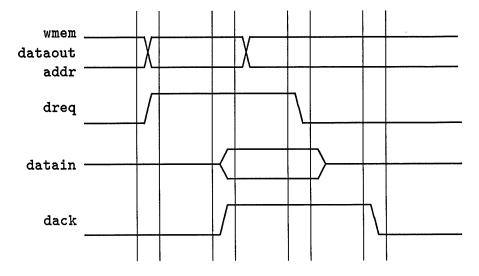

A concise and meaningful specification often depends on the right choice of notation. This fact was made vividly clear during the course of our research by experimenting with different ways to specify the TAMARACK-3 memory interface which is based on a four-phase handshaking protocol.

Our first attempt (reported elsewhere [82]) used explicit time variables without the introduction of any special notation. For instance, existential quantification was used to specify the unknown length of wait states in a handshaking sequence. This first attempt achieved some of our goals, in particular, the goal of giving an independent specification for external memory (as a physically separate device). However, the specifications were cumbersome and not intuitively clear. When presenting this work, we often resorted to replacing parts of the specification with natural language phrases so that the specification might be understood. The formalization also failed to cleanly separate constraints

1.3. Main Ideas

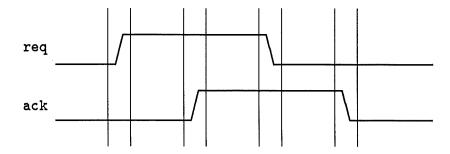

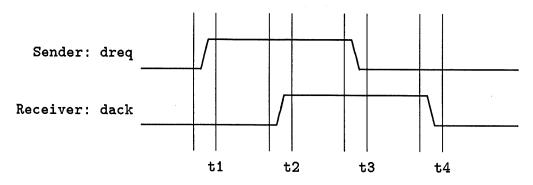

Figure 1.1: Simplified Handshaking Timing Diagram

on the handshaking signals from constraints on the accompanying data signals.

Our second attempt (and the one used in our verified stack) is based on the notation of temporal logic. The idea of using temporal logic to specify handshaking protocols had already been described by several people including Bochman [11], Dill and Clarke [44], and Fujita et al. [49]. The idea of embedding other calculi in higher-order logic had been demonstrated by Gordon [61] (for program logics) and by Hale [65] (for another form of temporal logic). The combined influence of these ideas lead us to experiment with temporal logic by defining some temporal logic operators as higher-order functions. The outcome of this experiment was far superior to our earlier attempt: the formal specifications were intuitively clear and concise. Moreover, the proof of correctness was easier and more general.

To elaborate on this point, Figure 1.1 shows a timing diagram typically found in conventional descriptions of constraints on a pair of handshaking signals, req ("request") and ack ("acknowledge"), used to synchronize data transfers between a microprocessor and an external device such as a memory chip.

The corresponding description in formal notation is given by the following set of temporal logic assertions which express constraints on the pair of handshaking signals. Although these assertions involve symbols with precise mathematical meanings (in the context of formal proof), they can be informally translated into natural language by reading the operators  $\sim$ ,  $\diamondsuit$ ,  $\longrightarrow$  and  $\cup$  as "not", "eventually", "implies" and "until".

```

\begin{array}{l} (\text{req} \; \longrightarrow \; (\text{req} \; \cup \; \text{ack})) \\ (\text{req} \; \longrightarrow \; (\diamondsuit \text{ack})) \\ (\text{ack} \; \longrightarrow \; (\text{ack} \; \cup \; (\sim \text{req}))) \\ (\text{ack} \; \longrightarrow \; (\diamondsuit (\sim \text{req}))) \\ ((\sim \text{req}) \; \longrightarrow \; ((\sim \text{req}) \; \cup \; (\sim \text{ack}))) \\ ((\sim \text{req}) \; \longrightarrow \; (\diamondsuit (\sim \text{ack}))) \\ ((\sim \text{ack}) \; \longrightarrow \; ((\sim \text{ack}) \; \cup \; \text{req})) \\ ((\sim \text{ack}) \; \longrightarrow \; (\diamondsuit \text{req})) \end{array}

```

For example, the assertion,

```

(req \longrightarrow (req \cup ack))

```

1.3. Main Ideas

expresses the constraint that when req is true, then it must remain true until ack becomes true. In other words, once a request has been initiated, the request must continue until it is acknowledged. The remaining seven assertions are explained in Chapter 6.

In addition to using the notation of temporal logic to specify the asynchronous memory interface, we have used the specialized notation of denotational description [53] to specify the semantics of a structured programming language at the top of our verified stack. In a conventional framework, the semantic clause

$$\mathcal{C}[\![\mathtt{C1};\mathtt{C2}]\!] = \mathcal{C}[\![\mathtt{C1}]\!] \circ \mathcal{C}[\![\mathtt{C2}]\!]$$

would be used to give the denotation (or mathematical meaning) of a command sequence C1;C2 where the semantic function  $\mathcal{C}$  is applied to syntactic objects surrounded by emphatic brackets  $[\![$  and  $]\![$ . We are able to closely imitate this style using relations instead of partial functions.<sup>5</sup>

From this and similar experiences, we believe that natural notations from well-established formalisms such as temporal logic and denotational description are valuable for specifying and reasoning about the diverse aspects of structure and behaviour in a microprocessor-based system. The ability to represent different notations in a single unified framework is one of the more essential uses of higher-order logic in our work. In addition to Gordon and Hale, several others including Camilleri [21] and Loewenstein [96] have also reported benefits of embedding other calculi in the framework of higher-order logic.

#### 1.3.6 Established Notations

At the hardware level, designers use a variety of established notations for diverse aspects of structure and behaviour. Some of these notations, such as a conventional hardware description language, are machine-readable. Other forms of conventional description are not necessarily machine-readable, for instance, they could be pictorial representations of block structure and memory interface timing diagrams.

To be understood in a wider context, formal descriptions must translate easily into these established notations. In some cases, it may be possible to mechanically translate a formal description into an established notation. In other cases, this translation is more informal, e.g., understanding a set of temporal logic assertions in relation to a memory interface timing diagram. In either case, the correspondence between a formal description and the same description in an established notation should be plainly seen with only a minimum of explanation.

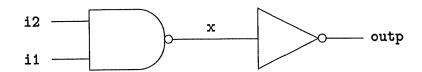

One area of formal description suitable for mechanical translation is the structural description of hardware. For example, Figure 1.2 shows the implementation of an AND-gate by a NAND-gate and NOT-gate.

In higher-order logic, the structure of this implementation is described by the following equation:

ANDGate (i1,i2,outp) =

$$\exists x$$

. NANDGate (i1,i2,x)  $\land$  NOTGate (x,outp)

<sup>&</sup>lt;sup>5</sup>Gordon has also used higher-order logic to represent a denotational semantics in a similar style [61].

Figure 1.2: AND-Gate Implementation

In VHDL<sup>6</sup> this same structure is described by the following declarations:

```

entity ANDGate is

port (i1,i2:in Bit;outp:out Bit);

end ANDGate;

architecture Structure of ANDGate is

component NOTGate port (i:in Bit;outp:out Bit);

component NANDGate port (i1,i2:in Bit;outp:out Bit);

signal x : Bit;

G1: NANDGate port map (i1,i2,x);

G2: NOTGate port map (x,outp);

end Structure;

```

The syntactic differences between these two descriptions are mostly superficial. The VHDL declarations contain more keywords and use longer identifiers for keywords, e.g., the symbol  $\exists$  corresponds to the keyword signal. The VHDL declarations also involve a full set of type declarations. The higher-order logic description could also be annotated with type declarations but normally this additional information is implied by context.

Overlooking minor differences of syntax, the close correspondence between formal and conventional forms of descriptions is not surprising. Both are based on the same fundamental style for describing hierarchical structure. Systems (or devices) at all levels are viewed externally as 'black boxes' connected to the external environment though a set of labelled ports, e.g., i1, i2 and outp. Internally, they are decomposed into a set of components, e.g., NANDGate and NOTGate and internal signals, e.g., x. Internal connections are indicated by ports with common labels, e.g., the internal signal x connects the output of the NAND-gate to the input of the NOT-gate.

In general, this correspondence between higher-order logic and established notations like VHDL scales upwards for 'bigger' cases of structural description. This correspondence has been demonstrated by Van Tassel in the (mostly) mechanical translation of a VHDL specification for an earlier version of the TAMARACK-3 microprocessor into a HOL specification [140,141]. Many other formal description languages besides higher-order logic can also be used to write similar descriptions of structure which easily translate into established notations.

Other forms of conventional description are not necessarily machine-readable. For instance, asynchronous interactions between a microprocessor and external devices are

<sup>&</sup>lt;sup>6</sup>VHDL is the VHSIC (Very High Speed Integrated Circuit) Hardware Description Language now adopted as an IEEE standard (Std 1076-1987) [3].

usually described by a mixture of natural language, flowcharts and timing diagrams. Here, we are using the term 'established notations' in a very loose sense to refer to this mixture of descriptions: though informal, they generally conform to standard conventions of style.

In this case, we have aimed to write formal descriptions which can be understood in relation to conventional forms of description with a minimum of explanation. Earlier, we described how a set of temporal logic assertions can be informally translated into a natural language description which directly corresponds to the timing diagram in Figure 1.1 Hence, natural notations such as temporal logic, besides offering the advantage of built-in economy, can also be successful as machine-readable versions of established notations such as flowcharts and timing diagrams.

## 1.4 The TAMARACK Stack

The verified stack described in this dissertation is based on a compiler for a very simple programming language called IMP and a very simple microprocessor called TAMARACK-3. The compiler and the microprocessor are both organized into a series of layers. The complete stack (for the purposes of this dissertation) is shown in Figure 1.3.

- Compiler

- IMP language (hierarchically structured)

- SM code (flat intermediate form)

- TM code (target machine)

- Microprocessor

- programming level

- microprogramming level

- phase level (register-transfer level structure)

Figure 1.3: The TAMARACK Stack

This stack can be extended both upwards and downwards. A paper by Gordon [61] shows how to extend this stack upwards by deriving Hoare proof rules for reasoning about IMP programs from a denotational semantics similar to one we have given for IMP. In work reported elsewhere [80,81,84,87,88], we have extended this stack downwards to the transistor level for an earlier version of the TAMARACK-3 microprocessor. In collaboration with researchers at SRI (Menlo Park), we have also begun to consider how to bridge the semantic gap between the bottom layer in the TAMARACK stack and the engineering models used to describe components in the library of a commercial silicon compiler [89].

## 1.4.1 A Very Simple Compiler

The IMP programming language is a hierarchically structured language with only a few basic constructs, e.g., expressions, assignment statements, while-loops. A semantics for this language is given in a typical denotational style by semantic functions which satisfy a set of semantics clauses. The main difference from the semantics given for IMP by Gordon [61] is the use of modular arithmetic to model the finite size of machine words and memory.

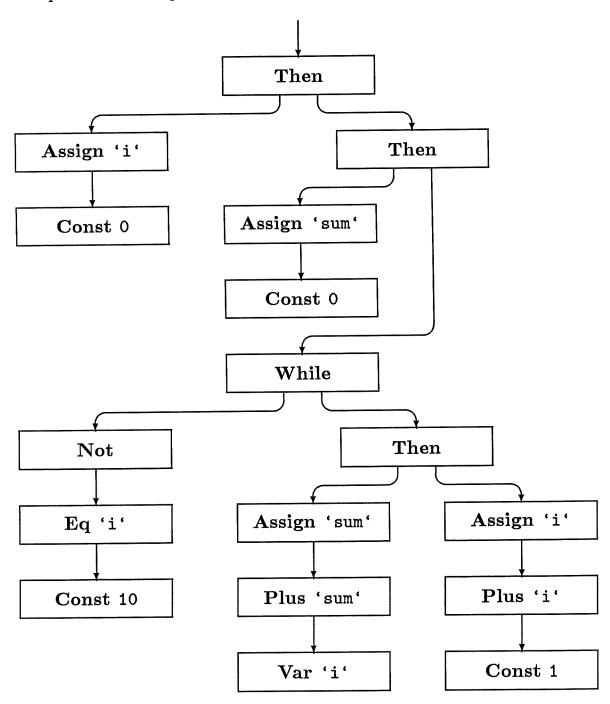

The compiler for this language is implemented by two layers or 'phases'. The first phase compiles the hierarchically structured program into a flat intermediate form called SM (Simple Machine) code. The second phase assembles SM code into TM (Target Machine) code. These two compilation phases are shown in Figure 1.4 where a simple IMP program is first compiled into SM and then assembled into TM. Operational semantics are given for both SM code and TM code.

The semantics and compiler for IMP are not parameterized to the same extent as the underlying hardware model. This is partly because this represents an earlier stage in our research and partly because a few more computational details are needed to verify the compiler. Nevertheless, the compiler specification is parameterized by the number of bits in a full-size word and, indirectly, by the size of memory.

This part of the verified stack is described in a separate paper included as an appendix to this dissertation; the paper is based on a technical report [85] which gives full details of the compiler and its formal verification. Both the paper and technical report are based on an earlier version of TAMARACK-3 but only slight modifications were needed to adapt this work to the current version of the hardware.

## 1.4.2 A Very Simple Microprocessor

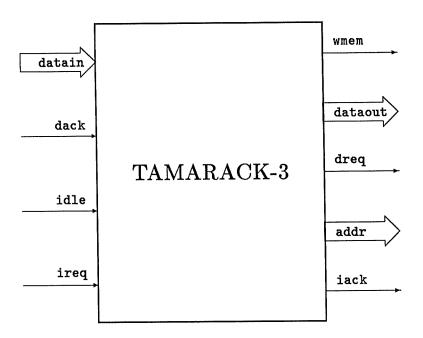

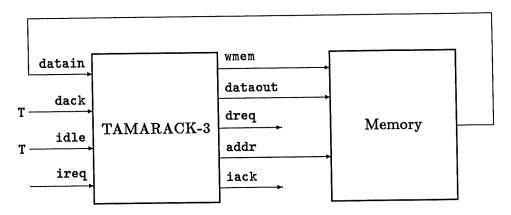

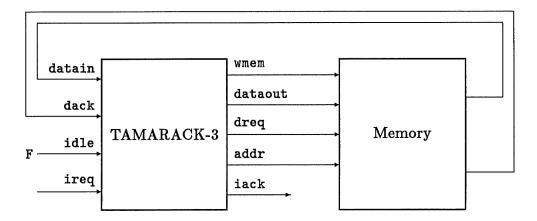

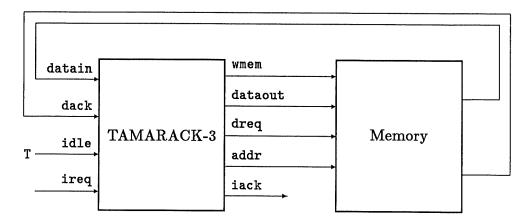

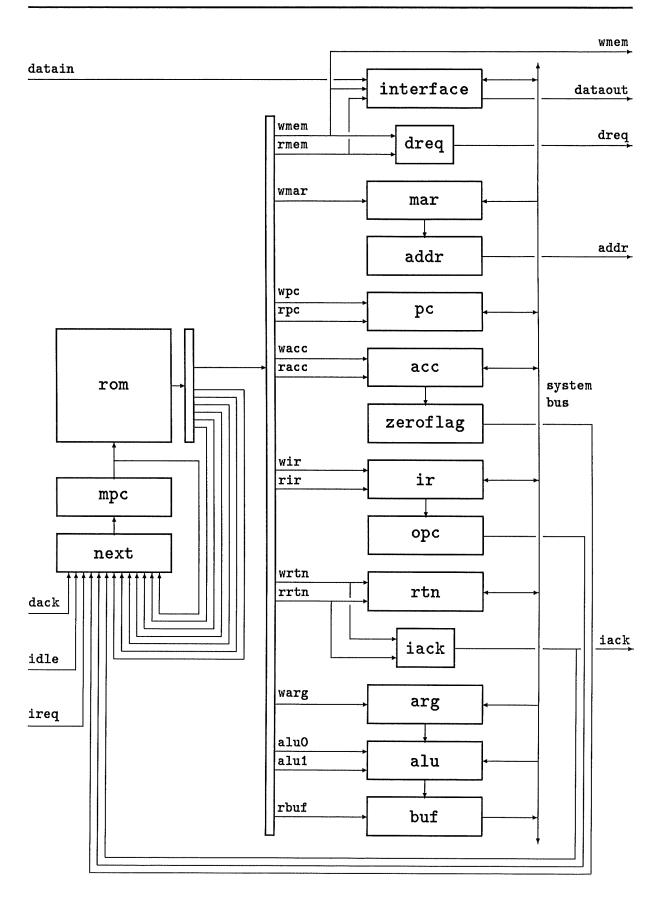

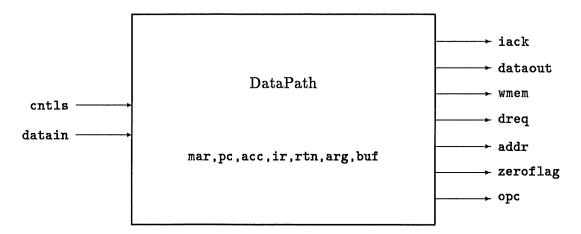

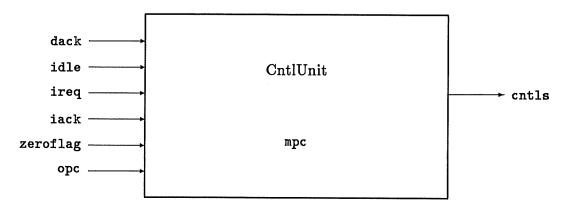

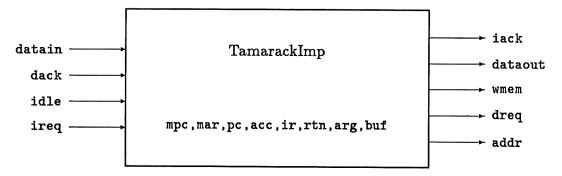

The main emphasis in this dissertation is on the TAMARACK-3 microprocessor which occupies the bottom half of this verified stack. This microprocessor has eight programming level instructions and a single addressing mode. The only kind of hardware exception is a single level, non-vectored hardware interrupt. The microprocessor can be interfaced to external memory to operate in one of three possible modes: fully synchronous, fully asynchronous, and extended cycle mode. All I/0 is memory-mapped. Figure 1.5 shows a functional diagram for the externally available signals of TAMARACK-3 (excluding clock signals, reset signal and voltage sources). These signals would be pins or groups of pins in a microchip implementation of this design.

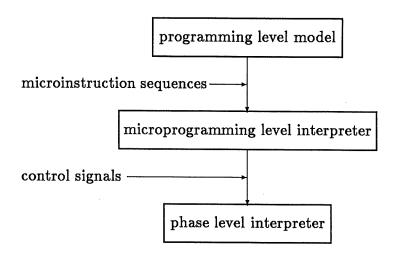

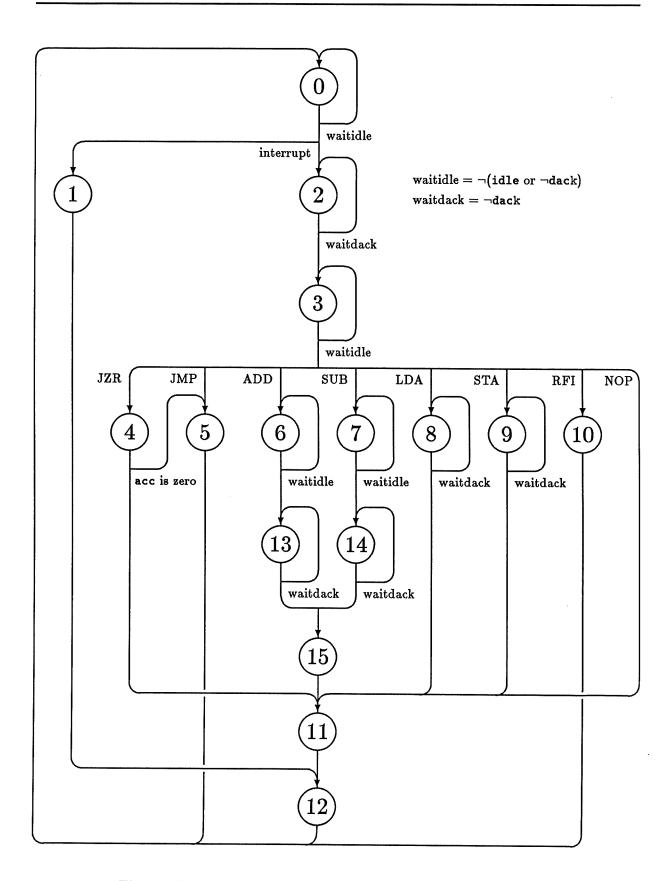

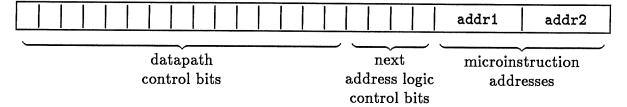

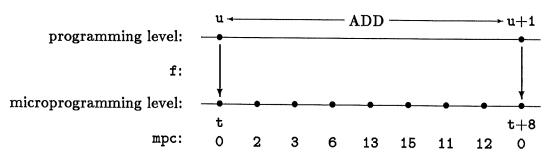

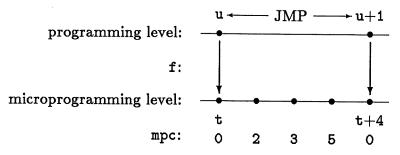

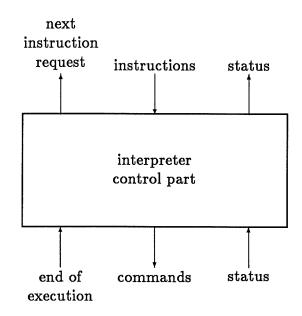

As we have shown in Figure 1.3, the microprocessor part of the verified stack is separated into three layers. The programming level model is a description of its operation as seen by a machine language programmer. This includes both the instruction set semantics and the processing of interrupts. The next layer down is the microprogramming level which describes the sequential execution of microcode. The phase level, at the very bottom of the verified stack, reveals the structural organization of the internal architecture in terms of register-transfer level components.

The original version of this simple microprocessor was described by Gordon [55,58]

<sup>&</sup>lt;sup>7</sup>A compiler phase is an entirely different idea than the phase level of the microprocessor architecture. Both uses of the term 'phase' are standard terminology [1,2].

```

base:

(LDA n (base+2))

(JMP n (base+3))

(O MOD 2^{n+3})

base+3:

(STA n (symtab 'i'))

base+4:

(LDA n (base+6))

(JMP n (base+7))

(0 MOD 2^{n+3})

base+7:

(STA n (symtab 'sum'))

base+8:

(LDA n (base+10))

i := 0;

(JMP n (base+11))

sum := 0;

(10 MOD 2^{n+3})

while not (i = 10) do

(SUB n (symtab 'i'))

base+11:

sum := sum + i;

(JZR n (base+16))

i := i + 1

(LDA n (base+15))

(JMP n (base+16))

1

base+16: (JZR n (base+20))

base:

('CONST', ARB, O)

(LDA n (base+19))

('STA','i',ARB)

(JMP n (base+23))

('CONST', ARB, O)

('STA', 'sum', ARB)

(LDA n (base+22))

base+4:

('CONST', ARB, 10)

(JMP n (base+23))

('EQ','i',ARB)

('NOT', ARB, ARB)

base+23:

(JZR n (base+27))

('NOT', ARB, ARB)

(LDA n (base+26))

('JZR',ARB,base+16)

(JMP n (base+30))

('LDA', 'i', ARB)

0

('ADD', 'sum', ARB)

(LDA n (base+29))

('STA', 'sum', ARB)

(JMP n (base+30))

('CONST', ARB, 1)

('ADD', 'i', ARB)

(JZR n (base+40))

base+30:

('STA', 'i', ARB)

(LDA n (symtab 'i'))

base+31:

('JMP', ARB, base+4)

base+32:

(ADD n (symtab 'sum'))

base+16:

(STA n (symtab 'sum'))

base+33:

base+34:

(LDA n (base+36))

(JMP n (base+37))

(1 \text{ MOD } 2^{n+3})

base+37:

(ADD n (symtab 'i'))

base+38:

(STA n (symtab 'i'))

base+39:

(JMP n (base+8))

base+40:

```

Figure 1.4: Two Phase Compilation of an IMP Program

- read/write select - data from memory wmem datain - data to memory dack - data acknowledge dataout - data request idle - extended cycle mode dreq - address to memory - interrupt request addr ireq - interrupt acknowledge iack

Figure 1.5: Functional View of the TAMARACK-3 Microprocessor.

for a predecessor of the HOL system called LCF\_LSM [57]. This example was re-done in HOL, implemented as a CMOS microchip (as an exercise in verification-driven design), and given the name TAMARACK-1 [78,79,88]. The design was then streamlined in TAMARACK-2 by eliminating some non-essential control features (and used as the target machine for an earlier version of the IMP compiler described in [85]). The version described here, TAMARACK-3, is distinguished from earlier designs by the addition of a hardware interrupt mechanism and the ability to interact asynchronously with external devices using handshaking signals.

Because TAMARACK-3 was designed as a verification example, it is not seriously intended for practical applications.<sup>8</sup> We have deliberately avoided some forms of complexity found in 'real designs' which do not necessarily contribute interesting verification problems aside from the very important problem of managing the sheer size of such proofs. For instance, multiple addressing modes are not provided because the problem of establishing correctness results for a particular instruction in different addressing modes is largely a matter of repeating the same proof strategy with slight variations for each case (as Cohn [30] has reported for the verification of the commercially-available VIPER microprocessor).

Although we have purged as much repetitious complexity as possible from the design of TAMARACK-3, the formal verification of this design is *not* a trivial problem. In place of repetitious complexity, we have introduced features which give rise to some intrinsically complex verification problems. In particular, the use of handshaking signals for data exchanges with external memory has lead us to consider the problem of reasoning about asynchronous interactions between a microprocessor system and external devices. By avoiding repetitious complexity, we have been left with a great deal of flexibility to consider different approaches to this particular problem, and more generally, to consider different strategies and techniques for structuring a formal proof into several layers.

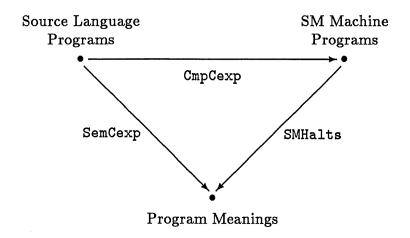

## 1.4.3 Linking the Compiler to the Microprocessor

The target machine of the IMP compiler is an instance of the generic TAMARACK-3 programming level model. The latter is more general partly because uninterpreted data types and uninterpreted primitives are used in the formal specification of TAMARACK-3 in place of defined data types and defined symbols. To link the top part of the verified stack with the bottom part, an instance of the TAMARACK-3 programming level model is created to satisfy the specification of the target machine, i.e., the operational semantics of TM code.

This is partly achieved by associating defined data types and defined symbols mentioned in the IMP semantics with uninterpreted data types and uninterpreted primitives that appear in the formal specification of the TAMARACK-3 microprocessor. For example, the defined symbol +, used in combination with the modulus function to specify the semantics of an IMP plus-expression, is associated with an uninterpreted primitive called add which is used to specify the semantics of a TAMARACK-3 ADD instruction.

<sup>&</sup>lt;sup>8</sup>But with a few more ALU functions, more kinds of conditional branches, and an alternative to absolute addressing, it is possible to imagine the use of a TAMARACK-like microprocessor in a very simple real-time control application. As Turner et al. [138] remarked with regard to railroad signalling, "the most complex interlock arrangement requires a simple combination of Boolean and time-based sequential logic, all well within the capability of the arithmetic unit of a small microprocessor".

The TAMARACK-3 programming level model is also more general because normal program flow can be interrupted by an external interrupt request. Even though interrupts are fully supported in the bottom half of the verified stack, it is currently necessary to disable interrupts (by assuming that the interrupt request pin ireq is wired to 'ground') in order to link the compiler to the microprocessor. This limitation is due to the way that we have defined the semantics of the IMP language: it is not a limitation of the microprocessor verification. However, it should be possible in future work to allow interrupts by modifying the semantics of IMP either using a continuation semantics [53,132] (and thus, remaining in a denotational framework) or else using a structured, or Plotkin-style, operational semantics [117].

Establishing that the target machine of the IMP compiler is an instance of the TAMARACK-3 microprocessor is the main illustration in this dissertation of how individual layers dealing with widely separated concerns can be linked together to form a chain of dependencies from the highest level of formal description down to the lowest level of formal description.

#### 1.5 Related Work

Our higher-order logic approach is directly inspired by Gordon [59]. The idea of using higher-order logic to specify and reason about hardware was first advocated by Hanna [67]. This section describes other work related specifically to our main areas of interest: microprocessor verification, verified synthesis, compiler verification and verified systems. There is a great deal of important work by others in the more general area of verifying hardware; we mention some examples of this work elsewhere in this dissertation as it relates to specific points of interest.

## 1.5.1 Microprocessor Verification

Gordon's [58] verification of a simple computer using the LCF\_LSM system was an early example of how formal proof and mechanical proof-generation could be used to reason about the design of a microprocessor. In addition to our work on TAMARACK-3, Gordon's example has been used to illustrate several other approaches to animating and verifying microprocessor hardware. This includes work by Barrow [5], Camilleri [19,20], Curzon [39], Davie [40], Richards [121], Van Tassel [140,141], and Weise [143].

The diversity of structure and behaviour in a typical microprocessor provides a rich source of verification problems. Currently, the field of microprocessor verification is dominated by two main examples: Hunt's verification of FM8501 [76] and Cohn's verification of VIPER [29,30,31]. These two examples are widely seen as the current state-of-the-art in microprocessor verification. Hunt was the first to consider the problem of reasoning about the implementation of a handshaking protocol in a microprocessor system. The VIPER project shows how the design of a microprocessor can be subjected to formal analysis in a series of decreasingly abstract levels.

#### 1.5.1.1 FM8501

FM8501 is a 16-bit microprocessor similar in complexity to a PDP-11. The instruction set of this microprocessor is rich enough to support realistic applications.

The programming level model of FM8501 and its internal architecture are formally specified in pure Lisp. The Boyer-Moore theorem-prover [13] was used to generate a formal proof of correctness which bridged the gap between the semantics of the FM8501 instruction set and a gate-level description of its implementation.

A particularly interesting aspect of the FM8501 example is the asynchronous memory interface which uses handshaking signals to synchronize data exchanges between the microprocessor and external memory. In the absence of existential quantification (which is not provided in Boyer-Moore logic), Hunt used an oracle to 'guess' the length of wait states in handshaking interactions. The correctness proof established that the implementation of the microprocessor is correct for all possible oracles.

The FM8501 also served as a prototype for the FM8502 which occupies the bottom layer of the verified stack developed by researchers at Computational Logic, Inc. [6,7].

#### 1.5.1.2 VIPER

The other well-known state-of-the-art example is Cohn's [29,30,31] verification of the VIPER microprocessor. This commercially-available microprocessor was designed by the British Ministry of Defence for use in life-critical applications [36,37]. Cullyer, one of the designers of VIPER, produced an informal paper-and-pencil correctness proof which related the top-level specification to the next lower level of description called the 'major state machine'. This level of proof was then re-done by Cohn using the HOL system and later extended down to an even lower level of description called the 'block level description'.

The first level of proof showed that the major state machine, with corrections, faithfully implements the top level specification of VIPER. This level of proof was exclusively concerned with flow of control and not with arithmetic or logical computations.

The second level of proof dealt with the block level description of VIPER which directly relates to the circuit design. In addition to flow of control, this level of proof was concerned with arithmetic and logical computations performed by functional units. At the block level, the proof only considered the operation of VIPER under normal conditions. These conditions appear explicitly in the correctness results as stated assumptions. Under these conditions, a limited set of correctness results were obtained which "amount to an analysis of the block machine under all circumstances covered by the specification" [30]. One of the reasons that made it impractical to carry out a complete proof of the block level was the current lack of support in the HOL system for reasoning about bit-level operations.

A major source of complexity in the VIPER proof is the problem of managing the sheer size of the correctness proof for a real design. There are 120 sequences of major state transitions to consider and each of these is implemented by a sequence of minor state transitions. However, the verification task would have been much harder if not for the assumption (as a condition of normal operation) that every memory request is satisfied in a fixed and minimal number of clock cycles. Consequently, state transitions

<sup>&</sup>lt;sup>9</sup>Although the VIPER design supports other protocols, the high-level specification given by VIPER

in the top level specification correspond to a finite set of fixed sequences at lower levels.

A particularly interesting outcome of the VIPER project is that it revealed weaknesses in the links between designer, verifier and manufacturer. One problem faced by Cohn was to derive a formal description of the block level from a mixture of engineering documents, partly pictorial and partly textual, supplied by the VIPER designers. Errors were found in both the top level specification of VIPER and in the major state machine, but these errors were not propagated down to the fabricated chips. Drawing from this experience, Cohn has contributed a sound appreciation of the scope and limitations of using formal proof to verify microprocessor systems.

Cullyer [38] describes plans for using VIPER in a railroad signalling application which also involves use of the HOL system to verify software against a formalization of well-established rules of railroad signalling. Gordon [63] has proposed to verify a compiling algorithm for a structured assembly language called VISTA which is targetted to VIPER.

#### 1.5.1.3 Other Work

Crocker et al. [35] describe a re-verification of the FM8501 using SDVS (State Delta Verification System). The semantics of SDVS were well-suited to specifying the external memory as a separate process from the FM8501. In previous work, this group verified a microcoded packet switch called the C/30 used in the US Defense Data Network; however, this work is not yet publicly documented.

Another example of verifying an asynchronous memory interface is described by Sekar and Srivas [128]. Bickford and Srivas [8] have begun work on verifying a 3-stage instruction pipelined RISC processor with plans to eventually extend this example with interrupts and an asynchronous memory interface.

Herbert [72] verified a network interface chip in the Cambridge Fast Ring using both the LCF\_LSM and HOL systems. The formal description of this chip was mechanically generated from the designer's original specification written in Modula-2.

Narendran and Stillman [114] hand-translated the VHDL description of an image processing chip into first-order logic and used RRL (Rewrite Rule Laboratory) to generate correctness results. Formal verification revealed several errors unknown to the chip designers.

Birtwistle and Graham [10,64] describe work on formalizing the design of a functional language co-processor based on Landin's SECD machine. The formal verification is being undertaken in the HOL system with plans to verify a complete system based on the fabricated chip.

Bowen [12] has used Z, a specification language developed at Oxford University, to specify the entire MC6800 instruction set including interrupts and memory configurations.

Leonard [94] is investigating techniques for specifying computer architecture in higher-order logic. This work is particularly concerned with multi-processor systems which interact through shared memory. This work also considers techniques for mapping architectural specifications to implementations.

Rushby and von Henke [124] have used the SRI EHDM (Enhanced Hierarchical Design Methodology) system to verify the Interactive Convergence Clock Synchronization Al-

1.5. Related Work 21

gorithm of Lamport and Melliar-Smith. Clock synchronization is fundamental to fault tolerance mechanisms in life-critical systems implemented by a set of communicating microprocessors. This work demonstrated the value of mechanical proof-generation with the discovery of several technical flaws in previously published hand-proofs.

#### 1.5.2 Verified Synthesis

Early work on verified synthesis by Milne [104] proved the correctness of a very simple silicon compiler in a process algebra called CIRCAL.

May and Shepherd [130] used algebraic laws of the OCCAM programming language [122] to transform a high-level specification of the INMOS T800 Transputer floating-point unit into a microcode level description.

Martin et al. [97] have used synthesis techniques amenable to formal verification to generate the first entirely asynchronous (also called self-timed or delay-insensitive) microprocessor from a high-level specification based on CSP. The surprising robustness of the fabricated chips to variations in temperature and VDD voltage values [98] may also be significant for life-critical applications.

Brown and Leeser [15] describe work on compiling programs into application specific chips generating a microcoded controller and datapath as an intermediate stage in the synthesis process. The synthesis procedures are being developed using the NUPRL theorem-prover [34].

Brock and Hunt [14] describe techniques for verifying circuit generation functions formally specified by a list of constants in the Boyer-Moore logic [13]. They have verified a family of ALU's in the Boyer-Moore theorem prover using these techniques.

Fourman et al. [47,48] have combined CAD technology with a rule-manipulation system based on a higher-order polymorphic predicate calculus of partial terms. Their system, called LAMBDA, supports the interactive refinement of designs directed by the user through a graphical interface but constrained by the underlying logic.

Hanna et al. [69] use the VERITAS<sup>+</sup> system in a goal-directed manner to interactively generate a design and a correctness proof. The synthesized design is then translated into the MODEL hardware description language.

Johnson et al. [77] have considered the interplay between design verification and design synthesis. They have developed a transformation system DDD (Digital Design Derivation) based on functional algebra which has been used to reduce the FM8501 programming level model to a gate level description.

## 1.5.3 Compiler Verification

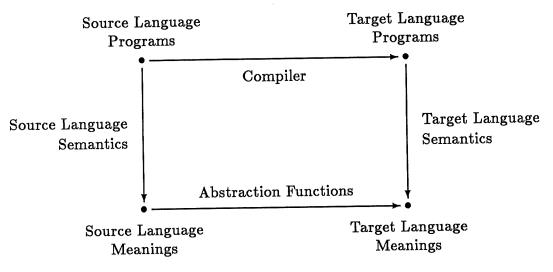

The earliest example of compiler correctness (that we are aware of) was described more than twenty years ago by McCarthy and Painter [99]. They verified an algorithm for compiling arithmetic expressions into code for an abstract machine. This early work established a paradigm for subsequent work on compiler correctness (as summarized by Cohn [28]):

- Abstract syntax.

- Idealized hardware.

1.5. Related Work 22

- Abstract specification of the compiler.

- Denotational source language semantics.

- Operational target machine semantics.

- Correctness stated as a relationship between the denotation of a program and the execution of its compiled form.

- Proofs by induction on the structure of source language expressions.

In a separate report [85], we give a detailed history of subsequent developments in this area. This includes work described by: Kaplan [90]; Burstall and Landin [17]; Milner and Weyhrauch [107]; Morris [110,111]; Chirica [24]; Milne and Strachey [106]; Goguen et al. [50]; Russell [126]; Cohn [28]; Polak [118,119]; Thatcher et al. [137]; Chirica and Martin [25]; Despeyroux [42] and Collier [33]. These developments include the use of algebraic methods and domain theory, more language features, verification by formal proof based on axioms and inference rules, mechanical assistance for proof-checking and proof-generation, and correctness proofs about parsing and syntax analysis.

## 1.5.4 Verified Systems

Most of the previous work on the compiler correctness problem is ten to twenty years old. This work has generally followed the paradigm laid down by McCarthy and Painter of distancing the problem from the details of real hardware by using a target machine with idealized features.

Since this early work, proof-generation systems have developed considerably and have been used to construct some very large proofs. These developments, combined with recent successes in the formal verification of microprocessors such as VIPER and FM8501, have revived interest in the compiler correctness problem and given it a greater relevance than before.

#### 1.5.4.1 The CLI Stack

The most remarkable achievement so far has been made by researchers [6,7] at Computational Logic, Inc. (CLI). The "short" version of the CLI stack consists of four layers:

Micro-Gypsy - a high level programming language [144] Piton - a high-level assembly language [109]

FM8502 - 32-bit microprocessor based on the FM8501 prototype

Gates - register-transfer level model of an implementation

Each layer in this stack is intended to support realistic applications. A small operating system called Kit has also been implemented and proven correct. However, this operating system does not fit precisely onto the "short" stack due to minor architectural differences.

In addition to the four main layers of the CLI stack, there are several minor layers. For instance, the assembly of Piton programs involves an intermediate form called i-code which provides an intermediate layer between Piton and FM8502.

A distinctive aspect of the CLI approach is that each layer in the stack is cast into the same basic mold: each layer is described as a finite-state machine defined by an interpreter function in pure Lisp. This contrasts with the approach described in this dissertation of using special-purpose notations from well-established formalisms such as temporal logic and denotational description. Another distinctive feature of the CLI approach is its adherence to the closed-world principle where every operator and every data type is completely defined within each layer. This contrasts with our use of generic specification to filter out non-essential detail from each layer of a multi-layered stack.

#### 1.5.4.2 The SAFEMOS Stack

Research is jointly underway at Cambridge University, INMOS, Oxford University and SRI International (Cambridge Research Centre) on a project to develop a prototype design and verification environment for *real-time* mixed hardware/software systems.

The verified stack will include a real-time language with simple constructs based on OCCAM, a program verifier for that language, a verified processor and a verified translator for compiling the real-time language into the processor instruction set.

The project will combine the INMOS CAD system and HOL proof-generation system and will also involve other formal methods suitable for specifying real-time systems including Z and CSP.

## 1.6 Outline of this Dissertation

Chapter 2 provides an introduction to the HOL logic and the HOL proof-generation system. This chapter concludes with remarks on the use of formal proof and mechanical proof-generation to reason about the correctness of software and hardware.

Chapter 3 describes the operation and design of the TAMARACK-3 microprocessor in a conventional style of microprocessor description. This chapter introduces the idea of describing hardware generically and explains how the internal architecture of a microprocessor can be viewed as a hierarchy of interpretation levels.

Chapter 4 elaborates on the advantages of generic specification and shows how this technique is used to formally specify the TAMARACK-3 microprocessor. This chapter is central to the argument of this dissertation.

Chapter 5 illustrates fundamental proof strategies for verifying microprocessor systems. The main ideas presented in this chapter are: stating correctness results, structuring a proof into multiple levels, and using logic to symbolically execute a design.

Chapter 6 elaborates on the idea of embedding natural notations from special-purpose formalisms. This is illustrated by embedding a form of temporal logic in the HOL logic for the purpose of reasoning about the interaction of TAMARACK-3 with external memory using handshaking signals.

Chapter 7 concludes this dissertation with remarks on the scope and limitations of the TAMARACK-3 proof of correctness and its relationship to other levels of proof.

# Formal Proof in the HOL System

The research described in this dissertation is based exclusively on 'the HOL logic'. This is a formulation of higher-order logic originally set out by Church [26] and adapted by Gordon [60,62] for representation in the HOL system.

In this chapter we provide brief descriptions of both the HOL logic and the HOL system. These descriptions have been tailored for the purposes of this dissertation; they are accurate in what is described but they do not represent a complete account of either the logic or the proof-generation system.

We also comment on the *security* and *extensibility* of the HOL system which we regard as its most important and distinctive features. Finally, we conclude this chapter with some remarks on why formal proof in a mechanized system such as HOL may be useful.

## 2.1 Introduction

Although higher-order logic was originally developed to study theoretical questions about the foundations of mathematics [70], a non-theoretician should be able to understand most aspects of this formalism without too much difficulty. Much of our notation will be familiar from the informal notation of mathematics, e.g.,  $\neg$ ,  $\land$ ,  $\lor$ ,  $\Longrightarrow$ ,  $\forall$ ,  $\exists$ . Some of the most important concepts will be familiar to readers with experience in strongly-typed programming languages and functional programming.

Higher-order logic extends first-order logic by allowing variables to range over functions and predicates. It also includes notation from the  $\lambda$ -calculus for describing functions. Functions which accept other functions as arguments or return functions as results are called 'higher-order' functions. The Lisp function mapcar is an example of a higher-order function in a programming language. In both logic and programming, higher-order functions result in specifications or definitions which are shorter, simpler and often easier to understand. Predicates in higher-order logic are just a particular kind of function, namely, a function which returns values corresponding to true and false. Thus, higher-order predicates are just higher-order functions which return values corresponding to true and false.

## 2.2 The HOL Logic

We begin with the syntax of the HOL logic which centers upon two main ideas: a set of well-formed terms composed from elementary terms and a set of types which are associated with terms in the logic.

#### 2.2.1 Terms

More detailed descriptions of the HOL logic [60,62] reveal that there are just four different kinds of terms: variables, constants, abstractions, and applications. However, this conciseness is mostly hidden from a user of the HOL system and is not essential to our discussion. Instead, we describe the syntax of the logic from a notational point of view where, for the purposes of this dissertation, the syntax consists of: