Number 174

# General theory relating to the implementation of concurrent symbolic computation

James Thomas Woodchurch Clarke

August 1989

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

#### © 1989 James Thomas Woodchurch Clarke

This technical report is based on a dissertation submitted January 1989 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Trinity College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

#### Abstract

#### General Theory Relating to the Implementation Of Concurrent Symbolic Computation

The central result of this work is the discovery of a new class of architectures, which I call D-RISC, sharing some characteristics of both dataflow and von Neumann RISC computers, for concurrent computation. This rests on an original and simple theory which relates the demands of concurrent computation on hardware resources to the fundamental performance constraints of technology. I show that dataflow and von Neumann architectures have different fundamental hardware constraints to performance, and that therefore a D-RISC architecture, which balances these two constraints, is likely to be optimum for concurrent computation.

The work forms four related sections:

- A study of the nature of concurrent symbolic computation and the demands which it makes from any implementation. Two new results emerge from this. A model of computation which will be used extensively in subsequent sections, and a way of incorporating imperative updates in a functional language, similar but superior to non-deterministic merge, which captures locally sequential updates in a computation with minimum constraint on global concurrency.

- The computational model is used to contrast different policies for localising data near a CPU. A new type of cache is proposed which renames all of its cached addresses in order to reduce CPU wordlength.

- CPU design is examined and a new class of architectures for concurrent computation, called D-RISCs, are proposed.

- The multiple-thread implementation problems encountered in the new architectures are examined. A new analysis of the relationship between scheduling and intermediate store use in a symbolic concurrent computation is presented.

## Contents

| 1 | Int | roduction                                                 | 1         |

|---|-----|-----------------------------------------------------------|-----------|

| 2 | Mo  | dels of Symbolic Computation                              | . 4       |

|   | 2.1 | Side-Effects and Concurrency                              | 5         |

|   | 2.2 | Evaluation Order                                          | 10        |

|   |     | 2.2.1 Annotations                                         | 11        |

|   | 2.3 | A Computational Model of Threads                          | 12        |

|   | 2.4 | Modelling Temporal Constraints with DEGs                  | 13        |

|   | 2.5 | Related Models of Computation                             | 15        |

| 3 | Mo  | dels of Hardware                                          | 17        |

|   | 3.1 | A Low Level Model                                         | 18        |

|   |     | 3.1.1 Synchronous and asynchronous hardware               | 18        |

|   |     | 3.1.2 Balancing synchronous and asynchronous resource use | 20        |

|   | 3.2 | Data Storage                                              | 23        |

|   |     | 3.2.1 Cache theory                                        | 24        |

|   |     | 3.2.2 Cache hierarchies                                   | 25        |

|   |     | 3.2.3 Data management                                     | 27        |

|   |     | 3.2.4 Name-translating caches                             | 30        |

|   | 3.3 | A Model Of Processors                                     | 32        |

|   | 3.4 | Summary and Related Work                                  | 37        |

| 4 | CP  | U Design                                                  | 39        |

|   | 4.1 | Von Neumann and Dataflow CPUs                             | 40        |

|   | 4.2 | Latency and Bandwidth Constraints on CPU Performance      | 43        |

|   | 4.3 | D-RISC CPUs                                               | 46        |

|   |     | 4.3.1 Frame cache design                                  | 46        |

|   | ٠   | 4.3.2 Scheduling                                          | 48        |

|   |     | 4.3.3 Arvind's argument                                   | 49        |

|   |     | 4.3.4 Separating control And data concurrency             | <b>52</b> |

|   |     | 4.3.5 Latency-bandwidth tradeoffs in memory design        | 54        |

|   | 4.4 | What is a Uniprocessor?                                   | 56        |

|   | 4.5 | Multiprocessor Design Taxonomy                            | 57        |

|   |     | 4.5.1 Scalability                                         | 61        |

|   | 4.6 | Summary and Related Work                                  | 62        |

| 5 | Imp        | plemen | tation Issues                                | 64  |

|---|------------|--------|----------------------------------------------|-----|

|   | 5.1        | Concu  | rrent Implementation On Uniprocessors        | 65  |

|   |            | 5.1.1  | Thread implementation techniques             | 65  |

|   | •          | 5.1.2  |                                              | 68  |

|   |            | 5.1.3  | Data lifetimes in concurrent computation     | 70  |

|   |            | 5.1.4  | Scheduling and frame cache lifetimes         | 72  |

|   | <b>5.2</b> | Concu  | irrency and Performance                      | 75  |

|   | <b>5.3</b> | Multi  | processors                                   | 76  |

|   |            | 5.3.1  | Data representation                          | 76  |

|   | * .        | 5.3.2  | Thread export                                | 78  |

|   |            | 5.3.3  | Distribution efficiency                      | 79  |

|   |            | 5.3.4  | Thread locality                              | 80  |

|   |            | 5.3.5  | Switching efficiency                         | 81  |

|   |            | 5.3.6  | Communication bus topology                   | 83  |

|   | 5.4        | Laten  | cy Limited Computation                       | 85  |

|   |            | 5.4.1  | Optimising NFIB                              | 86  |

|   | *          | 5.4.2  | Cloning                                      | 88  |

|   | 5.5        | Analy  | sis of Test Programs                         | 90  |

|   |            | 5.5.1  | Concurrent computation                       |     |

|   |            | 5.5.2  | Test programs                                | 91  |

|   |            | 5.5.3  | Conclusions from implementation of mergesort | 93  |

|   | 5.6        | Summ   | nary                                         | 94  |

| 6 | Cor        | clusio | ns and Directions for Further Research       | 101 |

|   |            |        | ALL STROME AVE & GALUMOL AUCOCCITOR          | TOT |

| A | Glo        | ssary  |                                              | 103 |

| В | Test       | t Prog | ram Listings                                 | 104 |

## Chapter 1

### Introduction

This thesis approaches the problem of multiprocessor architecture design for symbolic computation from a standpoint which bridges two different fields of research: concurrent language implementation and hardware design.

My choice of this approach owes much to the SKIM project: my part in which was the specification and design of the two processors, so I will first describe this project and my interest in it.

SKIM was a simple specialised uniprocessor designed specifically to perform (fixed) combinator reduction. SKIM II was designed after development of the system software for SKIM, and benefited from this. The subsequent software development on SKIM II resulted in a highly sophisticated combinator reducer incorporating a number of innovative implementation techniques.

The relevance of SKIM to this thesis lies in its illustration of the intimate relationship between hardware and system software design. The architectural enhancements to SKIM II were of two distinct types:

- Balancing. The bandwidths of the various concurrent operations permitted within a microcycle were adjusted to optimise use of hardware resources.

- Generalising. Wherever possible without undue extra complexity hardware capabilities used on SKIM were generalised and made more flexible. This lead to a word tagged architecture with 4 bit tags and a rich set of tests and branches on tags.

The balancing enhancements arose from what we did understand about combinator reduction algorithms. The generalising enhancements from an awareness that there was much that we did not understand.

The most interesting results to emerge from SKIM II came from the use of generalising architectural enhancements in ways that were completely unanticipated at hardware design time. For example the richness of the tag structure allowed the efficient use of unique pointer one bit local garbage collection. The discovery of this technique would not have happened without both detailed development of the microcode and the fortuitous extra hardware capability that made it feasible.

This exemplifies a fundamental problem in research into innovative hardware for applications where the software is itself not well developed. The ideal simul-

taneous optimisation of hardware and software is impossible: instead a laborious process of experimentation is necessary.

What about the use of simulation to obviate this problem? SKIM was an unusual example of hardware where the total hardware design, construction and test time was small, and the working machine provided facilities that enabled otherwise impracticable software development. The preliminary study of high performance architectures can usually more easily proceed by simulation. However the instrumentation of a simulation fast enough for substantial software development is difficult and liable to preclude the architectural flexibility that would allow investigation of many different architectures. Furthermore the higher level, and hence faster, a simulation the less easy it is to relate its parameters to real hardware constraints.

Multiprocessor architecture investigation offers a particularly intractable example of this dilemma. Neither system software nor hardware are separately understood, whilst the enormous range of possible implementation techniques makes iterative solution extremely difficult.

Analysis of the way that SKIM hardware was used by its software led to general insight into the fundamental performance constraints in combinator reducing hardware and showed how much faster hardware could be designed. My aim has been to achieve the same sort of general insight into the much more difficult problem of multiprocessor architecture performance. To do this requires an investigation which is broadly-based and can identify the relationship between constraints on hardware and performance of the software that uses it. I will call this sort of analysis implementation theory because an implementation is composed of both hardware and system software.

It is generally the case that implementation theory is worked out retrospectively, as experience with existing designs shows the relationship between different implementation problems. The work from which this thesis started was such an analysis of SKIM's performance and its relationship to the SKIM hardware [Cla84]. The problem which I address in this thesis is more ambitious: how can the implementation theory appropriate to new hardware be investigated sufficiently to have some idea about the advisability of the new hardware design?

In uniprocessor design the underlying theory is relatively simple, so new designs can be investigated with some confidence. The corresponding central theory appropriate to designs for concurrent computation is the object of my investigation in this thesis.

The central result of my work is the discovery of a new class of architectures, sharing some characteristics of both dataflow and von Neumann computers, for concurrent computation. This rests on an original and simple theory which relates the demands which concurrent computation makes on hardware resources to the fundamental performance constraints of technology.

The results of my work thus form four related sections:

Chapter 2 studies the nature of concurrent computation and the demands which it makes of an implementation. Two new results emerge from this. A model of computation which will be used extensively in subsequent sections, and a way of incorporating imperative updates in a functional language, similar but superior to non-deterministic merge, which captures locally sequential updates in a computation with minimum constraint on global concurrency.

- Chapter 3 studies the low-level performance limitations of processor hardware, and uses the computational model to contrast different policies for localising data near a CPU. One new result of this is the discovery of a type of cache which renames all of its cached addresses in order to reduce CPU word-length.

- In Chapter 4 the preceding work is applied to CPU design and a new class of

architectures for concurrent computation is predicted to have performance

which is superior to conventional von Neumann or dataflow architecture.

Without concrete design this theoretic prediction can be no more than a

motivation for further work, however recent design work by Ianucci [Ian88]

offers support for the proposition that these architectures are truly superior

to existing ones.

- Finally the multiple-thread implementation problems encountered in the new architectures (and also in any multiprocessors for symbolic computation) are examined. A new result here is an analysis of the relationship between scheduling and intermediate store use in a symbolic concurrent computation. This provides an underlying theory which is confirmed by recent experimental results [RS87] on dataflow machine store use.

## Chapter 2

## Models of Symbolic Computation

| 2.1 | Side-Effects and Concurrency             |

|-----|------------------------------------------|

| 2.2 | Evaluation Order                         |

|     | 2.2.1 Annotations                        |

| 2.3 | A Computational Model of Threads         |

| 2.4 | Modelling Temporal Constraints with DEGs |

| 2.5 | Related Models of Computation            |

This chapter describes the styles of computation to be considered in this thesis, and gives an overview of the assumptions to be made about programming languages and computational models.

It will assumed that computation is specified by an annotated implementation language (IL). The implementation problem which I address is determined by the type of computation expressible in this IL, and so issues of language design and compilation above the level of the IL need not be of concern in subsequent chapters.

The first section considers the extent to which the IL should be functional (free of side effects) and concludes that some imperative-style updates are necessary. A class of updates is introduced which are related to non-deterministic list merge, and which have particularly clear semantics.

The next section argues that the IL should use a parallel evaluation order which behaves semantically like applicative order evaluation but allows greater concurrency. Section 2.2.1 describes a set of annotations of the IL which cooperate with a run-time system to control export of computation.

The next section introduces a formal model of threads which describes the concurrency available in an IL program. The final section bridges the gap between IL and hardware by showing how any IL expression defines a set of ALU operations necessary for its evaluation. The temporal constraints on these operations may be derived from the IL directly and define the potential concurrency of the expression.

#### 2.1 Side-Effects and Concurrency

Even when a fully parallel language is used to specify computation, at the level of hardware all execution occurs by updating the value of physical memory locations. Since there are a finite number of these and an arbitrary number of intermediate data in a computation some notion of sequence must be adhered to in order to permit location reuse.

The implementation of any IL must cope with this need for sharing and therefore compile to one or more sequential threads, each of which may then make sequential use of the resources allocated to it. The multiplicity of threads expresses the (asynchronous) concurrency which can be achieved: between different threads the sharing of resources is asynchronous and may be determined by the whims of a run-time system.

On uniprocessors the sophisticated compilation of purely functional languages leads to equivalent and more efficient sequential programs in which tail-recursive function calls turn into loops with assignment to local variables. In functional languages any recursion imposes a sequence on necessary ALU operations. If the same computation is expressed using structured loops and variable assignment then exactly the same constraints on execution order will be present; in this sense structured use of iteration and local variable assignment are exactly equivalent to the use of functional languages and recursion.

In order to maximise potential concurrency in the IL it is thus necessary to

limit side-effects only between operations that could lie on concurrent threads. If the IL is a purely functional language then, subject to the dataflow constraints examined in Section 2.4 below, any two different function applications could be concurrent. The uncontrolled use of global assignment by any part of an expression is thus dangerous and could lead to unnecessary specification of evaluation order in order to preserve well-defined semantics.

There are however important cases in which the addition of side-effects to an otherwise functional language allow algorithms to be expressed in a more concurrent way. A common instance of this is in the incremental construction of some global object (for example a symbol table). A number of function calls, perhaps from different and concurrent threads, must sequentially access and update the value of a variable. Initially some value is assigned to the variable and eventually, after all updates have occurred, the variable may be read. Between these two events the sequence of updates is arbitrary; however each update must be an atomic imperative operation. Without this restriction such a task could only be accomplished by specifying a predefined order in which the updates are to be handled, with it updates may be interleaved freely.

This lack of expressiveness in pure functional languages has long been recognised, and remedies have been suggested. The most popular of these, see for example as in [Hen82], is to allow a primitive non-deterministic merge operation which merges two lists in some order determined by the run-time system. In the rest of this section I will introduce and then consider the properties of a new operation, which I call a sequencer. This is similar to a non-deterministic merge, but more general. Furthermore the resulting language semantics are clearer because the effect of the non-determinism introduced is clearly demarcated.

Sequencers. I will call a globally updated variable a sequencer. Associated with each sequencer s of type S is an update function  $f_s$  of type  $S \times X \to \langle R, S \rangle$ , say. Each call of  $f_s$  has as a side-effect the modification of s and returns a value which may depend on the current value of s. The important property of  $f_s$  is that it be semantically commutative: that is that any permutation in the order of a set of calls of  $f_s$  does not alter the final result of the computation.

This can be proved when the S and R are such as to limit the operations that may be performed on values within them to ones which are invariant under these permutations. The proof may be local, without any reference to the global structure of the program, and it is this which makes sequencers an appropriate way of packaging limited side-effects, needed for either semantic or implementation convenience, within a concurrent program. Sequencers introduce into a program non-determinism which is provably (by local analysis) encapsulated within certain data types. If these are not printable the result of the program must be deterministic.

The semantic commutativity of sequencer calls means that sequencer updates can often be written using a semantically associative operation. In fact the semantic commutativity of sequencer calls means that this can in principle always be done, though the required operation may be expensive.

Call a set of objects each tagged with a positive integer a mset—msets are sets with possibly multiple members. For any mset of sequencer calls X, let  $S_X$  be one corresponding possible state of the sequencer. The associativity of mset union transforms to semantic associativity of sequencer state combination by defining  $S_X \diamond S_Y = S_{X \cup Y}$ . This operation can at worst be implemented by holding X together with each  $S_X$  and generating  $S_{X \cup Y}$  from  $S_X$  and Y. Often (as in the example below) a simpler algorithm can be found for  $S_{X \cup Y}$ .

Now let

$$f_{\bullet}(x) = \langle f_{\text{result}}(s, x), f_{\text{update}}(s, x) \rangle$$

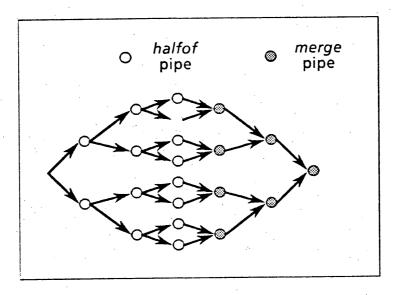

If  $f_{\text{update}}(s,x) = s \diamond x$ , where  $\diamond$  is an associative commutative operation,  $f_s$  can be implemented as a tree of sequencers which establishes a sequence over an arbitrary number of concurrent threads while never exceeding the spot bandwidth needed for two threads.

Consider a simple example: the distribution of a unique non-negative integer to every node of a tree in such a way that the maximum integer so used is O(the size of the tree). Three implementations of this are:

a) Sequencer with:

$$S = INT$$

$R = INT$

$X = VOID$

$f_s(s,x) = \langle s+1, s+1 \rangle$

In this implementation the sequencer calls form a sequential thread within the otherwise concurrent tree-crawling threads which use the sequencer. Where the sequencer update bandwidth is less than the total sequencer call bandwidth this does not constrain program execution.

b) Pure functional program in which tagged subtrees are merged to give the right answer:

```

%(REDUCE-like fragment)

Procedure tag_tree( tree) =

If atom tree

Then tag_atom tree

Else merge_tagged_trees( tag_tree( car tree), tag_tree( cdr tree))

Procedure merge_tagged trees( x, y) =

Let n = largest_tag_in x

In ( x . add_to_tags( y, n+1))

Procedure largest_tag_in x = .... % return largest tag in tree x

Procedure add_to_tags( x, n) = .... % return copy of x with n added

```

The concurrency of the tree crawl is preserved but at the cost of an overhead O(average depth of tree).

c) Set of sequencers with:

$$S = INT$$

$R = INT$

$X = INT$

$f_s^i(n,x) = \langle n+x, n+x+1 \rangle$

In the following description in order to simplify notation I will write  $f_s^i(x)$  meaning an application of the function  $X \to R$  defined by sequencer  $f_s^i$  to x.

Suppose that the  $f_s^i$  are used by a tree-crawling program in such a way that a call to any  $f_s^a$  has the effect of a single global sequencer call, irrespective of a. This can be achieved by combining the  $f_s^a$  together. To combine  $f_s^1$  and  $f_s^2$  to get a single sequencer  $f_s^3$ :

- If a call to just one of  $f_s^1$  and  $f_s^2$  is outstanding pass it on to  $f_s^3$  unchanged and return the corresponding result.

- If two calls  $f_s^1(x)$  and  $f_s^2(y)$  are outstanding, let  $r = f_s^3(x+y)$ , and return r and r+x as result of  $f_s^1(x)$  and  $f_s^2(y)$  respectively.

In this way sequencers can be combined in an arbitrary tree which preserves the sequencer semantics. If the tree is binary no sequencer has an update bandwidth greater than the maximum call bandwidth at a leaf of the tree.

It is interesting to contrast the operation of such a tree of sequencers with the pure functional algorithm, which also combines results in a tree using an associative combination operation. There are two differences:

- 1. The functional program does not allow sequencer state to propagate down the tree to the leaves and so must recompute a subtree's tags at each node.

- 2. The sequencer algorithm uses a combining tree whose shape is arbitrary instead of being exactly specified by the program <sup>1</sup>.

The first of these demonstrates the way in which sequencers can use (local) side-effects, a different sequencer with no side effects could be used which would more closely mimic the functional program. The second of these demonstrates the great freedom which explicit acknowledgement of the associativity of a sequencer operation gives the implementor.

The number and tree structure of sequencers can be chosen so as not to limit overall concurrency while minimising sequencer combination overheads. This

<sup>&</sup>lt;sup>1</sup>In fact following the program's Thread Creation Tree, see Section 2.3

choice may be made with due consideration to hardware connectivity or execution dynamics (new sequencers can be added dynamically as necessary to prevent saturation of any one sequencer).

In a binary switching network this type of sequencer can be distributed across switching nodes so enabling global sequencing without any sequencer call bandwidth hot-spots. This example has been used in a number of architectures for this purpose, where atomic primitive "fetch-and-op" instructions provide concurrent communication for different (associative) arithmetic and logical operators, and are combined in special "combining" communications networks. For example the IBM RP3 multiprocessor [AH88], where processors communicate via either a fast read/write network or a slower combining network.

Sequencer Implementation. Each sequencer s must be given an initial value, updated, and then read. The reading of a sequencer can be synchronised so as to be after all possible updates by the use of update permit thread reference counts. A thread which contains a sequencer initialises it and then has update permission until it tries to read the sequencer. Any thread created by a thread with update permission may be given its own update permission: a global reference count associated with the sequencer must return to 0 before the sequencer is read.

The run-time overhead of these reference counts can be reduced by careful static code analysis: for example a thread which updates a sequencer and then creates just one update-permitted thread may pass on its own count to this thread. The use of reference counts is only necessary when a sequencer is read. This need not be so, consider for example a simple sequencer used to distribute globally unique tags.

For the purposes of implementation two subclasses of sequencers can thus be identified:

- 1. Sequencers whose final state is never read: thus communication is always downwards to subthreads. Reference counts are not needed.

- 2. Sequencers which do not return a useful result on individual calls: thus communication is always upwards from subthreads to some parent. In this case, if the sequencers are also associative, local sequencers can be used as required to reduce latency or increase bandwidth. This case corresponds to algorithms which can be expressed directly (but less efficiently) in pure functional languages.

In general a sequencer will use both types of communication, as in the implementation of a symbol table returning access keys for names in individual calls, and whose final value is the symbol table itself.

The implementation of sequencers in multiprocessor hardware requires atomic read-modify-write access to shared store which must be carefully considered during architecture design, and perhaps incorporated into combining switching networks for higher global bandwidths.

Sequencers express a type of inter-thread communication which occurs naturally in many algorithms in a way which minimises the requisite sequentiality. Where a sequencer can be represented by an associative update this information can be used by the hardware or run-time system to optimise communication. They are thus an indispensible element of a concurrent implementation language.

#### 2.2 Evaluation Order

Thread creation and reference results in parallel evaluation order. In a functional language this has the same semantics as applicative evaluation order but allows more concurrency. Normal evaluation order, in which function bodies are evaluated first and arguments are then evaluated by need, is often confused with lazy evaluation, in which every expression is evaluated only if it is subsequently needed and at most once. The difference lies in whether repeated references to an expression result in repeated evaluations of it.

One reason for this confusion is that normal order combinator reduction is efficient and results fortuitously in lazy evaluation. Combinator reduction has recently been shown (for example in [FW87]) to be an efficient implementation technique for uniprocessor lazy evaluation, and this has encouraged parallel graph reduction machine architects. The words lazy, combinator, parallel architecture, graph reduction machine are not synonymous.

Normal order semantics result in the best possible termination properties for programs, in the sense that if any evaluation order for an expression will terminate then the normal order one will. This results in greater freedom for the programmer, who can represent infinite objects explicitly in a program without worrying about their unnecessary and fatal evaluation.

Normal order semantics has some problems, and these are to do with implementation. The evaluation of expressions only on need often leads to large intermediate expressions, consisting of nested suspensions, in evaluation of recursion. In a large program it is easy to produce 'space leaks' where very large suspensions accumulate during execution. This is undesirable and results in a use of store that is much higher than expected by the programmer.

It is in general very difficult to infer from the structure of a Normal order program where a space leak will occur. This is the other side of the programming freedom introduced by Normal order. It appears that reasoning about size of intermediate results is very difficult with the highly data-dependent specification of evaluation order necessitated by lazy semantics.

Strictness analysis is a technique used to ameliorate this problem. From static analysis of code it is often possible to infer that an expression will always be needed. Then it may be evaluated in applicative or parallel order without disturbing Normal order semantics. A Normal order semantics evaluation can only make use of concurrency by the use of strictness analysis to identify expressions which can be evaluated eagerly.

The implementation issue here is important. If code can be evaluated ap-

plicatively then architectural investigation should concentrate on strict functional languages and use conventional implementation techniques. Otherwise architectures which optimise combinator reduction must be considered. The differences in run-time execution behaviour between the two are significant.

I choose to base this analysis on applicative (which in a concurrent architecture may be implemented as parallel) order languages. There are two reasons for this.

First, parallel order semantics result in more concurrent implementation than normal order semantics. Therefore they will be used if either strictness analysis allows this or, in the interests of high performance, the freedom of normal order semantics is foregone. A pessimist would require the latter, an optimist hope that developments in strictness analysis result in the former.

Second, in a parallel system applicative order must be used sometimes, so the additional consideration of Normal order evaluation merely complicates the analysis. The problems of concurrent implementation are large enough themselves without solving other implementation problems as well.

The sequencers described above allow explicit implementation of combinatorlike lazy evaluation: this extension to the IL thus allows lazy evaluation should this ever be required.

Logic programming languages present a different set of implementation problems from functional languages and are not directly considered by this thesis. The efficient implementation of non-deterministic concurrent computation, as in breadth first searches, where termination of one computation may make necessary the killing of a large number of sibling computations, is an extra computational requirement which does not exist in a thread world. However the results of this work do extend to the larger problem, though extra work may be needed fully to understand the requirements of these programs.

#### 2.2.1 Annotations

An annotation of the IL constitutes added information that does not affect its semantics but is used to optimise code generation. A well-known example of annotation is the register declaration in C.

Two sorts of annotation may be identified: critical and advisory. A critical annotation, if present, must be correct; an example of this is type information used to optimise code generation. An advisory annotation can never result in incorrect program execution. In a functional language export of computation is semantically invisible so all annotations controlling this are advisory. This has an important implication: export annotations may be adjusted empirically by unsophisticated programmers without catastrophic results. Alternatively, annotations may be generated automatically be empirical rules that give good results most of the time. The formulation of such a rule is much easier than that of a rule which will always give good results.

The export annotations chosen for the IL are architecturally independent. They specify the export of computation, but give no indication of where such computation is to go. One possibility is for computation annotated for export

to be scheduled on its creating processor. The export annotations, in addition to specifying thread boundaries (and hence possible units of exportable computation) may give additional information which the run-time system will take into account when deciding whether or not to export a thread.

#### 2.3 A Computational Model of Threads

The preceding sections motivate and describe an IL in which concurrent symbolic computation can be expressed. The rest of this chapter is concerned with a more formal description of one aspect of the IL of interest to an implementor: its potential concurrency. The notion of a thread of computation has been used above informally: I now introduce a formal definition of the word.

I will call the unit of computation associated with asynchronous concurrency a thread. Threads vary in size from single ALU operations in a dataflow machine to whole programs in a von Neumann processor. Threads are characterised by their internal execution, which is synchronous. Thus the execution of a thread defines a set of clock-ticks which are constrained to occur in a particular sequence. Each clock-tick may have associated with it a number of operations which happen concurrently. This is called synchronous concurrency<sup>2</sup>: an array processor may have a large amount of synchronous concurrency, von Neumann compiled code has an amount limited to that available within one function body.

Perhaps surprisingly this amount can be considerable if careful compilation is used to unroll loops and treat as exceptional conditional exits from loops. Fisher [JAF88] has demonstrated that most von Neumann programs exhibit high (> 5) fine-grain synchronous parallelism when appropriately compiled. The cost of this is a big increase in static code size.

The execution of compiled code on a von Neumann machine will be called a VN-thread, and corresponds to sequential execution of function bodies.

In general the execution of a thread will require local temporary data which will be called the thread's context. The size of a thread's context may vary with time: the dynamic part of a VN-thread's context is usually held in a stack.

This notion of a thread is similar to the familiar one of a task. I use the word thread because it evokes a sequential strand of computation and in order to be precise about the communication allowed between different threads. Threads may be created, exported and referenced. Creation of a thread immediately returns a unique handle which is a data object and may be used globally to refer to the thread. Reading this handle at any time results in either a synchronisation wait, if the thread has not finished execution, or its value. Requests for the value of an unfinished thread are in general queued with its context and satisfied when it finishes.

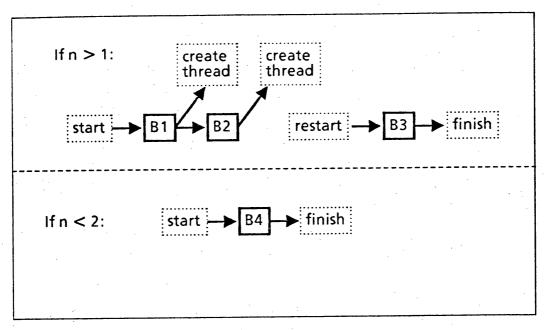

It may be expedient to ensure that synchronisation waits occur only at the start of a thread's execution, so that data availability becomes an enabling condition for execution of the thread. This can be accomplished simply by requiring a thread

<sup>&</sup>lt;sup>2</sup>An exact definition of synchronous concurrency will be given in Chapter 3.

to create a new thread on waiting. The thread's value will be returned by the new thread, which is just the waiting continuation. Semantically this distinction is trivial, but it results in differences in implementation strategy which are important and will be considered later on in Chapter 5.1.

This method of inter-thread communication may be optimised in various special cases. The most important of these is when the identity of the sole referencer of a thread is known at thread creation time. In this case the thread value can be forwarded directly to the referencing thread when it is ready. Other optimisations may result from less complete information about how a thread may be referenced.

Threads thus allow dataflow style communication but may also be incorporated into data structures by reference so maximising concurrency. They are units of both inter-thread reference and concurrent communication. These two operations are conceptually separate although (asynchronous) concurrent execution requires some form of inter-thread reference. In Chapter 5.3 I evaluate the usefulness of different strategies of global heap reference.

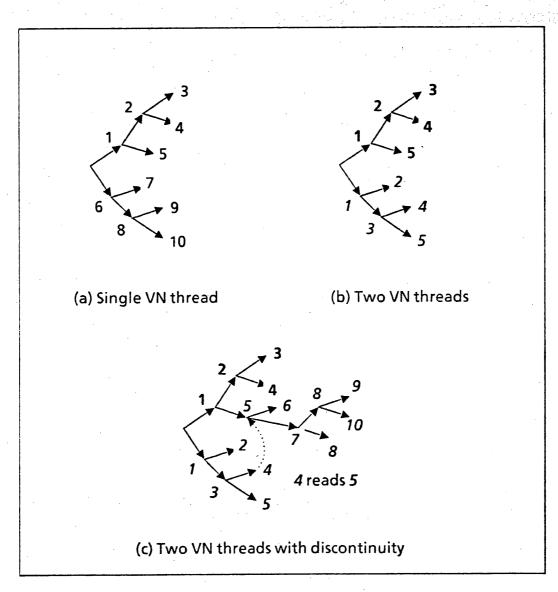

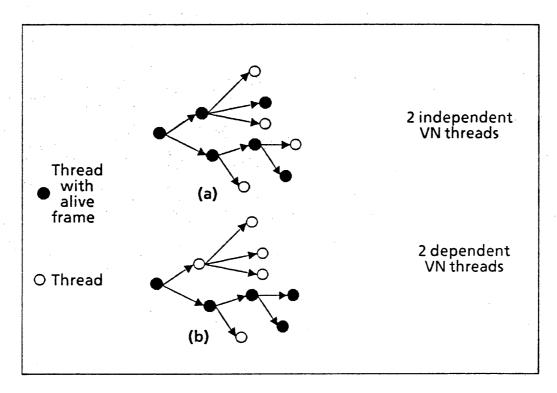

Thread Creation Trees. A thread decomposition of a particular symbolic computation has one important associated structure: its Thread Creation Tree (TCT). The TCT is a structure describing the thread structure of a computation: each node represents a thread and arcs point from parents to their children. Different static decompositions of a computation into threads will therefore have different TCTs.

The TCT captures the relationship between threads. Chapter 5 will use TCTs when describing the dynamics of executing programs. For example the likelihood that two executing threads are dynamically executed on the same processor may be related to their distance apart in the TCT.

#### 2.4 Modelling Temporal Constraints with DEGs

A thread decomposition of an IL program specifies asynchronous parallelism. I will now introduce a new and related model which captures exactly the algorithmic constraints on parallelism: a Dataflow Execution Graph (DEG). We will see below that implementation can be viewed as an appropriate map from DEG to hardware execution model, determined by a compiler.

A Dataflow Execution Graph describes abstractly the constraints on any hardware executing an IL expression. It thus specifies the task of code generation for the expression in a way which is architecture independent.

A DEG is a convenient way of representing two partial orders which define the sequencing intrinsic to a concurrent computation. Throughout this thesis a number of structures will emerge which are, mathematically, order relations on finite sets. For notational convenience these are described by the corresponding canonical directed acyclic graphs—any dag establishes a partial order on its nodes through path connectedness; the minimal dag representing a given partial order (the one with the minimum number of arcs) represents the order canonically.

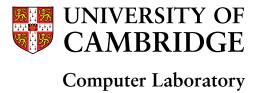

Figure 2.1: DEG of FIB(2)

A DEG is constructed from a (strict functional) expression by noting the ALU operations performed in its execution, these form the nodes of the DEG. Directed arcs between the nodes represent causal relationships so that  $a \to b$  means 'a must happen before b'.

ALU operations must first be specified and then fired. During evaluation the specification of an ALU operation determines the compile-time information associated with it and guarantees that, at some future time, the operation will be executed. Firing of a specified operation requires the availability of its source data. Every ALU operation must first be specified and then fired. After firing of an ALU operation its result becomes available as source data for subsequent operations.

The DEG thus consists of two separate directed acyclic graphs sharing a common set of nodes. One represents dependence of specification on firing, the other dependence of firing on firing. Call these two graphs, respectively, the C-graph and D-graph and their arcs C-arcs, D-arcs. It is useful to think of C-arcs as representing control flow, and D-arcs data flow.

Arcs that do not signify immediate dependence, and so are implied by other arcs, are omitted from the DEG.

The DEG for fib(2) is shown in Figure 2.1. Note that the D-arcs to the final + node source compile-time constant ones, available only after the firing of the associated test.

A DEG is closely related to a dataflow graph, but should not be confused with it. Whereas dataflow graphs may be used as a particular execution model for a program DEGs are a general abstract description of a computation. The DEG is not determinable from static inspection of a program because it describes all of a computation's execution dynamics.

A single CPU, together with appropriate IL compiler determines a map from the DEG of any IL computation to a concrete execution trace which has three components:

- A temporal order on nodes corresponding to their execution sequence on the ALU.

- A map from each D-arc to a function from the time interval between the two ends of the arc to the set of data locations in the CPU. These functions must satisfy the constraint of unique location occupancy as well as data transfer constraints determined by CPU architecture.

- A way of remembering those nodes which have been specified but not yet fired.

The study of CPU design for strict functional languages is thus the study of the hardware constraints imposed on this map. Asynchronous concurrency in a CPU or multiprocessor system may be related to a partitioning of the DEG into appropriate subsets which define threads.

#### 2.5 Related Models of Computation

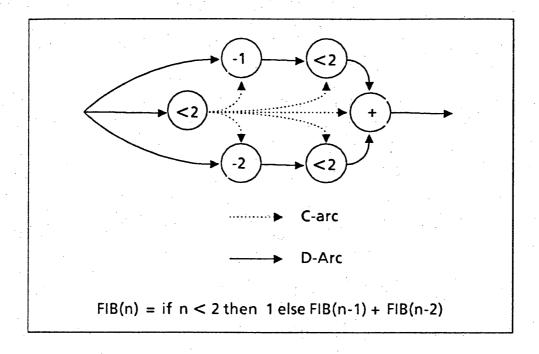

This chapter has now established a number of different models of the style of symbolic computation which this thesis considers. This work lies in between implementation oriented descriptions of computation, such as dataflow graphs ([Den80]), and programming languages: for example Multilisp [Hal85].

The Multilisp language design contrasts with this work by allowing arbitrary imperative constructions within a mainly functional language—it is thus close in spirit to LISP and larger than my IL. However with this exception the type of computation which I consider is more general than other proposed models of parallel computation.

The models of parallelism which correspond to successful parallel architectures and are widely used differ from my definition of symbolic computation by using concurrency which is (to some extent) well-defined at compile time. This is much easier to map efficiently onto parallel machines than the general case of highly dynamic concurrency. Two directions in which work has resulted in some success are vector parallelism, in which parallel computation is highly regular; and models which define concurrent processes and communication statically (for example OCCAM [Hoa]).

One interesting new model suggested by Sabot ([Sab88]) introduces coarsegrain dynamic creation of concurrent array operations: this is nearer to symbolic computation than pure vector models.

One other set of execution models is based on lazy functional languages, for example Hudak's "parafunctional programming" [HS85]. These are rejected by me for the reasons given in Section 2.2 above.

Figure 2.2 illustrates the relationship between different styles of computation. Those occupying a smaller area are in general easier to implement.

Figure 2.2: Types of Computation

# Chapter 3

## Models of Hardware

| 3.1 | A Low Level Model                                         | 18 |

|-----|-----------------------------------------------------------|----|

|     | 3.1.1 Synchronous and asynchronous hardware               | 18 |

|     | 3.1.2 Balancing synchronous and asynchronous resource use | 20 |

| 3.2 | Data Storage                                              |    |

|     | 3.2.1 Cache theory                                        | 24 |

|     | 3.2.2 Cache hierarchies                                   |    |

| •   | 3.2.3 Data management                                     |    |

|     | 3.2.4 Name-translating caches                             |    |

| 3.3 | A Model Of Processors                                     |    |

| 3.4 | Summary and Related Work                                  | 38 |

This chapter provides a low-level description of hardware which complements the description of computation by Dataflow Execution Graph in Chapter 2. The next chapter will relate these ideas to CPU design by discussing the different ways in which hardware can be used to localise data near an ALU.

The performance of a CPU can only be established by considering the characteristics of the hardware from which it is constructed. This can be done in many ways: in VLSI design it is usual for a circuit to be analysed at different levels of abstraction: solid state physics, transistors, gates, functional blocks. Low level descriptions are more detailed: in establishing the characteristics of a particular circuit a global low-level analysis would be ideal, this is seldom possible because the computation required to do it is not feasible. Instead a number of levels of analysis are used; each level calculates the operational parameters which are used by the next level up.

The rôle of abstraction in hardware design is similar. An ideal design algorithm would be to analyse all possible designs at a low level and select the one with the best performance and cost. This is impractical, the number of possible designs is exponential in design size and proving even one low level design to be correct without recourse to high level abstraction is usually a combinatorial nightmare.

Hardware design must thus proceed by making some high level decisions about structure and then working through the necessary low level details. It is difficult because until these have been worked out it is difficult to be sure that the high level decisions made in the design lead to high performance. Formal design tools for verifying and estimating the performance of a particular design do not help to formalise high level choices between design strategies. Computer design still proceeds by trial and error: a computer designer makes informed guesses about the shape of a new architecture based on what is understood about the performance of existing architectures.

This chapter examines a set of models of concrete hardware which facilitate understanding of the performance of multiprocessor architectures. The models here are not formal languages for the description of hardware operation, such as Hoare's CSP [Hoa85] or a model proposed by Monteiro and Pereira in [MP86] which describes clearly the formal properties of general communicating asynchronous systems. I propose models of hardware which explain the performance of differing implementations.

The lowest level of these is that described below, where the operation of hardware is related to time, and hence performance.

#### 3.1 A Low Level Model

#### 3.1.1 Synchronous and asynchronous hardware

Hardware may be modelled by functional blocks which perform operations sequentially. The operation of a memory requires this description, the value of a read is defined to be that remembered from the most recent corresponding write. Something which happens at an instant will be called an event. A memory may be

described by a sequence of read and write events.

If the operation of the block can be described by a single sequence, defining a total temporal order on events, the block will be called synchronous. Synchronous blocks may be composed synchronously to form larger blocks. Operation is still described by a totally ordered set, each object in the set is a tuple of operations, one for each of the composed blocks.

In contrast blocks may be composed asynchronously, with communication between blocks imposing only a partial temporal order on all operations. The operation of an asynchronous system may be described by a partially ordered set of events.

The performance of a synchronous system is defined by the rate at which events can happen: its bandwidth. Simple hardware may be described synchronously with reference to a fixed frequency global clock. Here the bandwidth of the system is constant. A more complicated synchronous description, for example a von Neumann instruction sequence, may have a variable bandwidth with different operations taking a different length of time.

Analysis of the performance of an asynchronous system is more complicated. Performance is limited by the latency between ordered events. Consider the minimal directed acyclic graph that is equivalent to the partial order on events defining the system. Each arc on this graph may be labelled with a latency, the real time between two events is given by the length of the critical path between the events. Here the length of a path is the sum of the latencies of its arcs, and the critical path between two events is the longest path connecting them.

It should be clear from this that synchronous systems are just a subset of asynchronous systems. The words synchronous, asynchronous may be appropriate at different levels of abstraction in the description of the system. All hardware is at a low level asynchronous: operation is determined by logic levels and delays through gates—in the limit their behaviour must be analysed with analog rather than digital electronics. When gates happen to form flip-flops with a common global clock the system may most usefully be described synchronously—however any determination of clock rate (and hence the system's bandwidth) must refer to critical paths through gate delays in the lower level asynchronous description. A large functional block which is globally clocked may also be given a simple approximate asynchronous interface description.

For example a memory system may be clocked synchronously in common with a CPU and take 10-12 cycles of delay from presentation of address to emergence of the appropriate data. Its interface with the CPU comprises a handshake, and so the memory may be described at a high level as an asynchronously cooperating unit. Successive levels of abstraction require a description which is asynchronous, then synchronous, then asynchronous again.

When analysing the performance constraints on a high level description of a design both asynchronous and synchronous styles of analysis may be appropriate. Synchronous performance limits are determined by the bandwidths of particular functional blocks, asynchronous performance limits by the latencies on critical paths in the system.

The DEG description of concurrent computation relates operations to time by specifying partial temporal orders that individual operations must satisfy and so is an asynchronous description. However the local descriptions of the operation of individual CPUs may most appropriately be synchronous. Reasoning about the performance of a multiprocessor system will thus use both synchronous and asynchronous models, corresponding to separate latency and bandwidth constraints.

A central problem in multiprocessor design relates to the use of synchronous units. Whenever computation can be synchronised the extra information that interacting blocks have about each other can be used to simplify design and reduce communication costs. The asynchronous nature of the concurrency in symbolic computation makes global synchronism extremely inefficient: in contrast the synchronous concurrency which can be exploited in vector and array computation is relatively efficient. The design of a multiprocessor system must balance the benefits of local synchronicity against its costs. The choice between synchronous and asynchronous use of resources must be made at many different levels in system design and is a compromise. An important example of this is considered in Chapter 4.

The next section looks in more detail at this tradeoff between synchronous and asynchronous use of resources.

## 3.1.2 Balancing synchronous and asynchronous resource use

In a CPU design the performance of some unit, for example operand fetch, may be described by both latencies and bandwidths. The latency of the unit is the time from the event that defines an operation to the event that completes it. The bandwidth of an operation is the maximum rate at which operations can be performed. Both parameters are important, and either may be the one which limits system performance.

If a unit x is used concurrently by n operations its bandwidth,  $f_x$ , and its latency,  $t_x$ , separately constrain its use. The frequency with which it can be used is  $\min(f_x, \frac{n}{t_*})$ . Concurrency relaxes latency constraints on throughput.

In synchronous systems concurrency is usually limited, since it requires organised correlation of different activities. An example of synchronous concurrency is tightly-coupled pipelining of von Neumann instruction fetch and execution, which works best when it is known a priori that these operations take the same time. In asynchronous systems resources may be used concurrently with more freedom, activities are unconstrained except by their competition for the shared resource.

This illustrates a beneficial effect of asynchronous use of resources: increased concurrency means that the design constraints on latency of the resource may be relaxed allowing a faster design.

An intrinsic disadvantage of asynchronous concurrency can easily be identified. Suppose that N asynchronous activities are each using a hardware resource X of bandwidth  $f_X$ . Each activity consists of a sequence of operations, some of which are requests to use the resource. Suppose that resource requests are made

randomly at a constant rate  $f_A$ , the distribution of time between requests is thus exponential. This simple model is a reasonable first approximation to the nature of resource use in arbitrary computations.

When an activity requests use of the resource it suspends until the request is granted, this wait does not alter the expected length of time between resumption and the next resource request.

Now consider the average use of the resource by these activities. The resource will be used for as long as the number of queued activities is not 0. Let

$$q_i = rac{ ext{Probability queue length is } i}{ ext{Probability queue length is } 0}$$

and

$$\alpha = \frac{Nf_A}{f_X}.$$

$\alpha$  is the amount by which the total rate of request of the resource exceeds its bandwidth.

Equating the transitional probabilities from and to each queue length we have:

$$q_1 = \alpha$$

$$(1 + \alpha(1 - \frac{i}{N})q_i = q_{i+1} + \alpha(1 - \frac{i-1}{N})q_{i-1}(1 \le i \le N)$$

From this we find that

$$q_i = \left(\frac{\alpha}{N}\right)^i \frac{(N)!}{(N-i)!}$$

Let  $S = \sum_{i=0}^{N} q_i$ , then the fraction of time for which the resource is used is  $1 - S^{-1}$  and the amount by which the activities are slowed down because of queuing is therefore  $\alpha/(1 - S^{-1})$ .

By inspection if  $x = \frac{\alpha}{N}$  then  $\frac{d}{dx}(x^{-N}q_i) = -q_{i+1}$ , so:

$$x^{-N}S' - Nx - (N+1)S = -S+1 \Rightarrow$$

$$S' = \frac{N}{\pi}S + x^{N}(1-S)$$

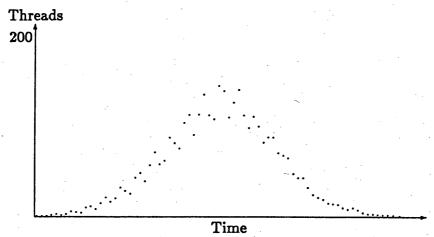

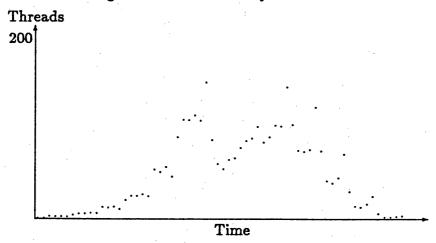

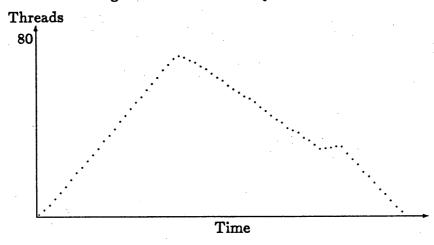

This equation does not have a closed analytic solution, so neither does S. For the purposes of this investigation it is sufficient to observe that  $\forall k < n$  S is bounded from below by  $\{(1-\frac{k}{N})\alpha\}^k$ , so that for large N the resource is nearly fully used when  $\alpha$  is near to and above 1, in other words when the total resource demand bandwidth is slightly more than  $f_X$ . However for small N the cost paid in some combination of high  $\alpha$  or low resource use is considerable: in Figure 3.1a the utilisation of resource X is tabulated for different  $\alpha$  and N.

This behaviour is characteristic of any resource shared by independent activities. If the resource is expensive extra concurrency must be wasted on it in order to ensure its nearly full use. An example of this can be found in Chapter 4 where the resource in question is CPU activity. In this case resource idleness impacts

| α   | N            |      |      |      |      |

|-----|--------------|------|------|------|------|

|     | 1            | 2    | - 3  | 4    | 5    |

| 1.0 | 0.67         | 0.80 | 0.86 | 0.89 | 0.91 |

| 1.2 | 0.67<br>0.74 | 0.88 | 0.93 | 0.96 | 0.98 |

| 1.4 | 0.79         | 0.92 | 0.97 | 0.99 | 0.99 |

| 1.6 | 0.83         | 0.95 | 0.98 | 1.00 | 1.00 |

| 1.8 | 0.86         | 0.97 | 0.99 | 1.00 | 1.00 |

(a): N activities competing for single resource

| α   |      | N    |      |      |      |

|-----|------|------|------|------|------|

|     | 1    | 2    | 3    | 4    | 5    |

| 1.0 | 0.60 | 0.69 | 0.74 | 0.76 | 0.79 |

| 1.2 | 0.67 | 0.77 | 0.82 | 0.86 | 0.88 |

| 1.4 | 0.72 | 0.83 | 0.88 | 0.91 | 0.93 |

| 1.6 | 0.77 | 0.87 | 0.92 | 0.95 | 0.97 |

| 1.8 | 0.80 | 0.90 | 0.95 | 0.97 | 0.98 |

(b): Single activity with up to N queued requests for resource

Figure 3.1: Concurrent resource use

CPU performance directly, and the extra concurrency required to reduce this idle time results in higher CPU register storage requirements.

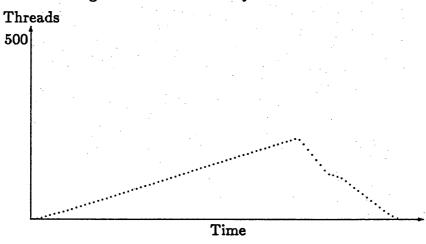

This calculation may be repeated in the different case of a single activity using a resource but which does not wait on requests until its queue of outstanding requests is full, for example a CPU fed by an asynchronous prefetch unit. With a maximum queue length of N and ratio of request bandwidth to resource bandwidth of  $\alpha$  elementary queuing theory gives S and  $q_i$ , defined as above:

$$q_i = \alpha^N$$

$$S = \frac{\alpha^{N+1} - 1}{\alpha - 1}$$

This is tabulated in Figure 3.1b.

Another difference between synchronous and asynchronous systems may be identified. The low-level non-determinism introduced by asynchronism has its cost in the consequent extra book-keeping to keep track of which user each operation belongs to. I will be considering hardware where the number of users is relatively small (the reason for this will become apparent in the next chapter), so the storage overhead of appropriately tagging requests is low.

However a problem arises with contextual data local to a user which is needed by a shared resource. This must either be cached near the resource and randomly accessed by the tag on each request, or queued with each request. Either strategy requires extra storage at least proportional to the maximum number of queued activities. This contrasts with a synchronous system in which no activity is queued and storage is minimal. The costs of asynchronism are illustrated by for example the Am29000 RISC CPU design [amd88]. In this processor throughput in a synchronous 4-stage pipeline is maintained by sophisticated hardware which keeps track of inter-instruction data dependencies and maximises instruction overlap. The registers to do this represent a large context which must be saved and restored on interrupts.

The designer is thus presented with a fundamental dilemma. In order to achieve freedom from latency design constraints where operations take variable lengths of time it is desirable that units cooperate asynchronously, however this results in extra overheads.

#### 3.2 Data Storage

How can the data needed by a computation most efficiently be stored? It is possible to address this question by considering different ways in which the data associated with a DEG can be mapped onto physical storage locations.

#### Abstract data and physical locations

In this dissertation I distinguish between abstract data and the use of physical locations. The use of an abstract datum is defined by two operations, creation and lookup. The creation of a datum associates with the value of the datum a name which may be used later to look up the datum. In this model of abstract data it is impossible to update a datum. This makes the use of abstract data functional (free from side effects) and so is particularly appropriate to concurrent computation. The update of physical locations in a computer will correspond to the reuse of a location by different abstract data. Efficient reuse of locations is part of the optimised compilation of single threads of computation, not part of the specification of concurrent computation, because any reuse of a location imposes some sequentiality on the computations that use it.

#### Static and dynamic names

A name may have both a static and a dynamic component. In the creation of heap a unique dynamic tag is used to access a tuple of data. Each datum in this tuple is thus named by the concatenation of the tuple's dynamic tag and a static tag that distinguishes between elements of the tuple. A dynamic name is generated non-deterministically at data creation time, a static name has a value that is known at compile time and will be correlated with other static data that make

<sup>&</sup>lt;sup>1</sup>More precisely: dynamic names are allocated in such a way that no name is reused, but other than this the client of name allocation can make no assumptions about the sequence of dynamic names which is released to it.

up a program. Every random access location in a computer has a fixed absolute name. This name will allow direct access to, or writing of, the contents of the location. The advantage of static name definition is that absolute names can be used directly resulting in efficient physical access to locations.

The distinction between static and dynamic data allocation, made here, is fundamental to any meaningful use of data in a computation. The specification of the computation consists of statically named data produced by a compiler, its execution will require extra dynamically named data. Static names are static with respect to a particular compilation, and associated other static data. There is in general no reason why in the course of a computation intermediate data should not be analysed and perhaps transformed, with newly static specification of subsequent computation resulting. The cost of global data analysis is such that this is not often done. Typically a compilation step will take more than a million times longer than a single subsequent data read, so it is not worth applying compiler techniques to intermediate results likely to have a limited lifetime.

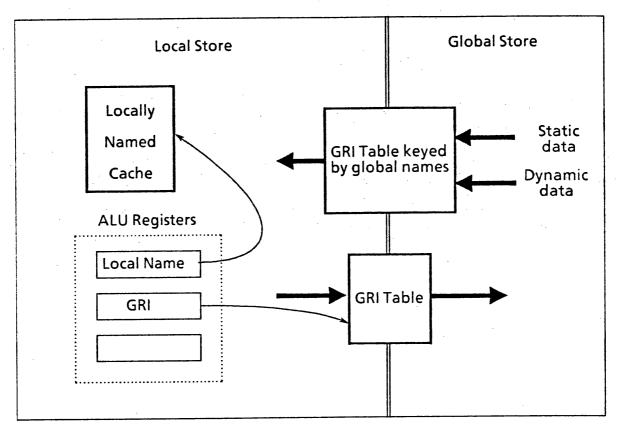

Dynamic cacheing of frequently used data can be seen to be a way of utilising some of the advantages of static names without the cost of global compilation. The absolute cache entry tags associated with a global name may index directly into a small fast data store. However the cost of cacheing a new global name is relatively small. A general theory of data use must allow the same abstract datum access by different names within different local contexts, where the datum may be cached in different physical locations. A way of formalising this is described in the next section.

#### 3.2.1 Cache theory

A cache is a local memory within which frequently used data can be stored. This is managed by using local names (corresponding to the absolute names of the cache locations) and maintaining a dynamic mapping from local to global names. With respect to a particular cache at a given time any datum may be local, global, or shared. If the latter then its global and local names must be associated by the cache. Cache will be used here for both compiler-named local state (registers) and programmer-invisible fast storage (often called cache memory) which is automatically allocated. This will allow different strategies for cacheing to be compared and contrasted. The distinction between these two methods is very apparent to a compiler-designer, less so to a CPU designer where they represent methods of achieving the same end.

A datum may be created inside a cache by an ALU and return a dynamic local name which is also its absolute location name. This datum remains local until either its name is passed out of or its location is flushed from the cache. It must then be associated with a global name, and becomes a shared datum. When both the datum has been flushed and no local names to the datum remain in the cache the datum becomes global and uses no resources inside the cache.

Conversely a global datum may be cached by finding a free cache location and copying its value to the location. While a datum is shared, within the cache, its

global and local names are synonymous. However access from a local name is quicker because it does not require associative name mapping. The disadvantage of holding local name references in the cache is that they must be converted to global names when the datum is flushed from the cache.

Optimisation of local data in a cache becomes of interest when a high proportion of data created in the cache is of limited life and so can be garbage collected while still local. This sort of garbage collection within a cache has the function of localising data in the cache: the management overhead of the data is invisible outside the cache.

Single thread uniprocessors do not make use of garbage collection within caches. This would be surprising to an unbiased naive investigator, since a high proportion of intermediate data in most computation are short-lived. The reason lies in the very special optimisation that single thread compilation can make of data use. The study of computation has a heavy historical bias towards von Neumann sequential processing. The explicit reuse of datum locations is built into the structure of most high level languages as assignment to variables and so what is in single thread computation a useful static (compile-time) optimisation of data use has become a standard execution model. A major part of the technology of optimising compilers for von Neumann machines is concerned with the management of this mapping (see Aho, Sethi and Ullman [ASU86] pp 513-722).

In arguing this I am neither advocating the use of functional programming languages on aesthetic grounds, nor diminishing the importance of explicit static location reuse to all implementation. It is however a technique which works only for locations used by a single thread and it may not be so useful in the execution of concurrent computation. Certainly the model of non-destructive data use, presented here, is most appropriate for describing concurrent computation. Within it the reuse of locations can be evaluated as an optimisation free from the preconceptions that single thread implementation has imposed. When thinking in general about the use of data in a computation it is more natural to use a non-destructive abstract model of data use to specify computation, and then consider desirable optimisations.

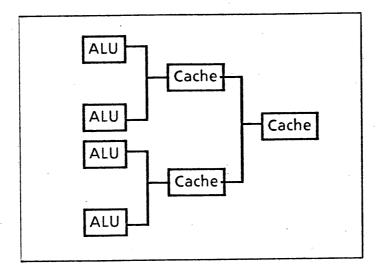

#### 3.2.2 Cache hierarchies

In uniprocessor designs we can sometimes consider cache hierarchies to be totally ordered sets (or equivalently linear unidirectional graphs). Separate instruction and data caches require a more complicated model, as do multiprocessor designs, where more than one ALU must be fed with data. Two possible extensions to this, in order of increasing generality, are for the hierarchies to have the structure of trees or directed acyclic graphs.

A tree hierarchy of caches contains nodes each of which is equivalent to a number of separate caches with global name spaces identified. A datum is cached by a node if it is local to any of its constituent caches. If a datum is cached by any two nodes it will be cached by every node on the unique path that connects them in the tree.

A node may be implemented by a number of local caches communicating with a shared global memory. In the tree structure communication between processors has much the same implementation as global data access. Any access which does not hit in a node will proceed towards the root of the hierarchy until it can be satisfied.

A complication results from the nature of inter-thread reference. In order to maximise concurrency it must be possible to export references (names) of threads which have not yet finished. These may be read and will result in synchronisation waits for the reading ALUs until they complete. The synchronisation management will happen at the level of the outermost cache node within which the thread has been exported, in other words the innermost cache node which covers both source and destination ALUs of the thread result.

This necessitates that the value of a thread be transferred to all nodes that cache it on the path between its ALU and the hierarchy root as soon as it is available. In the common case that a thread is read only once this method of communication is inefficient. Efficient communication within one node can happily be accomplished by a snoopy bus. Snoopy bus is a vague term used to cover busses in which each access is monitored by all bus users who source their own data as necessary. In non-destructive data use there is no need to share modifiable data and so snoopiness is merely a way of replacing two shared memory accesses by one user-to-user bus transfer. see

A tree cache hierarchy is only scalable if most data reference can be kept local to twigs of the hierarchy. This is not in general possible, as will be seen in Chapter 5. A scalable cache hierarchy must have multiple path, and hence high bandwidth, global data transfer.

A Direct Acyclic Graph (DAG) cache hierarchy may be used to provide this. The basic component of a DAG hierarchy is a node as in a tree but with multiple outgoing (from the ALU) connections. Each shared datum will have a global name on just one of these connections. A DAG hierarchy thus behaves like a switching communications network. A datum cached in a node of the hierarchy will be accessible by the processors that the node covers, nodes in outer levels of the hierarchy cover increasing numbers of ALUs—every outermost node covers all ALUs. An example of such a system would arise if cache nodes were to be integrated into, for example, a delta network [JHP79] as proposed for ALICE [MDF\*87] or Project Flagship [WW87].

In a DAG hierarchy different data follow different paths through the hierarchy. Names of threads may thus be exported along a different path from that required in their reading, so every name must contain itself enough information to find where it is cached. This means that names must be passed outwards through the hierarchy by hashes on their addresses, at the outermost level each name must cache in just one node. It is difficult to predict what level in the hierarchy will be needed in reading of a datum, so all data must be written through to the outermost level of the cache. Storage in a dag hierarchy has two uses: a hit early in the hierarchy has lower latency than one at the outermost level, and multiple reads may be satisfied with traffic at a low level in the hierarchy. This use of

storage may be compared with broadcast bandwidth optimisation, where node storage is used to queue requests rather than data.

#### Mapping between local and global names

In a cache the administration cost of name mapping is critical. In general the more flexible the cache name mapping the more its hardware cost. A simple strategy is for each global name to map to a unique local name got by hashing its address. This hash can be simple, usually it is just the global address modulo some power of two. This allows efficient lookup directly from the global name, but suffers from a poor hit rate when the hashes of global names which are used together clash.

A more complicated strategy is to have a local cache content addressable on the full global name of the cached datum, and a cache replacement policy which tries to keep frequently used data in the cache. A typical high performance uniprocessor cache will use global name hashing into sets of a small number of content addressable locations.

An interesting possibility is for local to global name mapping to occur only on the interface between the cache and outer caches. Inside the cache all shared names are local and access the cache directly. Flushing of a name from the cache requires the renaming of all of its instances within the cache. This renaming can be accomplished in a single content addressable update operation. Section 3.2.4 investigates the advantages of a small cache of this sort close to an ALU—one of these is a reduction in word length of the ALU. Note that for this to be possible all internal CPU address-holding registers must be regarded as part of the cache and so modifiable as described below.

#### 3.2.3 Data management

In uniprocessor CPUs data use is classified into, for example, code, stack and heap, for each of which different storage strategies are used. Stack data is taken to include all purely local or temporary values which are of limited scope, and heap includes permanently allocated (static) data. The efficient use of data depends on three things:

- How many times is the data to be referenced?

- How can it be established that the data is no longer needed?

- Can access of abstract data be mapped onto a small static name space corresponding to physical registers?

In order to investigate data use in concurrent computation we can look at the characteristics of the data used in a DEG.

#### Data in a DEG

The data needed by an ALU in the execution of a DEG may be classified into three categories:

Control data. Data needed to identify those nodes in the DEG which have been created but not yet fired. The control data must also distinguish between those nodes which are waiting on data and those which have data available and so may be fired.

In a conventional von Neumann compiled program control data comprises a code pointer and set of return addresses, managed dynamically, together with static flow control information embedded in code. Control data is thus highly static with only a small amount of dynamic data from conditional branches and indirect jumps. The disadvantage of this is the consequent statically defined synchronous execution order of ALU operations.

Code. Static data used to define the DEG and perhaps determine explicitly data allocation to locations or ALU operation order.

Intermediate data. Data on D-arcs in the DEG that is dynamically created and must be stored until it is no longer needed. The data associated with heap cannot usually be associated in any way with the ALU operations that use it because it is difficult to establish where, if anywhere, in the future evolution of a DEG a datum will be used.

In single-threaded compilation of a DEG most intermediate data can be stored in a FILO stack with data access happening only at the top of the stack. This leads to optimised storage in registers or a RISC multiple window register bank [TS83]. The tradeoffs here between register, shift register, and random access register bank cacheing are between cost of register access and cost of register update on stack push or pop.

In multiple thread compilation each thread requires a separate stack, since by definition different threads are asynchronous. These are much more difficult efficiently to localise, because localisation in fixed registers or a single stack incurs a high context switch cost on thread switching. This cost is fundamental where CPU cacheing relies on the FILO nature of intermediate data use to optimise data storage. The latency vs. synchronisation dilemma examined by Arvind and Ianucci [AI86], see Section 4.5.1, is a direct consequence of this and the use of thread switching to hide latency.

The structure of intermediate data use in multiple thread computation is that of a dynamically constructed acyclic graph. Each thread uses local data on a stack which may at any time be forced to wait on the completion of one or more other threads. Access to data on the active ends of stacks requires random access of a cache, however physical locations can still be reused.

The concurrent equivalent of a single thread stack is thus a random access cache of stack frames with explicit garbage collection of frames on function exit.

The efficiency of this sort of cache, contrasted with a von Neumann cache, depends on the way in which threads are scheduled and is examined in Chapter 5.1.

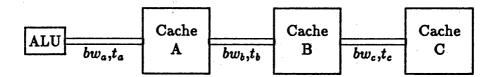

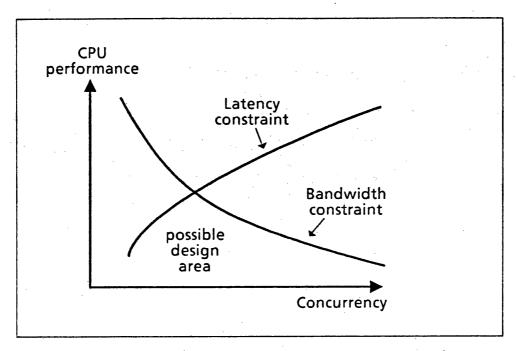

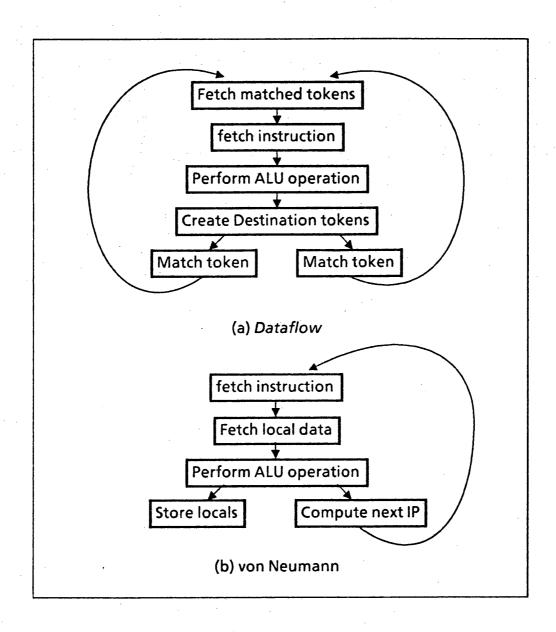

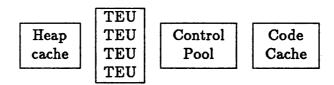

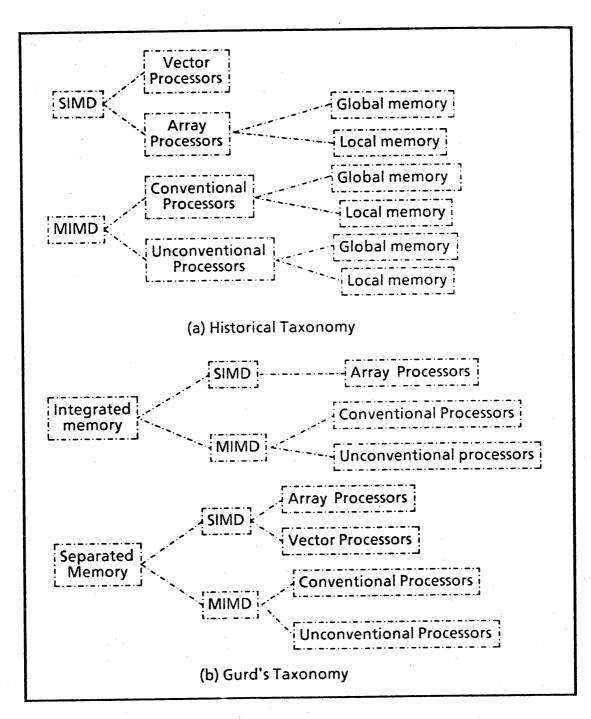

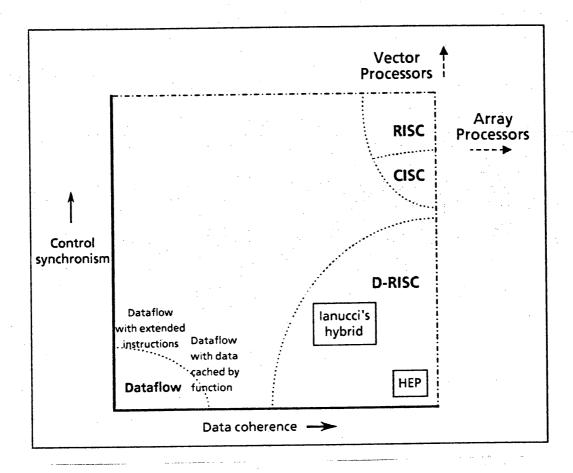

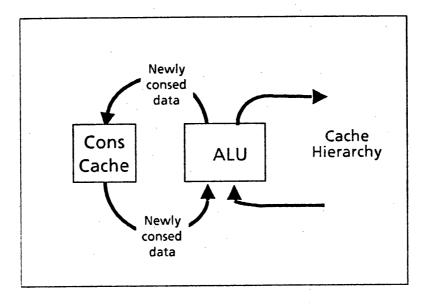

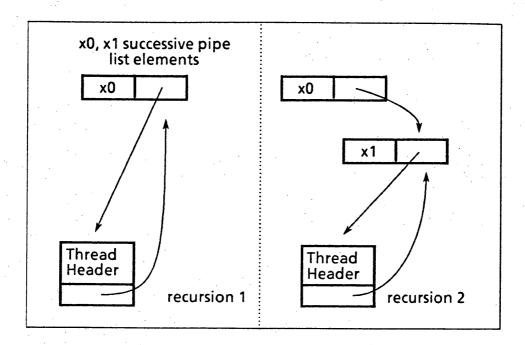

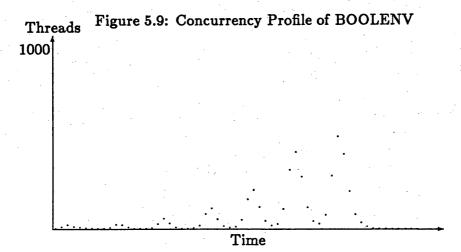

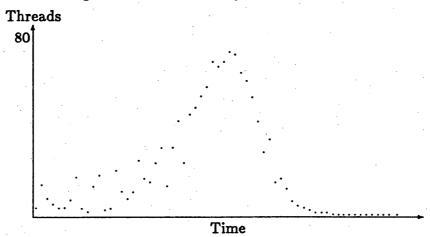

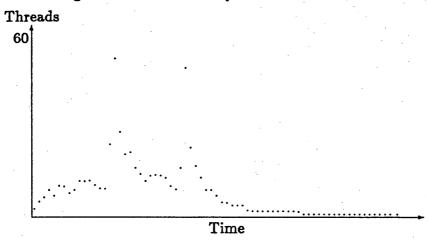

#### Garbage collection