Number 165

# Fast packet switching for integrated services

Peter Newman

March 1989

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

#### © 1989 Peter Newman

This technical report is based on a dissertation submitted December 1988 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Wolfson College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Contents

| Li       | st of       | Figures                                   | xi                     |

|----------|-------------|-------------------------------------------|------------------------|

| Li       | ${f st}$ of | Tables                                    | xiv                    |

| G.       | lossa       | ry of Terms                               | $\mathbf{x}\mathbf{v}$ |

| 1.       | Intr        | oduction                                  | 1                      |

|          | 1.1         | Objectives                                | 2                      |

|          | 1.2         | Outline                                   | 2                      |

|          | 1.3         | Growth of Communications Networks         | 3                      |

|          | 1.4         | Multi-Service Traffic                     | 7                      |

| <b>2</b> | Sta         | tistical Switching Mechanisms             | 9                      |

|          | 2.1         | Multiplexing                              | 9                      |

|          | 2.2         | Switching Mechanisms                      | 11                     |

|          | 2.3         | Evolution of the Packet Switch            | 16                     |

|          | 2.4         | Fundamentals of Fast Packet Switch Design | 19                     |

|          | 2.5         | Summary                                   | 21                     |

| 3        | Fas         | t Packet Switch Architecture              | 23                     |

|          | 3.1         | A Simple Classification of Switch Designs | 23                     |

|          | 3.2         | Input Buffered Switches                   | 25                     |

|          | 3.3         | Output Buffered Switches                  | 28                     |

|          | 3.4         | Internally Buffered Switches              | 32                     |

|          | 3.5         | Performance Comparison                    | 37                     |

|          | 3.6         | Summary                                   | 38                     |

| 4 | Mu  | Iti-Stage Interconnection Networks          | 41 |

|---|-----|---------------------------------------------|----|

|   | 4.1 | An Introduction to Interconnection Networks | 41 |

|   | 4.2 | The Crossbar Network                        | 46 |

|   | 4.3 | Banyan Networks                             | 47 |

|   | 4.4 | The Clos Network                            | 50 |

|   | 4.5 | The Beneš Network                           | 50 |

|   | 4.6 | The Batcher Sorting Network                 | 52 |

|   | 4.7 | Summary                                     | 53 |

| 5 | Des | ign of the Cambridge Fast Packet Switch     | 55 |

|   | 5.1 | Binary Routing Networks                     | 55 |

|   | 5.2 | Design Issues                               | 57 |

|   | 5.3 | The Switching Mechanism                     | 59 |

|   | 5.4 | The Switch Fabric                           | 61 |

|   | 5.5 | The Multi-Plane Switch Structure            | 66 |

|   | 5.6 | Summary                                     | 68 |

| 6 | Swi | tch Fabric Performance                      | 69 |

|   | 6.1 | Traffic Models                              | 69 |

|   | 6.2 | The Simulation Model                        | 70 |

|   | 6.3 | The Crossbar Switch Fabric                  | 72 |

|   | 6.4 | The Delta Network                           | 75 |

|   | 6.5 | The Beneš Network                           | 80 |

|   | 6.6 | Summary                                     | 83 |

| 7 | Per | formance for Multi-Service Traffic          | 85 |

|   | 7.1 | Multi-Service Traffic Requirements          | 85 |

|   | 7.2 | Extensions to the Switch                    | 87 |

|   | 7.3 | Traffic Models                              | 87 |

|   | 7.4 | Poisson Traffic                             | 88 |

|   | 7.5 | Talkspurt Voice                             | 92 |

|   | 7.6 | Packet Length                               | 94 |

|   | 7.7 | Buffer Overflow                             | 95 |

|   | 7.8 | Discussion                                  | 96 |

|                      | 7.9   | Summary                                              | 98  |

|----------------------|-------|------------------------------------------------------|-----|

| 8                    | Imp   | lementation of the Fast Packet Switch                | 101 |

|                      | 8.1   | An Experimental Implementation                       | 101 |

|                      | 8.2   | The Switching Element                                | 102 |

|                      | 8.3   | The Input Port Controller                            | 106 |

|                      | 8.4   | Performance Measurements                             | 107 |

|                      | 8.5   | Towards a Full-Scale Switch Implementation           | 108 |

|                      | 8.6   | Summary                                              | 114 |

| 9                    | Con   | clusion                                              | 115 |

|                      | 9.1   | Summary                                              | 115 |

|                      | 9.2   | Discussion                                           | 119 |

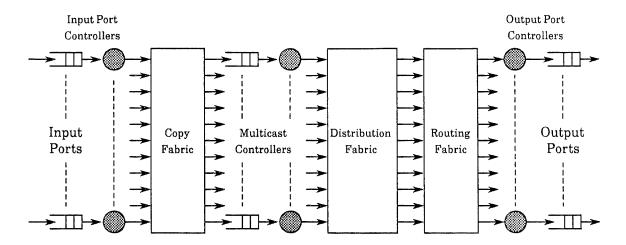

|                      | 9.3   | Multicast Operation                                  | 121 |

|                      | 9.4   | Network Aspects                                      | 123 |

| Aı                   | ppen  | dix: Simulation results for throughput at saturation | 127 |

| $\mathbf{R}\epsilon$ | efere | nces                                                 | 135 |

# List of Figures

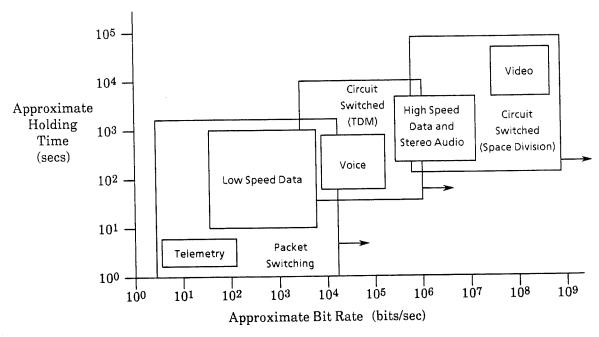

| 1.1  | Relationship between bit rate and holding time for various classes of traffic and switching mechanisms | 8          |

|------|--------------------------------------------------------------------------------------------------------|------------|

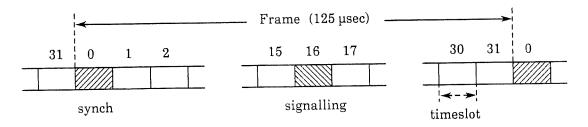

| 2.1  | An example of time division multiplexing (TDM)                                                         | 0          |

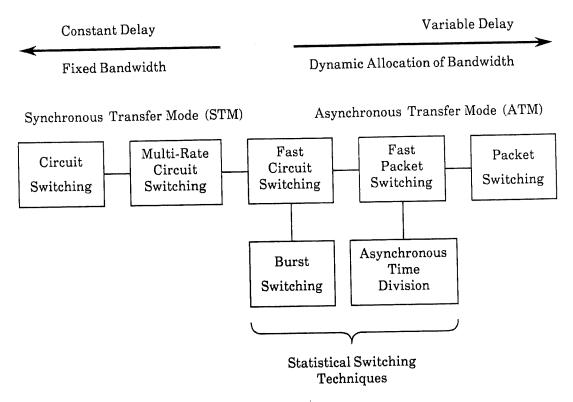

| 2.2  | The spectrum of switching mechanisms                                                                   | 2          |

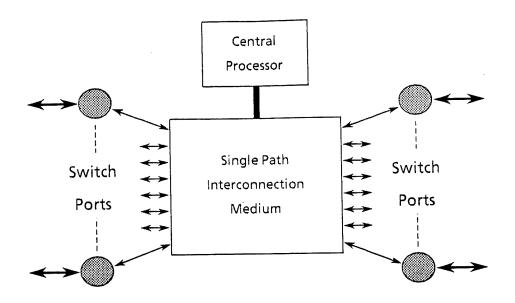

| 2.3  | A single path decentralised packet switch                                                              | 7          |

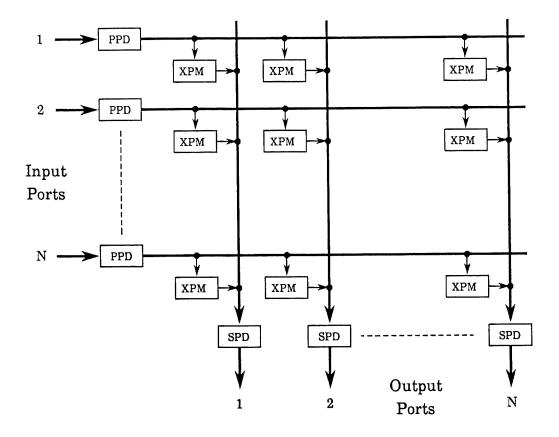

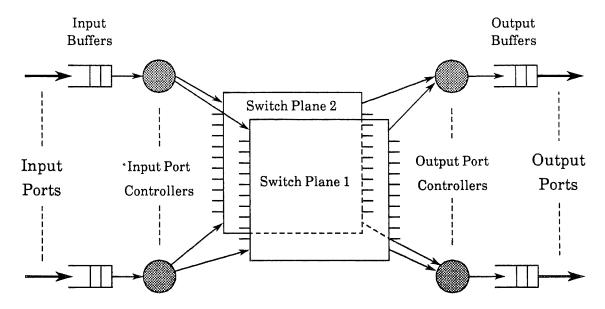

| 2.4  | General structure of a fast packet switch                                                              | 9          |

| 3.1  | A simple classification of fast packet switch design                                                   | 4          |

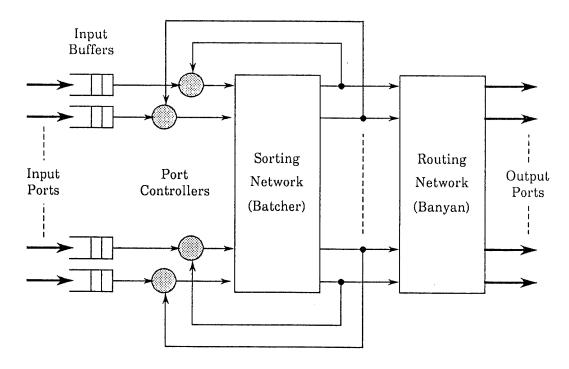

| 3.2  | Basic structure of the three phase Batcher-banyan switch                                               | 26         |

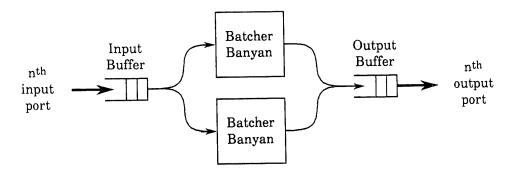

| 3.3  | A two-plane switch structure                                                                           | 27         |

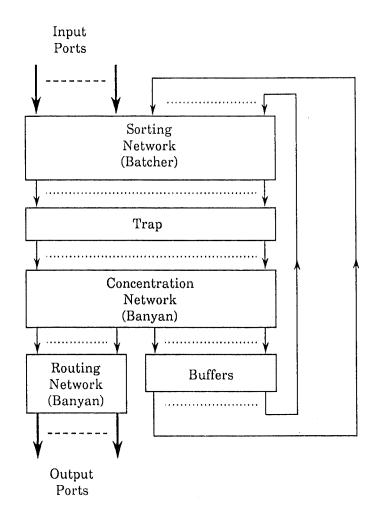

| 3.4  | The Starlite fast packet switch                                                                        | 8          |

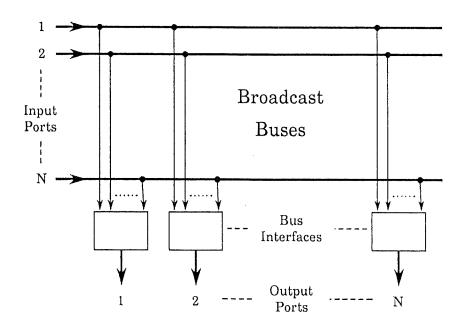

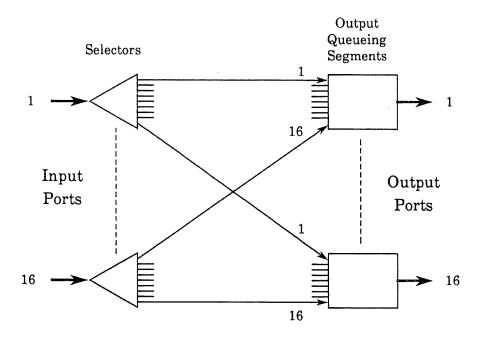

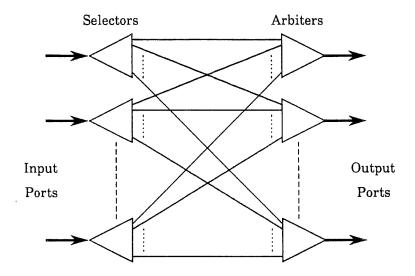

| 3.5  | Structure of the Knockout Switch                                                                       | 0          |

| 3.6  | The bus interface of the Knockout Switch                                                               | 31         |

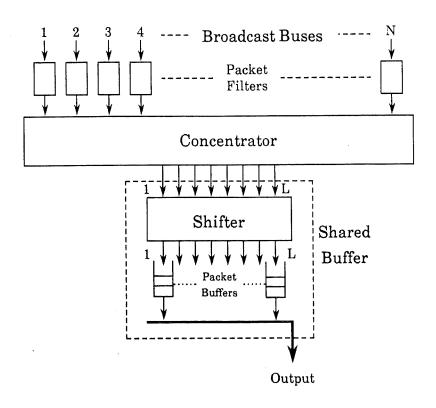

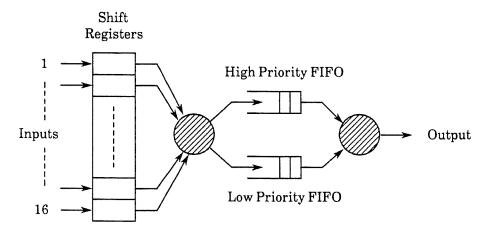

| 3.7  | Structure of the Prelude switching element                                                             | 3          |

| 3.8  | Structure of the Bus Matrix switching element                                                          | 34         |

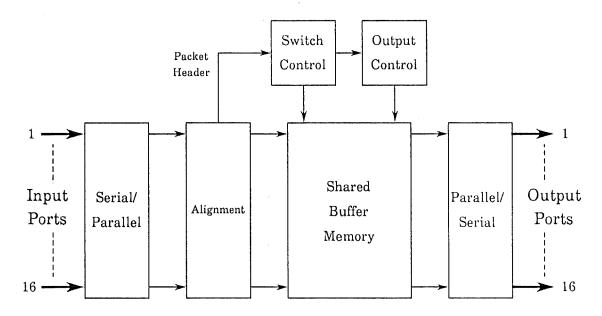

| 3.9  | Structure of the IBM switching element                                                                 | 35         |

| 3.10 | The output queueing segment of the IBM switching element 3                                             | 35         |

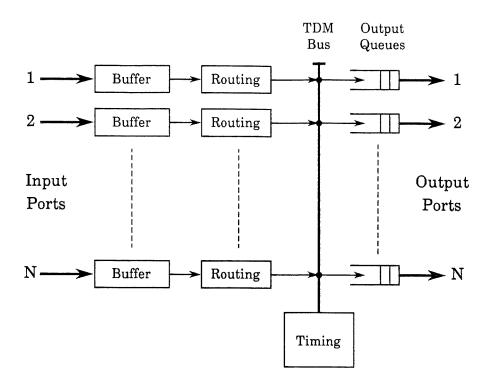

| 3.11 | Structure of the TDM Bus switching element                                                             | 86         |

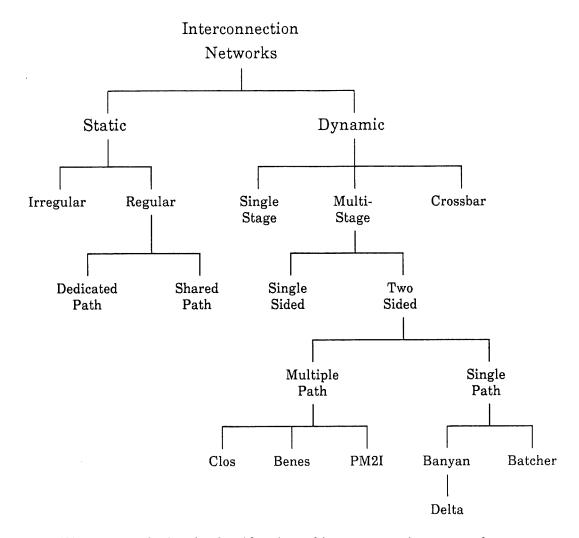

| 4.1  | A simple classification of interconnection networks                                                    | 2          |

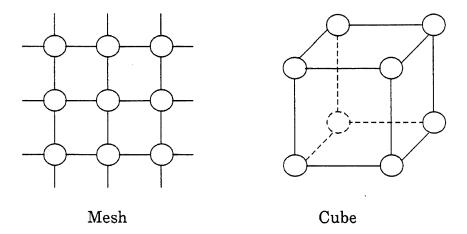

| 4.2  | Examples of regular static network topologies                                                          | 3          |

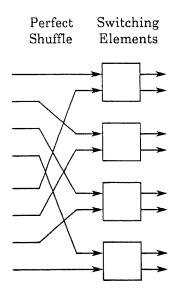

| 4.3  | A single stage 8×8 shuffle exchange                                                                    | 4          |

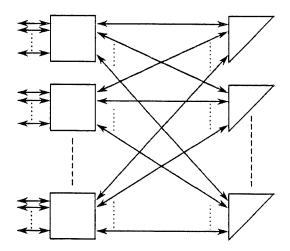

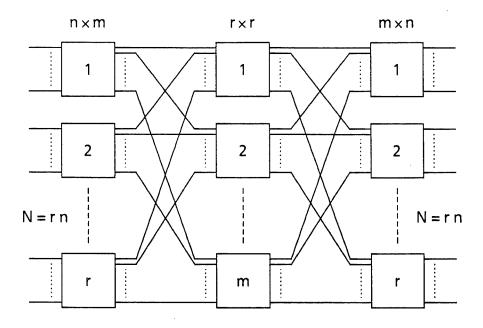

| 4.4  | A single sided Clos network                                                                            | 4          |

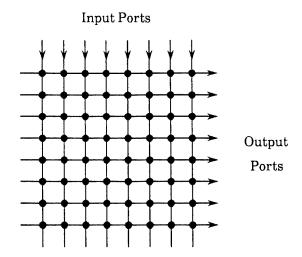

| 4.5  | The general representation of a crossbar network                                                       | Į7         |

| 4.6  | A self-routing crossbar switch                                                                         | Į7         |

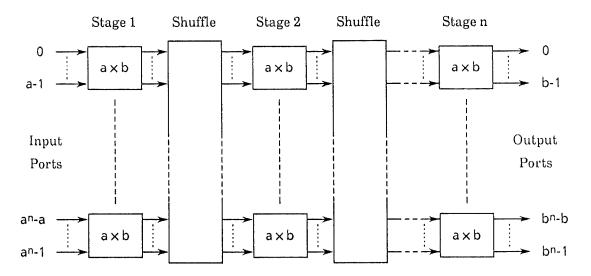

| 4.7  | The general structure of a delta network                                                               | <b>L</b> S |

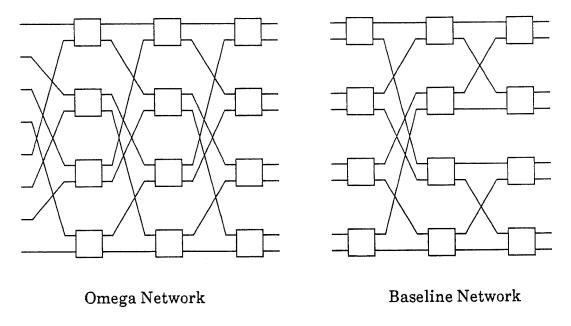

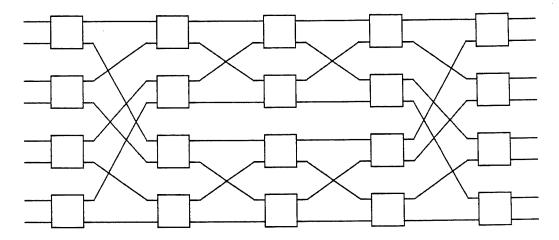

| 4.8  | Examples of 8×8 delta networks constructed from 2×2 switching elements                                                             | 50  |

|------|------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.9  | A square three stage Clos network                                                                                                  | 51  |

| 4.10 | An 8×8 Beneš network constructed from 2×2 switching elements.                                                                      | 51  |

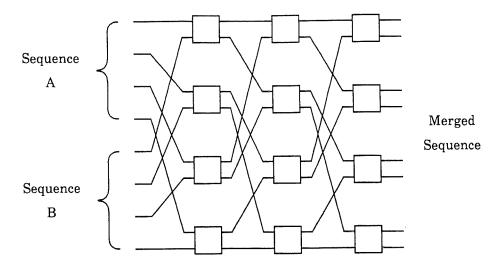

| 4.11 | An 8×8 bitonic sorter                                                                                                              | 53  |

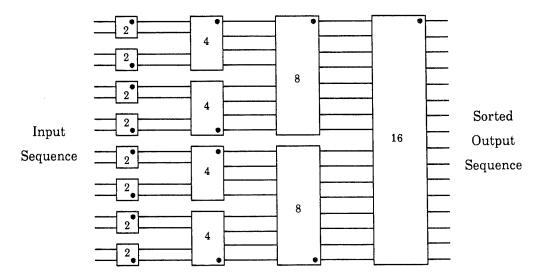

| 4.12 | A $16 \times 16$ full sorter                                                                                                       | 53  |

| 5.1  | The structure of a buffered binary routing node                                                                                    | 56  |

| 5.2  | The basic structure of the Cambridge Fast Packet Switch                                                                            | 60  |

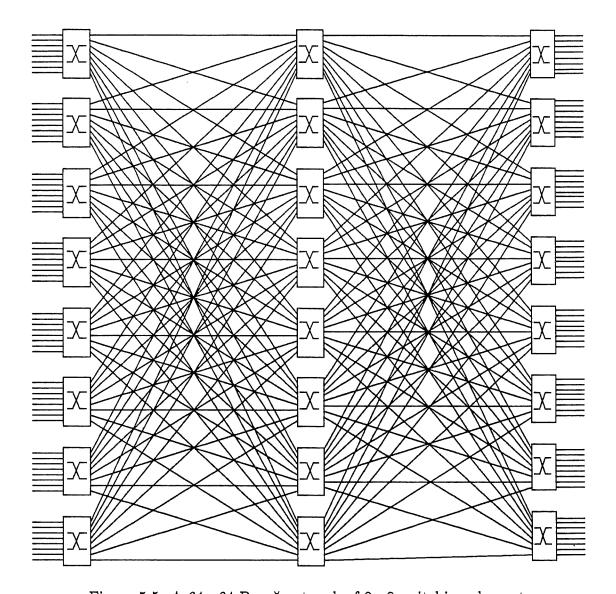

| 5.3  | A $64 \times 64$ delta network of $8 \times 8$ switching elements                                                                  | 62  |

| 5.4  | A $16 \times 16$ modified delta network of $8 \times 8$ switching elements                                                         | 63  |

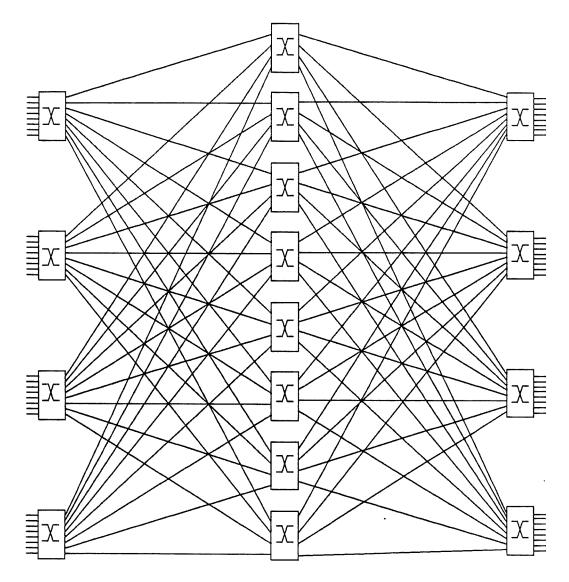

| 5.5  | A 64×64 Beneš network of 8×8 switching elements                                                                                    | 65  |

| 5.6  | A 32×32 sub-equipped Beneš network of 8×8 switching elements.                                                                      | 66  |

| 5.7  | A two-plane switch structure                                                                                                       | 67  |

| 6.1  | Throughput at saturation for the crossbar switch fabric                                                                            | 72  |

| 6.2  | Analysis and simulation of mean delay performance for slotted traffic.                                                             | 74  |

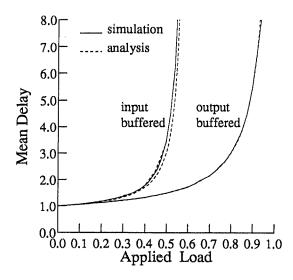

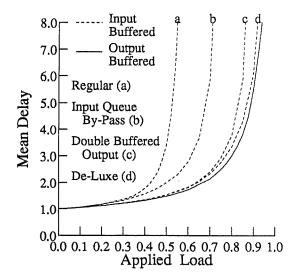

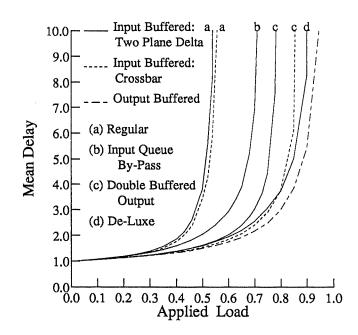

| 6.3  | Mean delay performance of crossbar switch structures for slotted traffic                                                           | 74  |

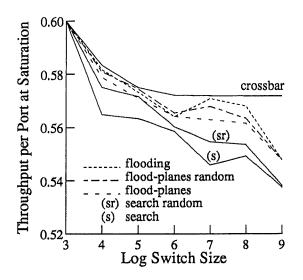

| 6.4  | Throughput at saturation for single plane input buffered flooding delta networks                                                   | 75  |

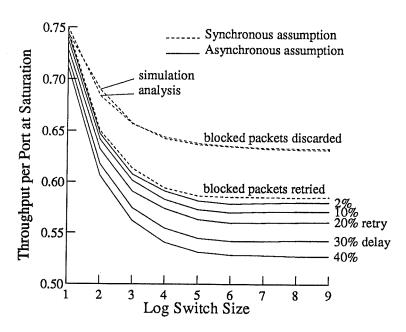

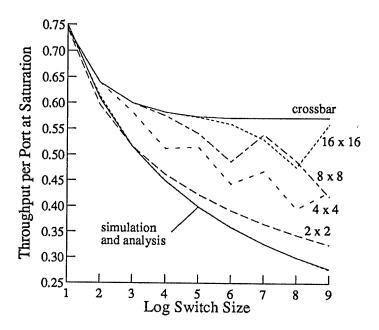

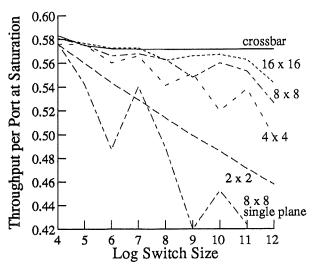

| 6.5  | Throughput at saturation for multiple delta networks in parallel                                                                   | 77  |

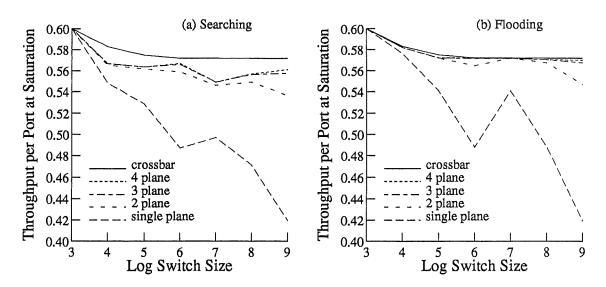

| 6.6  | Comparison of algorithms to select a free path across the network.                                                                 | 78  |

| 6.7  | Throughput at saturation for two-plane pure input buffered delta networks                                                          | 78  |

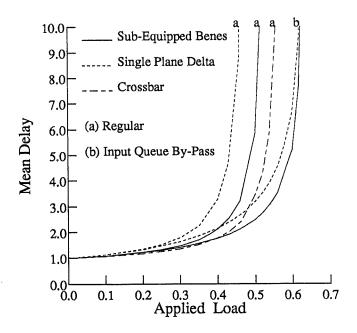

| 6.8  | Comparison of mean delay performance for slotted traffic of various switch structures of size $64 \times 64$                       | 79  |

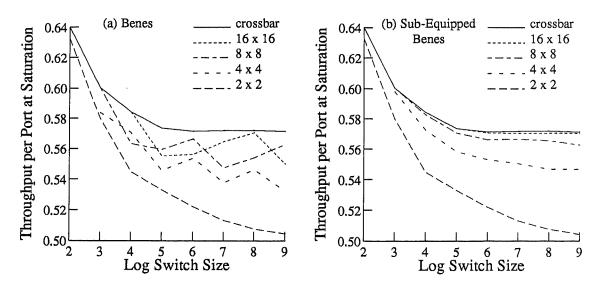

| 6.9  | Throughput at saturation for flooding Beneš structures                                                                             | 81  |

| 6.10 | Comparison of mean delay performance for slotted traffic of $64 \times 64$ sub-equipped Beneš networks against other structures    | 82  |

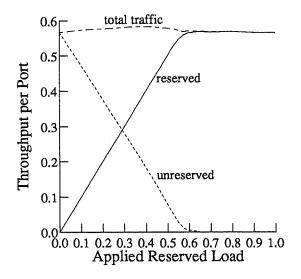

| 7.1  | Throughput performance for the Poisson reserved service + saturated unreserved service traffic model                               | 89  |

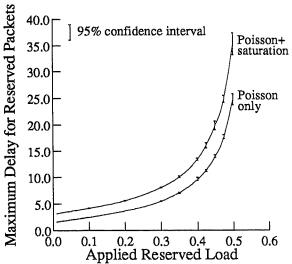

| 7.2  | Maximum reserved service packet delay for the Poisson reserved service traffic model with and without saturated unreserved service | 0.0 |

|      | traffic                                                                                                                            | 89  |

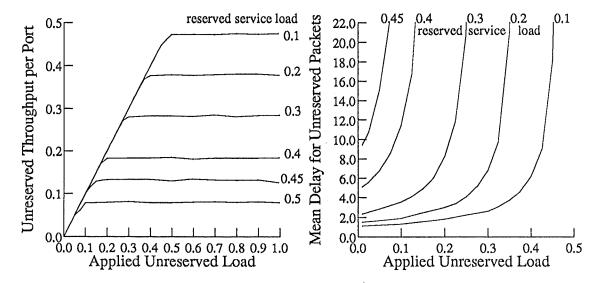

| 7.3 | Unreserved service throughput performance for the Poisson reserved service + Poisson unreserved service traffic model                                        | 90  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.4 | Mean unreserved service packet delay for the Poisson reserved service + Poisson unreserved service traffic model                                             | 90  |

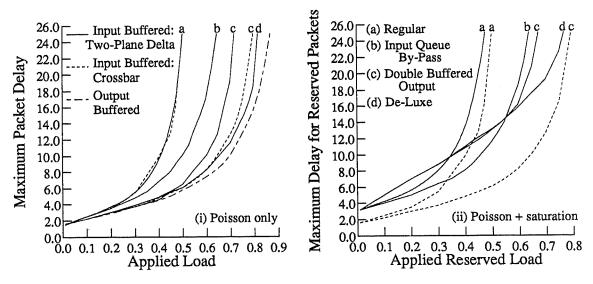

| 7.5 | Comparison of maximum delay performance of various switch designs of size 64×64 for Poisson traffic with and without saturated unreserved service traffic    | 91  |

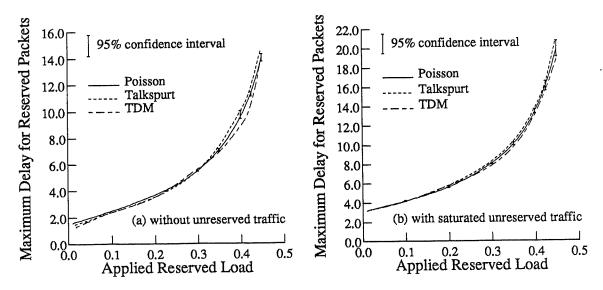

| 7.6 | A comparison of maximum reserved service packet delay for Poisson, talkspurt and TDM voice models both with and without saturated unreserved service traffic | 93  |

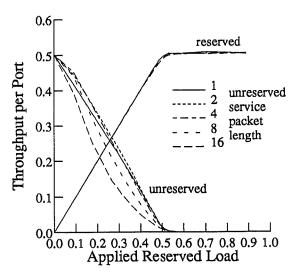

| 7.7 | Effect of unreserved service packet length on throughput performance for the Poisson reserved service + saturated unreserved service traffic model           | 94  |

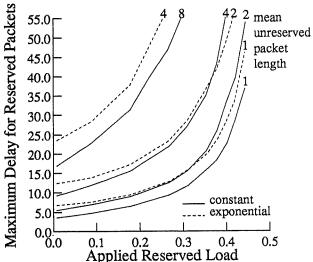

| 7.8 | Effect of unreserved service packet length, constant and exponentially distributed, on maximum reserved service packet delay                                 | 94  |

| 7.9 | Buffer overflow probability for the input buffered crossbar switch                                                                                           | 96  |

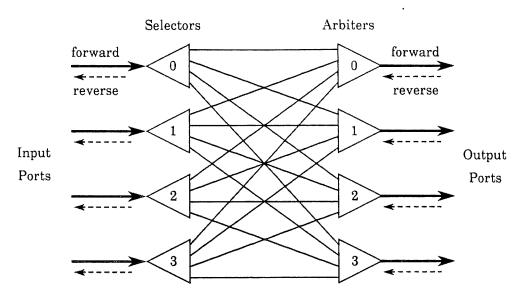

| 8.1 | Structure of the 4×4 crossbar switching element                                                                                                              | 102 |

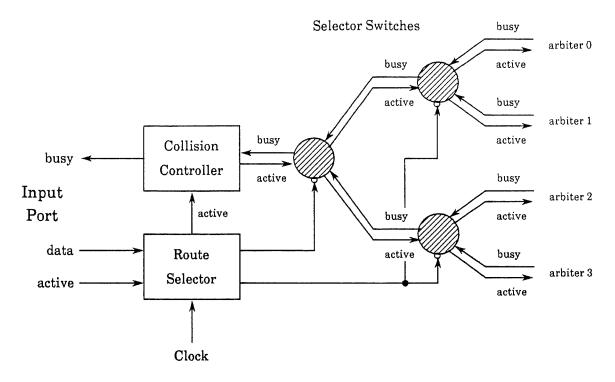

| 8.2 | Implementation of a 1 to 4 selector                                                                                                                          | 104 |

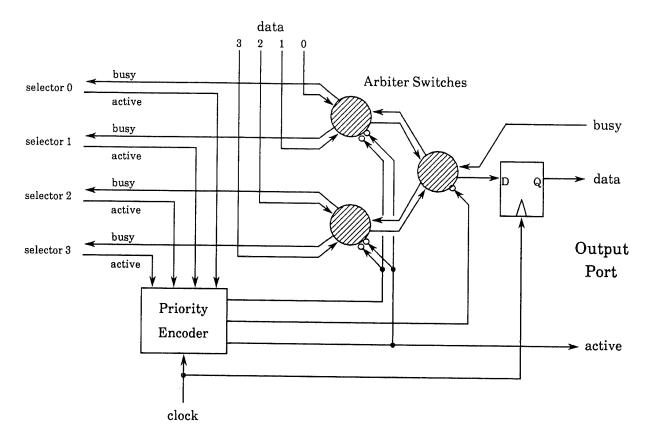

| 8.3 | Implementation of a 4 to 1 arbiter                                                                                                                           | 105 |

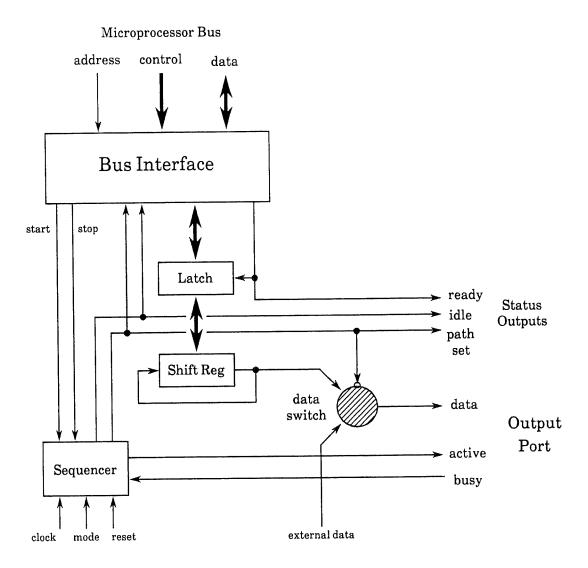

| 8.4 | The experimental input port controller                                                                                                                       | 107 |

| 8.5 | Structure of a fast packet switch implementation                                                                                                             | 109 |

| 8.6 | The I/O port controller                                                                                                                                      | 110 |

| 9.1 | Switch structure for multicast operation                                                                                                                     | 122 |

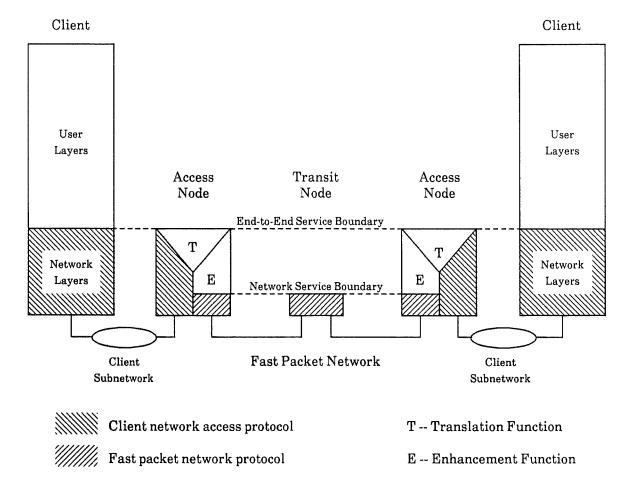

| 9.2 | General model of protocol structure for a network of fast packet switches.                                                                                   | 124 |

# List of Tables

| 1.1 | Multi-service traffic characteristics                                                                               | 7   |

|-----|---------------------------------------------------------------------------------------------------------------------|-----|

| 6.1 | Switch fabric design parameters                                                                                     | 70  |

| 6.2 | Percentage error in throughput at saturation of simple model for delta networks with switching elements of degree 8 | 79  |

| 6.3 | Percentage error in throughput at saturation of simple model for single plane delta networks                        | 80  |

| 7.1 | Comparison of maximum delay performance of various 64×64 switch designs at maximum reserved service traffic load    | 92  |

| 8.1 | Estimated complexity of crossbar switching elements                                                                 | 112 |

| 8.2 | Approximate maximum bandwidth per switch port for various implementation technologies                               | 113 |

| A.1 | Throughput at saturation for crossbar switch fabrics                                                                | 127 |

| A.2 | Throughput at saturation of delta networks with switching elements of degree 2 for a searching algorithm            | 128 |

| A.3 | Throughput at saturation of delta networks with switching elements of degree 4 for a searching algorithm            | 128 |

| A.4 | Throughput at saturation of delta networks with switching elements of degree 8 for a searching algorithm            | 129 |

| A.5 | Throughput at saturation of delta networks with switching elements of degree 16 for a searching algorithm           | 129 |

| A.6 | Throughput at saturation of delta networks with switching elements of degree 2 for a flood-planes algorithm         | 130 |

| A.7 | Throughput at saturation of delta networks with switching elements of degree 4 for a flood-planes algorithm         | 130 |

| A.8 | Throughput at saturation of delta networks with switching elements of degree 8 for a flood-planes algorithm         | 131 |

| A.9  | Throughput at saturation of delta networks with switching elements of degree 16 for a flood-planes algorithm | 131 |

|------|--------------------------------------------------------------------------------------------------------------|-----|

| A.10 | Throughput at saturation of sub-equipped Beneš networks with switching elements of degree 2                  | 132 |

| A.11 | Throughput at saturation of sub-equipped Beneš networks with switching elements of degree 4                  | 132 |

| A.12 | Throughput at saturation of sub-equipped Beneš networks with switching elements of degree 8                  | 133 |

| A.13 | Throughput at saturation of sub-equipped Beneš networks with switching elements of degree 16                 | 133 |

#### Glossary of Terms

ATD: Asynchronous Time Division, (see page 5).

ATM: Asynchronous Transfer Mode, (see page 5).

BiCMOS: A high speed implementation technology integrating both bipolar and

CMOS devices on the same integrated circuit, (see page 113 and ta-

ble 8.2).

B-ISDN: Broadband ISDN, (see page 5).

CAD: Computer Aided Design.

CAM: Computer Aided Manufacture.

CATV: Community Antenna Television, i.e. cable TV.

**CCITT:** The International Telegraph and Telephone Consultative Committee.

CMOS: Complementary Metal Oxide Semiconductor — An implementation

technology, (see page 112 and table 8.2).

**DTDM:** Dynamic TDM, (see page 11).

ECL: Emitter Coupled Logic — A high speed implementation technology,

(see page 113 and table 8.2).

FDDI: Fiber Distributed Data Interface — A high speed local area network.

FIFO: First In First Out — A queueing discipline.

GaAs: Gallium Arsenide — A very high speed implementation technology,

(see page 113 and table 8.2).

HCMOS: High speed CMOS — An implementation technology, (see page 101).

HDLC: High-level Data Link Control — A popular data link layer protocol.

I/O: Input/Output.

**ISDN:** Integrated Services Digital Network, (see page 5).

LAN: Local Area Network, (see page 3).

MAN: Metropolitan Area Network, (see page 4).

PABX: Private Automatic Branch Exchange — A private telephone exchange.

STM: Synchronous Transfer Mode, (see page 5).

TASI: Time Assignment Speech Interpolation, (see page 13).

**TDM:** Time Division Multiplexing, (see page 9).

TTL: Transistor Transistor Logic — An implementation technology.

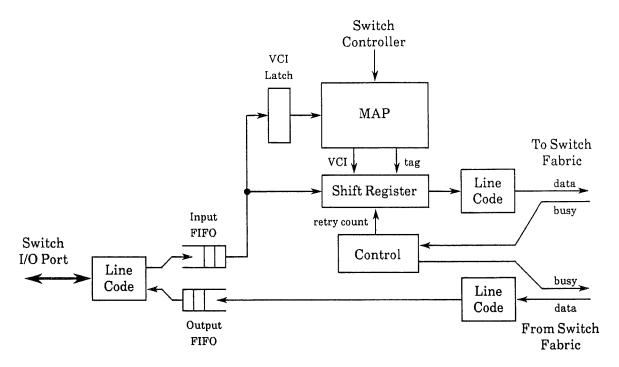

VCI: Virtual Circuit Indicator, (see page 109).

VLSI: Very Large Scale Integration — An integrated circuit containing a large number of active devices.

# Chapter 1

#### Introduction

For many years voice telephony remained the dominant service supported by the telecommunications networks throughout the world. To support a single class of traffic only a single switching mechanism was required: circuit switching, which was well suited to the characteristics of voice traffic. Within the past twenty years the growth of the computer industry has led to the requirement that telecommunications networks offer computer communications services, originally aimed mainly at file transfer and terminal to host interconnection. Although the circuit switched telephony network has been used to support such applications it has proved inefficient and inadequate thus we have seen the development of packet switched networks to support computer communications traffic. Recently, with the rapid drop in the cost of computer technology has come the requirement to support many more communications services. Examples include voice, high quality audio, broadcast quality video, compressed video, image, facsimile, text and many forms of data transfer. The existing practice of providing a separate network, with its own switching mechanism, for every class of traffic cannot be extended to support the demand forecast for many new communications services. The most flexible solution is that of an integrated communications network with a single switching mechanism capable of handling all classes of traffic. Fast packet switching has been suggested as a possible switching mechanism to support integrated services.

If fast packet switching is to support the growth in demand for communications services for the foreseeable future, two major problems require attention. First the design and implementation of a fast packet switch must be investigated, capable of expansion from small sizes of switch up to structures of very high capacity, to handle the expected growth in traffic (especially if video services are contemplated). Secondly the switch must be capable of satisfying the delay requirements of the delay sensitive classes of multi-service traffic. These form the two major issues addressed in this dissertation.

#### 1.1 Objectives

There are many possible approaches to the design of a fast packet switch. The work presented in this dissertation investigates a design which leads to a very simple hardware implementation. A simple implementation offers flexibility, a wide range of potential applications and operation at both conventional speeds and also at possibly very high speeds. The design features a number of parameters that have an effect upon the performance of the switch. Several techniques are also described to enhance the performance beyond that of the basic design. The first objective is thus to characterise the effect of the various parameters upon the performance of the switch. This allows the selection of the preferred design parameters.

The second objective is to characterise the performance of the switch for multiservice traffic. This objective has proven more difficult to satisfy mainly because of the problem of adequately defining the characteristics of multi-service traffic. The performance of the switch for telephony voice traffic, which is well characterised, has been investigated in detail. A simple model of multi-service traffic has also been used to investigate a statistical upper bound on the delay performance of the switch. The effect of packet length on the delay and throughput performance has been measured and some observations made on the packet loss probability due to buffer overload.

A third objective of this work has been the implementation of the two fundamental components of the switch design in current gate array technology. This provides an insight into the complexity of the design and its suitability for implementation in the various available logic families. It also lays the foundation for the development of an experimental model of the switch which will be required for future experimental work in the use of fast packet switching techniques for communications applications.

#### 1.2 Outline

For a concise presentation of the design of the Cambridge Fast Packet Switch and of the major results discussed in detail in this dissertation the reader is referred to [118] or [117]. The work has also been presented at the conference "IEEE Infocom '88" [116] and at the 'European Telecommunications Workshop' [115].

The remainder of this chapter presents an introduction to the growth of telecommunications networks and discusses the requirement for the integrated support of multi-service traffic. Chapter two considers the switching mechanisms capable of supporting this requirement within a high capacity switch implementation and presents the argument for selecting fast packet switching. Some of the fundamental characteristics of a fast packet switch are also discussed. In chapter three a simple classification of fast packet switch designs is introduced followed by a review of many of the major designs of fast packet switch available in the literature. Many

of these designs are based upon the use of a multi-stage interconnection network which also forms a central feature of the design of the Cambridge Fast Packet Switch. Chapter four therefore presents a review of interconnection networks concentrating upon those most relevant to the design of a fast packet switch. The design of the Cambridge Fast Packet Switch is presented and discussed in chapter five. Chapter six presents the results of a simulation study of the performance of the switch fabric in order to gain an insight into the effect of the various switch parameters on performance and to select the appropriate switch design parameters. Chapter seven introduces the requirements that multi-service traffic imposes upon the switch and presents the simulation results of various aspects of a simple model of multi-service traffic applied to the switch. A detailed simulation study of the switch performance for telephony voice traffic in the presence of saturated data traffic is also investigated as a specific example of multi-service traffic of practical interest. In chapter eight the details of the experimental hardware implementation of the two major components of the switch design in current gate technology are presented. Performance measurements of the hardware model are compared to the simulation results and the extension of the model to a full-scale switch implementation is discussed. Finally, chapter nine summarises the insight gained from this study, introduces some ideas for the support of multicast traffic, and discusses some of the problems involved in the networking of fast packet switches that remain for further study.

#### 1.3 Growth of Communications Networks

#### Local Area Networks

A local area network (LAN) connects computers, workstations, terminals, printers and related peripheral equipment across a distance of up to approximately 1 km [72]. Although research into local area network design began over ten years ago, to some extent stimulated by distributed computing applications [109], major commercial exploitation has developed over the last five years or so. As the cost of computer based equipment has fallen, so the requirement for interconnection within the local area has grown with the major area of commercial application being office automation. The vast majority of traffic currently carried on commercial LANs consists of file transfer and interactive data traffic but much research has been aimed at supporting other classes of traffic on the LAN especially voice traffic [121,106,38,144,3]. The local area network is privately owned and maintained which has encouraged work aimed at the integration of the LAN and the private telephone exchange (PABX) with varying levels of success [42,151,152,46].

The traffic capacity of current commercial LANs is in the region 1-10 Mbits/sec. With the geographical constraint of about 1 km, LANs must be interconnected via bridges to extend the capacity and area of coverage. Work on the transparent interconnection of LANs via bridges is well advanced [10,133]. The extent to which

the traffic capacity may be increased by bridging between multiple LAN segments is limited. Thus to interconnect large numbers of LANs and to support emerging wideband services, such as image and video, high speed local area networks are being developed for use as a backbone network [68,67,90,129,130]. These networks offer a bandwidth of the order of 100 Mbits/sec. This represents a considerable bandwidth for conventional computer communications applications but if the cost of workstations that support graphics and image applications continues to fall, and with the possible growth of video applications, a requirement to interconnect such high speed networks may develop. Unless traffic is highly localised, the interconnection of high speed LANs in a mesh topology, using simple bridges, will not greatly increase the capacity of the overall network. Thus the use of a fast packet switch as a high capacity multi-port bridge, to support the interconnection of high speed LANs, (and also as a high speed local area network itself,) forms a possible area of application for the use of fast packet switching technology. Furthermore, the high speed LANs that require interconnection need not be local to each other. Thus fast packet switching provides a mechanism whereby widely separated local area networks may be interconnected, at high capacity, to give the impression of a single virtual LAN spanning a very large area.

#### Metropolitan Area Networks

The metropolitan area network (MAN) is a public network which may be considered as an extension of the high speed local area network to encompass an urban area with a diameter of up to about 50 km [81]. It must also be capable of supporting multi-service traffic with reasonable efficiency and particularly the voice service. A number of network designs have been proposed [138,62,98], but the design most likely to be selected for public service is based on a dual bus arranged as a loop. It has the property that access to the network emulates the action of a single queue although sources are distributed across the network [103,119]. The integration of multi-service traffic is currently proposed in a hybrid manner. Integration is achieved at the access and transmission level but separate circuit and packet switches are used for compatibility with the existing digital telephony network. Packet traffic, however, is fragmented and transported within short, fixed length packets which permits evolution to the support of multi-service traffic upon a single integrated switching mechanism should this prove desirable.

A single network segment cannot possibly support the evolving needs of an entire urban community thus many segments must be interconnected by means of a switch [29]. Thus as the demand for packet based communications traffic grows we find another application for a fast packet switch that offers the flexibility to support growth to a very high capacity and the ability to handle multi-service traffic.

#### Public Wide Area Networks

For many years the public telephone network has been evolving from analogue to digital transmission and switching techniques [127]. In the developed countries penetration of digital techniques into the trunk transmission and switching network is now very high and attention is being focussed upon the local telephone network. Digital access from the subscriber to a digital local exchange is forecast to encourage the development of new telecommunications services at an acceptable cost. The integrated services digital network (ISDN) [125] promises to provide integrated access through a common, standard interface to both circuit and packet switched networks. The circuit switched channels will offer a bandwidth of 64 kbits/sec and access to the packet network will be at up to 64 kbits/sec. The basic rate interface will offer two 64 kbits/sec circuit switched channels with a 16 kbits/sec packet switched signalling channel. In Europe, primary rate access will offer 30 circuit switched channels with a 64 kbits/sec packet switched signalling channel. Wideband access to (N×64 kbits/sec) channels is being considered for later implementation and standards have been developed for packet based usernetwork signalling.

The philosophy of the ISDN is to employ the existing copper cable between the subscriber and the local exchange for digital access. The possibility of gradually replacing the copper connection with optical fibre is currently under consideration with the opportunity of increasing the bandwidth between the subscriber and the local exchange to many hundreds of Mbits/sec. Such a network is referred to as the broadband ISDN (B-ISDN) [157,91] and may be required to support services such as: video telephony; image, video and hi-fi audio retrieval services; and the distribution of high definition television [135,9]. The economic feasibility of the evolution to a widespread broadband network is at present uncertain. However, active consideration is being given to developments in the switching and transmission technology that would be required.

Two approaches have been proposed for the realisation of the broadband ISDN: synchronous transfer mode (STM) and asynchronous transfer mode (ATM), also called new transfer mode [101]. STM is an extension of traditional circuit switching principles and provides channels of fixed bandwidth with a packet switched signalling mechanism. ATM, however, is based upon a fast packet switching mechanism which can provide channels with a bandwidth that is highly variable throughout the lifetime of a connection. In the parlance of broadband ISDN the term 'fast packet switch' implies the use of variable length packets, whereas fast packet switching with short, fixed length packets is called asynchronous time division (ATD). The Cambridge Fast Packet Switch is equally suited to handling both short, fixed length packets and variable length packets of any reasonable size without loss of efficiency. Thus the more general term 'fast packet switching' is used in this dissertation to cover both applications.

ATM offers the major advantage of flexibility over the STM approach. The traffic characteristics of future service requirements cannot be predicted in ad-

vance thus the more flexible the network, the easier it becomes for a network administration to offer new services. It is not certain, however, that all services may be supported across an ATM switching mechanism, e.g. distribution video. Also, ATM technology may not be fully developed within the timescale which may be required by early broadband implementations. Hybrid solutions have therefore also been proposed in which both STM and ATM are supported over the same access interface and transmission link [161]. One solution proposes STM channels at about 150 Mbits/sec for the distribution of entertainment video services with a full-duplex ATM channel also at 150 Mbits/sec for all other services [91]. Broadband ISDN therefore forms a further application of fast packet switching techniques with the dual requirement of very high capacity and the ability to support a large number of services.

#### Integration

Three distinct levels of integration may be recognised in the evolution of telecommunications networks: access, transmission and switching. The current ISDN provides integrated access to circuit and packet switching networks that remain totally separate. Thus no sharing of resources between the networks is possible, two networks must be separately maintained and the support of future services is limited by the characteristics of the individual networks. Integration at the transmission level continues to require separate circuit and packet switches but the bandwidth of the transmission links connecting the switches is shared dynamically between the two switching mechanisms. Switches of this nature are referred to as hybrid switches and much work has been done on the integrated transmission of circuit voice and packet data services [32,48,93,155]. The circuit switched component offers low delay and low variance of delay which is a requirement of the voice service in current public networks [102] while the packet switched component handles bursty services.

Only when a single switching mechanism handles all classes of traffic is integration at the switching level achieved [146]. Such a network offers integration of access, transmission and switching and may be considered fully integrated. The greatest advantage of full integration is the flexibility to adapt quickly to the changing traffic requirements of new communications services. Other advantages include transmission efficiency, independence of the switching mechanism from the characteristics of the source traffic, and the need to support and maintain only a single integrated network. Fast packet switching offers one possible solution for a fully integrated network.

| Service Class | Service             | Natural Rate        | Burstiness |

|---------------|---------------------|---------------------|------------|

|               |                     | bits/sec            |            |

| Conversation  | Telephony           | $4 - 64 \mathrm{k}$ | 2 - 3      |

|               | Video Telephony     | 2–34M               | 1-5        |

|               | Interactive Data    | 1k-1M               | >10        |

|               | Telemetry           | <10k                | >10        |

| Mail          | Voice Mail          | $4-64\mathrm{k}$    | 2–3        |

|               | Video Mail          | 234M                | 2–3        |

|               | Text                | 1k-1M               | 1–10       |

|               | Facsimile           | 10k–1M              | 1–10       |

|               | Mixed Mode          | 100k-10M            | 1-10       |

| File Transfer | Bulk Data           | 1M                  | 1–10       |

|               | Program Download    | 1M                  | 1–10       |

|               | CAD/CAM             | 1-40M               | 1–10       |

| Retrieval     | Hi-Fi Audio         | 1-2M                | (2)        |

|               | Video               | 2-34M               | 2-3        |

|               | Mixed Mode Document | 100k-10M            | 1–10       |

|               | Data                | 1M                  | 1–10       |

Table 1.1: Multi-service traffic characteristics.

#### 1.4 Multi-Service Traffic

A simple classification of multi-service traffic is presented in table 1.1 which is adapted from [84] and [83] which itself reflects current CCITT¹ thinking. The natural rate indicates the source bit rate of the traffic class and in some cases assumes a certain amount of compression to reduce redundancy in the signal. Some sources emit traffic continuously at a single bit rate but many exhibit bursty behaviour in which traffic is emitted in bursts interspersed with idle periods. The burstiness of a source is expressed as the ratio of the peak to average bit rates. If the communications channel is fast enough to avoid being a bottleneck then most forms of data traffic become bursty due to user behaviour and the need to share processors amongst applications. Most forms of non-data traffic are also bursty if coded by efficient signal processing technology as the information content of the signal varies with time. A further parameter of the source traffic is the holding time of a connection. The relationship between the range of bit rates and holding times for various classes of traffic and switching mechanisms is illustrated in fig. 1.1 which is taken from [91].

Each class of source traffic also exerts various requirements on the performance of the communications network: set-up delay, bit error rate and information delay. The set-up delay is the time required to establish a connection across the network.

<sup>&</sup>lt;sup>1</sup>The International Telegraph and Telephone Consultative Committee.

Figure 1.1: Relationship between bit rate and holding time for various classes of traffic and switching mechanisms.

Estimates of the bit error rate required to support the various services vary widely but for a data service a residual error rate of better than  $10^{-12}$  may be required. For the various real-time services such as voice and video the delay requirements may not permit the use of an error detection and correction protocol but due to the redundancy of the signal a higher bit error rate may be tolerated. The information delay is the delay requirement from source to destination across the network of which several measures may be significant: mean, jitter and percentile. Some services may tolerate high and variable delay across the network. Other services, however, such as telephony, place stringent requirements upon the upper bound of delay and the delay jitter, (variance of delay across the network.) These must be maintained throughout the duration of the connection else the establishment of the connection should be refused. This requires that the network be aware of the bandwidth required by a connection request and be capable of ensuring that this bandwidth is available before granting the connection. This problem will be considered in greater detail in chapter 7. Further discussion of multi-service traffic and of the services under consideration for support by the broadband ISDN may be found in [135,9,8,92,156,142].

# Chapter 2

# Statistical Switching Mechanisms

In this chapter a review of the available switching mechanisms is presented and it is argued that a statistical switching mechanism is best suited to the requirements of the high capacity switching of multi-service traffic. Fast packet switching is selected for further study largely on the grounds of its flexibility and the development of the fast packet switch is traced. Some of the fundamental characteristics common to all designs of fast packet switch are then introduced.

#### 2.1 Multiplexing

Multiplexing is the technique whereby two or more separate communications channels are supported across a single transmission medium. A well known example from the telephone network is the support of multiple telephone conversations on a single high bandwidth trunk [22]. Early multiplexing systems for use in the analogue telephone network employed frequency division multiplexing (FDM) in which each separate channel was transmitted at a different carrier frequency. An analogous technique currently being developed for use in optical communications systems is that of wavelength division multiplexing (WDM) in which the various channels are carried on different optical wavelengths. In digital communications systems by far the most common form of multiplexing is that of time division multiplexing (TDM). In this technique the entire capacity of the shared transmission medium is allocated to each source in turn for a short duration sufficient for the source to transmit a brief burst of information of fixed length. As an example, a current European TDM transmission standard employs a 2.048 Mbits/sec digital carrier divided into frames of length 125  $\mu$ sec, fig. 2.1. Each frame is divided into 32 timeslots each of length 8 bits (one octet). In every frame, timeslot 0 is used for synchronisation and maintenance purposes, timeslot 16 is allocated to signalling and all other timeslots may be allocated to traffic sources. When allocated a channel, the source is given the timeslot number and it fills the appropriate timeslot in every frame with 8 bits of data. Each channel thus carries 64 kbits/sec of traffic.

Time division multiplexing offers channels of fixed bandwidth and is well suited

Figure 2.1: An example of time division multiplexing (TDM).

to continuous traffic sources of fixed bit rate, e.g. 64 kbits/sec voice, but many traffic sources are bursty and offer an instantaneous bit rate that is widely variable. TDM is very inefficient in its use of bandwidth for bursty services or for variable bandwidth services so statistical multiplexing has been introduced to overcome this inefficiency. In statistical multiplexing the channels are no longer of fixed bandwidth but each source receives as much transmission capacity as it requires instantaneously. As in TDM, sources continue to transmit information in bursts but these bursts are not necessarily of equal length and sources may submit bursts of information in any order and at a rate that reflects the instantaneous bandwidth required. Sources generally queue for access to the shared transmission medium on a first come first served basis but some sources may be allocated priority. In TDM, when a bursty source is temporarily idle the bandwidth allocated to it is unused but is not available to other sources whereas with statistical multiplexing a bursty source only consumes transmission bandwidth when it has information to send. In conventional TDM the identity of every channel is implicitly conveyed in the position of its timeslot within the frame but with statistical multiplexing the identity of each channel must be explicitly prefaced to every burst of information. This additional overhead tends to require that the information bursts of statistical multiplexing be much longer than those of conventional TDM.

In conventional TDM the offered traffic load can never exceed the capacity of the shared transmission medium, a utilisation of 100% may be supported indefinitely, delay is deterministic and jitter is very low. With statistical multiplexing, however, for short periods the offered traffic load can exceed the capacity of the transmission medium which may result in loss of information, delay or both. Statistical multiplexing cannot support an average utilisation of 100% on the transmission medium and 80% is a maximum utilisation frequently quoted. Delay is dependent upon the mean traffic load and the source traffic characteristics and jitter may be high. Despite these apparent disadvantages, statistical multiplexing is very flexible, supports traffic sources which vary widely in their bandwidth requirements and source traffic characteristics and handles bursty sources efficiently [149,50].

One proposal of statistical multiplexing for use in the asynchronous transfer mode of broadband ISDN has been termed asynchronous time division (ATD) [141,31]. The capacity of the shared medium is divided into short fixed length

blocks called cells of 128 bits each. Cells are allocated to traffic sources statistically on demand and each cell contains a short header to identify the source. No framing is applied to the transmission medium but empty cells are filled with a synchronisation pattern by which synchronisation across the transmission link is maintained. A sufficient supply of empty cells is guaranteed as on average the transmission medium will not be utilised beyond about 80%. Another proposal named dynamic TDM (DTDM) retains the frame and timeslot structure of TDM, with each timeslot containing a single cell, but allocates the timeslots statistically as in ATD [161]. A more flexible TDM multiplexing strategy for optical fibre links is under consideration named SONET [15]. It is capable of supporting both synchronous transfer mode (conventional TDM) and asynchronous transfer mode (statistically multiplexed) payloads. In a similar manner the multiplexing strategy under consideration for the STM proposal for broadband ISDN is also capable of supporting both STM and ATM payloads [37].

#### 2.2 Switching Mechanisms

Multiplexing allows the sharing of a high capacity communications link between many channels; but in order to achieve communication between source and destination across a network, a switching function is necessary. A range of switching mechanisms is available to accompany the various multiplexing techniques [84,127,25], from circuit switching for use with conventional time division multiplexing (or synchronous transfer mode) to packet switching which mates with the extreme end of statistical multiplexing (or asynchronous transfer mode). Between these two extremes lies a spectrum of available switching mechanisms illustrated in fig. 2.2 which is adapted from [84] and [37]. Switching mechanisms towards the left of the diagram offer channels with fixed bandwidth but a constant and small delay whereas those towards the right of the diagram offer variable bandwidth channels but with a variable delay which can be quite high [59]. Towards the centre of the diagram the statistical switching mechanisms attempt to provide the variable bandwidth required by bursty and variable rate sources but at low delay and low variance of delay compared with conventional packet switching.

#### Circuit Switching

Circuit switching is based upon the concept of a connection. A connection is an association between a source and its destination across a switched network. A connection may support communication in only a single direction or may offer both forward and reverse channels. A unicast, or point-to-point connection, is established between a single source and a single destination whereas a multicast, or distributive, connection may connect a single source to many destinations. Multicast connections will not be considered further until chapter 9. In circuit switched networks a communications channel of fixed bandwidth is exclusively allocated to

Figure 2.2: The spectrum of switching mechanisms.

a connection throughout the lifetime of that connection. A circuit switch, in general, connects input channels to output channels, (although the interconnection of bi-directional channels is also possible.) If each channel is presented to the switch on a separate transmission medium the switching is said to occur in the space domain and a connection is allocated a physical path across the switch [162,105]. If all of the channels are presented to the switch in a TDM multiplex on a single incoming and outgoing transmission medium, see fig. 2.1, then switching occurs in the time domain. In this case a connection represents an association between a timeslot on the incoming link and a timeslot on the outgoing link. During each frame the relevant timeslot is copied from the incoming link into a buffer and thence to the required timeslot on the outgoing link. This requires the buffering of one complete frame and inserts a constant delay of up to one frame length in the connection. In general, a digital circuit switch will be required to interconnect a number of separate incoming and outgoing transmission links, each of them TDM multiplexed with a number of channels. Thus both time and space domain switching is involved [127]. Small switches of up to 1000 or so 64 kbits/sec channels may be implemented using shared memory whereas larger switches will require an interconnection network [160,34].

Circuit switching offers channels of fixed bandwidth with a low and constant delay. It is transparent in that once a connection is established, the network takes no notice of the information it carries. In particular the network makes no attempt to correct transmission errors that may occur. Overload is handled by refusing

to accept further connection requests once the system capacity is fully allocated. This means that a connection once established will not suffer degradation of delay or bandwidth due to overload. Circuit switching is best suited to applications that require a fixed bandwidth, a low delay, and in which the call holding time is long compared to the call set-up time. It cannot effectively support the widely varying bit rates of many communications services at their natural rate. It does not exploit the burstiness of many forms of information and is inefficient for bursty traffic.

#### Multi-Rate Circuit Switching

Multi-rate circuit switching is a slight enhancement of circuit switching in that channels of different but fixed bandwidth may be formed by combining one or more integer multiples of some basic channel rate. Selecting the basic channel rate, however, poses a problem in order to satisfy the needs of both low and high bandwidth services. Multiple basic channel rates may be employed but this tends to complicate the design and control of the switch. Synchronising all of the basic rate streams that form a multi-rate channel also poses a significant problem as in general with a circuit switched network no guarantee is offered as to the relative delay between timeslots switched across the network. Neither is there any guarantee that any such delay will remain constant for the duration of a connection. The main disadvantage, however, is that multi-rate circuit switching does not handle bursty sources any more efficiently than does circuit switching.

#### Fast Circuit Switching

Fast circuit switching has been proposed as a means of handling bursty traffic. If the set-up of a connection across the switch is sufficiently fast, then a connection may be set up for each burst of traffic as it arrives and released immediately the burst ends. Thus the bandwidth of the switch is only allocated to active sources. The technique is similar to that of time assignment speech interpolation (TASI) [20,153] which was a multiplexing technique used on an expensive analogue transmission link to allocate voice sources to transmission channels only during periods of speaker activity (or talkspurts). The method provided a significant increase in the number of voice sources that could be handled by a transmission link without substantial loss of quality provided a sufficient number of sources were multiplexed.

It is inefficient to set up the entire connection on the arrival of each burst of information, thus burst switching [6,61] introduces the virtual circuit. A virtual circuit is a logical connection between source and destination which dissociates the concept of the connection from the bandwidth allocated to it. In burst switching a virtual circuit is set up at the beginning of a call which defines the connection but bandwidth is only allocated to that connection at the arrival of each burst of traffic. Buffering is also introduced so that if bandwidth is not available on the

arrival of a burst it may be delayed until bandwidth becomes available. For bursts of voice traffic, information is discarded once a burst becomes delayed for longer than 2 msec as it is no longer of any use. As a burst is always transmitted at the same bit rate as that at which it is received, there is no need to store the complete burst. It can be forwarded as soon as transmission bandwidth becomes available.

The interest in burst switching has so far proven somewhat limited with most of the work being undertaken by a single telecommunications manufacturer. Emphasis appears to be directed towards the switching of 64 kbits/sec voice in the presence of data traffic [122,123]. The switching mechanism could be made more flexible if multiple channel rates were available for burst switching, as in multirate circuit switching, but this would complicate the design and operation of the switch.

#### Packet Switching

Turning to the other end of the spectrum of switching mechanisms we find conventional packet switching [140,27]. In packet switching the bandwidth of the transmission medium is no longer divided into channels but the bandwidth of the entire medium is available to every burst of information from each source. Each information burst is constrained to a maximum length and additional fields of control information are added to identify source and destination and to support flow and error control etc. The resulting unit of information is called a packet. The maximum length of a packet is limited by the buffering requirements of packet switches and the packet delay requirements. It should not be too small, however, due to reasons of bandwidth efficiency as the overhead of control information can be quite considerable and is added to every packet. Packets are generally stored in every packet switch in the path and are not forwarded until completely received although suggestions such as cut-through and virtual cut-through [77,73] have been made to forward packets before they are completely received. Error checking and flow control protocol operations are performed on a link-by-link basis between every packet switch in the path and error correction may be performed both by retransmission from the preceding switch in the path and also on an end-to-end basis.

Packet switched networks offer two fundamental modes of operation: connection-oriented and connectionless. In connection-oriented mode a virtual circuit is established across the path between source and destination. In general, all packets belonging to the same virtual circuit follow the same route across the network which means that the routing operation only has to be performed once when the virtual circuit is set up. The processing of subsequent packets may thus be simplified, the packet header may be simplified, and flow control may be applied more efficiently and selectively to virtual circuits. In connectionless operation each packet, called a datagram, is handled individually and bears enough control information to completely identify it, its source and its destination. Packets between the same source and destination may follow different routes and packets may not

be guaranteed to arrive in the same sequential order in which they left. Connectionless operation requires more processing for every packet and flow control is less selective but it is less vulnerable to node failures and more easily adapted to changing traffic patterns. Connection-oriented mode is favoured by telecommunications administrations while connectionless operation is generally preferred by computer communications manufacturers.

Various experiments in supporting the voice service over wide area packet switched networks have been reported [154,49] but the high delay and high variance of delay over such networks requires complex resequencing procedures to reconstruct the voice signal which themselves insert further delay [11,104,108]. In addition, the public voice service requires a number of very large switches both in the total traffic capacity and in the number of switch ports, the support of which is beyond the ability of current designs of conventional packet switch. The support of the voice service over local area packet switched networks has perhaps been more successful [39,46,94,106,7] but even here the large maximum packet length permitted in many local area networks can introduce a large variance of delay for the voice signal reconstruction algorithm to handle.

Packet switching offers a very flexible communications facility supporting any arbitrary data rate up to the full rate of the transmission medium by selecting the size of the packet and the frequency with which packets are sent. It is also very efficient for handling bursty services and does not consume switching or transmission bandwidth during the idle periods of a call. It responds very rapidly to variations in the bandwidth required by sources during the active phases of a call and can interconnect sources and destinations operating at different data rates. Due to the large amount of processing per packet at every switch, conventional packet switches in general offer a much lower maximum capacity than circuit switches of comparable complexity. They also suffer from high delays across the network and a high variance of delay and it is to answer these drawbacks that fast packet switching has been proposed.

#### Fast Packet Switching

Fast packet switching attempts to retain the flexibility of conventional packet switching while reducing the delay and increasing the maximum switch capacity to approach that offered by circuit switching [50,149,79,146,147]. Recent advances in optical fibre transmission technology provide very high bandwidth links with very low bit error rates. With a low error rate on each transmission link, error control is no longer required on a link-by-link basis at every switch in the path. Also, at high transmission rates it may prove impractical to attempt to provide the functions of flow control and error control on every link in the path due to delay and buffering requirements. Therefore, in fast packet switching, the functions of flow control and error control are implemented on an end-to-end basis, or on entry to and exit from the network [66]. Thus services that require error detection and correction may implement a retransmission strategy on an end-to-end basis

whereas services, such as voice, that may tolerate a certain degree of error may take advantage of the low delay. As the protocol requirements of each switch are reduced, packets may be processed entirely in hardware. Thus switches of much greater capacity may be constructed and the switch may become more transparent to the data it carries than for conventional packet switching. Fast packet switching is in general connection-oriented. Thus once a virtual circuit is established across the network very short packet headers may be used to distinguish between each of the virtual circuits multiplexed over a single link. Also the routing of each packet may be performed in hardware by table look-up. As the packet overhead has been significantly reduced, very short fixed length packets may be used to reduce the delay across the switch to levels comparable with that of circuit switching. Fast packet switching with short fixed length packets is often referred to as asynchronous time division (ATD) in the context of broadband ISDN.

Both fast circuit switching and fast packet switching offer statistical switching mechanisms that handle bursty traffic efficiently and are capable of supporting high capacity switch implementations. Fast packet switching requires a header on every packet whereas fast circuit switching requires a header only on every burst. Fast packet switching therefore carries a greater overhead, perhaps 10% of the available bandwidth or more in a typical application, but with high capacity optical fibre transmission links, bandwidth efficiency may not be the most critical parameter. In both forms of statistical switching, overload occurs when the incoming information exceeds the transmission capacity resulting in delay, loss of information or both. Fast packet switching, however, is able to spread the effects of delay and loss over all calls or over a selected class or classes of calls. With fast circuit switching the effect must be absorbed by at most a few selected calls and can thus result in more severe delay or loss effects. Fast packet switching is also able to vary the allocation of bandwidth to individual sources instantaneously and can thus allow much greater flexibility. Fast packet switching may also give a better performance for data traffic as end-to-end retransmissions are carried using the entire bandwidth of the transmission links rather than across the narrowband channels of fast circuit switching. Thus fast packet switching has been selected for further study partly because of its flexibility but also because a very simple design of fast packet switch was envisaged and considered to be worthy of detailed study (see chapter 5).

#### 2.3 Evolution of the Packet Switch

#### Early Switch Architecture

In the early days of packet switching, computer processing power was an expensive commodity so packet switches were designed with a single central processor handling all of the switching, routing and protocol functions of the entire packet switch. Thus the throughput of the switch was limited by the processing capacity of the central processor and the complexity of the packet switching protocol.

Figure 2.3: A single path decentralised packet switch.

With the growth of VLSI technology the cost of processing fell rapidly until it became possible to provide some processing capacity on each switch port. Thus the lower level protocol functions, such as flow control and error detection and correction, could be handled independently by each switch port while the central processor provided higher level protocol functions such as routing. This increased the throughput by an order of magnitude, but as the central processor continued to interconnect all of the switch ports it remained a bottleneck.

#### The Single Path Decentralised Switch

To further improve the capacity of the packet switch it became necessary to remove the central processor completely from the transmission path of every packet. To achieve this, some form of single path interconnection medium was inserted to interconnect all of the intelligent, peripheral switch ports while the central processor took on more of a supervisory role, as illustrated in fig. 2.3. Hence, although some form of action may still have been required of the central processor on a per packet basis, it was decentralised by being removed from the task of physically transmitting each packet between the switch ports. The majority of packet switches have used shared memory as the single path interconnection medium with direct memory access in each of the switch ports but some designs have used serial bus [52,26], parallel bus [16,28] or ring [68,67,53] based structures.

When the majority of the per packet processing is removed from the central processor the throughput of the packet switch is determined by the bandwidth of the interconnection medium and the rate at which the processors in the switch ports can handle the protocol functions required. From an architectural perspective there is little difference between this class of packet switch and a local area

network (LAN). The switch port of the packet switch corresponds to the media access controller of the LAN. The only major difference is that the switching function in the LAN is distributed across the local area. This requires a more complex media access protocol than for the packet switch for which access to the interconnection medium is contained within the confines of the switch. A parallel may also be drawn between this class of packet switch and digital circuit switches that handle up to about 1000 telephony channels of 64 kbits/sec bandwidth. These also use a shared memory interconnection medium with a central processor that is in general only required at the set-up and clearing down of a connection.

Hybrid switch structures have also been proposed with a single path interconnection medium. These offer separate packet and circuit switching functions with integrated access and transmission facilities. Many such designs exist in the literature covering both discrete switches [80,16,151] and distributed switches, i.e. local area or metropolitan area network designs, both ring [18,23,138] and CATV bus [97].

#### The Multi-Path Switch

In considering switches of very high capacity, the bandwidth of a single path interconnection medium imposes a limit upon the switch capacity that may be achieved. To overcome this fundamental restriction it is clear that some form of multi-path interconnection medium is required that is capable of supporting communication between a large number of switch ports concurrently. Thus with a multi-path interconnection medium the total capacity of the switch is no longer limited to the bandwidth of the paths forming the interconnection medium but may grow as the number of switch ports increases. In this manner a much higher total switch capacity may be attained than for a single path interconnection medium using the same implementation technology. Conversely a high capacity switch no longer requires high speed and expensive device technology. The multi-path architecture applies equally to circuit, packet and hybrid switches. Circuit switches have used analogue multi-path switching networks for many years but more recently high capacity digital TDM circuit switches have been designed around a non-blocking, multi-path interconnection network [34,160]. Hybrid multi-path switches have also been proposed [150,139,96] and the majority of current fast packet switch designs are multi-path switches, examples of which will be discussed in the following chapter. Many forms of multi-path interconnection medium are possible, e.g. multiple rings [139,2], but the most general class, and the one which yields the highest switch capacities, is that of the multi-stage interconnection network which will be examined in detail in chapter 4.

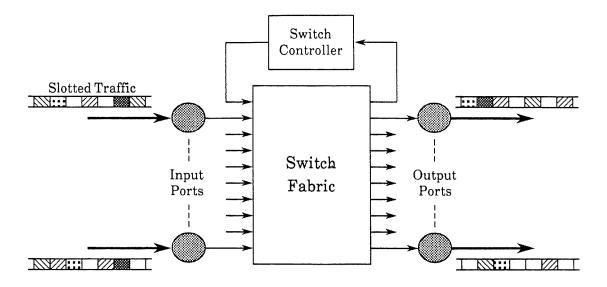

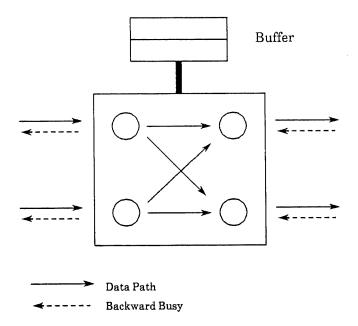

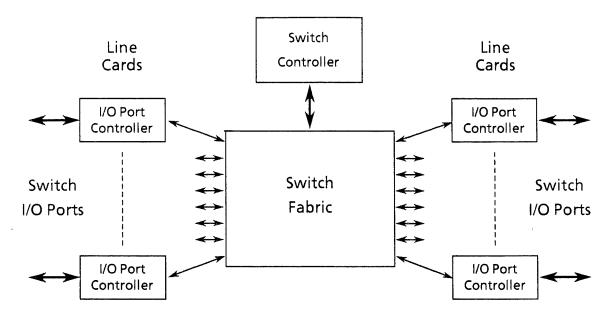

Figure 2.4: General structure of a fast packet switch.

#### 2.4 Fundamentals of Fast Packet Switch Design

There are some basic concepts that are common to many designs of fast packet switch and these will now be introduced prior to the detailed discussion of existing fast packet switch designs presented in the following chapter.

A fast packet switch will in general consist of a set of input lines each arriving at an input port, a set of output lines each departing from an output port, with input and output ports interconnected via a switch fabric, fig. 2.4. A switch controller will also be interfaced to the switch fabric and may control the input and output ports either directly or via packets across the switch fabric. External connections to the switch are generally required in the form of bi-directional links which are formed by grouping an input and an output line together. Many designs of fast packet switch are only capable of handling short fixed length packets. In such designs the bandwidth on both input and output lines is divided up into timeslots each of which may carry a cell (packet) or may be empty. All lines must be synchronised and this is accomplished either by means of a frame structure with a synchronisation pattern in every frame, as in TDM, or by filling empty cells with a synchronisation pattern. A multiplexing scheme of this nature is often referred to as 'slotted'.

Each packet includes a packet header which must contain a label that identifies the connection to which the packet belongs. In general the address space from which these labels are selected is specific to each input port of the fast packet switch. The label is selected by the control processor of the switch when the connection is established from the pool of unused addresses on the relevant input port of the switch. If the address space of the label field were not localised the problem of allocating a globally unique label in a large network would be time consuming and would limit the number of virtual circuits that could be supported

within the network. Thus to support a connection across a number of fast packet switches a different label is required to traverse each link within the path. One function of the input port of a fast packet switch is therefore to replace the label field of the incoming packet with an outgoing label. It does this by means of a look-up table which is set up when the connection is established. In a very large hierarchically structured network a two level labelling technique may be required, one label for local switching and another for trunk switching. Conversely in smaller networks a simpler scheme may be adopted possibly based on a globally unique destination name or upon a unique area code with a local destination name [51].

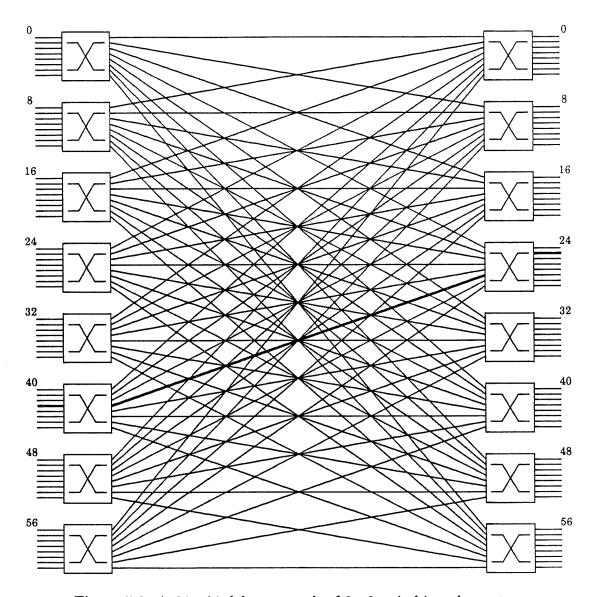

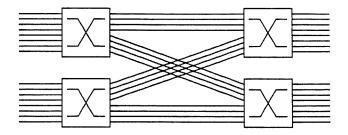

If a high capacity fast packet switch is to be constructed, a multi-path design is required. This may be achieved either by interconnecting a number of complete fast packet switches to form a larger structure or by implementing the switch fabric as a multi-stage interconnection network of simple switching devices. In both cases the switches that are interconnected will be referred to as switching elements. In the first case each switching element is a complete fast packet switch; complete with control processor, connection tables and label manipulation in the input ports. This allows flexibility in the choice of interconnection network but causes unnecessary replication of the control functions in a large switch. The second method, which is the more popular, does not require replication of the control processor or input port functions but implements the switch fabric as a multi-stage interconnection network of simple switching elements. Examples of multi-stage interconnection networks may be found in figs. 4.8 and 5.3.

The multi-stage interconnection networks generally selected have the property that a simple algorithm exists whereby each switching element can forward an incoming packet towards the correct output port. This algorithm usually requires that a tag specifying the required output port number be prefixed to each packet on entry to the switch. This function is performed in the input port by table look up on the label field in the packet header. One class of networks that display this property are commonly called banyan networks in the literature, although they have been more accurately defined as delta networks which refers to a specific sub-class of banyan networks. Switch fabrics are generally formed from square switching elements which have the same number of inputs as outputs and the degree of a square switching element is the number of its input (or output) ports. Most interconnection networks are constructed from identical switching elements. The degree of the switching element is important because it determines the number of stages of switching required in the interconnection network and hence the total number of interconnections required to form a given size switch. The number of interconnections required is a major factor in determining the maximum size of the switch due to implementation considerations.

#### 2.5 Summary

Time division multiplexing (TDM) offers fixed bandwidth channels with a constant and low delay. Statistical multiplexing is much more flexible, offers variable bandwidth connections and handles bursty traffic much more efficiently but may suffer from high delay, high variance of delay and also loss of information under overload conditions. Conventional circuit switching supports the interconnection of TDM channels while conventional packet switching handles the interconnection of statistically multiplexed channels. A switching mechanism is required that combines the benefits of circuit switching: low delay, low variance of delay and high capacity switch structures; with the flexibility and efficiency for bursty traffic that is offered by statistical multiplexing. Two statistical switching mechanisms have been reviewed: fast circuit switching and fast packet switching. Both appear capable of offering a delay performance close to that of circuit switching while being much more efficient in handling bursty traffic. Fast packet switching has been selected for further study as it appears to be the more flexible switching mechanism and also for performance and implementation considerations. From a brief review of the evolution of the packet switch a multi-path design has been suggested in order to achieve high capacity switch structures. Some of the basic concepts that underly many of the multi-path designs of fast packet switch have been introduced.

# Chapter 3

### Fast Packet Switch Architecture

Having established the basic concept of the fast packet switch and given an impression of the context into which it fits as a switching mechanism this chapter attempts to explore the architecture of the fast packet switch. A simple classification of fast packet switch designs is first introduced. A number of fast packet switch designs which have recently appeared in the literature are then reviewed and some comparisons drawn. Finally, from the existing literature, an elementary performance comparison between the three major classes of switch design is presented which will be developed in later chapters.

#### 3.1 A Simple Classification of Switch Designs

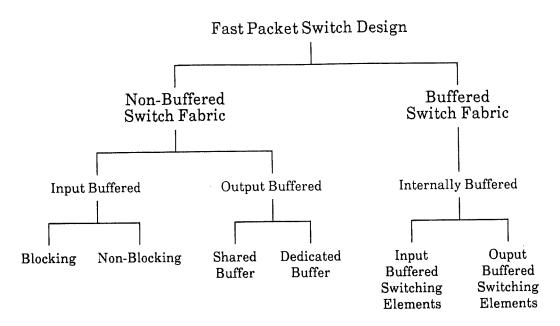

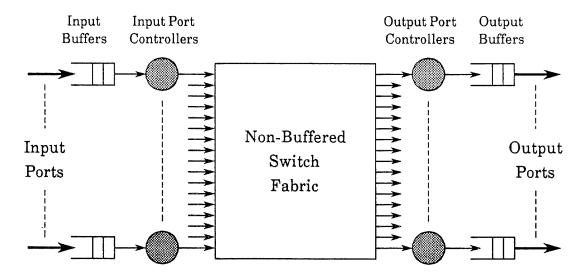

Two fundamental components are required to construct a fast packet switch: switching and buffering; and the relative positioning of these components permits a simple classification of fast packet switch design, fig. 3.1. If the buffering remains external to the switch fabric the design is based upon a non-buffered switch fabric. Else, if the buffering is implemented within each of the switching elements forming the switch fabric a buffered switch fabric (or internally buffered) design results. Of the designs based upon a non-buffered switch fabric, if the buffering precedes the switch fabric the switch is classified as input buffered. Else, if the buffering follows the switch fabric the design is output buffered. An input buffered design requires much less hardware and fewer interconnections than a similar output buffered switch but its basic performance is only about half that of the ideal output buffered switch. This difference in performance results from an effect known as head of the line blocking [71,76] which is discussed in the following section.

Input buffered switches may be classified according to whether the switch fabric is blocking or non-blocking. Blocking is said to occur when the transmission of an incident packet to a free output is temporarily prevented by other traffic within the switch fabric. A blocking switch will have a lower performance than an equivalent non-blocking fabric but will require fewer switching elements and interconnections.

Figure 3.1: A simple classification of fast packet switch design.