Number 151

# Formalising an integrated circuit design style in higher order logic

Inderpreet-Singh Dhingra

November 1988

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 http://www.cl.cam.ac.uk/

### © 1988 Inderpreet-Singh Dhingra

This technical report is based on a dissertation submitted March 1988 by the author for the degree of Doctor of Philosophy to the University of Cambridge, King's College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

### Abstract

If the activities of an integrated circuit designer are examined, we find that rather than keeping track of all the details, he uses simple rules of thumb which have been refined with experience. These rules of thumb are guidelines for deciding which building blocks to use and how they are to be connected. This thesis gives a formal foundation, in higher order logic, to the design rules of a dynamic CMOS integrated circuit design style.

Correctness statements for the library of basic elements are formulated. These statements are based on a small number of definitions which define the behaviour of transistors and capacitors and the necessary axiomatisation of the four-valued algebra for signals. The correctness statements of large and complex circuits are then derived from the library of previously proved correctness statements, using logical inference rules instead of the rules of thumb. For example, one gate from the library can drive another only if its output constraints are satisfied by the input constraints of the gate that it drives. In formalising the design rules, these constraints are captured as predicates and are part of the correctness statements of these gates. So when two gates are to be connected, it is only necessary to check that the predicates match. These ideas are fairly general and widely applicable for formalising the rules of many systems.

A number of worked examples are presented based on these formal techniques. Proofs are presented at various stages of development to show how the correctness statement for a device evolves and how the proof is constructed. In particular it is demonstrated how such formal techniques can help improve and sharpen the final specifications.

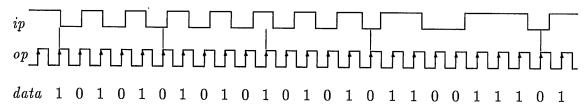

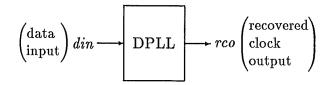

As a major case study to test all these techniques, a new design for a digital phase-locked loop is presented. This has been designed down to the gate level using the above dynamic design style, and has been described and simulated using ELLA. Some of the subcomponents have been formally verified down to the detailed circuit level while others have merely been specified without formal proofs of correctness. An informal proof of correctness of this device is also presented based on the formal specifications of the various submodules.

## Acknowledgments

During the time of this project, it is both pleasing and reassuring to note the number of people who have freely given their help and support. My greatest debt is to my supervisor Mike Gordon. This work could never have taken shape without his continued guidance and support. His patience during my earlier days and his ever optimistic manner has brought me through some of the most difficult times. He made valuable suggestions on earlier drafts of this thesis, and was the source of many excellent discussions.

In addition, I would like to express my sincerest thanks to Graham Birtwistle and Tom Melham. They diligently read through various drafts of this thesis and made valuable written comments. Tom's insistence on clear writing has set a standard which I will always try to aim for.

This work could not have started without the financial support of Racal Research and the British Science and Engineering Council. Racal Research has provided an excellent start to my career. The technical advice and individual guidance received while working there before the start of this project, and during the many visits thereafter, greatly helped in this project. Of the innumerable people who helped, I must explicitly acknowledge Bob Chapman and Dave Orton, who were the source of many stimulating discussions. I would also like to thank Racal Research for the funds to attend conferences.

Thanks also to Professor Roger Needham of the Computer Laboratory for providing such a stimulating and cheerful work environment. The hardware verification research group has proved an excellent platform to test ideas before making them public. Special thanks go to the following members of this group: Albert Camilleri, Avra Cohn, Thomas Forster, Don Gaubatz, Mike Gordon, Roger Hale, John Herbert, Jeff Joyce, Miriam Leeser, Tom Melham, Ben Moszkowski, and Glynn Winskel. Indeed, many thanks are due to the all the members of the Computer Laboratory for making this a friendly place to work.

During my year at the University of Calgary, I was looked after extremely well. For this I must acknowledge the kind generousity of Graham Birtwistle, and the

help of the VLSI research group: Brian, Han, Konrad, Mark, Mike, Todd, and others. I would also like to express my gratitude to the Alberta Microelectronics Center for allowing me access to their machines. In particular, Brian, Earl, Wallace, and Dale made my life there very enjoyable. Thanks also for all the free coffee and doughnuts guys.

Thanks are also due to the many people at the various sites for putting up with my persistent questioning about the systems etc.. These include Graham, Martin, Mike, Piete, and Steve at Cambridge, Dave, Keith, and Terry at the University of Calgary, and Earl and Wallace at the Alberta Microelectronics Center.

Finally, I would like to thank Humphry, with whom I shared a house for nearly three years. Thanks for all the cooked breakfasts, and for allowing me to test some of my crazy ideas. I can now confidently state that tomato skin is not a superconductor!

## Contents

| Abstract                                                      |                        |                                                    |    |  |  |  |  |

|---------------------------------------------------------------|------------------------|----------------------------------------------------|----|--|--|--|--|

| Acknowledgments                                               |                        |                                                    |    |  |  |  |  |

| 1                                                             | Introduction           |                                                    |    |  |  |  |  |

| 1.1 Background                                                |                        |                                                    |    |  |  |  |  |

| 1.2 Hardware Specification and Verification using Formal Meth |                        |                                                    | 9  |  |  |  |  |

|                                                               |                        | 1.2.1 What is a Proof of Correctness?              | 3  |  |  |  |  |

|                                                               |                        | 1.2.2 Related Work                                 | 5  |  |  |  |  |

|                                                               | Motivation             | 7                                                  |    |  |  |  |  |

|                                                               |                        | Research Summary                                   | 7  |  |  |  |  |

|                                                               |                        | 1.4.1 Outline                                      | 7  |  |  |  |  |

|                                                               |                        | 1.4.2 Simple Models for VLSI Primitives            | 8  |  |  |  |  |

|                                                               |                        | 1.4.3 Formalising the CLIC Design Style            | 9  |  |  |  |  |

|                                                               |                        | 1.4.4 A New Digital Phase-Locked Loop Design       | 9  |  |  |  |  |

|                                                               | 1.5                    | Hardware Verification using Higher-Order Logic     | 10 |  |  |  |  |

|                                                               |                        | 1.5.1 Logical Notation                             | 10 |  |  |  |  |

|                                                               |                        | 1.5.2 Types in Higher-Order Logic                  | 12 |  |  |  |  |

|                                                               |                        | 1.5.3 Specifying the Behaviour of Hardware Devices | 12 |  |  |  |  |

|                                                               |                        | 1.5.4 Specifying the Structure of Hardware Devices | 13 |  |  |  |  |

|                                                               |                        | 1.5.5 Deriving the Correctness Statement           | 14 |  |  |  |  |

|                                                               | 1.6                    | Thesis Outline                                     | 15 |  |  |  |  |

| 2.                                                            | Hardware Design Styles |                                                    |    |  |  |  |  |

|                                                               | 2.1                    | Introduction                                       | 17 |  |  |  |  |

| 2.2 Synchronous Circuits                                      |                        |                                                    | 19 |  |  |  |  |

|                                                               | 2.3                    | Clocked CMOS Circuits (C <sup>2</sup> MOS)         | 20 |  |  |  |  |

|                                                               | 2.4                    | Dynamic Circuits                                   | 21 |  |  |  |  |

|                                                               | 2.5                    | The DOMINO Logic Design Style                      | 22 |  |  |  |  |

|   | 2.6           | 2.6 The NORA Logic Design Style                          |                                                                    |    |  |  |  |

|---|---------------|----------------------------------------------------------|--------------------------------------------------------------------|----|--|--|--|

|   |               | 2.6.1                                                    | Problems with NORA                                                 | 2' |  |  |  |

|   | 2.7           | $\operatorname{Summ}$                                    | nary                                                               | 28 |  |  |  |

| 3 | $\mathbf{CL}$ | LIC: CLock Insensitive Cmos                              |                                                                    |    |  |  |  |

|   | 3.1           | Introd                                                   | luction                                                            | 29 |  |  |  |

|   | 3.2           | Informal Overview of the CLIC Design Style               |                                                                    |    |  |  |  |

|   |               | 3.2.1                                                    | Clock Description and Generation for CLIC                          | 30 |  |  |  |

|   |               | 3.2.2                                                    | CLIC Primitive Gates                                               | 31 |  |  |  |

|   |               | 3.2.3                                                    | Composition Rules for CLIC                                         | 36 |  |  |  |

|   | 3.3           | Forma                                                    | lising the CLIC Design Style                                       | 38 |  |  |  |

|   |               | l Definitions of Device Primitives                       | 39                                                                 |    |  |  |  |

|   |               | 3.4.1                                                    | The Signal Values                                                  | 40 |  |  |  |

|   |               | 3.4.2                                                    | CMOS Primitives                                                    | 41 |  |  |  |

|   | 3.5           | Forma                                                    | l Definition of Clock                                              | 43 |  |  |  |

|   | 3.6           | Forma                                                    | lising the Validity Conditions of CLIC Gates                       | 46 |  |  |  |

|   | 3.7           |                                                          |                                                                    | 47 |  |  |  |

|   |               | 3.7.1                                                    | N-type and P-type Logic Gates                                      | 47 |  |  |  |

|   |               | 3.7.2                                                    | The Latch                                                          | 54 |  |  |  |

|   |               | 3.7.3                                                    | The Static Inverter                                                | 55 |  |  |  |

|   | 3.8           | 3.8 Deriving the Correctness Statements of CLIC Circuits |                                                                    | 57 |  |  |  |

|   |               | 3.8.1                                                    | Deriving $\phi_2$ Correctness Statements from $\phi_1$ Correctness |    |  |  |  |

|   |               |                                                          | Statements                                                         | 57 |  |  |  |

|   |               |                                                          | Example: CLIC Gates Driven by the Same Clock Phase                 | 61 |  |  |  |

|   |               | 3.8.3                                                    | Example: CLIC Gates Driven by Different Clock Phases               | 64 |  |  |  |

|   |               | 3.8.4                                                    | Example: CLIC Circuits with Feedback                               | 67 |  |  |  |

|   |               | 3.8.5                                                    | Example: Using Higher Level CLIC Building Blocks                   | 69 |  |  |  |

|   | 3.9           | Summa                                                    | ary                                                                | 70 |  |  |  |

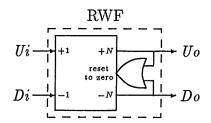

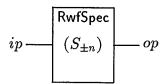

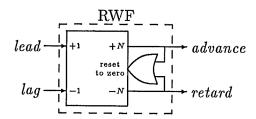

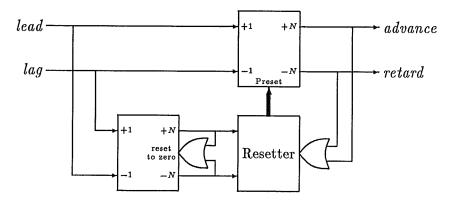

| 1 | For           | mulatin                                                  | g the Correctness of a Random Walk Filter                          | 73 |  |  |  |

|   | 4.1           | .1 Introduction                                          |                                                                    |    |  |  |  |

|   | 4.2           | Formal                                                   | Specification                                                      | 74 |  |  |  |

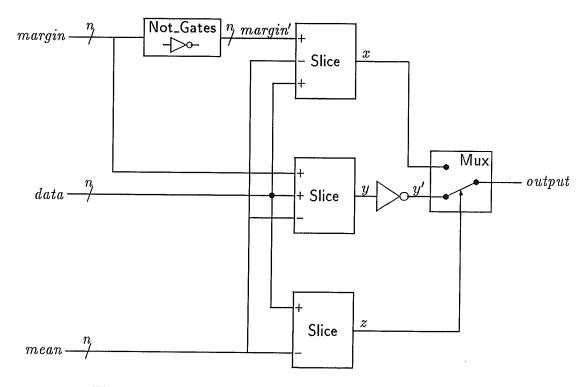

|   | 4.3           | Implem                                                   | $egin{array}{cccccccccccccccccccccccccccccccccccc$                 | 77 |  |  |  |

|   | 4.4           |                                                          |                                                                    |    |  |  |  |

|   | 4.5           | 5 Summary                                                |                                                                    | ٥٢ |  |  |  |

| 5                | Proof Plan for the Correctness of a Window Comparator |                    |                                                             |      |  |  |  |

|------------------|-------------------------------------------------------|--------------------|-------------------------------------------------------------|------|--|--|--|

| 5.1 Introduction |                                                       |                    |                                                             | . 87 |  |  |  |

|                  | 5.2 Formulating the Specification                     |                    |                                                             |      |  |  |  |

|                  | 5.3 Implementation                                    |                    |                                                             |      |  |  |  |

|                  | 5.4 Proof of Correctness                              |                    |                                                             |      |  |  |  |

|                  | 5.4.1 Interpretations of Signals                      |                    |                                                             |      |  |  |  |

|                  |                                                       | 5.4.2              | Specification of the CWIT primitives                        | 92   |  |  |  |

|                  |                                                       | 5.4.3              | Top Level Behaviour of CWIT $\dots \dots \dots \dots \dots$ | 96   |  |  |  |

|                  |                                                       |                    | Specification Transformation                                |      |  |  |  |

|                  |                                                       |                    | Result Transformation                                       |      |  |  |  |

|                  | 5.5                                                   | Summar             | ry                                                          | 106  |  |  |  |

| 6                | AN                                                    | lew Desi           | ign of a Verifiable Digital Phase-Locked Loop               | 109  |  |  |  |

|                  | 6.1                                                   | Introduc           | $\operatorname{ction}$                                      | 109  |  |  |  |

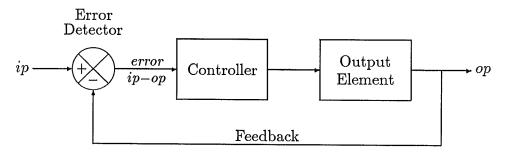

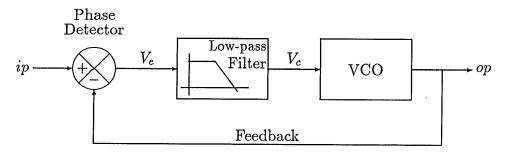

|                  |                                                       | 6.1.1 V            | What is a Phase-Locked Loop?                                | 110  |  |  |  |

|                  |                                                       | 6.1.2 I            | Digital Phase-Locked Loops                                  | 112  |  |  |  |

|                  |                                                       | 6.1.3 Т            | The Lead/Lag Digital Phase-Locked Loop                      | 113  |  |  |  |

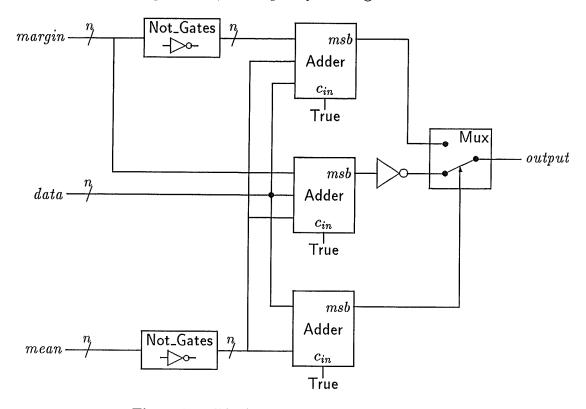

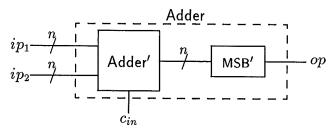

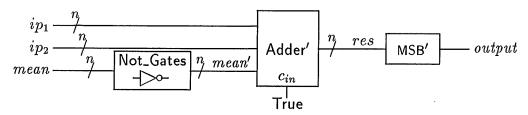

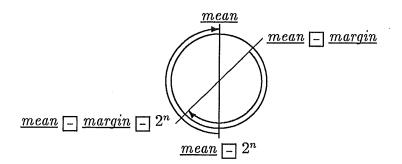

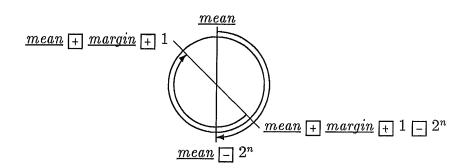

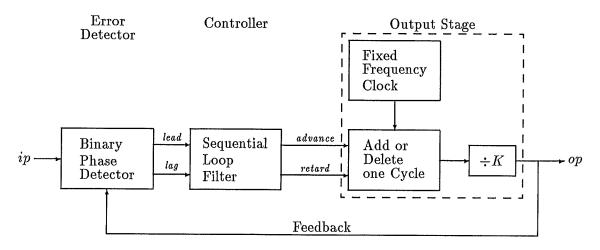

|                  | 6.2                                                   | Overview           | w of a New Design for a Lead/Lag DPLL                       | 116  |  |  |  |

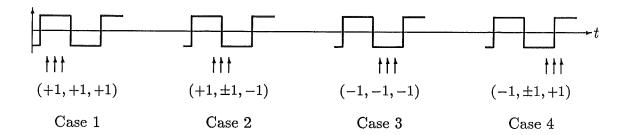

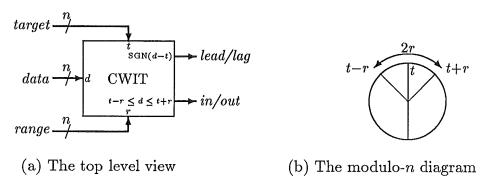

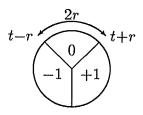

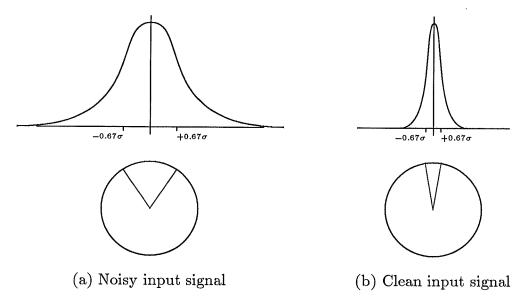

|                  |                                                       | 6.2.1 A            | A Self-Modifying Digital Phase Detector                     | 117  |  |  |  |

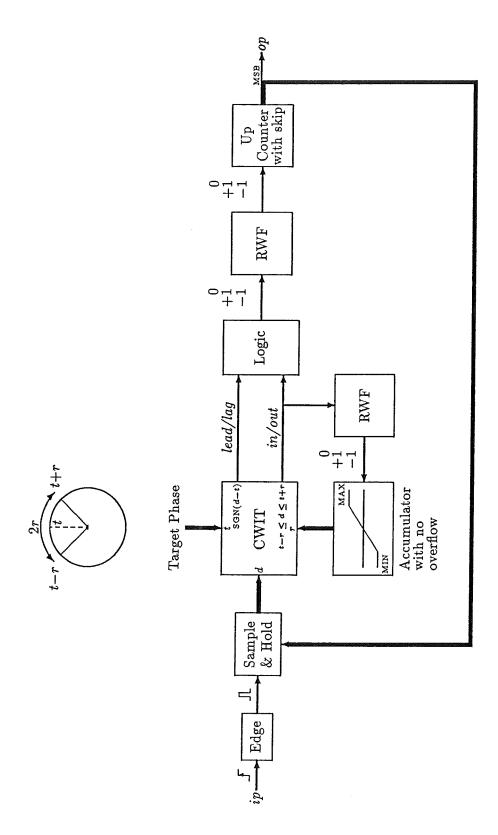

|                  |                                                       | 6.2.2 T            | The New Lead/Lag Digital Phase-Locked Loop $\dots$          | 120  |  |  |  |

|                  | 6.3 Formulating the Correctness Statement             |                    | ting the Correctness Statement                              | 124  |  |  |  |

|                  | 6.4                                                   | Formula            | ting the Proof Plan $\dots$                                 | 129  |  |  |  |

|                  | 6.5                                                   | Summar             | y                                                           | 131  |  |  |  |

| 7                | Con                                                   | Concluding Remarks |                                                             |      |  |  |  |

|                  | 7.1                                                   | Summar             | y of Work Done                                              | 133  |  |  |  |

|                  | 7.2                                                   |                    | on and Future Work                                          |      |  |  |  |

| Bibliography 1   |                                                       |                    |                                                             |      |  |  |  |

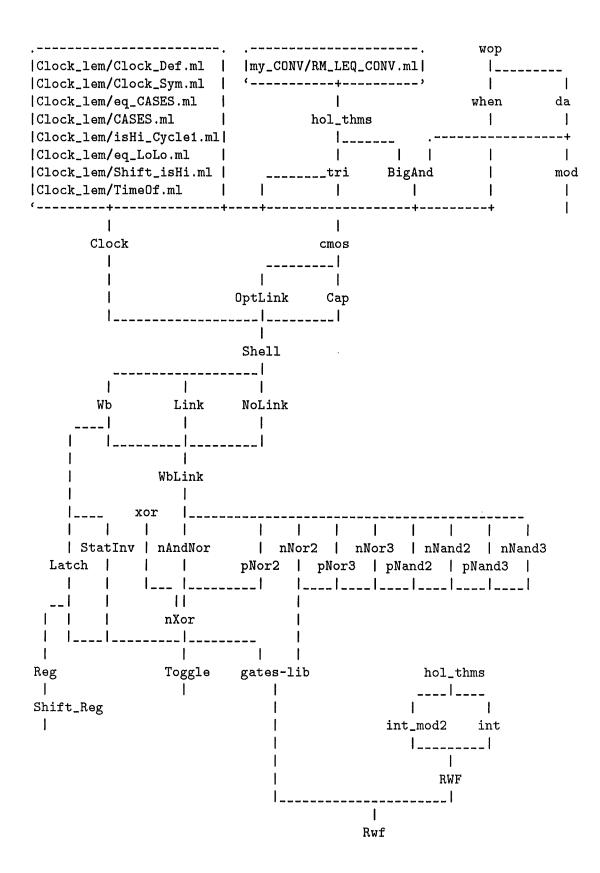

| ${f A}$          | The                                                   | Hierarc            | thy of Theories                                             | 145  |  |  |  |

| В                | ML                                                    | Code fo            | or the Correctness of the Toggle Device                     | 147  |  |  |  |

| $\mathbf{C}$     | $\mathbf{ML}$                                         | Code fo            | r the Correctness of the Random Walk Filter                 | 157  |  |  |  |

## Chapter 1

### Introduction

### 1.1 Background

On 23rd December 1947 at the Bell Laboratories in Murry Hill, the first semiconductor transistor was invented by Bardeen, Brattain and Shockley. It was kept a closely guarded secret until just before the first publication in 1948 [Bardeen 48]. It took a further five years before transistors were manufactured on a large scale. In 1953 the best transistors cost around \$80s [Braun 78]. Today it is possible to buy memory chips containing over a million transistors on a single chip for around \$10us, or about 0.00002 cents per transistor if converted to 1953 values!

But the development of the transistor was not without its problems. Manufacturing was difficult, and even more difficult was getting two transistor characteristics to match. The early transistors, i.e. point contact transistors, were very noisy and highly unreliable; and they tended to deteriorate rapidly with not too extreme temperature and humidity conditions. A story has it that a factory in England, upon retiring one of its senior manufacturing workers, found the yield of its point contact transistors dropped dramatically. This was due to the fact that the retired worker knew just how hard to tap the electrode to make the point contact. Too hard and the electrode went too deep into the semiconductor, and too light meant no contact; either way the transistor would not function.

It was fortunate that industry did not have to endure this for too long. By April 1952 the junction transistor was in manufacture, even though it was only at a rate of less than a hundred per month. Over the next few years, with the advent of zone refining and improved manufacturing techniques, the industry grew rapidly. The first integrated circuit was made in October 1958 by Jack Kilby of

Texas Instruments, and the first full scale microprocessor on a single chip, the Intel 4004, appeared in 1972.

By comparison, the developments of digital hardware design techniques have been slow. The complexity of the hardware has increased over the years, but the design tools have far from kept pace with this "silicon chip" revolution. The basic design techniques used today differ little from those used to design some of the early digital systems, which used valves and relays as switches instead of transistors. Today, Boolean logic [Boole 54] is used to design combinational circuits, and the methods of Mealy [Mealy 55] and Moore [Moore 64] are used to design sequential circuits.

With the advent of computers, designers have been able to design more complex systems, since they can be simulated on computers and so debugged to some extent before manufacture. The basic models used for the primitive devices have improved and hence the accuracy of simulators [Bryant 81]. However, for large systems, exhaustive simulation is prohibitively expensive, and requires exponentially large simulation time even with today's fastest computers. At IBM Research, scientists use the YSE machine, which is designed to simulate circuitry at the primitive component level rather than at the architectural level. This is a highly parallel processor, able to simulate several hundred times faster than any uni-processor machine. But even with this sort of specialised computing power it may still be not viable to simulate very large systems.

Due to these seemingly unsurmountable problems, designers have been forced to look in other directions to verify designs before building them. Even though the cost of manufacturing is coming down, it is still important to have confidence in the design before it is committed to silicon. This is essential since it is not always possible to test every aspect of the design in the time available. Whilst many applications can tolerate some errors, there are others where even minor flaws could be dangerous or too expensive to tolerate. These include:

#### • Safety critical applications:

Increasingly, integrated circuits of enormous complexity are being used in areas where errors in these circuits could lead to loss of life. Examples include flight control systems, railway signaling systems, medical life-support systems such as pacemakers, military applications, nuclear plant controllers, and anti-lock braking system in cars (see [Cullyer 88]).

### • Remotely sited applications:

Applications where access to the systems is difficult would benefit from having the design 100% correct. This is simply because the cost of repairing or

replacing faulty components would be too high. Examples include systems installed in arctic regions, satellites, and systems installed on oil and gas pipelines.

### • Volume production applications:

Many industries manufacture systems for the mass market. If the design of a device in such systems is faulty then the cost of recalling and repairing it would be very high. Examples include circuits in automobiles, in telecommunication systems, and in fact any domestic appliance which uses integrated circuits.

With such important applications as these, it is necessary to ensure that a design is correct. To achieve this, attention has turned to formal methods for specifying and verifying the correctness of circuit designs.

## 1.2 Hardware Specification and Verification using Formal Methods

Work in this area has progressed considerably over the last two decades, and several sites are now actively involved in research in this field. Some of this work is briefly described in this section. An overview is first given of what is meant by "hardware specification and verification using formal methods," and what constitutes a proof of correctness.

### 1.2.1 What is a Proof of Correctness?

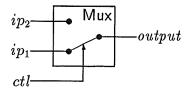

The idea of specifying the behaviour of hardware devices using boolean algebra is in fact quite old. Indeed, designers use boolean algebra all the time to communicate the behaviour of small circuits to other designers. A trivial example of this is the behaviour of a multiplexor circuit, which can be stated as follows:

$$op = (ctl \land a) \lor (\sim ctl \land b) \tag{1.1}$$

where the operators  $\sim$ ,  $\wedge$ , and  $\vee$ , represent logical negation, conjunction and disjunction respectively.

Equation 1.1 above can be referred to as the *specification* for the multiplexor circuit, because it contains all the information necessary to understand its top level

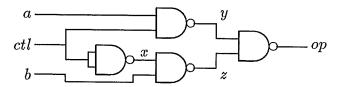

behaviour. Boolean algebra is also used for deriving the top level specification from the specifications of the lower level components that constitute the circuit. The steps of this derivation together constitute a proof of the correctness of the circuit (see [Gordon 85c]). Each line in this proof is either a hypothesis, or is derived from the previous lines. The final result is the derived theorem stating the top level behaviour of the circuit. As an example consider the proof for the multiplexor device. A circuit that implements the multiplexor device is shown in figure 1.1.

Figure 1.1: A simple multiplexor circuit

The proof of this multiplexor device is given below. The final result in this proof exactly matches the specification of this device.

| 1. | $x = \sim (ctl \wedge ctl)$                                      | [by definition of Nand]                           |

|----|------------------------------------------------------------------|---------------------------------------------------|

| 2. | $y = \sim (ctl \land a)$                                         | [by definition of Nand]                           |

| 3. | $z = \sim (x \land a)$                                           | [by definition of Nand]                           |

| 4. | $op = \sim (y \land z)$                                          | [by definition of Nand]                           |

| 5. | $x = \sim ctl$                                                   | [by 1 and the law $p \wedge p = p$ ]              |

| 6. | $z = \sim (\sim ctl \land b)$                                    | [substituting 5 into 3]                           |

| 7. | $op = \sim (\sim (ctl \land a) \land \sim (\sim ctl \land b))$   | [substituting 2 & 6 into 4]                       |

| 8. | $op = \sim \sim (ctl \land a) \lor \sim \sim (\sim ctl \land b)$ | [by law $\sim (p \land q) = \sim p \lor \sim q$ ] |

| 9. | $op = (ctl \land a) \lor (\sim ctl \land b)$                     | [by law $\sim p = p$ ]                            |

The important difference between this style of verifying the correctness of a circuit and techniques involving hardware description languages and simulation, is that the first supports *formal* reasoning. A validation technique which involves formal methods can be summarised as follows:

- 1. Write the top level specification in some formal language.

- 2. Design the circuit and describe it in the same language as that used for the specification.

- 3. By using the inference rules of this language, mathematically prove that the circuit description meets its specification.

In the above example the specification is given in equation 1.1, the implementation is given in figure 1.1, and the proof is given by the 9 steps shown above. This proof is an extremely simple one and could be done on the back of an envelope. But the proofs of real devices can be thousands of lines long and very complex, so different techniques are required to manage them. Several different approaches in this direction are briefly outlined below.

### 1.2.2 Related Work

Techniques used for the complete verification of hardware without use of simulation are briefly summarised in this section. Summaries of only the most relevant works are given, together with pointers to others.

The early work of Milner and others on the LCF project [Gordon 79] inspired much effort in the area of mechanised theorem proving. A specialised language was developed for specifying and verifying hardware [Gordon 82] which led to the development of the LCF-LSM theorem proving system [Gordon 83a]. Many examples were done using this system including the verification of a simple computer [Gordon 83b]. Many improvements to the LCF system have been made over the years, including an improved rewriting package [Paulson 83a], and a new tactics package [Paulson 83b]. Hanna and Daeche then independently developed the VERITAS theorem prover based on higher-order logic [Hanna 86b, Hanna 86a]. With the improved expressive power of higher-order logic becoming increasingly attractive, and with the experience gained from the LCF family of theorem provers, Gordon then developed the HOL theorem proving system [Gordon 85b, Gordon 88], which forms the basis of the work done in this thesis. A number of examples have been successfully completed which demonstrate the use of higher-order logic as a vehicle for specification and verification. These include the verification at the detailed timing level of a D-flip-flop implemented in logic gates (see [Hanna 86b] and [Herbert 86] for proofs done in the VERITAS and the HOL systems respectively), the verification of a ring interface chip [Gordon 85a], re-proof of the computer in HOL [Joyce 88], and the first level proof of correctness of VIPER, the first industrial microprocessor [Cohn 88].

The systems mentioned above are all based on general theorem provers, where the proof is done manually and the system merely does the housekeeping. In the direction of automated theorem provers is the work of Boyer and Moore [Boyer 79]. This has been used by Hunt to verify the correctness of a 16-bit microprocessor [Hunt 87]. The underlying logic of this theorem prover is first order predicate logic without quantifiers. In principle proofs are done automatically by this

system, but in practice the theorem prover needs to be guided considerably by carefully requesting simpler theorems to be proved first. Barrow's VERIFY system [Barrow84] is another example of an automatic theorem prover. The underlying model used by this system is that of finite state machines, based on Gordon's LSM language [Gordon83a]. In both of these systems, logic gates form the set of primitive devices on the basis of which hardware verification is done.

Another general formalism used for hardware verification is temporal logic. An interesting variant is that developed by Moszkowski known as Interval Temporal Logic (ITL) [Moszkowski 83a]. ITL has been used to formulate the specifications of a bit-sliced microprocessor [Moszkowski 83b]. Proofs using ITL were initially done by hand. Recent work by Hale [Hale 88b] shows that the HOL system can be used to mechanise proofs in ITL. A subset of ITL has also been developed as an executable language known as Tempura [Moszkowski 86]. More recently, Leeser has used a variant of this formalism together with Prolog to reason about circuits down to the detailed transistor level [Leeser 87].

On the side of more specialised formalisms are CIRCAL and  $\mu$ FP.

— The early work of Milne and Milner on Concurrent Processes [Milne 79] inspired a number of calculi. Milne went on to develop CIRCAL [Milne 83a, Milne 83b], while Milner went in a slightly different direction and developed the Calculus of Communicating Processes (CCS) [Milner 80, Milner 82]. In the CIRCAL framework, the structure of hardware devices is represented hierarchically, with communication between components being done through commonly named ports. Behaviour in this framework is described as a sequence of events on the external ports of devices. Operators are provided for the composition and the hiding of ports. Several examples have been completed using this framework, including a simple CRT controller by Traub in [Traub 87]. Here Traub also presents the various temporal concepts needed to model different granularities of time and means of moving between them. A Lisp based environment for doing proofs in this formalism has also been developed [Traub 83].

— Sheeran uses  $\mu$ FP [Sheeran 83], which is an extension of the programming language FP developed by Backus. Sheeran introduces the  $\mu$  operator into the basic language FP to model memory in circuits. Both the behaviour (functional part) and the implementation (geometric part) of a circuit can be represented in this language. With the aid of the  $\mu$  operator, the inputs and outputs are modeled as streams. Behavioural descriptions of circuits can be transformed into their geometric forms thus leading to correctness by construction. Only synchronous systems can be modeled by this formalism. Examples done using this framework include the design for a systolic correlator [Sheeran 83].

The above works have concentrated at the gate level and higher. Winskel in [Winskel 88] describes a compositional model for the more primitive components of a VLSI technology, namely transistors, capacitors, etc.. This work is based on the simulation models developed by Bryant [Bryant 81]. Though this work is at a more detailed level than what has been described so far, it is not clear how it can be related to the system level.

### 1.3 Motivation

From the above summary of work in the formal methods area, it is clear that effort has concentrated on getting concise models of devices (transistors, gates, circuits, etc.); but little effort is placed in formalising the rules of thumb used by designers of integrated circuits. These rules are generally obtained with experience, but in most cases their justifications are rooted in the detailed models of the lower level circuit devices. These rules of thumb are much simpler and more abstract than the formal reasoning behind what is and what is not a correct thing to do to get a correctly functioning circuit. The research work presented in this thesis addresses this problem.

### 1.4 Research Summary

There are a number of topics covered in this thesis in addressing the question of formalising an integrated circuit design style. These can be separated into the following areas:

- Develop simple models for the primitive components of a VLSI technology such as CMOS.

- Based on these simple models show the correctness of the rules of an integrated circuit design style.

- Demonstrate the viability of these ideas on a major case study.

### 1.4.1 Outline

If the activities of an integrated circuit designer are examined, we find that rather than keeping track of all the details, he uses simple rules of thumb which have

been refined with experience. These rules of thumb are guidelines for deciding which building blocks to use and how they are to be connected. Usually the more systematic the design style, the more structured these design rules are.

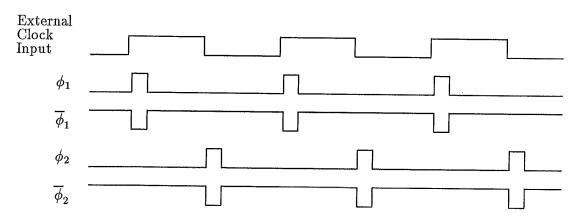

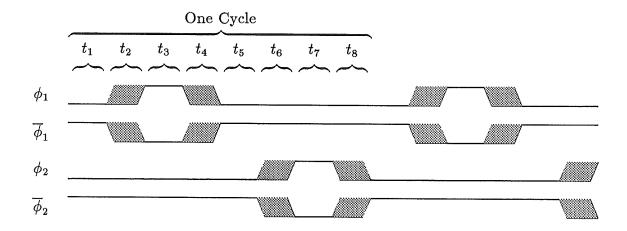

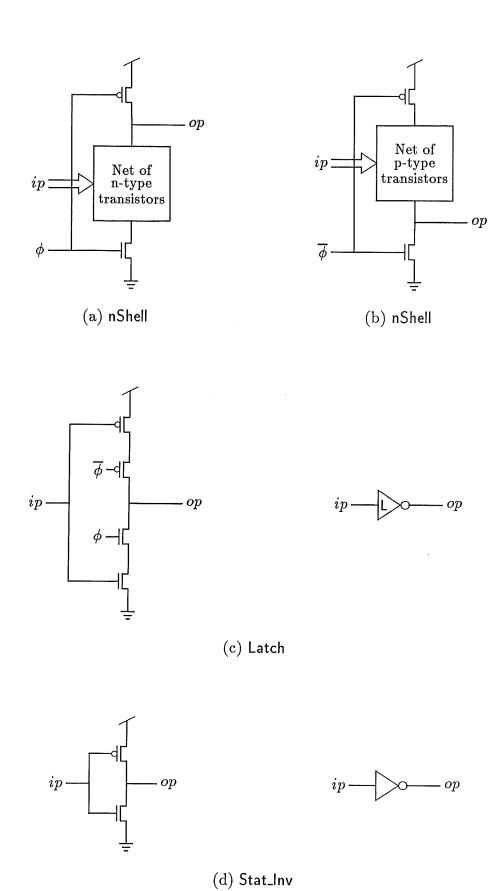

To show that these rules have a logical foundation, a design style known as NORA [Goncalves 83] has been analysed. In this design style there are two clock lines, inverses of each other, and two sorts of gates; n-type and p-type. The design rules govern how gates may be connected and which clock lines may drive them if the result on the output is to be guaranteed. To make the design style synchronous, a C<sup>2</sup>MOS latch is used as a dynamic register. This further complicates the rules, but gives rise to a design style that generates smaller and faster circuits than standard CMOS.

The NORA design style has been demonstrated to fail for large circuits [Orton 84], but a refinement of this design style using a two phase non-overlapping clocking scheme solves this problem. This design style is known as CLIC, and was developed at Racal Research by Orton and his team [Orton 84]. This has a more complex set of rules than its predecessor due to the extra pair of clock lines. The research work presented here gives a formal foundation for the design rules of the CLIC design style. This gives a higher degree of confidence in the correct functionality of devices designed using this design style.

### 1.4.2 Simple Models for VLSI Primitives

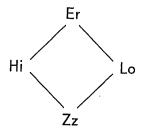

The work presented here in developing simple models of primitive devices has mainly concentrated on the CMOS technology. In particular, it has been guided by the needs for a simple and tractable model for the verification of the CLIC design style. The model originally used was based on Bryant's simulation work [Bryant 81], where three signal strengths were used to allow modelling of charge decay on capacitors. This results in a lattice of seven signals. This was further simplified by modelling the decay of charge on the capacitors in a different way resulting in the four valued model of Hi, Lo, Er and Zz as used at present.

The model used for the transistor is also simple. A simple uni-directional model was found to be adequate for modelling the CLIC design style. This simple model greatly reduces the complexity of the correctness proofs of CLIC gates. The model of hardware used at present and as presented in this thesis is a simple non-delay, uni-directional model of transistors, together with a model of capacitors with charge decay. More complex models could have been used, but they complicate the proof considerably. Also, since the CLIC design style uses transistors in a strictly

defined way, the simple model of hardware as used here could be derivable from other more complex models.

### 1.4.3 Formalising the CLIC Design Style

The formalisation of a design style [Dhingra 88] entails giving a formal foundation to any rules of thumb that are used. This means that all correctness statements of CLIC gates are derived from a small number of primitive device definitions, rather than merely being stated as axioms. These definitions cover devices such as transistors and capacitors, and the necessary axiomatisation of the four valued algebra for signals. Instead of rules of thumb, we now rely on being able to show the correctness of complex structures by logical inference, based on the correctness statement for the various CLIC gates.

For example, in order that a CLIC gate may drive another, it is important that the input constraints of one be satisfied by the output constraints of the other. In formalising the design rules, these constraints are captured as predicates and incorporated in the correctness statement of the CLIC gate. So when two gates are to be connected, it is only necessary to check that the predicates match. This checking is done using the HOL system [Gordon 85b].

### 1.4.4 A New Digital Phase-Locked Loop Design

As a major case study to test some of the specification and verification techniques, the design of a Digital Phase-Locked Loop (DPLL) system was undertaken. The function of this DPLL is to re-generate the clock signal from the serial data being received. The basic principle is to measure the phase difference between incoming data transitions and the sampling edge of the clock signal. When on average this phase difference becomes too small, or too large, then the clock period is appropriately adjusted.

Fully digital phase-locked loop designs exist using binary quantised phase detectors and discrete phase adjustments, e.g. [Yamamoto 78] and [Yukawa 73]. The characteristics of such systems vary, depending on the techniques used for averaging the phase difference; but they all use binary quantised digital phase detectors. The design presented in this thesis uses a new kind of a Digital Phase Detector (DPD). The heart of this DPD is a digital window comparator. The proof of correctness of this and other parts of the system are outlined in this thesis.

This new DPLL system has been designed down to the CLIC gate level and has been described and simulated using ELLA [Morison 84]. Some of the subcomponents have been formally verified down to the detailed circuit level while others have merely been specified without formal proofs of correctness. In this thesis a discussion is presented on constructing the correctness statement and the proof of correctness for such real time systems.

## 1.5 Hardware Verification using Higher-Order Logic

The formalism used in this thesis is that of typed higher-order logic [Church 40]. To make this thesis self-contained, a brief overview is given in this section of the logical notation that will be used, followed by a review of the techniques for specifying and verifying hardware using higher-order logic. The material presented in this section is not new, and has already been covered in considerably more detail in the literature. For a more complete description of this logic and its machine formulation see [Gordon 85b], and for a more thorough introduction to the general techniques for specifying and verifying hardware using higher order logic see [Gordon 86, Camilleri 87, Gordon 88, Melham 88a]. In particular, Melham's paper [Melham 88a] is an excellent source; most of what follows in the remainder of this section is taken, with permission, from this paper.

### 1.5.1 Logical Notation

What makes this logic higher-order is that quantification is allowed over functions and predicates. Furthermore functions can take functions as arguments and return functions as results. So for example the induction axiom for natural numbers can be expressed as the following theorem where the variable P ranges over predicates.

$$\vdash \forall P. P(0) \land (\forall n. P(n) \supset P(n+1)) \supset \forall n. P(n)$$

Note that a theorem is denoted here by the turnstile symbol ( $\vdash$ ) at start of the equation. This is to indicate that this is a derived fact in the system. Additional facts can be added to the basic system by either stating them as axioms or as definitions. Definitions are a conservative means of extending the basic system, i.e. they only add an additional constant to the system as a means for abbreviation. No additional facts can be derived with the addition of this definition that could not be derived before. An axiom however could lead to inconsistencies being introduced into the system if care is not taken. These are not used in the work that follows. As an example of a definition, consider the function Rise. This is defined in the logic as follows:

Rise

$$sig \ t =_{def} \sim sig(t) \land sig(t+1)$$

This predicate captures the notion that the signal sig rises at time t. The variable sig is a function from natural numbers to booleans, and is an example of a higher order variable being passed as an argument to a higher order function. The predicate Rise upon taking its first argument (sig) returns a function from numbers to booleans. This function when given an additional argument time (t) returns a boolean answer indicating whether the signal sig rises at time t or not.

In expressing complex terms in the logic, use is often made of an additional piece of syntax to simplify the readability of terms. This involves making abbreviations local to the term by making use of the "let ... in ..." statement. This is really syntactic sugar for a term stated in  $\lambda$ -calculus. The transformation of such terms into equivalent terms not involving this syntax is as follows:

$$\begin{pmatrix} \mathbf{let} \ x = a \\ \mathbf{in} \\ f(x) \end{pmatrix} \equiv (\lambda x. \ f(x)) \ a \equiv f(a)$$

One more primitive constant that needs to be described is the  $\varepsilon$ -operator. Terms of the form " $\varepsilon x$ .  $\operatorname{tm}[x]$ " denote the value v chosen such that " $\operatorname{tm}[v]$ " is

true. For example, the term " $\varepsilon x$ . x = 7" exactly denotes the number 7, and the term " $\varepsilon x$ .  $x^2 + 3x + 2 = 0$ " denotes one of two possible values, namely -1 or -2. However if this  $\varepsilon$ -operator is used over a term which is false for all values then an arbitrary but a fixed value is returned. For example, the term " $\varepsilon x$ . x < x" denotes an arbitrary natural number. For a more in depth discussion of the  $\varepsilon$ -operator see [Leisenring 69].

### 1.5.2 Types in Higher-Order Logic

Every correctly formed term in higher-order logic has a type. The type of each term must be consistent with the type of its subterms. Informally, types can be thought of as sets and terms of that type can be thought of as elements of that set. The basic HOL system has the type of natural numbers(: num) and the type of boolean truth values(: bool) built in. Types can be built from other types by using type operators. So for example the type of signals on a wire represented as functions from natural numbers to booleans can be denoted ":  $num \rightarrow bool$ ," where " $\rightarrow$ " is an example of an infixed type operator.

Writing "tm: ty" explicitly states that the term tm has type ty. By using this notation the type of the predicate Rise defined above can be stated as follows:

Rise :

$$(num \rightarrow bool) \rightarrow (num \rightarrow bool)$$

Such explicit type information is usually not given. In practice it is only necessary to give such detailed type information when it is not clear from the context what the type of the term should be.

New types can also be declared in the HOL system. This is a fairly tedious task. A package which allows new types to be declared automatically in the HOL system has recently been developed by Melham [Melham 88b]. The actual procedure for declaring new types in the HOL system is not described here, but for more information on this see [Gordon 85b, Melham 88b].

### 1.5.3 Specifying the Behaviour of Hardware Devices

The behaviour of hardware can be captured in higher-order logic by predicates. The labels corresponding to the external ports of a device are passed as arguments to the predicate. The predicate is defined as a relation indicating which combinations of values can appear on these ports. As an example, consider the definition for the behaviour of a two input nand gate as shown below:

$$i_1$$

$\bigcirc$   $op$

The behaviour of this device can be captured in logic by a predicate Nand<sub>2</sub> with three arguments corresponding to the three external ports. This predicate is then defined to be true for all combinations of values that can occur on these variables which correspond exactly to the ports of a hardware nand device. The definition for this device can be formally stated as follows:

$$\mathsf{Nand}_2(i_1, i_2, op) =_{def} (op = \sim (i_1 \land i_2))$$

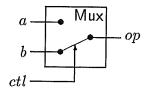

As another example, the behaviour of the multiplexor device as used earlier can be expressed formally in the same way. The top level view of this device is shown below in figure 1.2. The external ports are labeled here in exactly the same way

Figure 1.2: Top level view of a multiplexor device

they were labeled in figure 1.1 on page 4. The behaviour of this device is captured as a predicate Mux with four arguments corresponding to the four external ports. This is defined in logic as follows:

$$\mathsf{Mux}(ctl,a,b,op) \quad =_{\mathit{def}} \quad (op = (ctl \ \Rightarrow \ a \ | \ b))$$

### 1.5.4 Specifying the Structure of Hardware Devices

The structure of hardware devices is captured in higher-order logic by conjoining together the predicates for each of the subcomponents. In this way the constraints imposed by each of the subcomponents are pooled. These constraints together constitute the behaviour of the top level device. The interconnect between the parts is captured in logic by commonly named lines. So, for example, the structure of the multiplexor device shown earlier in figure 1.1 can be formalised as follows:

$$\mathsf{Nand}_2(ctl,ctl,x) \, \wedge \, \mathsf{Nand}_2(a,ctl,y) \, \wedge \, \mathsf{Nand}_2(b,x,z) \, \wedge \, \mathsf{Nand}_2(x,y,op)$$

The internal lines of this circuit are hidden from the environment, but in the above equation this "hiding" is not captured. Hiding of lines is done in logic by existentially quantifying them [Camilleri 87]. Now a new predicate MuxImp can be defined which captures the structure of the multiplexor circuit complete with the information that the lines x, y and z are hidden (or internal) as follows:

$$\begin{array}{ll} \mathsf{MuxImp}(ctl,a,b,op) &=_{def} & \exists x\ y\ z. \\ & \mathsf{Nand}_2(ctl,ctl,x)\ \land \\ & \mathsf{Nand}_2(a,ctl,y)\ \land \\ & \mathsf{Nand}_2(b,x,z)\ \land \\ & \mathsf{Nand}_2(x,y,op) \end{array}$$

This definition states that the values that can appear on the external ports are precisely those which satisfy the constraints imposed by the four predicates, where these four predicates model the four nand gates used in the implementation of this multiplexor device.

### 1.5.5 Deriving the Correctness Statement

The two predicates Mux and MuxImp as defined above, capture the specification and the implementation of a simple multiplexor device in higher-order logic. Now by simple logical manipulation in the logic, the following theorem can be derived:

$$\vdash \mathsf{MuxImp}(ctl, a, b, op) = \mathsf{Mux}(ctl, a, b, op)$$

This is the correctness statement for the multiplexor device. It states that the values that can appear on the external ports of the implementation are exactly those that are allowed by the specification, i.e. the implementation meets the specification.

In this example, the implementation predicate MuxImp is proved to be equivalent to the specification predicate Mux. For more complex devices, formulating the correctness statement as an equivalence relation may not be appropriate. The behavioural specification of large and complex systems could be different in many respects as compared to the implementation which implements them. For example, specification may be partial, or be stated at different granularities of time, or be stated using abstract data types. In such cases the correctness statement will generally be in the form:

```

ext{F} 	ext{ Dev\_Imp}(i_1, \ldots i_n, o_1, \ldots o_n) \supset \\ 	ext{let } ip = 	ext{Abs}_i(i_1, \ldots i_n) \\ 	ext{in} \\ 	ext{let } op = 	ext{Abs}_o(o_1, \ldots o_n) \\ 	ext{in} \\ 	ext{Dev\_Spec}(ip, op) \end{aligned}

```

where the abstraction functions Abs; and Abs, map the input and the output signals respectively of the implementation Dev\_Imp, to those of the specification Dev\_Spec.

### 1.6 Thesis Outline

Chapter 2: In this chapter a brief introduction is given to the various design techniques. In particular, the term "hardware design style" is clearly defined. Then an extended summary is given of two such design styles known as DOMINO and NORA, together with a discussion on their advantages and problems.

Chapter 3: In this chapter the CLIC design style is presented. This design style overcomes some of the problems associated with NORA. First a detailed but informal description of this design style is given. Then a full account is given of the formalisation of this design style in HOL, beginning with simple models of the primitives such as transistors and capacitors. The last part of this chapter is devoted to simple examples illustrating how this work can be used to derive the correctness statements for circuits designed using this formal framework.

The next two chapters give proof outlines of two components, with varying amounts of detail. Both of these components are used in the design of the digital phase locked loop.

Chapter 4: In this chapter a formal proof of correctness of the Random Walk Filter (RWF) is presented. The RWF is designed in the CLIC design style, and the correctness statement for it is derived using the formal techniques of chapter 3. Integers are used in the specification of this device since they help represent the functionality in a more natural way. This does however complicate the proof considerably at the higher level. This chapter focuses on deriving the correctness statement from a cluster of CLIC gates rather than dealing with the proof details at the higher levels.

Chapter 5: In this chapter a plan for the proof of correctness of the Window Comparator is presented. The proof uses integers and modular arithmetic, but it does not go all the way down to the transistor level as in the previous chapter. However the primitive devices used in constructing this device can be trivially proved down to the transistor level. An informal specification is first given which is then improved as the proof develops.

Chapter 6: This chapter first gives a brief overview of control systems with particular emphasis on Digital Phase-Locked Loops (DPLLs). Then a novel design for a new class of phase-locked loops is presented which uses the devices of the previous two chapters. A formal specification for this device is presented together with a sketch for an informal proof of correctness. Some of the difficulties involved in arriving at the correctness statement and constructing the proof are discussed.

Chapter 7: Conclusions, discussion and future work.

## Chapter 2

## Hardware Design Styles

In this chapter a brief introduction is given to various design techniques. In particular the term "hardware design style" is clearly defined. An extended summary is given of two such design styles known as DOMINO and NORA, together with a discussion of their advantages and problems.

### 2.1 Introduction

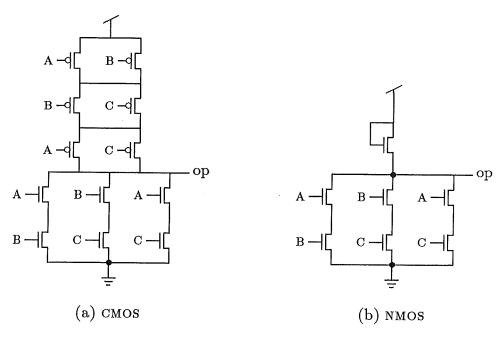

Circuits built using fully complementary CMOS techniques have an inherent redundancy of information. Consider, for example, the circuit for the carry out stage of a full adder, as illustrated in figure 2.1a. The six n-channel transistors contain all the information needed to implement the logic function of this gate as do the six p-channel transistors. The advantage of duplicating the functionality is that there is virtually no power consumed by the gate, except for the short periods of time when the inputs or the outputs are making transitions.

The problem with this approach is that for complex gates, such as the one in figure 2.1a, a considerable amount of silicon area is wasted by duplicating the functionality of the gate. Also, the capacitive loads of such devices are fairly high, since the output of these gates have to drive both the n-channel and the p-channel devices. To obtain the same functionality in NMOS would require only the n-channel devices together with a load transistor as shown in figure 2.1b.

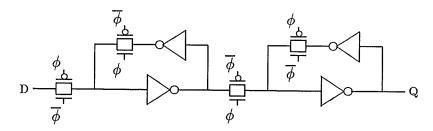

The other major problem with fully complementary CMOS technique has to do with clock races. As an example consider the design of a simple master-slave D-flip-flop. Illustrated in figure 2.2 is the D-flip-flop, which is amongst the most commonly-used elements in VLSI. Note that transmission gates are used to clock

Figure 2.1: The carry out circuit of a full adder

data in. These are generally implemented using a p-channel and an n-channel transistor in parallel. Single transistors are avoided due to low noise margins. For data to flow through the pn-transmission gate, two clocks,  $\phi$  and  $\overline{\phi}$ , are required. For any reasonably sized circuit, the clock will be degraded due to distribution and loadings, and this will lead to clock skew and the potential for some overlapping of the two phases. During the phase overlaps, several successive transmission gates may be switched on, which would lead to illegal data flow depending on the ratio between gate delay and clock skew. This has become a serious problem with the reduction in gate delays due to improvements in technology, and has resulted in designers paying considerable attention to clock distribution and load.

Figure 2.2: Master slave D-flip-flop designed in fully complementary CMOS

Because of these two drawbacks of fully complementary CMOS, designers have developed techniques which allow one to use stripped down versions of logic gates provided that certain rules are followed. It is these rules, either self imposed or motivated by the way the hardware is being used, which constitute "Hardware

Design Styles". In the remainder of this chapter a brief overview is given of two design styles which are the predecessors to the design style used as the subject of this thesis. But first a brief summary of Synchronous Circuits, Clocked CMOS Circuits  $(C^2MOS)$ , and Dynamic Circuits is presented, which are the generic techniques used in many design styles. All of these techniques use some form of a clocking scheme which is an important part of systems design. Weste summarises the use of clocking in systems design as follows:

Clocks are used in digital systems to hold up a signal until it is time for it to begin to move through the next stages of logic. Registers are used in conjunction with the clocks so that a signal can be stored at a location until it is needed.

[Weste 85, page 332]

### 2.2 Synchronous Circuits

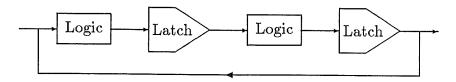

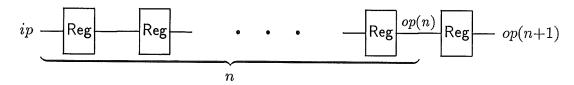

The basic principle behind any synchronous design philosophy is that the system is separated into blocks of purely combinational logic with no data storage facility, interleaved by register latches which hold the data between clock pulses. There is a global system clock which is used to clock the register latches, the period of which is such as to allow all combinational logic blocks to finish evaluation of results. So, on the tick of the clock, new data appears on the inputs of the combinational logic blocks, and the old results are passed as inputs to the next stage by use of the register latches. By definition there is no feedback within the purely combinational logic blocks. This principle is illustrated in figure 2.3.

Figure 2.3: Synchronous Logic Concept

The advantage of such a design technique is that all the timing problems are localised to the areas between the register latches. Thus the problem of identifying difficult timing paths and race hazards is considerably simplified. However, it does require care to ensure that the latency through the various paths are matched. Furthermore, in fully complementary CMOS, the register latches used are essentially variations of the basic D-flip-flop as discussed above. So problems due to clock skew and phase overlap are still present.

### 2.3 Clocked CMOS Circuits (C<sup>2</sup>MOS)

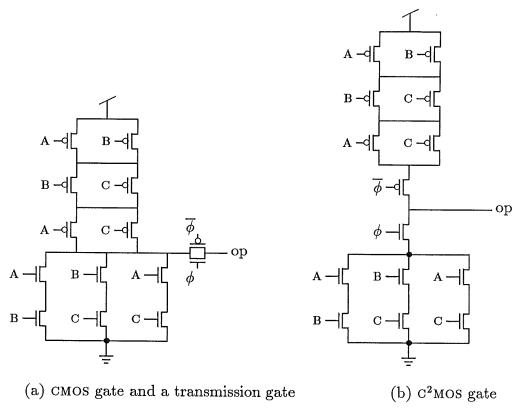

A C<sup>2</sup>MOS gate is essentially the net result of combining a fully complementary CMOS gate with its output passed through a clocked transmission gate. An example of this is illustrated in figure 2.4 using the adder circuit as described earlier with the output passed through a clocked transmission gate.

Figure 2.4: An example of a C<sup>2</sup>MOS gate

This technique was originally developed to build low power dissipation CMOS circuits for calculators [Suzuki 73]. The reason for the low dynamic power were to do with the layout considerations when using the metal gate CMOS technology. Though the technology has changed, the technique is still used where it is necessary to have fully complementary CMOS gate followed by a clocked transmission gate.

C<sup>2</sup>MOS gates have the same input capacitance as regular fully complementary CMOS gates, and larger rise and fall times on the outputs due to the extra clocking transistors in series to the path to the power rails. However these clocked gates are slightly faster than their equivalent circuit composed of a regular fully complementary CMOS gate followed by a clocked transmission gate.

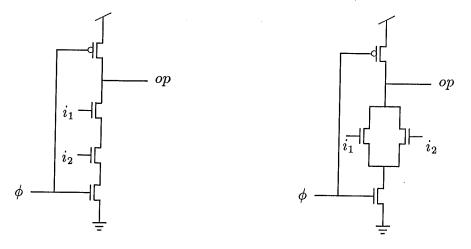

### 2.4 Dynamic Circuits

Dynamic logic gates have two phases of operation: the precharge phase and the evaluation phase. During the precharge phase the output nodes of the gates are precharged to a particular level, usually high for n-type gates. During this period the path to the other level, ground for n-type gates, is turned off. The changing of the inputs of the gate must also occur during this period. This is necessary because otherwise charge redistribution effects could corrupt the output node voltage. Then by using a system clock the gate is switched from the precharge phase to the evaluation phase. For n-type gates this involves turning off the path to the high level and turning on the path to ground. Depending on the state of the inputs, the output will either remain floating high or go low. Figure 2.5 illustrates this principle on the carry out circuit of the full adder described earlier.

Figure 2.5: N-type dynamic gate for the carry out stage of a full adder

The advantages of dynamic circuits are that far fewer transistors are used (approximately half), which means that the silicon area used per gate is reduced. Another implication is that the the load capacitance on the output of such gates is lower than in fully complementary CMOS, since they only have to drive either n-channel or p-channel transistors in the next gate. Further, the power consumed by such circuits is lower than with NMOS since there is no pull-up transistor. The output is precharged before evaluation, and during the evaluation only one path to the power rails is open, so there is no static current path consuming power.

Since there is no static current path and the load capacitance on the output is comparable to that of NMOS circuits, it would appear that dynamic circuits have the advantages of fully complementary CMOS, namely low power consumption, and those of NMOS, namely high speed operation. But in real circuits there is still some power penalty as compared to fully complementary CMOS, because each gate must

be precharged on every cycle even if its output is to continue at the other level. It is also difficult to realise these apparent speed advantages in real circuits since most useful circuits generally have several logic gates in series. In dynamic circuits this is a serious problem since dynamic CMOS gates cannot be cascaded by using a simple single phase clocking scheme. In order to cascade dynamic CMOS gates, designers have to resort to complex clocking strategies which can involve anything up to eight clock lines. One such technique forms the basis of the next two sections. For a more detailed survey of some of the other techniques see Weste's book on "CMOS VLSI Design" [Weste 85, pages 203–224].

One last point is that the clock in dynamic circuits cannot be stopped. There is a minimum speed at which the clock for such circuits could be operated, but they cannot be single stepped (which could be useful for debugging purposes, be it for problems due to technology or logic design).

### 2.5 The DOMINO Logic Design Style

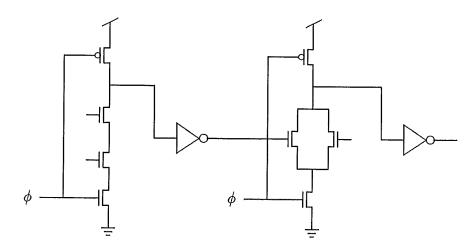

The previous section mentioned that dynamic gates cannot be cascaded by use of a single phase clock. Let us examine this in a little more detail. Consider some simple examples, namely an n-type Nand and an n-type Nor gate as illustrated in figure 2.6. The previous section also dictates that the inputs must only change during the precharge period, i.e. during the period when  $\phi$  is low.

- (a) n-type dynamic Nand Gate

- (b) n-type dynamic Nor Gate

Figure 2.6: N-type dynamic Nand and an n-type dynamic Nor gate

One solution would be to have only one dynamic gate at the start of a chain of gates with the remaining gates in the chain being static gates. This really doesn't

buy us much, and a great deal better can be done. The real insight is to develop a set of building blocks where a single transition on the input lines can result in no more than a single transition on the output. Then these blocks could be combined to make larger blocks provided no cyclic structures are used.

Going back to the Nand and the Nor gates of figure 2.6, note that if the inputs are precharged low and the outputs are precharged high, then, when these gates go from the precharge phase to the evaluation phase, then they in fact obey the above rules. Provided the inputs make no more than one transition (from low to high,  $\mathcal{F}$ ) then the output will also make no more than one transition (from high to low,  $\mathcal{F}$ ). This argument is true of both the Nand and the Nor gates of figure 2.6. In fact, this is true of any n-type complex gate provided the net of transistors used to compute the logical function of the gate are composed of parallel/serial combinations of n-type enhancement mode transistors only.

Now if the output of these gates are followed by a static inverter then the output of the inverter could make no more than one transition, from low to high (f). This in fact is exactly what is required on the inputs of the next dynamic gate. So collectively this now forms a design style where the output of each dynamic gate is buffered by a static inverter resulting in a set of building blocks consisting of And, Or, and complex noninverting gates. This design style is commonly known as the DOMINO logic design style [Krambeck 82], so called because the chain of evaluation goes sequentially from the start of the chain to the end, much as the fall of one domino causes the next to fall which in turn causes the next to fall and so on. A simple example illustrating this DOMINO style of circuit design is shown in figure 2.7 below.

Figure 2.7: An example DOMINO circuit

### 2.6 The NORA Logic Design Style

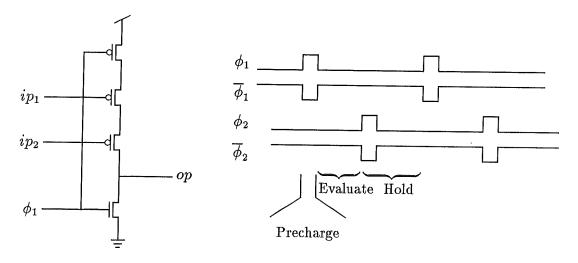

By duality to the DOMINO logic design style, a family of p-type dynamic gates can be developed which have almost an identical set of rules for cascading the logic blocks. The difference is simply that the inputs of the p-type gates are precharged high and the outputs are precharged low. As before, provided the inputs make no more than a single transition (in this case from high to low, \(\frac{1}{4}\)), then the output will also make no more than a single transition (from low to high, \(\frac{1}{4}\)). Again, by buffering each dynamic gate by a static inverter, a design style consisting of p-type, And, Or and complex noninverting gates results.

However a more universal design style can be developed if both n-type and p-type gates are mixed. Note that the behaviour of the output of an n-type dynamic gate is identical to the requirements for the inputs of a p-type dynamic gate; in both cases the nodes are required to be precharged high, and during the evaluation period there is no more than a single high to low  $(\mbox{$\mathbb{L}$})$  transition on these nodes. Similarly the behaviour of the output of a p-type dynamic gate is identical to the requirements for the inputs of an n-type dynamic gate; this time the nodes are required to be precharged low, and during the evaluation period there is no more than a single low to high  $(\mbox{$\mathbb{F}$})$  transition on these nodes.

So by ensuring that the inputs of all n-type dynamic gates are driven by p-type dynamic gates and vice versa, a more general design style evolves known as the n-p-CMOS design style [Goncalves 82]. This time the building blocks consist of the dynamic n-type and the dynamic p-type gates without the buffering static inverters. This means that the primitive building blocks are in fact a set of inverting dynamic gates which forms a more universal logic family. Not only this, but the style of DOMINO logic design can also be used within the framework of this new design style. Naturally this new design style has a more complex set of logic design rules than the DOMINO style, but the extra generality of inverting rather than noninverting dynamic logic gates is worth this price.

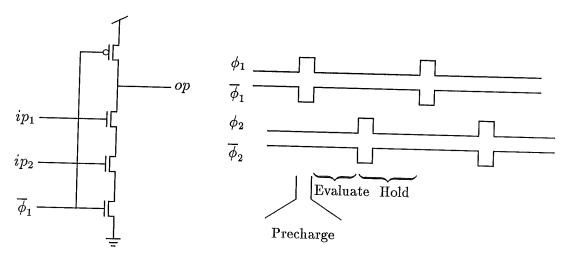

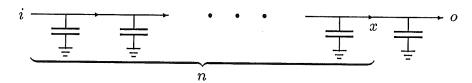

There is however still another refinement that can be made to this n-p-CMOS design style. Consider what happens if there is a very long chain of gates. As soon as the circuit goes into the evaluation phase, evaluation begins at the start of the chain and ripples down to the end. Depending on the length of the chain, the amount of time needed before the last gate in the chain finishes evaluation can be fairly large. During this period, most of the gates are idle; they are either waiting for the previous gate to finish evaluation, or have finished evaluation and so are waiting to be precharged in preparation for the next evaluation phase. The only gates which are active during this time are those which are at the waveform

of evaluation propagating down the chain. The only way to get more throughput from such circuits is to have more than one wavefront of evaluation running down the chain.

Since a gate cannot be made to go into another evaluation phase without having gone through a precharge phase first, the only solution is to divide the chain into smaller subchains, and have alternate subchains go into precharge and evaluate periods at different times. This would mean that once a subchain has finished evaluation, the results are passed onto the next subchain which is just coming out of the precharge period. Now the first subchain can go into precharge in preparation for the next set of data to be evaluated. So, this alternation of precharge and evaluation can be used to have multiple wavefront of evaluation running down the resulting large chain. The control mechanism is the obvious problem which is explained next.

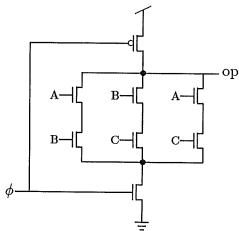

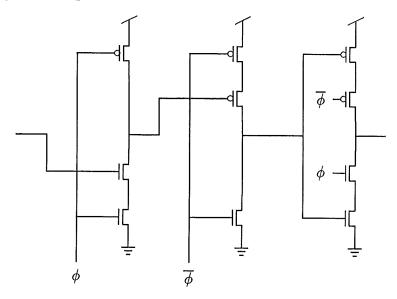

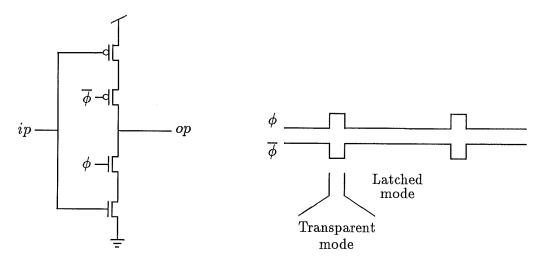

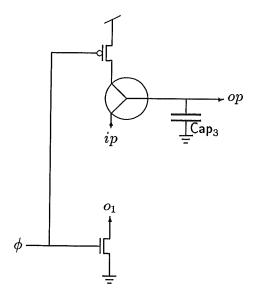

In order to pass the results of one subchain to the next while the first goes through the precharge phase, the results have to be stored at a node between the two subchains. This is achieved by using a simple  $C^2MOS$  latch driven by the same pair of clock lines,  $\phi$  and  $\overline{\phi}$ , as used for the dynamic gates in the subchains. This latch is clocked in such a manner as to latch onto the evaluated results of the subchain just as it goes into the precharge phase, and hold this result static on the output until the next evaluation period. This resulting subcircuit, containing a subchain and a latch to hold the result while the subchain is in precharge, will be referred to as a section. If all consecutive sections are clocked by opposite phases of the clock then the behaviour of the resulting network is such as to allow multiple wavefronts of evaluation to propagate through the circuit at the same time as outlined above.

So from the point of view of the designer the circuit can be viewed as one which is divided into small sections, each terminated by a latch. All the clock lines are swapped between neighbouring sections so that if a p-type gate in one section is clocked by  $\phi$  then the p-type gates in the following section will be clocked by  $\overline{\phi}$ . This has the effect of pipelining the computation along the row of sections. It means that when one section is in the evaluation phase then all the inputs to that section will be stable, since they all come from sections which are in the latched phase. And all sections which are in the latched phase will have all their internal dynamic gates being precharged during this period with their previously calculated results being held static on the output by the latch.

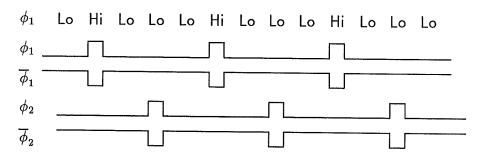

There are three distinct phases in the process of generating an answer on the output of a section. Consider a very simple section having only two dynamic gates

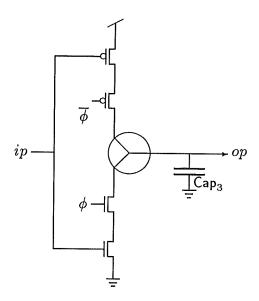

(an n-type and a p-type dynamic inverter) and a latch as shown in Figure 2.8. The answer on the output of this simple circuit is generated by tracing through the following three steps.

Figure 2.8: A simple NORA Circuit

Precharge Phase:  $\phi = \text{low}$ , and  $\overline{\phi} = \text{high}$

- The outputs of all p-type and n-type gates in the section are precharged high and low respectively.

- The latch terminating the section is turned off such that the previous value on the output of the latch is maintained and any further changes on the input to the latch have no effect on the output node until the clock lines toggle.

Evaluation Phase:  $\phi = \text{high, and } \overline{\phi} = \text{low}$

- The latch is turned on such that it becomes transparent, i.e. any changes on the input are reflected straight on the output.

- The evaluation begins from the input end of the section, bubbling the answer to the latch. Since the latch is now transparent the answer goes straight to the output of the section and is held there.

Latch and Precharge Phase:  $\phi = low$ , and  $\overline{\phi} = high$

• The latch terminating the section is turned off such that the previous value on the output of the latch (which is the evaluated result of the section the latch terminates) is maintained, and any further changes on

the input to the latch have no effect on the output node until the clock lines toggle again.

• The outputs of all p-type and n-type gates in the section are again precharged in preparation for the next evaluation phase.

This resulting technique of mixing n-type and p-type dynamic gates together with dividing the circuit into smaller sections to allow multiple wavefronts of evaluation through the circuit is known as the NORA logic design style [Goncalves 83]. The advantages of this technique are that it provides more logic flexibility as compared to the DOMINO style, and the circuits generated are faster and more compact as compared to fully complementary CMOS.

### 2.6.1 Problems with NORA

Unfortunately this design technique does not scale too well. For large circuits the signals on the clock lines will deteriorate due to clock distribution and loadings and will result in slow clock rise and fall times. During the interval when the signals on the clock lines are neither high nor low but somewhere in between, the behaviour of the circuit can no longer be guaranteed to be correct. Consider what happens at the interface between the last dynamic gate in a section and the latch which terminates that section. When the signals on the clock lines are in the process of changing state, then, due to slow clock rise and fall times, the latch may still be in its transparent mode when the gate feeding it starts to go into its precharge mode. This will then result in the evaluated answer of that section being lost and the new precharged value on the output of the dynamic gate being stored on the output of the latch.

This is a recognised problem with the NORA design technique which requires that the rise and fall times on the clock lines be less than a single gate delay. To overcome such problems the solution suggested by Goncalves and de Man in [Goncalves 83] is to use clock buffers at regular intervals to help maintain relatively sharp edges on the clock lines. This is a possible solution which will require considerable planning for the distribution of the clock signals on a chip, but a more general approach to solving this would be to use a two phase non-overlapping clocking scheme which removes the root cause of this problem.

The use of a two phase non-overlapping clocking scheme gives rise to a new design style with its own set of rules for cascading logic blocks. This is the subject matter of the next chapter where it is presented in considerable detail.

### 2.7 Summary

In this chapter various integrated circuit design techniques have been reviewed with particular emphasis on the DOMINO logic design styles. It has been demonstrated how the basic DOMINO logic design style can be generalised by using both ptype and n-type logic gates. This, together with using a C<sup>2</sup>MOS latch, gives rise to a design style known as NORA. Finally the failure mechanism for the NORA design style was briefly outlined. One solution, which forms the basis of the CLIC design style, uses a two phase non-overlapping clocking scheme. This is covered in considerably more detail in the next chapter.

# Chapter 3

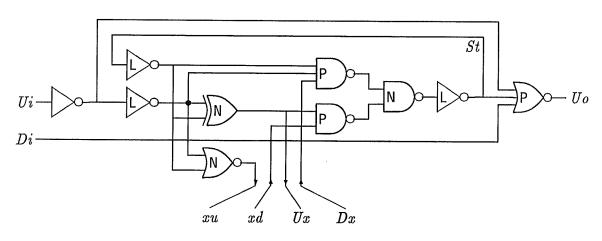

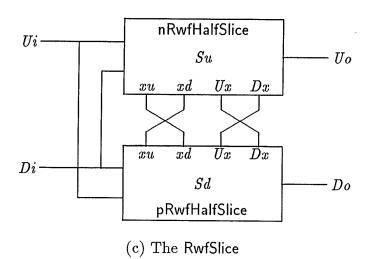

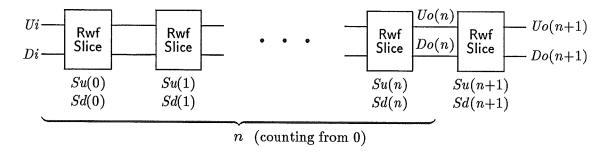

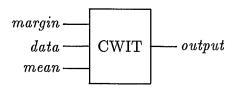

# CLIC: CLock Insensitive Cmos<sup>1</sup>