Number 140

# Executing behavioural definitions in higher-order logic

Albert John Camilleri

July 1988

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 http://www.cl.cam.ac.uk/

### © 1988 Albert John Camilleri

This technical report is based on a dissertation submitted February 1988 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Darwin College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Abstract

Over the past few years, computer scientists have been using formal verification techniques to show the correctness of digital systems. The verification process, however, is complicated and expensive. Even proofs of simple circuits can involve thousands of logical steps. Often it can be extremely difficult to find correct device specifications and it is desirable that one sets off to prove a correct specification from the start, rather than repeatedly backtrack from the verification process to modify the original definitions after discovering they were incorrect or inaccurate.

The main idea presented in the thesis is to amalgamate the techniques of simulation and verification, rather than have the latter replace the former. The result is that behavioural definitions can be simulated until one is reasonably sure that the specification is correct. Furthermore, proving the correctness with respect to these simulated specifications avoids the inadequacies of simulation, where it may not be computationally feasible to demonstrate correctness by exhaustive testing. Simulation here has a different purpose: to get specifications correct as early as possible in the verification process. Its purpose is not to demonstrate the correctness of the implementation—this is done in the verification stage when the very same specifications that were simulated are proven correct.

The thesis discusses the implementation of an executable subset of the HOL logic, the version of Higher Order Logic embedded in the HOL theorem prover. It is shown that hardware can be effectively described using both relations and functions; relations being suitable for abstract specification, and functions being suitable for execution. The differences between relational and functional specifications are discussed and illustrated by the verification of an n-bit adder. Techniques for executing functional specifications are presented and various optimisation stratagies are shown which make the execution of the logic efficient. It is further shown that the process of generating optimised functional definitions from relational definitions can be automated. Example simulations of three hardware devices (a factorial machine, a small computer and a communications chip) are presented.

# Declaration

I hereby declare that this thesis is the result of my own work and, unless explicitly stated in the text, includes nothing which is the outcome of work done in collaboration. No part of this thesis has already been, or is currently being, submitted for any degree, diploma or other qualification at any other university.

Albert John Camilleri February 14, 1988

# Acknowledgements

I am deeply grateful to my supervisor Mike Gordon for his inspiration, guidance and encouragement. Special thanks are also due to Tom Melham for several technical discussions and for reading various drafts of this thesis, including those early drafts which I was too embarrassed to spread around. Mike Gordon also made many useful contributions to later drafts of the thesis.

Other people contributed in various ways: John Herbert advised on the details of the ECL chip; Jon Fairburn came up with all the answers to the 101 questions I posed on lazy-evaluation; and Simone Camilleri made many suggestions on the layout and helped with the intricate work involved in drawing LATEX diagrams.

Thanks are due to Martyn Johnson and Graham Titmus for keeping the systems going, and to all in the Hardware Verification Group for all the interesting meetings, discussions, parties and pub-crawls, especially to the main protagonists: Avra Cohn, Francisco Corella, Inder Dhingra, Thomas Forster, Don Gaubatz, Mike Gordon, Roger Hale, John Herbert, Jeff Joyce, Miriam Leeser, Tom Melham and Ben Moszkowski. All members of the department helped by keeping a cheerful and lively atmosphere.

I would also like to thank Simone for her constant support, encouragement and patience, and my parents for giving me the opportunity to learn and teaching me never to give up.

My studies at Cambridge were supported by a scholarship from the Association of Commonwealth Universities, and by an award from the Lundgren Research Fund. The Dean of Darwin College and Graham Birtwistle of the University of Calgary helped with funding to attend conferences which contributed tremendously towards my research.

# **Dedication**

There is one special person without whom this thesis could never have been—the person who inspired me, filled me with hope and confidence, and spurred me on when I most needed it. To this person I dedicate this thesis.

To Simone

# Contents

| 1 | Intr | oducti   | ion                                           | 1  |

|---|------|----------|-----------------------------------------------|----|

|   | 1.1  | Hardy    | vare Verification and Simulation              | 1  |

|   | 1.2  | Backg    | round and Related Work                        | 3  |

|   |      | 1.2.1    | Simulators and Hardware Description Languages | 3  |

|   |      | 1.2.2    | Verification                                  | 6  |

|   |      | 1.2.3    | Verification and Simulation                   | 6  |

|   |      | 1.2.4    | Programming Languages and Simulation          | 9  |

|   | 1.3  | Overv    | riew of Thesis                                | 10 |

| 2 | The  | HOL      | Theorem Prover                                | 13 |

|   | 2.1  | The F    | OL logic                                      | 13 |

|   |      | 2.1.1    | Terms                                         | 14 |

|   |      | 2.1.2    | Types                                         | 15 |

|   |      | 2.1.3    | Hilbert's $\varepsilon$ -operator             | 17 |

|   | 2.2  | The F    | OL Meta-language                              | 17 |

|   | 2.3  | The F    | IOL System                                    | 23 |

|   |      | 2.3.1    | Theories: Definitions, Axioms and Theorems    | 24 |

|   |      | 2.3.2    | Primitive Inference Rules                     | 25 |

|   |      | 2.3.3    | Tactics and Tacticals                         | 26 |

| 3 | Spe  | cifying  | g and Verifying Hardware                      | 29 |

|   | 3.1  | Relati   | onal and Functional Specifications            | 29 |

|   |      | 3.1.1    | Verification using Relations                  | 32 |

|   |      | 3.1.2    | Verification using Functions                  | 33 |

|   | 3.2  | Repre    | sentation of $n$ -bit Words                   | 33 |

|   | 3.3  | A 1-b    | it Full-Adder                                 | 35 |

|   | 3.4  | An $n$ - | bit Adder                                     | 39 |

|   |      | 3.4.1    | Formal Proof of Relational Specifications     | 42 |

|   |      | 3.4.2    | Formal Proof of Functional Specifications     | 43 |

|   | 3.5  | Proofs   | s Relating Functions and Relations            | 46 |

| 4 | Exe  | cuting  | Specifications                                | 49  |

|---|------|---------|-----------------------------------------------|-----|

|   | 4.1  | ML as   | a Simulation Language                         | 49  |

|   | 4.2  | Combi   | inational Circuits                            | 50  |

|   |      | 4.2.1   | Modelling Logic Gates                         | 50  |

|   |      | 4.2.2   | Modelling Behaviour                           | 52  |

|   |      | 4.2.3   | Modelling Structure                           | 53  |

|   |      | 4.2.4   | Dealing with Partial Specifications           | 55  |

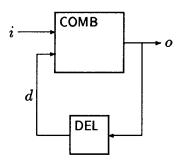

|   | 4.3  | Seque   | ntial Circuits                                | 56  |

|   |      | 4.3.1   | Time, Delay and Clocks                        | 57  |

|   |      | 4.3.2   | Feedback                                      | 59  |

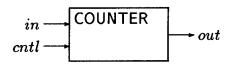

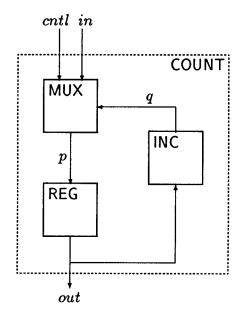

|   | 4.4  | Exam    | ple of a Simple Counter                       | 60  |

|   | 4.5  | ML or   | ELLA                                          | 63  |

| 5 | Fast | ter Sin | nulation Techniques                           | 69  |

|   | 5.1  | Ineffic | iencies in Basic Method                       | 69  |

|   | 5.2  | Memo    | isation                                       | 73  |

|   |      | 5.2.1   | The Algorithm                                 | 73  |

|   |      | 5.2.2   | Implementation                                | 76  |

|   |      | 5.2.3   | Memoisation of the Counter                    | 77  |

|   | 5.3  | Lazy l  | Evaluation                                    | 79  |

|   |      | 5.3.1   | General Simulation Principles                 | 80  |

|   |      | 5.3.2   | The Counter using Lazy Evaluation             | 84  |

|   | 5.4  | Memo    | -functions or Infinite Lists                  | 85  |

| 6 | Exe  | cuting  | the HOL logic                                 | 87  |

|   | 6.1  | From    | Relations to Functions                        | 88  |

|   | 6.2  | Auton   | natically Translating Relations               | 90  |

|   |      | 6.2.1   | Translating Predicates                        | 91  |

|   |      | 6.2.2   | Simple Relational Definitions                 | 92  |

|   |      | 6.2.3   | Primitive Recursive Definitions               | 95  |

|   |      | 6.2.4   | Relations Involving History Functions         | 96  |

|   | 6.3  | Relati  | ons Not Automatically Translated              | 98  |

|   |      | 6.3.1   | Relations with No Functional Interpretation   | 99  |

|   |      | 6.3.2   | Relations Requiring Normalisation             | 100 |

|   |      | 6.3.3   | Relations with Non-Executable Interpretations | 101 |

|   | 6.4  | Auton   | natic Translation of HOL to ML                | 103 |

| 7  | Sim   | ulating a Factorial Machine                     | 107 |

|----|-------|-------------------------------------------------|-----|

|    | 7.1   | The Specification                               | 108 |

|    | 7.2   | The Implementation                              | 109 |

|    | 7.3   | Implementation Using Simpler Primitives         | 114 |

|    | 7.4   | Example Simulations                             | 121 |

| 8  | Sim   | ulating a Computer                              | 125 |

|    | 8.1   | Description of Gordon's Computer                | 126 |

|    | 8.2   | Setting Up wordn Types in ML                    | 128 |

|    | 8.3   | The Target Machine                              | 132 |

|    | 8.4   | The Host Machine                                | 135 |

|    | 8.5   | Executing Programs on Gordon's Computer         | 144 |

| 9  | Sim   | ulating the ECL Chip                            | 149 |

|    | 9.1   | The Specification                               | 149 |

|    | 9.2   | The Implementation                              | 151 |

|    | 9.3   | Example Simulations                             | 157 |

| 10 | Con   | clusions and Future Research                    | 161 |

|    | 10.1  | Summary of Thesis                               | 161 |

|    | 10.2  | Specifying Behaviour                            | 163 |

|    |       | 10.2.1 Automatic Manipulation of Specifications | 163 |

|    | 10.3  | Executing Logic Specifications                  | 163 |

|    |       | 10.3.1 From HOL Relations to HOL Functions      | 164 |

|    |       | 10.3.2 From HOL Functions to ML Functions       | 165 |

|    |       | 10.3.3 Optimising ML Functions                  | 165 |

|    | 10.4  | Automatically Translating Types                 | 166 |

|    | 10.5  | Simulation at a Lower Level                     | 166 |

| Bi | bliog | graphy                                          | 169 |

| A  | Gra   | mmar for Parsing Relations                      | 177 |

| В  | Exa   | mple Interactive Session                        | 179 |

# List of Figures

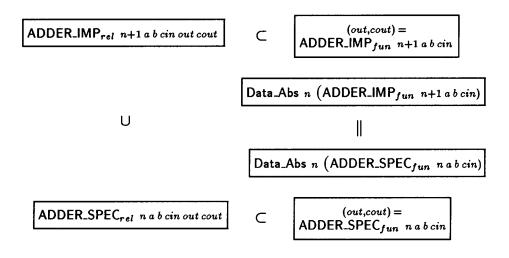

| 1.1 | The Ideal Verification Process                           | 2   |

|-----|----------------------------------------------------------|-----|

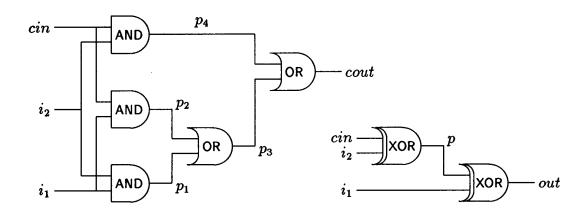

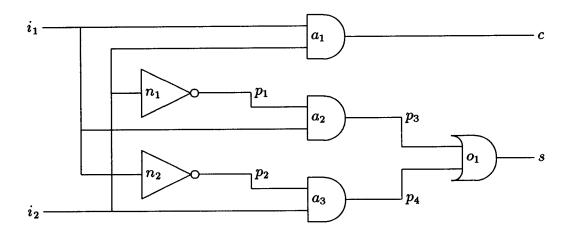

| 3.1 | A Full-Adder                                             | 36  |

| 3.2 | Implementations of CARRY and SUM                         | 36  |

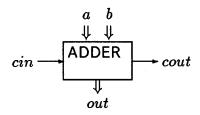

| 3.3 | Specification of a Binary Adder                          | 39  |

| 3.4 | Implementation of a Binary Adder                         | 40  |

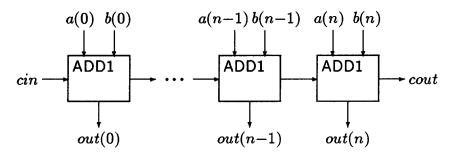

| 3.5 | Correctness Theorems                                     | 47  |

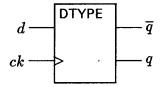

| 4.1 | Specification Diagram of a Counter                       | 61  |

| 4.2 | Implementation of a Counter                              | 61  |

| 4.3 | Implementation of a Half-Adder                           | 64  |

| 5.1 | Example Device for Illustrating Inefficient Modelling    | 70  |

| 5.2 | Tree Illustration of Inefficient Evaluation              | 72  |

| 6.1 | Relational Expressions in the HOL logic                  | 89  |

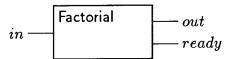

| 7.1 | A Factorial Machine                                      | 108 |

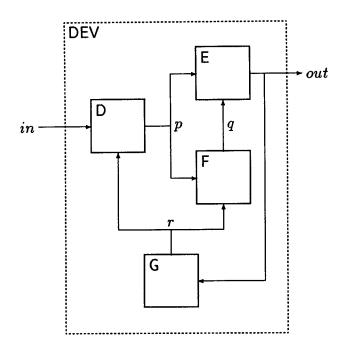

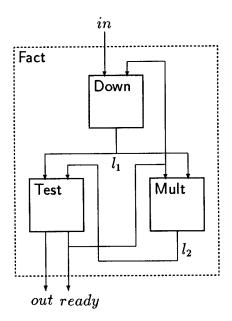

| 7.2 | Implementation of Factorial Device                       | 110 |

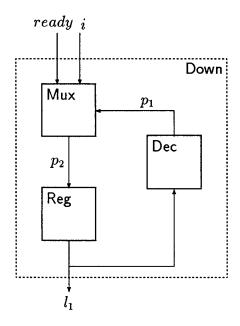

| 7.3 | Implementation of Down                                   | 117 |

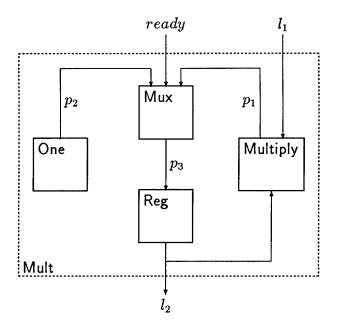

| 7.4 | Implementation of Mult                                   | 118 |

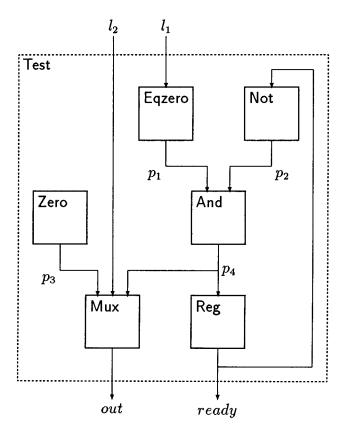

| 7.5 | Implementation of Test                                   | 119 |

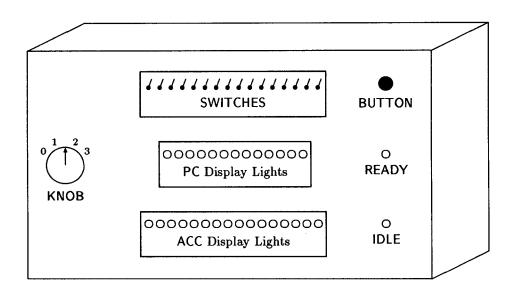

| 8.1 | Front Panel of Gordon's Computer                         | 126 |

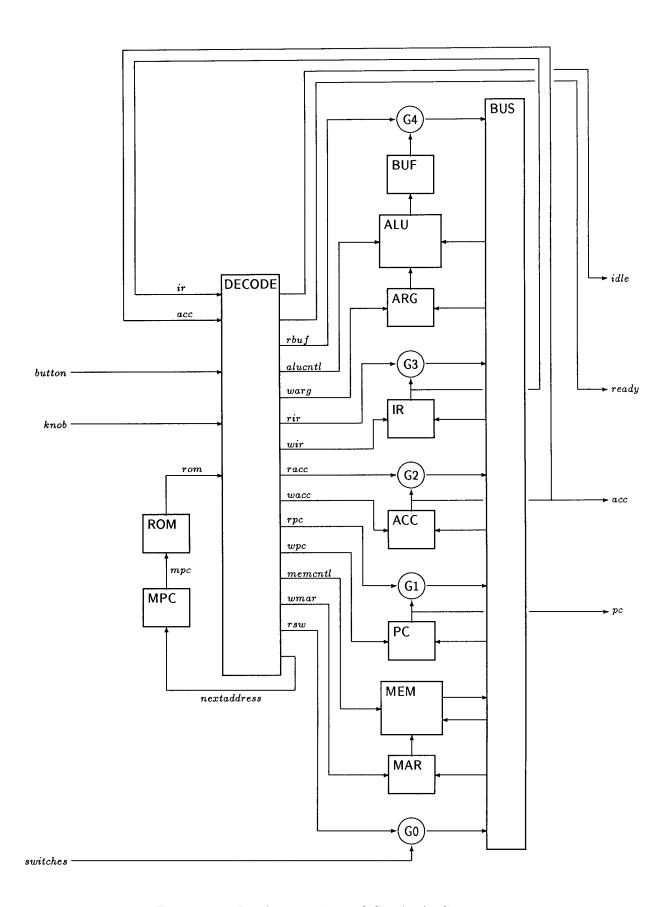

| 8.2 | Implementation of Gordon's Computer                      | 136 |

| 8.3 | Representation of Memory for Program to Add Two Integers | 145 |

| 8.4 | Representation of Program Executed on Gordon's Computer  | 146 |

| 8.5 | Table Displaying Stages of Simulation                    | 147 |

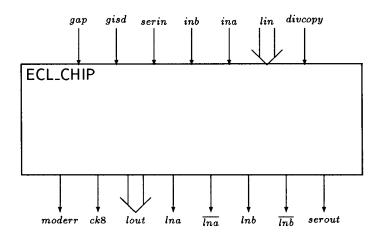

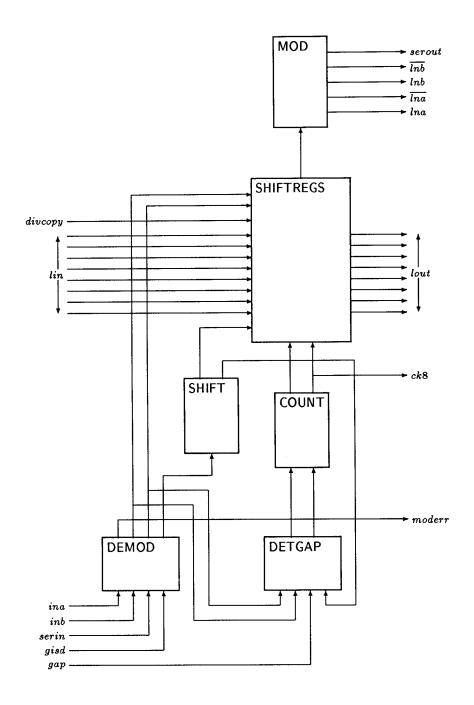

| 9.1 | The ECL Chip                                             | 150 |

| 9.2 | Top-level Implementation of ECL Chip                     | 152 |

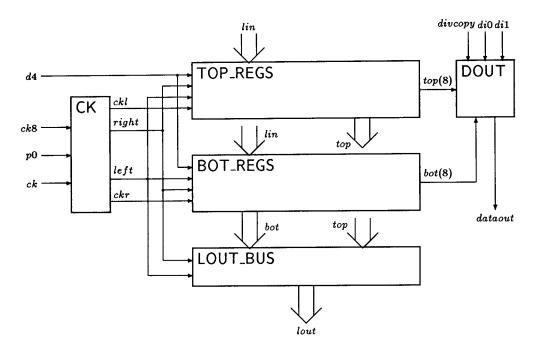

| 9.3 | Implementation of the SHIFTREGS Device                   | 153 |

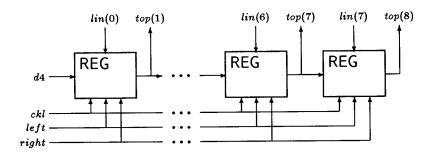

| 9.4 | Implementation of a Shift Register      | 54 |

|-----|-----------------------------------------|----|

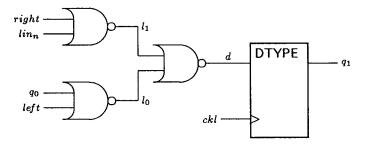

| 9.5 | Implementation of a Register Cell       | 54 |

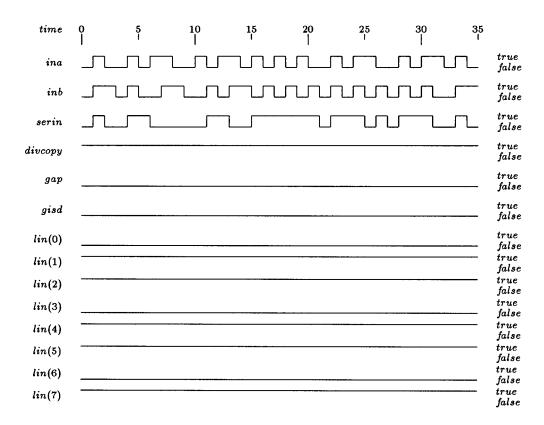

| 9.6 | Waveforms Showing Inputs to ECL Chip    | 57 |

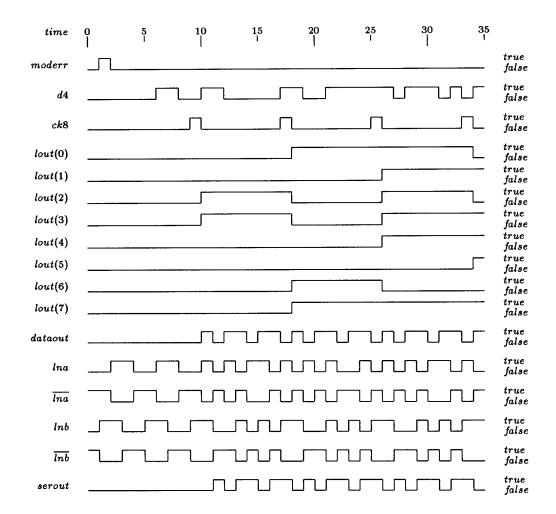

| 9.7 | Waveforms Showing Outputs from ECL Chip | 58 |

# Chapter 1

# Introduction

### 1.1 Hardware Verification and Simulation

Over the past few years, computer scientists have been applying verification techniques to the correctness of digital systems. This was mainly brought on by the increasing inadequacy of conventional approaches (i.e. simulation, prototyping, etc.) which could only demonstrate the presence of a bug, never its absence.

Several mechanical theorem provers have been designed and used for the verification of hardware [27,24,31]. Various techniques and approaches have been adopted but the goal has always been the same: to verify that a given system actually behaves in the desired way.

The idea behind hardware verification is to use a mathematical and logical notation to represent the desired behaviour of a digital circuit (specification) and to prove it equivalent to the representation of a contemplated implementation (verification). The verification process is complicated and expensive. Even proofs of simple circuits can involve thousands of logical steps. Often it can be extremely difficult to find correct device specifications and it is therefore desirable that one sets off to prove a correct specification from the start, rather than repeatedly backtrack from the verification process to modify the original definitions after discovering they were incorrect or inaccurate.

The idea discussed in this thesis is that the techniques of simulation and verification should be amalgamated, rather than have the latter replace the former. The result is that behavioural definitions can be simulated until it is reasonably sure that the specification is correct. Furthermore, proving the correctness with respect to these simulated specifications avoids the inadequacies of simulation, where it may not be computationally feasible to demonstrate correctness by exhaustive testing. In other words, simulation here has a different purpose: to

discover obvious design bugs and to get specifications correct as early as possible in the verification process. Its purpose is not to demonstrate the correctness of the implementation—this is done in the verification stage.

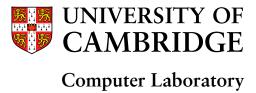

The process of designing and manufacturing a digital circuit can be summarised as shown in Figure 1.1. Ideally, the number of times one backtracks along arc 2 is kept as small as possible by the opportunity of backtracking along arc 1.

Figure 1.1: The Ideal Verification Process

The process starts at the specification and the design stage where specification definitions are written, a design to implement the specification is contemplated, and implementation definitions are written to represent the design. These definitions are simulated until they are fully understood before proceeding to verify them. Inaccurate models and specifications can be corrected by backtracking from the simulation stage to the design and specification stage until one is confident that the models reflect the desired behaviour. Without simulation, however, it would only be possible to backtrack from the verification stage, which usually involves a waste of time and effort. Some backtracking from the verification stage can still be required since design errors not trapped by simulation should be discovered during verification. Once the circuit is verified it can be fabricated. Ideally, there should be no backtracking from the fabrication stage for the purpose of correcting inaccurate designs since verification should yield design implementations which are 100% correct.

In this thesis we describe how the facility to simulate and verify digital systems can be supported in a theorem proving system called HOL, developed by Mike Gordon at the University of Cambridge [22] and based on the LCF system

developed by Robin Milner at the University of Edinburgh [16]. The system uses a version of higher order logic as a formalism for specifying and verifying hardware.

In the following chapters, we show how hardware specifications written in the HOL logic (see Chapter 2) can be cleanly transformed into executable programs which are notationally almost identical to the original non-executable specifications. This enables one to perform simulation in a formal verification environment, and avoids many dangers and inconsistencies introduced if different notations and systems were used for conducting simulation and verification separately.

The ideas presented revolve around the aim of performing simulation and formal verification using the same specifications. The ultimate goal would be to develop an infrastructure which supported several techniques used for designing correct hardware (e.g. silicon compilation, synthesis, timing analysis, simulation, verification), all of which used the same notation. In the rest of this thesis, however, we only discuss techniques that can be used to execute specifications within a theorem proving framework, and hence enable simulation. Before moving on to present the ideas behind the chosen approach, some related works in the areas of simulation and verification are discussed.

### 1.2 Background and Related Work

Some mechanical theorem provers combine the two notions of simulation and verification. The trend, however, has been either to develop a hardware simulator with no infrastructure for conducting formal proof, or to develop a theorem prover (or proof checker) which carries out formal proof by manipulating specifications but which does not do simulation.

Some mechanical systems which have been used for simulation, verification, or both, are described below. It is impossible to cover all the existing simulators and theorem provers; there are too many of them. In general, only those which are directly related to the modelling of digital circuits at the levels of description presented in this thesis are discussed. Furthermore, the discussions of these systems only provide a brief outline of their approach to demonstrating hardware correctness; further details can be found in the bibliography.

### 1.2.1 Simulators and Hardware Description Languages

Simulation has been the traditional approach for demonstrating the correctness of hardware devices. It is the process in which hardware descriptions are subjected to various input stimuli to generate output values which can be examined and checked for errors.

Over the years, many hardware simulators have been developed to model circuits at various levels of description. For example, SPICE [51] is a simulator aimed at the detailed circuit level in which capacitors, resistors, transistors, etc., are represented in terms of their physical magnitudes such as voltage and current, and MOSSIM [6] is a switch level simulator in which transistors are modelled as bidirectional, voltage controlled switches.

In this thesis we will be mainly concerned with writing specifications at the register-transfer level. A simulator which has become widely used at this level of description is ELLA [48], developed by the Royal Signals and Radar Establishment and marketed by Praxis Systems plc.

#### **ELLA**

ELLA supports the simulation of both behavioural and structural specifications of digital systems [55]. In ELLA, circuits are described as networks of nodes connected by wires, where nodes are described by functions and have at least one input and one output. Nodes are allowed to operate in parallel to give a realistic model of hardware, and they can be decomposed into networks of subnodes to allow a hierarchical description of circuits. The notion of nodes, in fact, is similar to that of devices used in the logic specifications presented in this thesis. A case study comparing hardware descriptions in ELLA with those in the general purpose functional programming language ML is given in Chapter 4.

Like other special purpose simulators, ELLA does not adopt a formal approach to demonstrating correctness. Because of the absence of verification facilities in the ELLA system, attempts to introduce formal proof in design processes involving ELLA simulations have required that the ELLA definitions be translated into formal specifications used by mechanical theorem provers (see Chapter 6 and [13]). Such use of different notations is dangerous because inconsistencies can be introduced in the specifications in the process of translation, and also because the semantic differences between two languages can impose completely different representations.

#### **VHDL**

Hardware description languages (HDL) are often used as input languages for computer aided design (CAD) tools. They provide a textual description of structure and/or behaviour which can then be input to simulators, silicon compilers, etc.

Once again, many HDLs have been designed for describing hardware at different levels of abstraction. One example of a HDL which enables the description of both hardware behaviour and structure at a register transfer level is VHDL, a language originated by the United States Department of Defence [57]. The main theme behind VHDL is to support the design, documentation, and simulation of circuits irrespective of different technologies, and to offer the flexibility to cope with new or upgraded CAD technologies.

Circuit descriptions in VHDL make use of ADA constructs to define functions that map from inputs to outputs. The descriptions are divided into two parts: a definition of the interface between the design and the outside world (i.e. the ports), and a functional definition of the circuit.

As is typical of other HDLs, however, VHDL does not have a formal semantics. For this reason, the approach described in this thesis is to translate formal specifications written in the HOL logic into a language which has a similar semantics, rather than to interface HOL with a HDL where the lack of formal semantics can give rise to ambiguous descriptions.

#### DAISY

One approach to hardware specification which enables simulation and has a formal semantics basis is DAISY, a system designed by Steven Johnson at Indiana University for conducting synthesis of hardware designs [32]. Specifications in DAISY are typed recursion equations based on the notation and semantics of the Scott-Strachey calculus [59].

It is not possible, at present, to conduct verification using DAISY, although it would seem that a theorem prover could be added to the system. This would address the concept of combining verification and simulation using the same specifications as presented in this thesis, but using the opposite approach (i.e. adding proof infrastructure to an existing system that supports executable specifications, rather than adding tools to an existing theorem prover that enable the specifications to be executed). The DAISY system, however, was mainly intended for synthesis, a technique for deriving correct implementation designs from specifications by construction. Hence, an alternative approach to verification is adopted for demonstrating correctness of designs.

Recent work by John O'Donnell at Indiana University and the University of Glasgow, has concentrated on automatically constructing the geometrical layout of hardware designs [52], and is highly influenced by the methodology of DAISY.

#### 1.2.2 Verification

#### Higher Order Logic

At the other end of the scale, VERITAS, developed by Keith Hanna at the University of Kent at Canterbury, is a mechanical theorem prover which has been applied to hardware verification [24]. The VERITAS logic is a species of higher order, polymorphically-typed logic [25]; its type structure is based on Martin-Löf's Intuitionistic Type Theory [37].

The use of higher order logic for hardware verification was first advocated by Keith Hanna, and has proved to be a promising formalism for specifying all aspects of hardware. Other theorem provers based on higher order logic include HOL (described in this thesis), and a system developed by Mike Fourman at Brunel University [15].

The higher order logic used in VERITAS is different from that presented in this thesis. Currently, specifications in VERITAS cannot be executed so no simulation is possible using it. It is only possible to conduct formal verification.

Hans Eveking also uses a version of higher order predicate logic for hardware verification [14]. Both the inadequecies of simulation, and the inability of HDLs to allow formal reasoning about specifications are identified in [14], and hence, Eveking's methods combine the use of HDLs with predicate calculus, replacing the HDL specifications by logical formulae in order to enable verification. Our approach is to avoid translating to and from HDLs, and to show that execution of a subset of the logic provides good enough simulation facilities, making the use of HDLs and special purpose simulators unnecessary to aid the verification process.

#### 1.2.3 Verification and Simulation

In this subsection, we present descriptions of various systems in which it is possible to conduct both simulation and verification. Each system has been chosen to typify a different approach. Some of these systems can seem more natural in supporting simulation than the approach described for HOL in this thesis. For example, in BOYER-MOORE and CIRCAL (see below) specifications can be simulated without requiring any translation into executable languages.

The research explained in this thesis, however, is also intended to show that although higher order logic sentences do not in general have an executable interpretation, the subset used for modelling hardware can be executed. Predicate logic specifications are abstract definitions (unlike in the BOYER-MOORE system

where specifications are programs) and so they have to be transformed into an executable notation if they are to be executed. From the experiences gained with HOL, the addition of simulation facilities to the system greatly helps the process of understanding specifications and conducting verification. The transformation process from abstract specifications to programs is not overly tedious since the translation process has been automated. It is recognised that it is insufficient to claim that specifications can be executed; they must be executed with an acceptable efficiency. It is later shown, therefore, that the execution strategies adopted enable efficient simulation of large, and real circuit designs.

In the light of the above, the provision of simulation facilities in HOL as described hereafter makes a useful contribution to the application of logical inference theorem provers to formal hardware verification by enabling efficient execution of specifications to support verification.

#### **BOYER-MOORE**

The BOYER-MOORE theorem prover, developed by Robert Boyer and J Strother Moore, is one of the leading automatic theorem provers [5]. This theorem prover is a mechanisation of a quantifier-free first order logic. Automatic proof is conducted by applying a set of heuristics in turn to a goal; if the goal is found to be true it is returned as a theorem and saved in a data base where it can be used to prove other theorems. Often, theorems cannot be proven straight away and require simpler and more general theorems to be proved and inserted in the database before the proof of the intended theorems can be conducted successfully. Primarily, the BOYER-MOORE logic is not typed although a form of type restriction can be employed explicitly by the use of functions which determine the nature of data types.

The BOYER-MOORE prover has been recently used to formally specify and verify a microprocessor called FM8501 by Warren Hunt Jr. [31]. Since the specifications are actually LISP programs, the LISP evaluation function eval [65] can be used to execute the specifications. Thus, hardware specifications written in the BOYER-MOORE logic can be directly used for both simulation and verification.

#### **CIRCAL**

Another formalism which has been applied to both simulation and verification of hardware circuits is CIRCAL [43], an algebraic calculus developed by George Milne. CIRCAL (CIRcuit CALculus) is based on the Dot Calculus, also invented by George

Milne [42], and is related to the CCS [45] and SCCS [46] calculi developed by Robin Milner.

In CIRCAL one can model concurrency (simultaneous occurrence of events), synchrony (occurrence of events at clocked intervals), and asynchrony (occurrence of events not controlled by clocks) [44]. These three features are among the strong points of CIRCAL which make it attractive both as a hardware description language and as an analytical framework within which to describe, specify and analyse the behaviour of communicating computing agents.

The general approach of CIRCAL to the description of hardware circuits is to formulate the behaviour as communications between agents or processes. Behaviour is specified by a CIRCAL expression which has an associated set of labels (called a sort) to indicate where devices may interact. A set of CIRCAL laws is used to manipulate expressions to conduct verification, whereas simulation is performed by composing expressions describing the behaviour of a device and expressions describing a single pattern of event stimuli [43]. A detailed account of CIRCAL as a medium for conducting simulation and formal verification can be found in [61].

#### **BSPL**

The behavioural specification language BSPL, developed by Martin Richards, is the input to an automatic tool designed primarily for the verification of microcode programs, but which has also been used to specify synchronous circuits [56]. The only data types available in BSPL are words of a specified number of signals, where each signal can take one of four values: 0 (low), 1 (high), X (undefined) and Z (floating). Specifications in BSPL are formal representations of clocked, finite-state machines with inputs, outputs and internal states. One of the hardware examples that has been specified in BSPL is the microcomputer presented in Chapter 8 of this thesis.

#### ITL

Another approach to reasoning about concurrency and hardware is Temporal Logic [23,47]. The imperative programming language Tempura, developed by Ben Moszkowski [50], is based on Moszkowski's earlier work on Interval Temporal Logic (ITL) [49]. In Tempura, the programs are themselves temporal logic formulae, so statements in Tempura can be used to specify, simulate and verify hardware circuits. In temporal logic, one makes use of special built-in operators (such as always

and sometimes) which have an implicit notion of time to represent time-dependent concepts when modelling hardware.

#### $\mu$ FP

The integrated circuit design language  $\mu$ FP, developed by Mary Sheeran, can describe both the behaviour and the layout of a circuit [58]. It is a formal design language with a semantics based on FP [3] but especially geared towards hardware design. The main extension over Backus's FP lies in the introduction of the combining form  $\mu$  which is used to represent memory in sequential circuits.

Circuit descriptions in  $\mu$ FP are functions which take sequences of inputs and return sequences of outputs. These specifications can be manipulated by using algebraic laws to demonstrate correctness by construction. Interpreters for executing  $\mu$ FP specifications have been written in both functional and imperative languages, providing the facility of performing logic level simulation. Design tools also exist for interpreting the specifications to produce a floor-plan of the described circuit.

#### 1.2.4 Programming Languages and Simulation

Over the years, several attempts have also been made to apply general purpose programming languages to hardware simulation. Essentially this approach is a methodology with which features characteristic of programming languages can be exploited to model and simulate hardware circuits. The use of programming languages, however, only enables simulation; there is no infrastructure to support verification. Our approach, therefore, has been to translate formal specifications used by a theorem prover to programs in a general purpose programming language, where the syntax and semantics of the subsets of the two notations required to model hardware at the register transfer level are almost identical.

The fact that general purpose programming languages are expressive enough to model many aspects of hardware designs has been widely demonstrated. Below are a few examples of such programming languages that have been used for hardware simulation.

#### **MIRANDA**

In [29] for example, Stephen Hill shows how the lazy functional programming language MIRANDA [62] can be used to simulate hardware. His techniques rely

heavily on the lazy nature of the language which enables the manipulation of infinite data structures. The ability to evaluate finite portions of infinite data structures allows signals to be represented as infinite lists of logic values. The use of lazy evaluation for hardware simulation is discussed further in Chapter 5.

#### **PROLOG**

William Clocksin has used the logic programming language PROLOG [10] in the role of simulation [9]. Among other features, the relational nature of logic programs is exploited to enable the modelling of bi-directional flow in low-level representations of circuits. This is one advantage over the functional approach since with relations there is no distinction between inputs and outputs. Comparisons between relations and functions form a major topic in this thesis.

#### **OCCAM**

Finally, the features for expressing parallelism in OCCAM [33] were used extensively by David May and David Shepherd to specify, simulate and validate a microprocessor called the IMS T800 [38]. Hardware circuits are specified in OCCAM as a collection of concurrent processes communicating via channels. Parallel computation in OCCAM is very efficient and makes simulation fast. The OCCAM language has a set of laws which can be used to demonstrate correctness by transformation.

## 1.3 Overview of Thesis

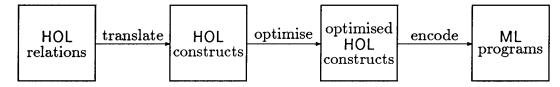

In this thesis we show how a subset of the higher order logic embedded within the HOL theorem proving system can be executed to enable simulation of hardware specifications.

The use of higher order logic as a formalism for specifying and verifying hard-ware circuits is discussed in [21,7], and some substantial and real circuits which have been verified using HOL are presented in [11,28,34]. The suitability of higher order logic as a medium for hardware verification, therefore, has been well established. In this thesis we give evidence that the HOL system can also be used for hardware simulation as a means for supporting verification.

Although logic specifications are in general not executable, we show how the subset of specifications used for hardware verification can be automatically transformed into executable programs. These programs are also automatically optimised to perform at an acceptable speed. In support of the practicality and

versatility of such automatic tools, the specifications of some major examples previously verified in HOL are automatically translated into executable programs and simulated for test data.

Below is a brief description of the organisation of the material presented in this thesis.

- Chapter 2 provides a brief description of the HOL system. We describe the species of higher order logic used, the meta-language ML in which the logic is formulated, and the theorem proving strategies used to conduct proofs in HOL. The main emphasis in this chapter is on those features of the HOL system which are used in later chapters of this thesis.

- Chapter 3 shows how hardware can be specified in HOL. The differences between relations and functions are explained and their respective advantages for modelling hardware are discussed. As an example, an n-bit adder is specified and verified using both relational and functional definitions. It is shown that the two different styles are not equivalent and a relationship between them is described.

- In Chapter 4 the HOL meta-language ML is shown to be a good hardware simulator at the register-transfer level. Furthermore, the style of writing programs in ML that model hardware is shown to be extremely similar to that used in writing HOL specifications in Chapter 3.

- The ML programs, however, are extremely inefficient to execute. In Chapter 5, the nature of the inefficiency is discussed and two optimisation strategies (memoisation and lazy evaluation) are proposed. Both are shown to provide good solutions, but only one technique (memoisation) is adopted and discussed further in the rest of the thesis.

- Chapter 6 covers the algorithms for automatically translating HOL relations to ML functions (or programs). The algorithms are shown to cater for most of the commonly used techniques in register-transfer level representations of hardware. An account is also given of which kind of relations can be automatically translated into executable functions and which do not have functional interpretations.

- Chapters 7–9 illustrate the techniques presented in Chapter 6 by describing the translations of the specifications of three hardware examples which were

previously verified in HOL. The examples are: a factorial machine, a simple microcomputer, and a communications chip. The problems and success encountered with each example are discussed, giving an idea of the practicality and versatility of the automation. The derived programs in each example are simulated over test data to show how this tool can be useful as an aid to verification.

• Finally, Chapter 10 evaluates the research described in this thesis. Some ideas for further research, possible solutions to problems encountered, and improvements to current strategies are also proposed.

# Chapter 2

# The HOL Theorem Prover

The HOL system, developed by Mike Gordon at the University of Cambridge, is a tool intended primarily for hardware specification and verification using higher order logic. It is implemented on top of Cambridge LCF [53] and supersedes the earlier system LCF-LSM [18].

HOL is the name given to the entire theorem proving system which supports higher order logic as a formalism for writing specifications and conducting proofs. In cases where it is necessary to distinguish between the computer system and the species of higher order logic embedded within it, the terminology HOL system and HOL logic is used respectively.

A detailed account of both the HOL system and the HOL logic can be found in [22]. In order to make this thesis self-contained, however, a brief introduction to HOL is given in the following sections. This should enable the reader with little or no experience with HOL to follow the rest of this thesis. Some familiarity with predicate logic is assumed. Readers familiar with HOL may wish to skip to Chapter 3.

### 2.1 The HOL Logic

The species of higher order logic used within the HOL system is a version of Church's Simple Type Theory [8]. The HOL logic uses standard predicate logic notation in which one makes use of the propositional logic connectives denoting negation  $(\neg)$ , conjunction  $(\land)$ , disjunction  $(\lor)$ , implication  $(\supset)$  and equivalence  $(\equiv)$  to connect propositions (such as properties and relations) to form more complicated sentences. Variables in such sentences are bound using universal  $(\forall)$  and existential  $(\exists)$  quantification.

Table 2.1 outlines the syntax and informal semantics of predicate logic. In the table, t,  $t_1$  and  $t_2$  stand for arbitrary terms while t[x] stands for some term containing free occurrences of the variable x.

| Notation                       | Meaning                                |

|--------------------------------|----------------------------------------|

|                                |                                        |

| P(x)                           | x has property $P$                     |

| R(x,y)                         | relation $R$ holds between $x$ and $y$ |

| $ eg t_1$                      | $not t_1$                              |

| $t_1 \lor t_2$                 | $t_1$ or $t_2$                         |

| $t_1 \wedge t_2$               | $t_1$ and $t_2$                        |

| $t_1 \supset t_2$              | $t_1 	ext{ implies } t_2$              |

| $t_1 \equiv t_2$               | $t_1$ if and only if $t_2$             |

| $\forall x.\ t[x]$             | t[x] is true for all $x$               |

| $\exists x.\ t[x]$             | t[x] is true for some $x$              |

| $(t \Rightarrow t_1 \mid t_2)$ | if $t$ is true then $t_1$ else $t_2$   |

Table 2.1: Predicate Logic Notation

Higher order logic generalises first order predicate calculus by allowing higher order variables—i.e. variables ranging over functions and predicates. For example, the induction axiom for natural numbers can be written as:

$$\forall P. [P(0) \land (\forall n. P(n) \supset P(n+1)) \supset \forall n. P(n)]$$

Here, the variable P is quantified and ranges over predicates; such variables are said to be higher order.

#### 2.1.1 Terms

The HOL logic uses four kinds of terms: variables, constants, function applications and lambda expressions.

Variables and constants are denoted by sequences of letters or digits starting with a letter. A few other symbols are also allowed in variable and constant names but will not be mentioned here. For example, x, y1 and gnd can be names of variables or constants. The difference between variables and constants is not apparent at this stage but will be dealt with in a later section on the HOL system when the notion of a theory is introduced.

Function applications have the form  $t_1(t_2)$ , where the subterm  $t_1$  is called the *operator* and  $t_2$  is called the *operand* (or *argument*). Due to the higher order

nature of the logic, the results of function applications can themselves be functions, i.e. functions can take functions as arguments or return functions as results.

To minimise bracketing, function applications can be written as f x instead of f(x). Furthermore, application associates to the left and so,  $t_1 t_2 \ldots t_n$  abbreviates  $((t_1 t_2) \ldots t_n)$ .

Lambda-expressions are the means for denoting functions within higher order logic. The term  $\lambda x$ . t (where t is any expression) denotes the function f, say, defined by

$$f(x) = t$$

If we take t in the above lambda-expression to be the expression x+y such that we have the term  $\lambda x. x+y$  then x is said to be a bound variable, y is a free variable and x+y is called the body of the  $\lambda$ -expression.

#### **2.1.2** Types

The HOL logic is a strongly typed logic, i.e. all terms expressed in this version of higher order logic must have a *type*. Without types, the HOL logic would be unsound as the availability of higher order variables can give rise to a version of Russell's paradox. This can be shown using the following definition of a predicate P:

$$P x = \neg(x x)$$

from which one can derive the paradox:

$$PP = \neg(PP)$$

The above paradox is prevented by the use of types and the reasons for this are presented in [20].

The type system used in the HOL logic is derived from that of PPLAMBDA [16] which, in turn, descends from the type system formulated by Alonzo Church [8]. It allows types to be either:

- atomic (e.g. bool to denote the sets of booleans or num to denote natural numbers), or

- compound (i.e. those types built from atomic (or other compound) types by using type operators).

Examples of type operators in the HOL logic are list,  $\rightarrow$  and #, where list is a unary type operator used to denote a list of values (e.g.  $num \ list$  denotes a list of natural numbers) while  $\rightarrow$  and # are infixed binary type operators used to denote sets of functions and pairs respectively. For example,  $(num \# num) \rightarrow bool$  denotes the type of a function with a domain of pairs of natural numbers and a range of boolean truth values.

Types in the HOL logic can contain variables. In order to demonstrate this, let us consider the function *compose* defined below.

$$compose = \lambda f. \lambda g. \lambda x. f(g x)$$

If compose is applied to two functions, f and g say, then the result would be a function which would apply g to its argument and f to that result.

For example, if not is the boolean negation function of type  $bool \rightarrow bool$  and even is a function of type  $num \rightarrow bool$  which returns 'true' if its arguments are even natural numbers and 'false' otherwise, then the result of applying compose to not and even in that order would be  $\lambda x. not(even x)$  which is a function of type  $num \rightarrow bool$ .

On the other hand, if rnd is a function of type  $real \rightarrow num$  which rounds off a positive real number to the nearest natural number, and log is the arithmetic logarithmic function of type  $real \rightarrow real$ , the result of applying compose to rnd and then log is the function  $\lambda x. rnd(log x)$  of type  $real \rightarrow num$ .

The function compose, therefore, appears to have two different types:

$$(bool \rightarrow bool) \rightarrow (num \rightarrow bool) \rightarrow (num \rightarrow bool)$$

and

$$(real \rightarrow num) \rightarrow (real \rightarrow real) \rightarrow (real \rightarrow num)$$

Indeed it appears that it can have many different types, depending on the types of the functions f and g it is applied to. In the HOL logic,  $type\ variables$  are used to allow functions with more than one possible type to be expressed within the logic. Without type variables, a different function would have to be defined for every type because a single function is not allowed to denote several types.

In HOL, however, it is only necessary to define a single function *compose*. If  $\alpha$ ,  $\beta$  and  $\gamma$  are type variables then *compose* is given the type:

$$(\beta \rightarrow \gamma) \rightarrow (\alpha \rightarrow \beta) \rightarrow (\alpha \rightarrow \gamma)$$

These type variables can be instantiated to different types according to the particular use of the function *compose*. Types containing type variables are called *polymorphic*.

#### 2.1.3 Hilbert's $\varepsilon$ -operator

Hilbert's choice operator,  $\varepsilon$ , plays a very important part in the HOL logic. It is most commonly used to denote values one knows to exist but have no name.

More precisely, if t[x] is a boolean term containing a free variable x of type  $\alpha$ , then the term  $\varepsilon x$ . t[x] denotes some value of type  $\alpha$ , a say, such that t[a] is true. For example,  $\varepsilon x$ .  $(7 < x) \land (x < 9)$  denotes 8 while the term  $\varepsilon x$ .  $x \ge 0$  denotes some unspecified positive number.

In the case that there is no value a such that t[a] is true, then  $\varepsilon x. t[x]$  denotes a fixed but unspecified value of type  $\alpha$ . For example,  $\varepsilon n:num. \neg (n=n)$  denotes an unspecified number. The notation term:type is used within the HOL logic to explicitly specify the type of a term.

No further detail regarding  $\varepsilon$  is given here. For a thorough discussion of Hilbert's  $\varepsilon$ -operator see [36]. A detailed description of how Hilbert terms are included in HOL to build in the Axiom of Choice [26] is given in [20].

The features of the HOL logic necessary to enable an understanding of the rest of this thesis have now been covered and we can go on to show (very briefly) how the logic is implemented in the HOL system. First, however, a brief introduction to ML, the meta-language embedded in the HOL system and with which most of the system is coded, is given.

### 2.2 The HOL Meta-language

The aim of this section is to give an introduction to the ML language; mainly covering those features which are discussed later on in the thesis. The version of ML described here as part of the HOL system is not Standard ML [64] but the LCF meta-language version described in the ML Handbook [12], where a complete description of the ML syntax and semantics is presented.

ML is a typed interactive functional programming language. At the 'top-level' one can:

- evaluate expressions

- perform declarations

The #-symbol is the prompt issued by ML to indicate it is ready for input. An input sequence is terminated by two consecutive semi-colons, ';;', and ML does not respond until these terminating characters are input. To avoid cluttering the text in the following examples, the prompt and terminating characters are only used

when it is necessary to distinguish between the system's response and the user's input.

Comments in ML are enclosed within two %-characters and are completely ignored.

```

#%This is a comment%

```

Anything else, however, is evaluated. If one types in 5;; to the system, ML returns the value 5, specifying its type, *int*. If one tries 9+7;;, the two numbers are added and the value 16 is returned. The special identifier 'it' in ML, recalls the last value evaluated.

```

# 5;;

5: int

# 9 + 7;;

16: int

# it;;

16: int

```

Several expressions can be evaluated in sequence by separating the expressions with a single semi-colon. Thus, when an expression  $e_1; \ldots; e_n$  is evaluated, each sub-expression  $e_i$  is evaluated in turn and the value of the entire expression is that of  $e_n$ . For example,

```

# 5+3;

true;;

true: bool

```

Declarations are performed using let statements. These are of the form let x = e, where the identifier x is bound to the value of expression e. Several declarations can be done in parallel by using 'and' between individual declarations. Local declarations make use of the phrase 'in' before the body of the expression within which the declaration applies.

```

# let x = 5;

x = 5 : int

# let y = 2+3 and z = 0;;

y = 5 : int

z = 0 : int

```

```

# let x = 10 in x \times x;;

100 : int

# x;;

5 : int

```

Destructive assignment is possible in ML provided the variables to be assigned values are first declared for this purpose. This is done by using the keyword letref which declares the identifiers and sets them to an initial value. The infix assignment operator ':=' can then be used to assign values to the declared variables. For example:

```

# letref y = 0;

y = 0 : int

# y := 5+y;

y = 5 : int

```

Another use of the let declarations is to define functions in ML. For example, the statement:

```

let suc n = n+1

```

defines the successor function, suc, with parameter n and body n+1. To apply suc to a particular parameter one merely evaluates the application. For example:

```

# suc 5;; 6: int

```

Once a function or other value is defined in ML and bound to an identifier, that identifier denotes the same function throughout an ML session unless redefined.

In the case of functions with several parameters, the parameters can be either curried or tupled. For example, the function add can be defined with curried parameters:

```

\mathbf{let} \ add \ x \ y = x + y

```

or with a single parameter of the cartesian product type (int#int):

$$let \ add(x,y) = x + y$$

The advantage of curried functions is that they can be partially applied.

As well as taking tuples for parameters, functions can also return tupled results. For example, one may wish to define a function order to take a pair of integers x and y, and return a pair with the two integers in ascending order. One possible

definition of order is given below which makes use of the ML conditional statement.

let

$$order(x, y) = if x > y$$

then  $(y, x)$  else  $(x, y)$

The conditional statement: if a then b else c is often abbreviated to the equivalent notation:  $a \Rightarrow b \mid c$ .

Functions with two parameters can be, and often are, declared as infix functions or operators. In our examples so far, we have already made use of several predeclared infix operators such as +, =, >, etc.

Recursive functions can be defined in ML in almost the same way as ordinary functions. The only difference is that letrec is used instead of let. For example, the factorial function, fact, can be defined recursively as:

letrec

$$fact \ n = \text{if } n = 0 \text{ then } 1 \text{ else } n \times (fact(n+1))$$

Of course, fact can be defined iteratively but since we will not be using iterative loops anywhere in this thesis, the reader is referred to [12] for further details.

One can also represent functions in ML as lambda-expressions. The following two definitions of a function f are equivalent.

$$(\operatorname{let} f x = e) \equiv (\operatorname{let} f = \lambda x. e)$$

Lists in ML are represented by a sequence of objects separated by semi-colons and enclosed within square brackets. All objects within a list must be of the same type. The expressions [], [1; 2; 3] and [true; false] are all examples of lists. A list such as [1; true] will not type check as the objects in the list, 1 and true, are of different types.

The standard functions on lists are:

- hd—returns the head of a list (e.g. hd[1;2] = 1),

- tl—returns the tail of a list (e.g. tl[1;2] = [2]),

- null—boolean function which checks if a list is empty,

- .—infix cons operator (e.g. 1.[2] = [1; 2]),

- @—infix append operator (e.g. [1]@[2] = [1;2]).

Another data type represented in ML is *string*. Strings are any sequence of characters enclosed within single quotes (e.g. 'This is a string'). There are also standard functions on strings such as *concat*, *explode* and *implode*.

Variables and functions in ML can be polymorphic. The notion of polymorphism has already been explained in Section 2.1.2 and so it will suffice here to give an example of how a polymorphic function is defined in ML. Consider the function map defined as follows:

letrec map

$$f l = (null l) \Rightarrow [] | f(hd l).(map f (tl l))$$

Since the types of the two arguments f and l are not specified in the definition of map, ML assumes the types of f and l to be polymorphic and defines map to be a polymorphic function of type:

$$(*\rightarrow **) \rightarrow * list \rightarrow ** list$$

Sequences of asterisks are used to denote type variables in ML. The difference between ML and logic types are briefly explained in the next section.

There are three ways in which one can define new types in ML. The first is by using the command typeabbrev to define new names to abbreviate previously defined types. This does not really define a new type but simply binds a name to a previously defined type. It is useful for shortening long type names or for renaming types more appropriately. For example:

typeabbrev

$$intpair = int #int$$

defines a type intpair to denote pairs of integers.

The two other ways of defining types are used to define altogether new types rather than just abbreviations. New types can be defined to be *concrete* or *abstract*.

Concrete types are used when the objects in the type can be enumerated into subgroups. For example, the declaration:

$$type \ signal = HI \mid LO \mid FLOAT$$

defines a new type signal which has three possible values: HI, LO or FLOAT.

The other way of defining types is by using abstraction. The ML command abstype allows one to make an abstract type declaration. While defining a type ty, say, there are two primitive functions,  $abs\_ty$  and  $rep\_ty$ , which are usable within the context of the type definition. The function  $abs\_ty$  maps the representation of ty to ty while the function  $rep\_ty$  maps ty to its representation. One can also define, within the type declaration itself, further primitive functions to manipulate the new type.

Consider, for example, the type declaration below which introduces a new type trigger, represented by the type bool.

```

= bool

abstype trigger

with

ON

= abs\_trigger\ true

= abs_trigger false

OFF

and

bool_of

= rep\_trigger

and

= abs\_trigger(not(rep\_triggerc))

inv c

and

clock \ n = \lambda t. \ (n = 0) \Rightarrow (abs\_triggerfalse)

and

((t \div n) \times n = t) \Rightarrow (abs\_trigger\ true) \mid

(abs_trigger false)

```

The type declaration makes use of the two locally available functions abs\_trigger and rep\_trigger to define the following primitive functions:

- ON and OFF—two constants of type trigger represented by true and false respectively.

- $bool\_of$ —a function of type  $trigger \rightarrow bool$  which maps a value of type trigger to its representative of type bool. For example,  $bool\_of\ ON = true$ .

- inv—a function of type  $trigger \rightarrow trigger$  which inverts values of type trigger, i.e.  $(inv\ ON = OFF)$  and  $(inv\ OFF = ON)$ .

- clock—a function of type  $int \rightarrow int \rightarrow trigger$ . The application  $(clock \ n)$  returns a function which models a clock with a pulse interval of n. Thus when n is 0, clock(0) returns a function which models a clock which is always OFF (pulse interval is 0, i.e. no pulse). The application clock(1), on the other hand, returns a clock which is always ON (pulse interval is 1, i.e. constant pulse). The application clock(2) models a clock which toggles ON and OFF alternately, and so on. Hence, in the application  $(clock \ n \ t)$ , n determines the frequency of the clock and t represents the time at which the clock value may be evaluated.

Finally, it is worth mentioning the *fail* mechanism built into ML. This can be triggered by the *fail* command and is usually followed by an error message explaining the reason for failure. The *fail* command is especially useful as an escape from a program.

The error messages that follow a *fail* command usually consist of the name of the function in which the failure occurred, thus indicating the code that caused the failure. Messages following a failure, however, can be set to anything desired simply by using the command  $failwith \ s$  (where s is a value of type string) instead of fail, thus generating failure with an error message s.

```

# hd[];;

evaluation failed hd

# failwith 'main program'

evaluation failed main program

```

Failure can also be trapped. The value of the expression  $e_1?e_2$  is that of  $e_1$  if  $e_1$  does not fail; otherwise it is the value of  $e_2$ . This feature is useful as a 'switch' where the sub-program  $e_1$  is executed by default but, in the case that  $e_1$  fails,  $e_2$  will be evaluated rather than failing the entire program.

```

\# (1 \div 0)?100;;

100: int

```

### 2.3 The HOL System

Terms of the HOL logic are represented in ML by enclosing them in double quotes. The syntax of HOL terms has been described in section 2.1.1 although in practice, various combinations of ascii characters are used to represent those logic symbols not supported by the ordinary ascii terminal.

For example,

$$\forall a \ b. \ a \supset b \equiv \neg a \lor b$$

is represented by

In the rest of this thesis we shall use the notation of Section 2.1.1 (i.e. we will be using  $\forall$  instead of ! and  $\supset$  instead of ==>). For a detailed account of the representation of the logic in the HOL system see [22].

When a HOL term is entered in ML, it is type-checked (according to the type rules of the logic—not ML) and, if successful, it is given the ML type term. Care should be taken here not to confuse the terminology HOL terms and ML expressions and, moreover, HOL types and ML types. The rule is as follows:

A HOL term is a special kind of ML expression and is distinguished by a pair

of double quotes enclosing the logical term. HOL terms have an ML type

called term.

• A HOL type is the type of a HOL term and forms an ML type called type. HOL types are expressions of the form ":...".

#### For example:

- (1,2) is an ML expression with type (int # int).

- "(1,2)" is an ML expression with type term (since anything enclosed within double quotes represents a HOL term). The HOL type of this term is (num#num).

- Likewise, ("1", "2") is an ML expression with type (term#term) where each term has HOL type num.

- ": num" is an ML expression with ML type type. It represents the HOL type num.

#### 2.3.1 Theories: Definitions, Axioms and Theorems

In [20], a theorem is defined as a sequent that is either an axiom or follows from other theorems by rules of inference, where

- a sequent is a pair  $(\Gamma, t)$  consisting of a finite set of boolean terms  $\Gamma$  (called assumptions) and a boolean term t (called a conclusion),

- an axiom is a sequent postulated to be a theorem, and

- rules of inference are procedures for deducing new theorems from existing ones (see Section 2.3.2).

When a sequent  $(\Gamma, t)$  is a theorem it is written as  $\Gamma \vdash t$  or, if  $\Gamma$  is empty, as  $\vdash t$ .

Certain types of axioms are classed as *definitions*. Definitions are those axioms of the form  $\vdash c = t$  where c is a constant not previously defined and t is a term containing no free variables. Of course, this kind of axiom is always safe as it merely defines an abbreviation. Ideally, all axioms should be of a definitional form since the freedom to postulate arbitrary axioms allows the introduction of inconsistencies.

To make a definition, prove a theorem, or declare a new HOL type, one must first enter a *theory*. A theory is a collection of types, type operators, constants, definitions, axioms and theorems.

New constants and types can be declared within theories. The distinction between variables and constants is, therefore, that variables are those terms (excluding function applications and  $\lambda$ -expressions) which are not declared as constants within a theory.

Theories can have other theories as parents. If one is working within a theory, th say, and an object from theory th' is required in th, then th' must be declared a parent of th. If th' is a parent of th then all the types, constants, definitions, axioms and theorems available in th' are available in th. Thus, th is said to be a descendant of th'.

#### 2.3.2 Primitive Inference Rules

Theorems in HOL are represented by values of type thm and must be distinguished from values of type  $(term \, list) \# term$ . For one to obtain a new value of type thm, one must apply a sequence of events (constituting a proof) to either axioms or previously proved theorems.

Such procedures for deriving new theorems are called rules of inference. The following is an example of a rule of inference called modus ponens. The example uses standard natural deduction notation where  $t_1$  and  $t_2$  denote arbitrary terms, the theorems above the horizontal line are called the hypotheses of the rule and the theorem below the line is called the consequent.

$$\frac{\Gamma_1 \vdash t_1 \supset t_2 \qquad \Gamma_2 \vdash t_1}{\Gamma_1 \cup \Gamma_2 \vdash t_2}$$

Hence, if we have a theorem of the form  $\Gamma_1 \vdash t_1 \supset t_2$ , say  $y > 1 \vdash y \geq y \supset y^2 > y$ , and we also have the theorem which says that  $\vdash y \geq y$  (i.e. the antecedent of the implication in the first theorem is true,  $\Gamma_2 \vdash t_1$ ), then by the rule of modus ponens the theorem  $y > 1 \vdash y^2 > y$  is derived. In the example above, the assumption  $\Gamma_2$  is empty.

Inference rules are represented in the HOL system as functions in ML. The core of the HOL system is made up of a small set of inference rules called *primitive* inference rules and a small number of definitions and axioms from which all the standard rules of logic can be derived. Indeed, one can derive further inference rules (called derived inference rules) which can be justified solely on the basis of these primitive inference rules and axioms.

The choice of primitive inference rules and primitive axioms in HOL is, to a certain extent, arbitrary, although it is desirable to keep them as small in number as possible so that the implementation of the logic can be kept simple and clean.

For the purpose of this thesis it is not important to list all the inference rules and axioms. The reader is referred to [20] for further details including a complete list of axioms and inference rules in the current version of HOL.

#### 2.3.3 Tactics and Tacticals

In the previous section we described rules of inference and how they can be used to carry out a proof. One starts with a set of definitions and theorems and manipulates them using the inference rules until the desired theorem to be proved is achieved. In other words, truth is preserved from truth. This form of proof is sometimes called *forward* proof.

The HOL system supports another way of carrying out a proof called goal directed proof or backward proof. The problem with forward proof is that it can often be difficult to foresee which definitions and theorems are required to prove the end result, especially if the proof is long and complicated. The idea of goal directed proof is to do the proof backwards, i.e. start from the desired result (called the goal) and manipulate it until it is reduced to a subgoal which is obviously true.

A tactic is an ML function which reduces goals to subgoals. The concept of tactics was invented by Robin Milner [16]. They are used for goal directed proving as described above. Tactics are written in a similar notation to inference rules, but with a double horizontal line. For example, mathematical induction can be coded as a tactic of the form:

$$\frac{\forall n. \ P[n]}{P[0] \quad \forall n. \ P[n] \supset P[n+1]}$$

If the induction tactic is applied to a term of the form  $\forall n. P[n]$ , then the two subgoals P[0] and  $\forall n. P[n] \supset P[n+1]$  are generated.

A goal consists of a pair of values and has ML type (term list)#term. The first element of the pair denotes the assumption list and the second element is the term to be proved. A theorem is proved by applying tactics to every subgoal generated until all subgoals are shown to be true, without the addition of invalid assumptions (see [22]).

Tactics can be combined together by using certain ML functions called *tacticals*. An example of a tactical is THEN where, if  $T_1$  and  $T_2$  are tactics then  $T_1$  THEN  $T_2$  evaluates to a tactic which first applies  $T_1$  to a goal and then applies  $T_2$  to the resulting subgoal or subgoals.

In fact, what really happens when tactics are sequentially applied to goals is that a proof tree is built at the same time as new subgoals are generated. Consider a tactic T and a goal g. If (T g) is evaluated, a pair  $([g_1; \ldots; g_n], p)$  is obtained, where p is a justification of the reduction of goal g to subgoals  $g_1, \ldots, g_n$  (i.e. p can be seen as a forward proof that can 'reverse' the tactic if the subgoal reduction is correct). Hence, if one proceeds to apply more tactics to the subgoals  $g_1, \ldots, g_n$  until all further subgoals are reduced to empty lists of subgoals, and if all the steps reducing  $[g_1; \ldots; g_n]$  to [] are justified by a justification p', then p'[] evaluates to a list of theorems  $[\vdash th_1; \ldots; \vdash th_n]$  such that  $p[th_1; \ldots; th_n]$  evaluates to a theorem  $\vdash th$  achieving g.

In the next chapter we move on to show how HOL can be applied to specifying and verifying hardware. This chapter, although not intended as a HOL manual, has served as an introduction to the main features of HOL which will enable a thorough understanding of the rest of this thesis. Further information on all aspects of the HOL theorem proving system can be found in the various references suggested throughout the text (e.g. [20,22]).

## Chapter 3

# Specifying and Verifying Hardware

The first stage in the process of hardware verification is to write down the mathematical and logical definitions that describe the behaviour of the particular hardware to be verified. The next stage is to design a circuit which operates in the manner specified in the behavioural definitions, and to write down definitions that describe the implementation.

In this chapter we show various ways in which the HOL logic can be used to write hardware specifications and implementation definitions. We also demonstrate how these definitions are used in proof to verify hardware, and illustrate the general ideas presented on the specification and verification of hardware by the example of an n-bit adder.

## 3.1 Relational and Functional Specifications

In HOL, behaviour can be modelled in two different ways: by relations or functions. The relational style is the usual way of writing specifications but the functional style is necessary to facilitate simulation, as described later in the thesis.

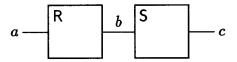

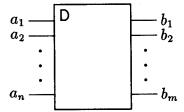

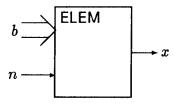

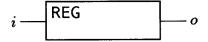

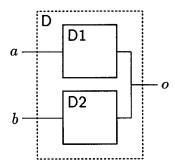

Consider the device D shown below, with input line a and output line b.

The behaviour of this device can be modelled by defining a relation as follows:

$$D_{rel}(a,b) \equiv t [a,b]$$

where  $D_{rel}$  is a predicate symbol of two arguments which abbreviates some boolean term t[a, b] involving a and b.  $D_{rel}(a, b)$  holds if and only if a and b are allowable values on the corresponding lines of D.

The behaviour of D can also be modelled using a function:

$$\mathsf{D}_{fun}(a) = t \left[ a \right]$$

where  $D_{fun}$  is a function symbol of one argument and t[a] is some term involving a. The application  $D_{fun}(a)$  computes the output value on line b of device D given an input value a.

The two models are different. In the relational model all ports of the device are parameters to the specification and no distinction is made between inputs and outputs. In the functional style, however, one is only interested in evaluating the values on the output ports as functions of the inputs. Only the input lines are needed as parameters.

For simple cases, the correspondence between the two styles of definitions is:

$$\mathsf{D}_{rel}(a,b) \equiv (b = \mathsf{D}_{fun}(a))$$

In this chapter, however, we show that this is not generally the case, and an alternative correspondence is explained.

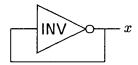

Not only are the two styles different, but in certain cases a relational model is possible when a functional model is not. For example, a delayless CMOS n-transistor shown below:

$$a \xrightarrow{g} b$$

can be modelled using a relation as follows:

$$Ntran(q, a, b) \equiv (q \supset (a = b))$$

where Ntran is a predicate symbol abbreviating the definition of the behaviour of an n-transistor [7]. The above definition states that Ntran(g, a, b) holds if and only if a and b are equal whenever g is true. The predicate Ntran specifies a bidirectional device because there is no distinction between inputs and outputs for the ports a and b. The definition can be used to model port a as input and port b as output, or vice-versa.

With functions, however, a model like the above is not possible. One would have to define functions which model the transistor as a unidirectional device, either with a as an input port and b as an output port, or vice-versa. Reasons supporting the use of both relations and functions are given on page 31.

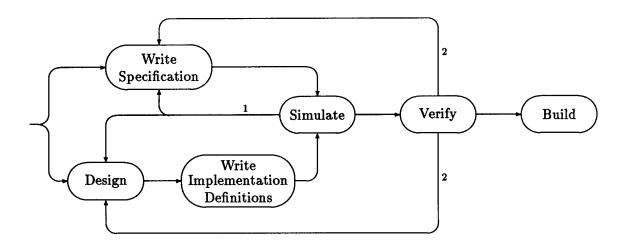

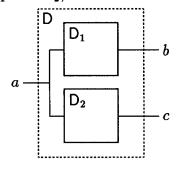

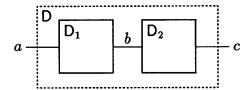

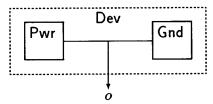

To see how structure can be specified in logic, consider a simple case when internal lines are involved. The diagram below shows the connection of two devices R and S via an internal line b to form a larger device with external ports a and c.

The relational definition for the overall device is:

$$\mathsf{Dev}_{rel}(a,c) \equiv \exists b. \, \mathsf{R}_{rel}(a,b) \land \mathsf{S}_{rel}(b,c)$$

while the functional definition is:

$$\mathsf{Dev}_{fun}(a) = (\mathsf{let}\ b = \mathsf{R}_{fun}(a)\ \mathsf{in}\ (\mathsf{S}_{fun}\ b))$$

The let statement used in the definition above is part of the HOL syntax. In fact it is merely syntactic sugaring for the lambda abstraction used in the alternative definition of  $Dev_{fun}$  below.

$$\mathsf{Dev}_{fun}(a) = (\lambda b. (\mathsf{S}_{fun} \ b))(\mathsf{R}_{fun}(a))$$

In order to be consistent, let statements will be used in functional definitions throughout this thesis. Reasons for using let expressions instead of  $\lambda$ -abstractions are given in Chapter 4.

Two aspects of the above definitions come to attention here.

- The first is that of composition. In the relational model, this is represented by conjunction (Λ). In the functional definition this is represented by evaluating the output of the first 'block' in a structure and passing it on as input to the next 'block'.

- *Hiding* is the other aspect. In the relational model, the use of existential quantifiers ( $\exists$ ) enables one not to mention the internal line variables as parameters to the external relation. The same hiding effect is achieved in the functional model by the use of let statements to declare local variables.

Traditionally, in HOL, it has been more common to model behaviour in a relational way because it is relatively easy and natural to express the behaviour derived from structure relationally. With the use of predicates, one merely states boolean conditions which define the intended behaviour of a device and so one has the advantage of:

• only stating the conditions describing the features of a device which are of interest, thus forming a partial specification,

dealing with bidirectional devices by merely defining relations between ports without distinguishing inputs from outputs (as seen in the transistor example above).

Functional definitions, however, also have advantages.

- They are necessarily total. This will be demonstrated in the following sections discussing the verification of an adder.

- Given a suitable interpreter, they can be executed.

Hence, both relations and functions have advantages. It is therefore desirable to have a theorem prover which supports both styles, and perhaps to translate from one style to another.

Comparisons like "how both relations and functions cope with common techniques such as hiding or structure" are important in developing some form of automatic mapping between relational and functional definitions, and are discussed in a later chapter.

The relations and functions shown above are indeed very similar. This is not, however, always the case, and the verification of an *n*-bit adder described in later sections illustrates this. We first describe general statements that could be proved to demonstrate the correctness of hardware designs using both relational and functional models.

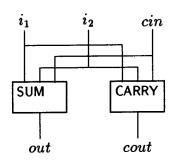

### 3.1.1 Verification using Relations

In this section, we present the general form of correctness statements that can be proved using relational specifications. For simple devices it is possible to prove that the implementation definition and the behavioural specification are equivalent. The correctness statement is of the form:

$$orall i_1 \ldots i_m \ o_1 \ldots o_n. \ \operatorname{\mathsf{Imp}}_{rel}(i_1, \ldots, i_m, o_1, \ldots, o_n) \equiv \operatorname{\mathsf{Spec}}_{rel}(i_1, \ldots, i_m, o_1, \ldots, o_n)$$