Number 135

# Using recursive types to reason about hardware in higher order logic

Thomas F. Melham

May 1988

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

#### © 1988 Thomas F. Melham

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Using Recursive Types to Reason about Hardware in Higher Order Logic

Thomas F. Melham

University of Cambridge Computer Laboratory New Museums Site, Pembroke Street Cambridge, CB2 3QG, England.

Abstract: The expressive power of higher order logic makes it possible to define a wide variety of data types within the logic and to prove theorems that state the properties of these types concisely and abstractly. This paper describes how such defined data types can be used to support formal reasoning in higher order logic about the behaviour of hardware designs.

First printed: May 1988 Reprinted with revisions: April 1990

An earlier version of this paper appears in: The Fusion of Hardware Design and Verification, ed. G.J. Milne (North-Holland, 1988), pp. 27-50.

# Contents

| I                    | ntrod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | duction                                                | 5      |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------|

| 1                    | <b>H</b> a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rdware Verification using Higher Order Logic  Notation | 5      |

|                      | 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Specifying Hardware Behaviour                          | 5<br>6 |

|                      | 1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Specifying Hardware Structure                          | 7      |

|                      | 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Formulating Correctness                                | 8      |

| 2                    | and the state of t |                                                        | 8      |

|                      | 2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Type Definitions                                       | 10     |

|                      | 2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Deriving Abstract Axioms for New Types                 | 12     |

|                      | 2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Recursive Types                                        | 12     |

| 3                    | Reasoning about Tree-Shaped Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                        | 16     |

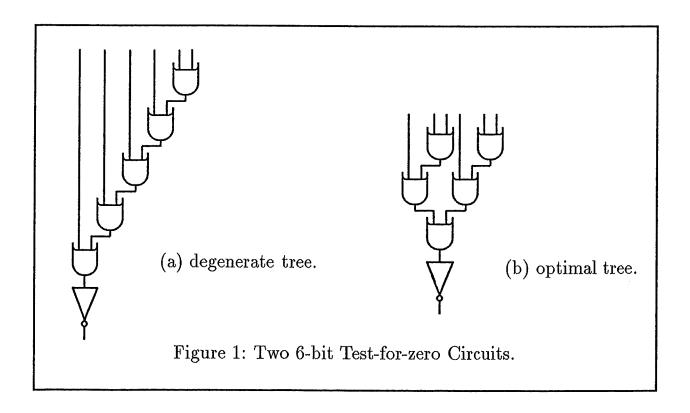

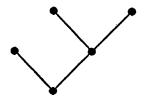

|                      | 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | The Example Device and its Top-level Specification     | 16     |

|                      | 3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Alternative Implementations of the Device              | 18     |

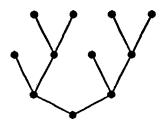

|                      | 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A Type of Binary Trees                                 | 19     |

|                      | 3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Specifying the Set of all Implementations              | 20     |

|                      | 3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | The Proof of Correctness                               | 21     |

|                      | 3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Generating Provably Optimal Implementations            | 22     |

|                      | 3.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Discussion                                             | 23     |

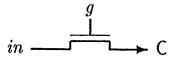

| 4                    | Comparing Two Transistor Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                        | 24     |

|                      | 4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A Switch Model of Transistors                          | 24     |

|                      | 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A Threshold Switching Model of Transistors             | 26     |

|                      | 4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A Recursive Type for the Syntax of MOS Circuits        | 27     |

|                      | 4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | The Semantics of Circuit Terms                         | 29     |

|                      | 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Defining Satisfaction                                  | 31     |

|                      | 4.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Translating Specifications                             | 32     |

|                      | 4.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Relating the Two Models                                | 33     |

|                      | 4.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Discussion                                             | 36     |

| 5 Concluding Remarks |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37                                                     |        |

| Acknowledgements     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                        | 37     |

| References           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                        | 38     |

## Introduction

The aim of this paper is to show how recursive data types can be used to support formal reasoning in higher order logic about the behaviour of hardware devices. Two examples are given: the correctness proof of a class of tree-structured circuits, and the formulation and proof of assertions describing the relationship between two simple transistor models. In both examples, recursive types are used to state propositions about hardware in a general and concise way.

The organization of the paper is as follows. In Section 1, a brief review is given of the conventional techniques for specifying and verifying hardware in higher order logic. Section 2 discusses how recursive types can be added to higher order logic without making ad hoc extensions to the axioms of the logic. Sections 3 and 4 give two examples to show how such recursive types can be used to extend the techniques outlined in Section 1. Recursive types are used in both examples to model the structure of circuits independently of their behaviour.

# 1 Hardware Verification using Higher Order Logic

The basic techniques for specifying and proving the correctness of hardware using higher order logic are well established and are documented in several recent papers [1,6,9,12]. To make this paper self-contained, a brief review is given in this section of these techniques. The version of higher order logic used is based on Church's type theory [3], extended with the type discipline of the LCF logic PP $\lambda$  [7]. This formulation of higher order logic was developed by Mike Gordon for the HOL theorem prover [5] and is described in detail in [4].

## 1.1 Notation

The formulation of higher order logic used in this paper includes terms that correspond to the conventional notation of predicate calculus. A term of the form Px expresses the proposition that x has the property P, and a term of the form R(x,y) means that the relation R holds between x and y. The usual logical operators  $\neg$ ,  $\wedge$ ,  $\vee$ ,  $\supset$  and  $\equiv$  denote negation, conjunction, disjunction, implication, and equivalence respectively. The universal and existential quantifiers  $\forall$  and  $\exists$  express the concepts of every and some:  $\forall x.Px$  means that P holds for every value of x, and  $\exists x.Px$  means that P holds for some (i.e. at

least one) value of x. The additional quantifier  $\exists!$  denotes unique existence:  $\exists! x.P x$  means that P holds for exactly one value of x. Nested quantifiers of the form  $\forall v_1. \forall v_2. \cdots \forall v_n. tm$  can also be written  $\forall v_1 v_2 \cdots v_n. tm$ . Other notation includes  $(c \Rightarrow t_1 \mid t_2)$  to denote the conditional 'if c then  $t_1$  else  $t_2$ ', and  $f \circ g$  to denote the composition of the functions f and g. The constants T and F denote the truth values true and false.

Higher order logic extends the conventional notation of predicate calculus in three significant ways: (1) variables are allowed to range over functions and predicates, (2) functions can take functions as arguments and return functions as results, and (3) functions can be written in the notation of the  $\lambda$ -calculus.<sup>1</sup> For example, the idea that a clock ck rises at some time t can be expressed in higher order logic as follows:

$$\forall ck \ t. \ (\mathsf{Rise} \ ck) \ t = \neg ck(t) \land ck(t+1)$$

In this definition, ck is a higher order variable ranging over functions from time (modelled by natural numbers) to booleans, and Rise is a higher order function that takes a function modelling a clock as an argument and yields a predicate on natural numbers as a result. Conventional practice is that function application in higher order logic associates to the left. For example, the term (Rise ck) t can also be written Rise ck t.

## 1.2 Specifying Hardware Behaviour

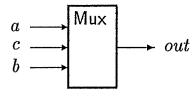

The behaviour of hardware devices can be specified in higher order logic by defining predicates that state which combinations of values can appear on their external ports. Consider, for instance, the one-bit multiplexer shown below:

The behaviour of this device can be specified in logic by a four-place predicate Mux, defined such that the term 'Mux(c, a, b, out)' is true exactly when the

$<sup>^{1}\</sup>lambda$ -calculus notation will not, however, be used in this paper.

combination of the values of the variables c, a, b, and out is one that could occur on the corresponding ports of the device. The definition of Mux is:

$$\mathsf{Mux}(c, a, b, out) \equiv (out = (c \Rightarrow a \mid b))$$

In this specification the variables c, a, b, and out range over boolean truth-values. The predicate Mux asserts that the relationship between these values corresponds to the way a multiplexer works in practice: when the control line c is true, the value on the output out is equal to the value on the input a; and when c is false the value on out is equal to the value on b.

## 1.3 Specifying Hardware Structure

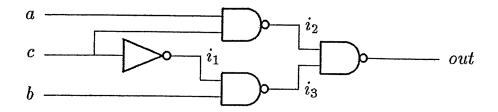

The behaviour of devices constructed by wiring together smaller devices can be represented in logic by conjoining the predicates that specify the behaviours of their components with the logical connective ' $\Lambda$ ' and using the existential quantifier ' $\exists$ ' to hide internal signals [1,6]. Consider, for example, the multiplexer implementation shown below:

If Inv and Nand are predicates that specify the behaviour of an inverter and a NAND-gate respectively, then this multiplexer implementation can be specified in logic by the predicate Mux\_imp defined as follows:

$$\mathsf{Mux\_imp}(c,a,b,out) \equiv \\ \exists i_1 \ i_2 \ i_3. \ \mathsf{Inv}(c,i_1) \land \mathsf{Nand}(a,c,i_2) \ \land \mathsf{Nand}(i_1,b,i_3) \land \mathsf{Nand}(i_2,i_3,out)$$

In this definition the three internal wires  $i_1$ ,  $i_2$ , and  $i_3$  are 'hidden' from the external environment using the existential quantifier ' $\exists$ '. The definition of Mux\_imp states that the values which can appear on the external ports of the multiplexer are precisely those which satisfy the constraints imposed by the predicates modelling the four gates from which it is built.

## 1.4 Formulating Correctness

The predicate Mux defined in Section 1.2 specifies the intended behaviour of a one-bit multiplexer. The multiplexer circuit defined by Mux\_imp can be proved correct with respect to this specification by proving the following theorem:

$$\vdash \forall c \ a \ b \ out. \ \mathsf{Mux\_imp}(c, a, b, out) \equiv \mathsf{Mux}(c, a, b, out)$$

This theorem states that the values which can appear on the external ports of the multiplexer implementation are exactly those allowed by the specification of intended behaviour. The implementation defined by Mux\_imp is therefore correct with respect to the specification given by Mux.

In this simple example, the implementation predicate Mux\_imp is logically equivalent to the specification of intended behaviour Mux. For more complex circuits, however, it may be inappropriate to formulate correctness as logical equivalence. The behavioural specification that a large or complex circuit is expected to satisfy will typically be an abstract description of its intended behaviour. It may be only a partial specification; or it may be given in terms of higher-level data types or a different time-scale than the predicate defining the implementation. In this case, the correctness of an implementation Imp with respect to a specification Spec will not be a logical equivalence,

$$\vdash \forall i \ o. \ \mathsf{Imp}(i, o) \equiv \mathsf{Spec}(i, o)$$

but an implication of the form:

$$\vdash \forall i \ o. \ \mathsf{Imp}(i, o) \supset \mathsf{Spec}(\mathsf{Abs}(i, o))$$

where Abs is an abstraction function that maps input and output signals of the implementation description Imp to corresponding signals of the abstract specification Spec. For a discussion of various ways in which the correctness of circuits can be formulated using such abstraction functions see [12].

# 2 Recursive Types in Higher Order Logic

Higher order logic is a typed logic; every syntactically well-formed term of the logic must have a type that is consistent with the types of its subterms. Informally, types can be thought of as denoting sets of values, and terms can be thought of as denoting elements of these sets. The basic types of the version of higher order logic used in this paper include bool (denoting the set of boolean

truth-values) and num (denoting the set of natural numbers). These two types are examples of type constants; they denote fixed sets of values. Types can be built from other types using type operators. An example is the primitive type operator ' $\rightarrow$ ', denoting the function space operation on types. If  $ty_1$  and  $ty_2$  are types, then the type  $ty_1 \rightarrow ty_2$  denotes the set of all total functions from values of type  $ty_1$  to values of type  $ty_2$ . The syntax of types also includes type variables. These are written  $\alpha$ ,  $\beta$ ,  $\gamma$ , etc., and are used to stand for 'any type'. Type variables occur in Church's formulation of higher order logic as metavariables ranging over types; in the version of higher order logic used here they are part of the object language.

Writing 'tm:ty' indicates explicitly that the term tm has logical type ty. The function Rise defined in Section 1.1, for example, can be written with explicit type information as shown below:

$$Rise:(num \rightarrow bool) \rightarrow (num \rightarrow bool)$$

Such type information will usually be omitted, however, when it is clear from the form or context of a term what its type must be.

As a syntactic device, types are necessary to avoid inconsistency. Without types, the expressive power gained by allowing variables to range over functions makes it possible to write paradoxical expressions in the logic that make it inconsistent (e.g. Russell's paradox). Ensuring that every term has a type which is consistent with those of its subterms makes such expressions syntactically ill-formed, and thus eliminates them from the logic.

The type expressions needed to prevent inconsistency have a very simple and economical syntax. All that is needed are the type constants num and bool, and types of the form  $ty_1 \rightarrow ty_2$ . In principle, every type needed for doing proofs in higher order logic can be written using only these primitive types. But in practice it is desirable to extend the syntax of types to include more kinds of types than are strictly necessary to prevent inconsistency.

Extending the syntax of types in higher order logic allows types to play a mathematical role in reasoning about hardware, in addition to their purely logical role of eliminating inconsistency. In mathematical (and programming) practice the notion of types is used to make distinctions between variables that range over different kinds of values (e.g. numbers, pairs, lists, recursive structures, etc.). From this point of view, a type is the name of a commonly-used set of values of a particular kind, having certain well-defined properties. Such types are often characterized by sets of axioms that define their properties abstractly and concisely.

Many of the sorts of values that arise naturally in reasoning about hardware (e.g. bit-vectors) can be represented by types of this kind. As will be discussed in Section 3, devices whose components exhibit some form of recursively regular structure (e.g. adders and trees of gates) can also be represented by axiomatized data types. While the primitive types of the logic are in principle sufficient to represent these data structures, adding new types to the logic make it possible to formulate propositions about hardware in a more natural and concise way. This pragmatic motivation for a rich syntax of types is similar to the motivation for the use of abstract data types in high-level programming languages.

Section 2.1 below contains a brief explanation of how the syntax of types in higher order logic can be consistently extended using type definitions. These are analogous to abstract type definitions in programming languages like ML [10]; they define a new type by representing it by a set of values of an already existing type. Section 2.3 describes a class of recursive types which can be added to the logic using such type definitions.

## 2.1 Type Definitions

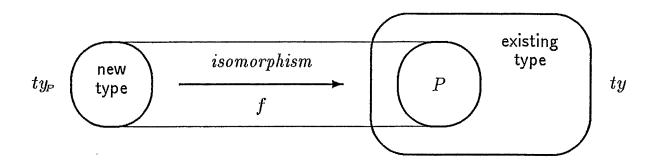

The type definition mechanism described in this section is based on a suggestion by Mike Fourman, which has been formalized by Mike Gordon in [4]. The idea is that a type definition is made by adding an axiom to the logic which asserts that a new type is isomorphic to an appropriate 'subset' of an existing type:

Suppose, for example, that ty is a type of the logic and  $P:ty\to bool$  is a predicate on values of type ty that defines some useful subset of the set denoted by ty. A type definition introduces a new type constant  $ty_P$  which denotes a set having exactly the same properties as the subset defined by P. This is done by extending the syntax of types to include the new type constant  $ty_P$

and then adding an axiom to the logic asserting that the set of values denoted by the new type is isomorphic to the set specified by P:

$$\vdash \exists f: ty_P \to ty.$$

$$(\forall a_1 \ a_2. \ f \ a_1 = f \ a_2 \supset a_1 = a_2) \land (\forall r. \ P \ r = (\exists a. \ r = f \ a))$$

$$\tag{1}$$

This axiom states that there is a function f from the new type  $ty_P$  to the existing type ty which is one-to-one and onto the subset defined by P. The function f can be thought of as a representation function that maps a value of the new type  $ty_P$  to the value of type ty that represents it. Because f is an isomorphism, it can be shown that the set denoted by  $ty_P$  has the same properties as the subset of ty defined by P. By adding this axiom to the logic, the new type  $ty_P$  is therefore defined in terms of the existing type ty.

All types of higher order logic must denote non-empty sets. This means that the predicate P used in the type definition above must be true of at least one value of the representing type; i.e. it must be the case that  $\vdash \exists x:ty. P \ x$ . This theorem must be proved before the type definition axiom (1) can be added to the logic.

If the subset defined by P is non-empty, then adding the type definition axiom (1) shown above is a conservative extension of the logic. That is, for all boolean terms tm not containing the new type,  $\vdash tm$  is a theorem of the extended logic exactly when it is a theorem of the original logic. In particular,  $\vdash$  F is a theorem of the extended logic if and only if it is a theorem of the original logic. Thus adding type definition axioms to the logic will not introduce inconsistency; adding type definition axioms is 'safe'.

In addition to type constants, new type operators can also be defined by adding axioms of the form shown above. For example, a Cartesian product type operator 'x' can be defined by postulating a type definition axiom of the form:

$$\vdash \exists f : (\alpha \times \beta) \rightarrow (\alpha \rightarrow \beta \rightarrow bool).$$

$$(\forall a_1 \ a_2 . f \ a_1 = f \ a_2 \supset a_1 = a_2) \land (\forall r. P \ r = (\exists a. r = f \ a))$$

(2)

where P is a predicate on values of type  $\alpha \rightarrow \beta \rightarrow bool$ , defined such that the subset of  $\alpha \rightarrow \beta \rightarrow bool$  satisfying P represents the Cartesian product of the types  $\alpha$  and  $\beta$ . Since (2) asserts that  $(\alpha \times \beta)$  is isomorphic to this subset, adding this axiom to the logic defines 'x' to be the Cartesian product operation on types. See [4] for details.

## 2.2 Deriving Abstract Axioms for New Types