Number 134

# Correctness properties of the Viper black model: the second level

Avra Cohn

May 1988

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

#### © 1988 Avra Cohn

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Contents

| 1 | Intr           | oduction                                            | 4  |

|---|----------------|-----------------------------------------------------|----|

| 2 | The            | Scope and Limitations of the Proof                  | 10 |

| 3 | The            | Design of Viper                                     | 14 |

|   | 3.1            | Viper Instructions                                  | 14 |

|   | 3.2            | Design Features of Viper                            | 15 |

| 4 | $\mathbf{The}$ | HOL System                                          | 16 |

|   | 4.1            | An Outline of the HOL System                        | 16 |

|   | 4.2            | The Logic                                           | 17 |

|   | 4.3            | The Framework for Expressing the Block Model in HOL | 20 |

|   | 4.4            | Proof in HOL                                        | 22 |

| 5 | $\mathbf{The}$ | Plan for Verification                               | 23 |

| 6 | $\mathbf{Rep}$ | resenting the Problem                               | 26 |

|   | 6.1            | The High Level                                      | 26 |

|   | 6.2            | The Block Level                                     | 30 |

|   | 6.3            | An Example                                          | 31 |

|   |                | 6.3.1 Representing the Whole Block with the Latch   | 35 |

|   |                | 6.3.2 Joining Blocks                                | 45 |

| 7 | Usi            | ng the Representation: The Minor State Transitions  | 51 |

|   | 7.1            | Lemmas about the Thirty-Six Lines                   | 52 |

|   | 7.2            | Lemmas about Sub-Blocks                             | 55 |

|   | 7.3            | The Progression of the Registers                    | 58 |

|   | 7.4            | The Individual Minor State Transitions              | 62 |

|   | 7.5            | Composing the Minor State Transitions               | 65 |

|   | 7.6            | Lemmas for the Composed Transitions                 | 70 |

|   | 7.7            | Remarks                                             | 72 |

| 8 | Usi            | ng the Representation: The Major State Transitions  | 74 |

|   | 8.1            | The Major State Transition Conditions               | 74 |

|   | 8.2            | The Major State Tree                                | 79 |

|   | 8.3            | Major State Transitions                             | 81 |

|   | 8.4            | Conclusions about the Major State Transitions       | 83 |

| 9  | Spec               | culation | n on the Rest of the Proof                      | 84      |  |  |  |  |  |  |  |  |

|----|--------------------|----------|-------------------------------------------------|---------|--|--|--|--|--|--|--|--|

| 10 | $_{ m Less}$       | ons an   | d Conclusions                                   | 90      |  |  |  |  |  |  |  |  |

| 11 | 1 Acknowledgements |          |                                                 |         |  |  |  |  |  |  |  |  |

| 12 | App                |          | The HOL Viper High Level and Block Level Defini | -<br>99 |  |  |  |  |  |  |  |  |

|    |                    |          | gh Level Specification                          | 99      |  |  |  |  |  |  |  |  |

|    |                    |          | The Types                                       | 99      |  |  |  |  |  |  |  |  |

|    |                    |          | The Definitions                                 | 100     |  |  |  |  |  |  |  |  |

|    |                    |          | The High Level State Transition Function        | 102     |  |  |  |  |  |  |  |  |

|    | 12.2               |          | ock Definitions                                 | 102     |  |  |  |  |  |  |  |  |

|    |                    |          | Minor Block Types                               | 102     |  |  |  |  |  |  |  |  |

|    |                    |          | Major Block Types                               | 102     |  |  |  |  |  |  |  |  |

|    |                    |          | Timeout Block Types                             | 102     |  |  |  |  |  |  |  |  |

|    |                    |          | Timing Block Types                              | 103     |  |  |  |  |  |  |  |  |

|    |                    | 12.2.5   | BandStop Block Types                            | 103     |  |  |  |  |  |  |  |  |

|    |                    | 12.2.6   | Decoder Block Types                             | 103     |  |  |  |  |  |  |  |  |

|    |                    |          | ALU Block Types                                 | 103     |  |  |  |  |  |  |  |  |

|    |                    | 12.2.8   | Datareg Block Types                             | 103     |  |  |  |  |  |  |  |  |

|    |                    |          | FSelect Block Types                             | 103     |  |  |  |  |  |  |  |  |

|    |                    | 12.2.10  | External Block Types                            | 104     |  |  |  |  |  |  |  |  |

|    |                    | 12.2.11  | . Memory Block Types                            | 104     |  |  |  |  |  |  |  |  |

|    |                    | 12.2.12  | Minor Block                                     | 104     |  |  |  |  |  |  |  |  |

|    |                    | 12.2.13  | Major Block                                     | 104     |  |  |  |  |  |  |  |  |

|    |                    |          | Timeout Block                                   | 104     |  |  |  |  |  |  |  |  |

|    |                    | 12.2.15  | Timing Block                                    | 104     |  |  |  |  |  |  |  |  |

|    |                    |          | BandStop Block                                  | 105     |  |  |  |  |  |  |  |  |

|    |                    |          | 7 Decoder Block                                 |         |  |  |  |  |  |  |  |  |

|    |                    |          | BALU Block                                      |         |  |  |  |  |  |  |  |  |

|    |                    | 12.2.19  | Datareg Block                                   | 109     |  |  |  |  |  |  |  |  |

|    |                    |          | FSelect Block                                   |         |  |  |  |  |  |  |  |  |

|    |                    |          | 1 External Block                                |         |  |  |  |  |  |  |  |  |

|    |                    | 12.2.22  | 2 Memory Block                                  | 110     |  |  |  |  |  |  |  |  |

| In | $_{ m idex}$       |          |                                                 | 111     |  |  |  |  |  |  |  |  |

# Table of Figures

| Figure | 1 | <br> |  |  | <br>• |  |  |  |  | ٠. | • |  | <br> | <br> | <br> | • | <br>• | • | • |  | <br>• |   | <br> | • | • | <br> | 32 |

|--------|---|------|--|--|-------|--|--|--|--|----|---|--|------|------|------|---|-------|---|---|--|-------|---|------|---|---|------|----|

| Figure | 2 | <br> |  |  |       |  |  |  |  |    |   |  |      | <br> | <br> |   |       |   |   |  |       | • |      |   |   | <br> | 37 |

| Figure | 3 | <br> |  |  | <br>  |  |  |  |  |    |   |  | <br> | <br> |      |   |       |   |   |  |       |   |      |   | • | <br> | 80 |

#### 1 Introduction

This report describes the partially completed correctness proof of the Viper 'block model'. Viper [8,9,10,11,22] is a microprocessor designed by J. Cullyer, C. Pygott and J. Kershaw at the Royal Signals and Radar Establishment in Malvern (henceforth 'RSRE') for use in safety-critical applications such as aviation and nuclear power plant control. To this end, Viper has a particularly simple design about which it is relatively easy to reason using current techniques and models.

The designers, who deserve much credit for the promotion of formal methods, intended from the start that Viper be formally verified. Their idea was to model Viper in a sequence of decreasingly abstract levels, each of which concentrated on some aspect of the design, such as the flow of control, the processing of instructions, and so on. That is, each model would be a specification of the next (less abstract) model, and an implementation of the previous model (if any). The verification effort would then be simplified by being structured according to the sequence of abstraction levels. These models (or levels) of description were characterized by the design team. The first two levels, and part of the third, were written by them in a logical language amenable to reasoning and proof. The top level model was a simple, direct state transformation function – a conditional expression specifying the effect on Viper's registers of processing each class of machine instructions (see [8] and [5]). The lowest level model in the sequence was the circuit structure itself, expressed in the hardware description language ELLA; and there were several levels in between.

To give due credit all around, all of the design work for Viper was carried out by the RSRE team. So also was the plan for verifying Viper and for structuring the verification effort, as well as the design, into a sequence of abstraction levels. The RSRE team produced the first two levels of specifications of Viper (and part of the third) in a logical language suitable for verification purposes. Further, J. Cullyer carried out a (more-or-less correct) informal paper-and-pencil correctness proof up to the second abstraction level [9]. Viper was not designed in any part or aspect by the Hardware Verification Group at Cambridge University, despite what one reads or hears in the media. The task of formally and mechanically verifying the Viper design (up to register-transfer level) was sub-contracted by RSRE to members of the Hardware Verification Group at Cambridge University, for a period of about two years (see Acknowledgements), during which time the manufacture of the chip was already underway or indeed completed at various U.K. sites. The mechanical verification task was therefore the full extent of the

Cambridge University participation in the Viper project; and the task was carried out during and after the manufacture of the chip.

Verification was intended to be done in HOL (Higher Order Logic) [2,14,15], a theorem-proving system derived from R. Milner's LCF system (Logic for Computable Functions) [12,21] and based on higher order logic as set out by A. Church [3]. HOL was implemented by M. Gordon at Cambridge University and is currently in use by the Hardware Verification Group at Cambridge University and at various sites throughout the world. 'Verification' was understood by the designers (as by the LCF and HOL communities) to mean complete, formal, logical proof in an explicit and well-understood logic. That is, it means proof in the usual mathematical sense of a sequence of inference steps, and not just simulation or some other non-formal process. Proofs of this sort are constructed interactively in HOL with machine assistance and user-guidance, and not (usually) fully automatically.

A case study in the methodology for the Viper proof was carried out by the author and M. Gordon in 1986; this treated a simple hardware device (in fact, a component of Viper) at several abstraction levels down to and including gate level [4]. The first level of the Viper correctness proof was carried out by the author in 1986-7 [5]. (As mentioned, an earlier informal proof had been done by J. Cullyer.) The formal proof, fully completed, confirmed that the second level of description, the 'major state machine', with certain corrections made, faithfully implemented the top level specification of Viper (again, with certain corrections made). The major state machine was designed to implement each top level state transformation (i.e. the processing of each instruction type) by a sequence of lesser steps, each of which determined the next step or else indicated the end of a sequence. The steps were called 'major states'. The major state model concerned itself only with the flow of control in Viper, and not with arithmetic or logical computations. That proof, assisted by the HOL system, consisted of about a million primitive inference steps<sup>1</sup> and took about six person-months to complete. As mentioned, it revealed errors (which were subsequently corrected) in both the major state model and in the top level specification, as presented. These errors, however, did not manifest themselves in the actual Viper chips, so that although the major state model was intended to be a useful link in the chain of abstraction levels, it was of no direct concern to the fabricators of Viper chips.

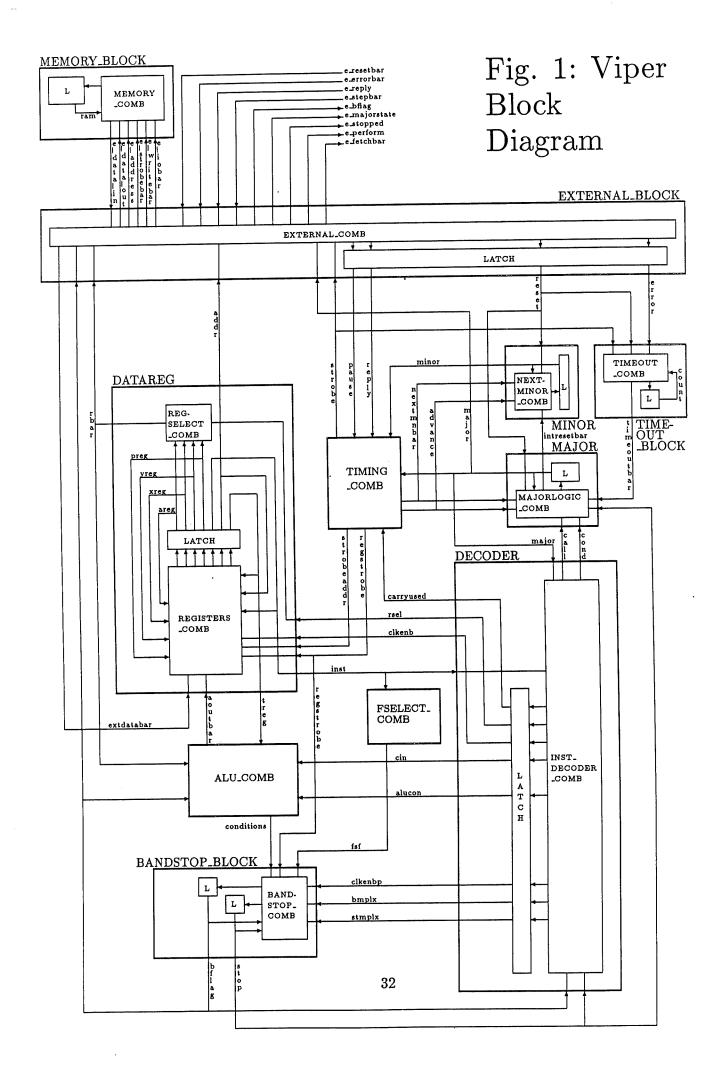

The block model, described here, is of concern to the manufacturers because it directly relates to the circuit design. The block model can be previewed in

<sup>&</sup>lt;sup>1</sup>On the issue of counting inference steps, see the footnote on page 23.

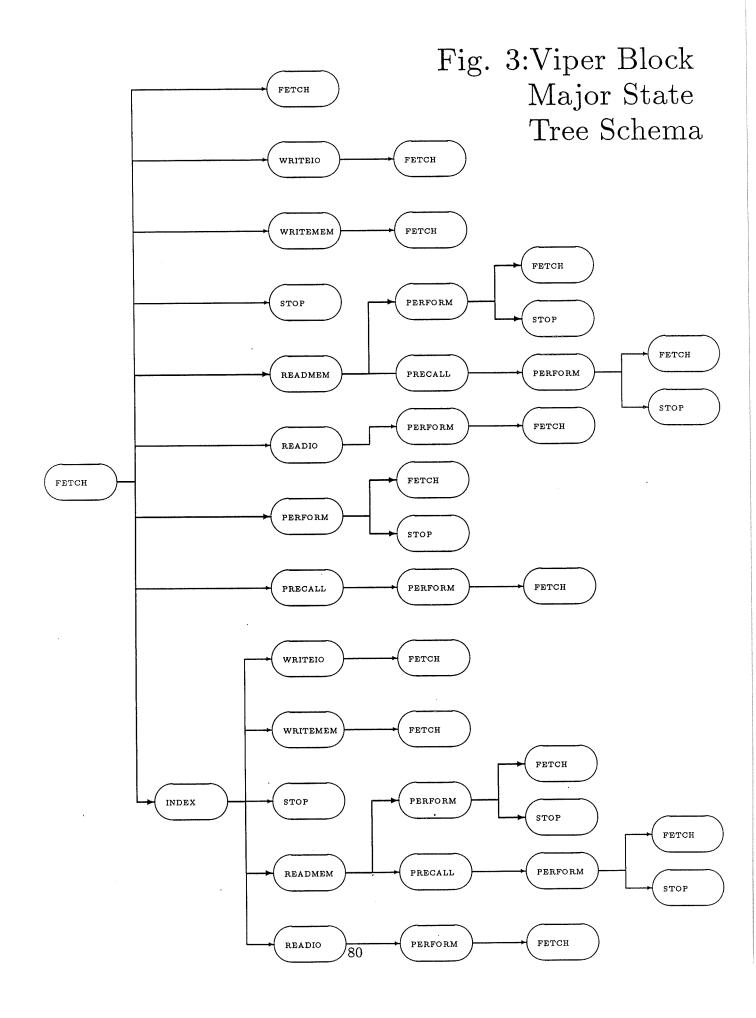

Figure 1 (page 32); it is a partly pictorial and partly textual (and functional) model consisting of 'blocks' (such as Viper's instruction decoder, its ALU and and its memory), with information passing between blocks, and to/from the outside world, at fixed clock cycles. The functional specifications concern the internal combinational logic of the various blocks, but not their time-behaviour, nor the connection between separate blocks; the pictorial specification fills in the rest of that information. Much as at the major state level, the concept of single instruction types being processed by sequences of steps (major states) is built into the block model; specifically, one of the blocks is a counter representing the major state. In addition, several minor states implement each major state in the block model; another block is a counter for minor states. Thus there is a yet-finer time-scale at the block level than at the major state level.

The first task in the verification effort is to derive a functional expression of the block model in a formal logic which is suitable for reasoning and proof. This is necessary because it is difficult to reason formally about a schematic diagram indicating the transfer of information to and from its sub-units simultaneously<sup>2</sup>.

The second task is to analyze the behaviour of the block model using its functional representation. What one ultimately wants to know is (for each instruction type) how many minor and major steps must be cycled through before the instruction is fully processed, and what the accumulated effects are on the 'state' of the block model after that number of cycles. These involve extracting from the formal representation (i) the concept of the state of the block machine; (ii) the conditions under which one state leads to another; and (iii) and the assumptions which must be made about initial states and 'normal' behaviour in order to resolve the state transitions. These concepts are implicitly determined once the functional representation is constructed. It must also be shown that the state transition conditions cover all logical possibilities, to ensure that no possible instruction types have been omitted.

The third task is to deduce the results at the *higher* level for each instruction type, under the same conditions that drive the block machine through its major

<sup>&</sup>lt;sup>2</sup>It is possible to imagine doing this by reasoning about sequences of annotated pictures, but the real problem is not so much the obvious awkwardness of such a method as the lack of a formal semantics of pictures. The 'proof' would not be formal without a clear semantics; that is, we would have to invent and justify a logical calculus whose terms were pictures.

<sup>&</sup>lt;sup>3</sup>'Normal' behaviour means behaviour which is within the scope of the high level specification. For example, we have to assume in the Viper block proof that no resetting signals come in from the outside world during the course of the block-level processing of instructions; and that the block machine's timeout facility is never invoked. This is because the high level specification itself does not treat these block level contigencies.

and minor steps for that particular instruction type. Then, case by case, the results are compared at the two levels. This requires (i) relating the block level state to the higher level state; and (ii) relating the conditions which drive the block machine to the more abstract conditional choices at the higher level. Whether the third task is achieved, as intended, via the major state machine, or is achieved directly by comparing the results to the top level results, is a technical question discussed in Section 10; in this case the latter seems less complicated.

The first task has been completed and is treated in Section 6: from the pictorial and textual block information provided by RSRE we have derived a fully formal expression of the block model from which we can logically infer the block model's behaviour on the various classes of Viper instuctions. This is done using techniques now standard in hardware verification. This task is perhaps the most interesting part of the analysis, and is an important achievement in itself.

The second task has also been completed (see Sections 7 and 8): the functional expression has been used to describe the state transition conditions of the block machine, and then to logically derive the cumulative behaviour of Viper for each instruction type. There are about 120 sequences of major state transitions to consider, each requiring certain assumptions to be made concerning normal behaviour and initial conditions. Every major state transition of the sequences comprises a sequence of minor state transitions. The large number of major state sequences includes all possible types of computation – additions, shifts, comparisons, and so on – with elaborations such as indexed or looked-up operands, and so on. We have also proved that among this multitude of cases no case has been omitted.

The development of the proof up to this point is not fixed in advance; rather, the major and minor state transition conditions are determined by the various block definitions. These are repeatedly unfolded (under the transition conditions for each instruction type) to produce results not necessarily foreseen. This means that the proof (up to this point) makes rather unsophisticated use of HOL; this is the use indicated by the nature of the problem<sup>4</sup>.

The third task has *not* been completed, although some preliminary analysis has been done which indicates that the block results are at least plausible. This is discussed in Section 9. It has proved to be impractical to pursue the third task at present in the absence of (i) better support in HOL for advanced reasoning about intricate bit-string manipulations; and (ii) a better understanding on the

<sup>&</sup>lt;sup>4</sup>Like LCF, HOL provides a repertoire of tools (and facilities for designing one's own tool-set) for proving conjectures by applying strategies in a subgoaling fashion.

part of the author of microprocessor architecture in general and of Viper's design in particular, in order to relate the differing computations at the high and low levels.

In short, what we have achieved is to have proved some useful properties of the block model, without having managed to prove the block model to be an adequate implementation of the top level specification. By describing the cumulative effects on the state of the Viper block model of each instruction class, we have essentially symbolically executed the block model (considered as a finite-state machine). This in itself is valuable; the results of the symbolic execution could be used to build a simulator able to jump (in a provably correct way) from result to result without having to derive the minor and major transitions of the block machine again. Of course, in proving that each derivation is correct and that all possible cases have been treated, we have done rather more than a symbolic execution; and a symbolic execution in itself was not the aim of the work. Nonetheless, the proof can be considered as a kind of 'quality control' for the symbolic evaluation, assuring that the results are dependable. Furthermore, the functional specification of the block model could be used to prove properties of the Viper block model not manifest in the high level specification; for example, we could infer from our representation the consequences of a reset signal or of a 'bad' initial state.

The proof is very hierarchically structured, as one would expect. First the minor state transitions are analyzed (Section 7); then the major state transitions (Section 8.1), themselves composed of minor state sequences; and finally, the cumulative results for major state sequences, which process single instruction types (Section 8.3). The many lemmas required throughout the development form a layered dependence structure. These lemmas are described as they arise. Although it is difficult to find a slice through the proof structure which conveys its interlocking complexity and total bulk, it is clearly impossible (and would be hopelessly boring and repetitious, anyway) to describe the proof as a whole; so as far as possible, a particular instruction type is taken as typical: this is addition with overflow detection.

In the process of performing the proof thus far, a great deal has been learned about managing and properly structuring massive proof efforts. The techniques required did not go beyond anything already standard in HOL circles; and aside from space problems, the proof did not tax the HOL system at all, which is encouraging news about HOL. To date, the block level proof comprises about seven million inference steps and required about one person-year to generate. So far, no

real surprises have emerged about the behaviour of the block machine – but then, surprises would seem likelier to turn up in the third (uncompleted) phase of the project than in the first two. (The preliminary correctness results are described in Sections 8.3 and 9.)

The reader will notice (probably with increasing distress) that this paper is a very straightforward, chronological and (deliberately) detailed account of the proof effort, intended so that anyone wishing to reproduce the proof, or part of it, could use the paper as a reference; and so that dedicated HOL users can examine details. A briefer and more conceptual account is to appear in future [6]. No attempt has been made to explain the design of Viper or the parts and operation of the block machine beyond what is really necessary for describing the formal proof in HOL. Anyone interested in Viper apart from this is referred to the RSRE Viper literature.

Although the paper is meant to stand on its own, it will obviously make more sense in context of the RSRE and HOL literature in general and [5] in particular. A very brief introduction to Viper is given in Section 3, and to HOL in Section 4. Though actual HOL tactics and procedures are only suggested in this report, it should be understood that for every theorem and lemma mentioned, a full formal proof in HOL was performed – by the application of a procedure in HOL's metalanguage ML. From a research point of view, none of the HOL tactics or methods used are particularly original or interesting.

For an overview of the proof effort, Sections 3, 4, 5, 6.1, 6.2 and the Conclusions section should give some idea of what was proved, and a bit about how.

Appendices containing the HOL versions of the original RSRE definitions of the top level and the block level of Viper are provided for reference. The author claims full responsibility for any typographical or other errors in the translation of the original text (which was in an informally annotated and now-obsolete early prototype of the HOL logic, with some misprints) into the HOL logic. Such errors can be difficult to find. The appendices are supplemented by Figure 1 (page 32), a figure compiled by the author from ten separate RSRE figures. To construct Figure 1, the ten separate figures were connected together according to the coincidence of the names of lines amongst the original figures. They were then topologically rearranged, and completed (for type-correctness) by the addition of an extra block (FSELECT\_COMB) as well as six extra internal line names: ram, count, prog, xrog, yrog and areg. The author also claims full responsibility for any errors in the translation into Figure 1 of the original ten figures. All subsequent reasoning about the block

model is based on Figure 1.

Finally, Section 2 contains a discussion of the problems involved in asserting that a chip has been 'verified'. There are great dangers in making such claims if their scope and limitations are misunderstood, as they often are. There is little room for misunderstanding in real-life safety-critical applications. The author strongly urges that Section 2 be read and pondered even if the technical sections are skimmed or skipped.

Several other people have worked on the formal verification of processor designs. Hunt [16] used the Boyer-Moore theorem prover to prove correct the 'FM8501', a microcoded microprocessor that he developed as part of his Ph.D. research. The FM8501 is a machine invented for the purpose of the proof (and not implemented), which therefore has a cleaner specification than Viper; it is roughly as complex as Viper. Joyce [17] has verified Tamarack, another machine invented for proof purposes. Tamarack, though very much simpler than Viper, has actually been implemented and fabricated. The proof was also done in HOL. This work is noteworthy because the proof goes all the way down to the transistor level, and is currently being extended up to software levels. An early version of Tamarack was verified by Barrow using his VERIFY system [1], and again by Gordon using LCF\_LSM [13]; neither of these two latter systems were based on a clearly delineated logical calculus.

#### 2 The Scope and Limitations of the Proof

When we hear that a chip such as Viper has been 'verified', it is essential to understand exactly what is meant. Several important points sharpen and limit the senses in which a chip (and Viper in particular) can be called verified.

Ideally, one would like to prove that a chip correctly implemented its intended behaviour in all circumstances; we could then claim that the chip's behaviour was predictable and correct. In reality, neither an actual device nor an intention are objects to which logical reasoning can be applied. The intended behaviour rests in the mind of the architects and is not itself accessible. It can be reported in a formal language, but not with checkable accuracy. At the same time, a material device can only be observed and measured, not verified. It can be described in an abstracted way, and the simplified description verified, but again, there is no way to assure the accuracy of the description. Indeed, the description is bound to be inaccurate in some respects, since it cannot be hoped to mirror an entire

physical situation even at an instant, much less as it evolves through time. In short, verification involves two or more models of a device, where the models bear an uncheckable and possibly imperfect relation both to the intended design and to the actual device. This point is not merely a philosophical quibble; errors were found both in the top level specification of Viper and in its major state model, none of which was either intended by the designers or evident in the manufactured Viper chips (they are discussed in [5]). The errors were fairly minor and quickly repaired, but their presence throws into relief the rather limited sense in which an actual product can be said to have been verified against the architect's design.

That the actual chips appeared not to suffer from the errors found in the models also illustrates the rather academic nature of the research described in [5] and in the present paper. The chips were already in the process of being built by the time the sub-contracted verification work began on the major state proof at Cambridge; and they had been built and were being advertised by the time the work described in this report was undertaken. While it is possible in theory that an error in an abstract specification had been reflected in the circuit design given by RSRE to the manufacturers – the abstract specifications were no doubt in the architects' minds while they designed the circuit – it seems more likely that because of the weak links between the abstract specifications, the circuit design process and manufacturers, that problems in the specification would not propagate down to chip problems.

At more concrete levels of description, the problem may be further complicated by there not even being provided a description in a formal language. For example, Viper's top level specification and its major state model were both supplied in a logical language; but at the block level, the subject of this report, the description given was partly formally (see the Appendix) and partly pictorially (see Figure 1, page 32). Combining these two parts required some human ingenuity and guesswork (see pages 34 to 35 and 37 to 38). Before verification can be meaningfully applied in such cases, a fully formal description must be produced. Once again, accuracy cannot be checked; the new formal description may be a flawed translation of the pictorial specification, or a flawed combination of picture and text, but there is no sense in which this can be tested. One might thus very well end up proving properties of a formal description bearing an imperfect relation to the intended design. In fact, this was a problem in the block level representation of Viper; the author's first attempt at a formal representation of the Viper block diagram involved interchanged line names whose presence was only discovered (rather later in the proof) by an unsystematic inspection. This additional problem of the accuracy of a representation could appear at the gate level, the transistor level or any other level at which a linguistic description has to be constructed creatively from a pictorial one. It further limits the sense in which a chip can be called verified.

Another point which must be made explicit, given that verification relates a more to a less abstract model, is the level of abstraction and the degree of completeness of the models in question. We say that a device has been verified 'at the major state level' or 'at the register transfer level'; it is not enough to say simply 'verified'. For example, Viper's major state machine has been fully verified with respect to its top level specification, where the major state machine captures the flow of control (implicit at the top level) through the fetch-decode-execute cycle, but does not concern itself with any arithmetic or logic computations. The block machine concerns itself with Viper's arithmetic and logical operations, and with the transfer of information between registers and memory; and not with gate connections, transistors, electrical effects, timing problems, and similar areas in which unsuspected errors seem most likely to be found<sup>5</sup>. In addition, the models may be incompletely specified. For example, Viper's highest level model is complete only as regards the processing of instructions, and does not cover resetting or timingout the machine, or other possible behaviours described at the block level. This restricts any analysis to the high level behaviours alone, again ignoring the more subtle issues. In view of all of this, Viper should not be called verified without reference to the nature of the models used to represent it.

Further, as mentioned, the verification of the block level with respect to the high level has for practical reasons not been completed.

All of these limitations on the use of the word 'verified' are glossed over in advertising claims such as the following [23]:

"VIPER is the first commercially available micropressor with both a formal specification and a proof that the chip conforms to it."

Such assertions, taken as assurances of the impossibility of design failure in safety-critical applications, could have catastrophic results.

<sup>&</sup>lt;sup>5</sup>In those areas, enormous amounts of research remain to be done on finding useful, tractable models, even before we begin to verify them.

#### To summarize,

- A physical *chip* is not an object to which proof meaningfully applies.

- The top level formal specification of Viper (and hence any verification effort) is itself incomplete, covering only the fetch-decode-execute cycle of Viper.

- Viper has been analyzed at best at register-transfer level, i.e. still very abstractly, and not yet at levels at which problems seem likeliest to occur.

- At register transfer level, the proof has been only partially completed.

Finally, the correctness of an abstract representation of a chip must be placed in context when we talk about the reliability of physical systems in safety-critical applications. The author claims no expertise in the field of reliability, but it would be irresponsible not to point out the obvious: that this very abstract and limited sense of correctness (the equivalence of a register transfer level model to a functional specification of the fetch-decode-execute cycle) is only one of many issues which have to be considered collectively. Aside from possible problems at more concrete levels of description, which have already been mentioned, safety will also depend on factors as yet outside of the world of formal description: these range all the way from issues of social administration and communication, as well as staff training and group behaviour, at one end, to the performance of mechanical and chemical parts, and so on, at the other. One has only to list the mass catastrophes of the last ten years or so to perceive the predominant role played by these extralogical factors. It is the author's guess (albeit, again, not an expert opinion) that the sort of a posteriori abstract design correctness discussed in this paper, though of undoubted importance, forms a relatively small contribution to the overall reliability of real machinery. (This seems so at least at the present stage of research into representation and proof, and with the present weak links between designer, verifier and manufacturer.) That is, using a hardware design verified only down to register-transfer level (and there only partially verified and only in 'normal' situations) as part of the control system in extraordinarily hazardous applications (in which large populations or land masses may be destroyed) does not seem significantly safer than using any other design. The use of the word 'verified' must under no circumstances be allowed to confer a false sense of security.

These remarks should be taken as evidence, in our short-sighted times, of the need for further basic research (i.e. the *funding* of further basic research), and

not as pessimism. After all, the HOL system, currently one of very few theoremprovers capable of handling realistic hardware proofs, is directly based on research in pure mathematics and philosophy by Frege, Russell and most directly, Church, many decades ago; and on R. Milner's theorem prover for denotational semantics, a very different application area. The remarks pertain to the current early (but thoroughly optimistic) state of research into the representation and verification of hardware.

# 3 The Design of Viper

Viper [8,9,10,11,22] is a microprocessor designed at the Royal Signals and Radar Establishment and now commercially available. It is intended for use in safety-critical applications, and has several design features supporting such applications. Viper is hard-wired rather than microcoded, to minimize the number of gates. As mentioned in the introduction, no attempt is made in this report to describe the design of the machine or its unique features; for that, the reader is referred to the Viper literature. In this section we introduce only those aspects of the architecture required for a discussion of the correctness proof of the block level model. Indeed, of all the features at that level, only those concerned with (uninterrupted) instruction processing are described. This is because, as mentioned, the top level specification of Viper provided by the designers itself only covers instruction processing.

## 3.1 Viper Instructions

Viper has a 32-bit memory. Addresses are 20-bit words, but the memory is addressed by 21-bit words whose the most significant bit distinguishes main from peripheral memory. (Peripheral memory is for input-output operations.) The registers visible to the user are: a 20-bit program counter, a 32-bit accumulator, two 32-bit index registers, a boolean flag (for holding the results of comparisons, etc) and a stopping flag (which normally indicates an error condition).

Instructions are 32-bit words, of which the top twelve bits are the instruction code and the bottom twenty the address. The twelve bits of the instruction encode the following fields:

- Bit 4: A 1-bit indication of whether the instruction is a comparison;

- Bits 0 to 3: A 4-bit function selector indicating the ALU operation to be computed, according to whether a comparison has been indicated;

- Bits 10 and 11: A 2-bit register source selector for the computation, indicating either the program counter, the accumulator or one of the two index registers as the source of one of the operands;

- Bits 8 and 9: A two-bit memory source selector for the computation, indicating either literal addressing, content addressing, or addressing offset by the value in one of the two index registers as the method of accessing the operand in memory;

- Bits 5 to 7: A 3-bit destination selector to choose a destination for the computation from amongst the accumulator, the two index registers, and the program counter conditionally or unconditionally on the boolean flag.

(Some of these fields can double for other purposes.) The operations are as one would expect: comparisons test numerical less-than and equality between operands; non-comparisons (involving one or two operands) include addition, subtraction, shifts, logical operations, procedure calls, and so on. As mentioned, the example used in this report is addition with overflow detection. In that case, the comparison field holds the value 0 (indicating a non-comparison) and the appropriate function selector value happens to be 5.

## 3.2 Design Features of Viper

Certain internal registers are used (in the course of executing instructions) which are not accessible from the outside: these include a 32-bit temporary register; a 20-bit register for storing the address field of instructions; and a 12-bit register for storing the instruction code.

Viper accepts certain inputs from the outside world which control its behaviour but are not modelled at the top level. (These are all shown in Figure 1, page 32, prefaced by 'e\_'.) They include a signal for resetting the machine (e\_resetbar), one for single-stepping it (e\_stepbar), one for forcing an error (e\_errorbar), and one for extending read/write cycles (e\_reply). There are also outputs to the world, for viewing certain state values directly – for example, the indications of whether the machine is stopped (e\_stopped), is fetching an instruction (e\_fetchbar) or is performing

a computation (e\_perform). The boolean flag and the major state can also be read externally, on e\_bflag and e\_majorstate respectively.

Internally, there is a fixed limit (recorded by a counter, count) to the number of cycles in which the memory can respond, after which an exception occurs (to prevent deadlock due to memory failure)<sup>6</sup>. As mentioned earlier, for establishing the correspondence between the block level and top level models we must assume that certain of these signals are well-behaved; e.g. we assume that the reset signal is false throughout the execution of an instruction, and that at the initial stage in processing an instruction, the timeout-counter is not already at its maximum value.

The Viper chip contains no memory aside from its registers. The block level model, however, includes a simple memory model, since that is the minimum configuration in which it makes sense to talk about executing an instruction (for purposes of verification). The memory model provided is simplified in that it responds in a fixed and minimal number of cycles. The Viper design supports other memory protocols, but these are not modelled by RSRE. This means that the timeout facility (with its counter) is not exercised in the correctness proof.

# 4 The HOL System

The verification described in this report was carried out in the HOL system ('HOL' standing for 'higher order logic'). In this section we attempt to give just enough information about HOL to make the rest of the report readable; readers curious to know more about the system are referred to [2,14,15].

#### 4.1 An Outline of the HOL System

The HOL system is a version of LCF ('logic for computable functions'). LCF was designed by R. Milner in association with C. Wadsworth, M. Gordon, M. Newey and L. Morris [12,21]. HOL, like LCF, is designed to facilitate the interactive generation of formal proofs. In both systems, a logic in which problems can be expressed is interfaced to a programming language in which proof procedures and strategies can be encoded. The combination enables deductions in the logic (in the sense of chains of primitive inference steps) to be produced by invocation of programming constructs at a higher level of abstractness. This makes it possible for very long, detailed, complex proofs in the logic to be produced by use of procedures

<sup>&</sup>lt;sup>6</sup>This is the device verified to gate level as a case study [4].

meaningful to the user of the system – yet without compromising the formality and completeness of the underlying proof. Examples of procedures meaningful to a user might include: unfolding definitions on fixed parameters, normalizing form, case analysis, and rewriting left-to-right using axioms and previously proved theorems.

HOL differs from LCF in the particular logic used. The logic part of HOL is conventional higher-order logic as set out by Church [3]. The version used in the HOL system is oriented towards proofs about hardware only insofar as it provides built-in types, constants and axioms for representing bit strings<sup>7</sup>. New types, constants and axioms can be introduced by the user, and organised in logical theories, as in LCF. Theorems once proved can be saved in and retieved from theories. Theories themselves are organized into hierarchies in which the types, constants, axioms and theorems of an ancestor theory are accessible from within a descendent theory.

The programming language of HOL is ML (for 'meta-language'), which originated as the meta-language in the LCF system (though is now well-known in its own right). The type discipline of ML ensures that the only way to create theorems in the object logic is by performing proofs; theorems have the ML type thm, objects of which can only be constructed by the application of inference rules to other theorems or axioms. (Theorems are written with a turnstile, 1-, in front of them, and with assumptions to the left of the tunstile.) LCF-style proof is explained more fully in [21].

#### 4.2 The Logic

The HOL system uses the ASCII characters  $^{\sim}$ ,  $^{\vee}$ , and  $^{\wedge}$ , ==>, !, ?, and  $^{\vee}$  to represent the logical symbols  $^{\neg}$ ,  $^{\vee}$ ,  $^{\wedge}$ ,  $^{\vee}$ , and  $^{\vee}$  respectively.

For the purposes of this paper a *term* of higher-order logic can be one of the following kinds.

- A variable;

- A constant such as T or F (which represent the truth-values true and false respectively);

- A function application of the form t<sub>1</sub>t<sub>2</sub> where the term t<sub>1</sub> is called the operator and the term t<sub>2</sub> the operand;

<sup>&</sup>lt;sup>7</sup>They are built in only for convenience; the machinery for defining them 'from scratch' exists.

- An abstraction of the form \x.t where the variable x is called the bound variable and the term t the body;

- A negation of the form "t where t is a term;

- A conjunction of the form t<sub>1</sub>/\t<sub>2</sub> where t<sub>1</sub> and t<sub>2</sub> are terms;

- A disjunction of the form t1\/t2 where t1 and t2 are terms;

- An implication of the form t<sub>1</sub>==>t<sub>2</sub> where t<sub>1</sub> and t<sub>2</sub> are terms;

- A universal quantification of the form !x.t where the variable x is the bound variable and the term t is the body;

- An existential quantification of the form ?x.t where the variable x is the bound variable and the term t is the body;

- A conditional of the form t=>t<sub>1</sub>|t<sub>2</sub> where t, t<sub>1</sub> and t<sub>2</sub> are terms; this has if-part t, then-part t<sub>1</sub> and else-part t<sub>2</sub>;

- A local declaration of the form let x=t1 in t2, where x is a variable and t1 and t2 are terms; this is provably equivalent to (\x.t2)t1 (see Section 4.4); and

- A list of the form  $[t_1:t_y;t_2:t_y;...;t_n:t_y]$  where  $t_y$  is a type (see below). Here  $t_n$  is called the zero<sup>th</sup> element,  $t_1$  the  $(n-1)^{th}$  element or the head<sup>8</sup>, and  $[t_2;...;t_n]$  the tail.

All terms in HOL have a type. The expression tity means t has type ty; for example, the expressions Tibool and Fibool indicate that the truth-values T and F have type bool for boolean, and 3:num indicates that 3 is a number.

If ty is a type then (ty)list (also written ty list) is the type of lists whose components have type ty. If ty<sub>1</sub> and ty<sub>2</sub> are types then ty<sub>1</sub>->ty<sub>2</sub> is the type of functions whose arguments have type ty<sub>1</sub> and whose results have type ty<sub>2</sub>. The cartesian product operator is represented by \*, so that ty<sub>1</sub>\*ty<sub>2</sub> is the type of pairs whose first components have type ty<sub>1</sub> and second, ty<sub>2</sub>.

In this paper, the logical constants AND, OR and NOT used by RSRE are used interchangeably with the corresponding HOL constants.

As indicated earlier, the HOL system provides a number of predefined types and constants for reasoning about hardware. The types include  $word_n$ , the type of n-bit words and  $mem_{n1,n2}$  for memories of  $n_2$ -bit words addressed by  $n_1$ -bit words. The

<sup>&</sup>lt;sup>8</sup>The 'reverse' numbering is used to correspond with conventional significance-order of bit-strings

expression  $\#b_{n-1}\cdots b_0$  (where  $b_i$  is either 0 or 1) denotes an n-bit word in which  $b_0$  is the least significant bit.

The predefined constants used in this paper are shown below.

- V:bool list->num converts a list of truth-values to a number;

- VAL<sub>n:wordn->num</sub> converts an n-bit word to a number;

- BITS<sub>n:word<sub>n</sub>->bool list converts an n-bit word to a list of booleans;</sub>

- WORD<sub>n:num->word<sub>n</sub> converts a number to an n-bit word;</sub>

- FETCH<sub>n1:mem<sub>n1,n2</sub>->(word<sub>n1</sub>->word<sub>n2</sub>) looks up a word at an address in memory;</sub>

- $store_{n1}: word_{n1} \rightarrow (word_{n2} \rightarrow (mem_{n1,n2} \rightarrow mem_{n1,n2}))$  stores a word at an address in memory;

- EL:num->(bool list->bool) selects the specified element of a boolean list, where the last (rightmost, in the notation) element of the list is the zero<sup>th</sup>;

- cons:ty->(ty list->ty list), for any type ty, constructs a new list [t;t1;t2;...;tn] from a list [t1;t2;...;tn] and an element t:ty, so that t is the n<sup>th</sup> element of the new list;

- HD:ty list->ty, for any type ty, maps a list  $[t_1; t_2; ...; t_n]$  to  $t_1$ , i.e. to its  $(n-1)^{th}$  element;

- TL:ty list->ty list, for any type ty, maps a list [t1;t2;...;tn] to [t2;...;tn];

- seg:(num#num)->(bool list->bool list) returns the specified segment of a boolean list between and including the elements whose numbers are given;

- NOT<sub>n:word<sub>n</sub>->word<sub>n</sub> inverts the bits of a word;</sub>

- AND,: word, -> word, conjoins two words bit-wise;

- ORn: wordn->wordn disjoins two words bit-wise; and

- ARB is a constant whose type is instantiable to any type; it denotes an arbitrary unspecified value at each type this is useful in certain formal expressions.

To make terms more readable, HOL uses certain conventions. One is that a term  $t_1t_2\cdots t_n$  abbreviates  $(\cdots(t_1t_2)\cdots t_n)$ ; that is, function application associates to the left. The product operator \* associates to the right and binds more tightly than the operator ->. For example, the type of seg could be written simply as num\*num->bool list->bool list. For another example, the function used in the Viper block model to select the register operand for a computation (page 34) has the type

word32#word32#word32#word20#word2->word32

which abbreviates

(word32#(word32#(word32#(word20#word2))))->word32

# 4.3 The Framework for Expressing the Block Model in HOL

The registers of Viper are represented in HOL using the HOL logic's special types for bit-strings. We choose variable names for the various registers so that:

- areg:word32 is the accumulator (a-register);

- xreg: word32 is the first index register (x-register);

- yreg:word32 is the second index register (y-register);

- preg: word20 is the program counter (p-register);

- bflag:bool is the boolean flag (bflag);

- ram:mem21\_32 is the memory;

- treg:word32 is the temporary register (t-register);

- addr: word20 is the address register; and

- inst:word12 is the instruction register.

The constants (predicates) pertaining to hardware are used to manipulate these; for example, if FETCH\_ABBR(ram,preg) is an abbreviation we introduce that denotes the 12-bit instruction code part of the word in the memory ram pointed to by the program counter preg), then

~EL 4(FETCH\_ABBR(ram,preg))

means that the new instruction is not a comparison instruction (see page 15). If in addition

```

WORD4(V(SEG(0,3)(FETCH_ABBR(ram,preg)))) = #0101

```

then (given that the instruction is a non-comparison), the value 5 is defined to indicate the ALU operation: addition with overflow detection. (This is the example computation used throughout the report.)

As mentioned, FETCH\_ABBR is a convenient abbreviation we introduce in the logic. In terms of the basic bit-manipulation function FETCH\_ABBR(ram,preg) stands for

```

EL 4

(BITS12

(WORD12

(V

(SEG

(20,31)

(BITS32

(FETCH21 ram(WORD21(V(CONS F(BITS20 preg))))))))))

```

That is, the new instruction is fetched from the address in the 20-bit program counter (with the twenty-first bit false to indicate main rather than peripheral memory); it is converted into a list of thirty-two boolean values; the upper 12-bit segment (the instruction code) is extracted; its value is considered as a 12-bit string; this is converted to a list of twelve booleans; and the fourth element of the list, the comparison indicator, is selected.

This whole expression (and most subsequent expressions) are pretty-printed for ease of parsing (rather than economy of space!)<sup>9</sup>.

Occasionally, the 12-bit instruction field (usually represented by the variable inst) and the other fields are dealt with separately from the 20-bit address. In such cases we write

```

EL 4(BITS12 inst)

WORD4(V(SEG(0,3)(BITS12 inst)))

WORD3(V(SEG(5,7)(BITS12 inst)))

WORD2(V(SEG(8,9)(BITS12 inst)))

WORD2(V(SEG(10,11)(BITS12 inst)))

```

to denote the comparison indicator, the function selection field, the destination selection field, the memory indicator and the register selector, respectively.

<sup>&</sup>lt;sup>9</sup>Expressions of this sort can sometimes be logically simplified, but this expression is one that actually arises in the analysis, so it is left in the form required.

#### 4.4 Proof in HOL

As an example of HOL features mentioned thus far, consider (in a purely formal way) the simple HOL definition of the block model function which computes the source register for a computation. Given the a-, x-, y- and p- registers as arguments, and the 2-bit source register indicator, the function RECSELECT returns the appropriate register (negated):

```

|- REGSELECT(areg,xreg,yreg,preg,rsel) =

(let rf = VAL2 rsel in

((rf = 0) => NOT32 areg |

((rf = 1) => NOT32 xreg |

((rf = 2) => NOT32 yreg |

((rf = 3) => NOT32(WORD32(VAL20 preg)) | ARB)))))

```

The turnstile indicates either an axiom, a definition or a theorem (here, a definition). Constructs of the logic used include the *let*-construct and the conditional. The constant ARB serves as the final *else*-value of the conditional (which is intended never to be returned, since rsel is a 2-bit word). The HOL bit-string constants used in the definition are: VAL2, WORD32 and VAL20.

The basic rules of inference in HOL take the form of ML functions which (roughly speaking) map theorems (and sometimes various parameters as well) to theorems. More elaborate patterns of inference can be constructed from the basic inference rules of the logic by user-designed ML functions. The validity of the compound inferences is preserved by the type system of ML in which only inference rules may return theorems as results.

In our example, we can transform the definition of REGSELECT more computationally useful by applying a compound inference pattern (an ML function) which expands the *let*-construct into the equivalent lambda expression, and performs the resulting beta-conversions to deduce a new theorem:

Applying the inference pattern actually invokes 520 primitive HOL inference steps (as we have written it) but only requires the user to apply one function to one definition in order to generate the 520-step proof. The pattern applies to any definition written using the *let*-construct. This relieves the user of constructing a 520-step chain of substitutions of equals for equals, and so on (which no one would want to bother with) whilst still assuring that an actual proof is done.

(For perspective, the whole block model correctness proof comprises about seven million primitive inferences<sup>10</sup>.)

Much of the Viper block proof consists in successive unfoldings of known facts on specific values. For example, the new form of the definition of REGSELECT can be applied to particular values, and the resulting theorem then simplified. We can prove for example that

|- REGSELECT(areg, xreg, yreg, preg, #00) = NOT32 areg

by applying a compound inference rule which instantiates the definition to a specific value and then simplifies, using axioms and previously established facts about bit-strings and so on. This particular unfolding consists in 89 primitive inferences. (In a case argument based on the various possible values of real, the theorem above is used to simplify one of the cases.)

Proofs based on unfolding are an example of a particularly simple and unsophisticated use of HOL: they procede in a forward direction, starting without a fixed idea of the result, but applying known procedures. In the block model case, the method allows us to symbolically evaluate the block model on each of the possible instruction types, and so give a complete description of the model's behaviour. In contrast, one often starts with a conjecture – i.e. with an end result in mind – and constructs a proof backwards by engaging proof strategies to produce successively simpler subgoals. As a result of this process, a forward proof is then constructed.

## 5 The Plan for Verification

The original RSRE plan was to establish the correctness of Viper in a series of decreasingly abstract stages.

The top level specification, as mentioned in the introduction, is just a transition function specifying how an abstract state (representing the memory and the visible flags and registers) changes as Viper executes each of the possible instruction types. It thus embodies an operational semantics of the instruction set. The notion of time is implicit in the notion of next state; there are no time variables or clocks.

<sup>&</sup>lt;sup>10</sup>A much shorter proof could be constructed in this particular case, but the figure of 520 arises from the generality of the rule used, which relies on the full power of left-to-right recursive rewriting to expand *let*-expressions (250 steps), and then looks for possible beta-conversions at any depth in the resulting expression. It seems desirable, since many definitions of varying complexity have to be treated similarly, to trade computational resources for user effort in this way. However, the apparent length of proofs can be greatly and sometimes misleadingly inflated by use of such general procedures.

The basic time unit is quite coarse: namely, the execution of a whole instruction schema.

The next (more concrete) level was called the major state level. At the major state level, an instruction is executed by a sequence of events corresponding to major states of the model and representing the phases of processing of an instruction schema. Each event could affect the visible registers of the high level state or any of several internal registers. (These internal registers were still part of an abstract model of Viper, and did not necessarily correspond to parts of the actual Viper chip.) The next event was determined according to the current event, the visible state, and the internal state; some events were recognizably terminal and some are initial, in the sequences. From all of this we extracted a state transition function representing the major state model, which determined a graph of events showing all possible major state sequences of Viper. This led to a correctness statement (proved in HOL) of the following form:

If the major state transition function always gives the next internal state based on the current internal state, and if the state at the start time is the initial state, and if it requires n major state traversals to return for the first time to the initial state, then after n traversals the visible part of the internal state agrees with the new state specified by the top level state transition function.

This was proved by analyzing each path through the graph and comparing the results, under the same conditions which force that path to be taken, with the high level results. There was an explicit notion of time at the major state level in the sequencing and accumulation of effects of the various events; several major state transitions simulated the effect of a single state transition at the high level, i.e. simulated the effect of executing a single instruction. The machine proof was based on a paper and pencil proof by J. Cullyer [9].

The ten (numbered) major states and their associated effects are listed below.

- 0. INDEX: To the temporary register is added the register indicated;

- 1. FETCH: The word indicated by the program counter is got from memory;

- 2. RESET: Various registers are cleared;

- 3. PRECALL: The program counter is stored before a procedure call;

- 4. PERFORM ALU: The appropriate arithmetic-logic operation is done;

- 6. READIO: A peripheral device is read;

- 7. READMEM: The memory is read according to the temporary register;

- 8. STOP: The machine is stopped (because of an error);

- 10. WRITEMEM: The memory is written; and

- 11. WRITEIO: A peripheral device is written.

The theorem expressing the correctness of the major state machine, though not easy to prove, did not say very much; merely that the flow of control in the major state machine was correct. There was no computation of values at the major state level – that is, additions, comparisons, shifts, and so on – so the essential correctness of Viper was not really addressed; the proof did not require any analysis of the function representing the arithmetic-logic unit, at either level.

Still less abstract than the major state model is the block level model [22], whose proof is described in this paper. At the block stage, we begin to approach the functional units and connectivity of the actual circuit, though still in a very abstract way. The block model is a collection of separate functional units (for example, the arithmetic-logic unit, the decoder, and so on) specified functionally, along with information on their inter-connectedness and timing behaviour, specified pictorially (with labelled schematic diagrams). The combination of the definitions and the pictorial information are given; the block machine's behaviour patterns must be inferred logically from what is supplied. The time scale at the block level is finer again than (but congruent with) the scale at the major state level; each major state transition is implemented by several minor state transitions. (There are mechanisms (blocks) to keep track of the major and minor states.) The block model therefore determines another graph, in which each major node consists of several minor event nodes. Before the graph is analyzed, though, it first has to be derived from the given information (see Section 6.2). (At the major state level the graph transitions were given explicitly in the definition of the major states.)

At the block level, the behaviour of the arithmetic-logic unit is analyzed, so we come closer to the essence of the microprocessor. This means that there is no single major state called 'PERFORM' corresponding to the execution of an arithmetic-logic operation (as at the major state level) but rather a collection of distinct major states for the various arithmetic-logic operations of Viper.

The original plan was to state and prove the equivalence of the high level specification and the major state model on the visible state; and then of the major state

model and the block model on the major state; and finally to make the connection by a some sort of transitivity argument. The first equivalence, as mentioned, has been proved completely, and is described in [5]. The second turned out to be awkward (for technical reasons at least). In fact, by using the methods established in the first proof, a direct comparison of the high level and the block level turns out to be straightforward, and this is what is ultimately wanted anyway. The proof has not been completed up to the equivalence (it would not have been practical with present tools and resources), but only to the point of a complete logical description (analysis) of the graph of the block level. This in itself is very valuable because it can be returned to the designers who can then decide whether the results are as predicated and hoped. Further, it reveals what would be required to complete the proof.

The major state proof is thus not necessary for the block proof, and is not used in this paper, but only mentioned in passing. The block level correctness statement, had it been proved, would have had a similar form to the correctness statement at the major state level, except that it would have had the added complication of assumptions carried along with each case. These assumptions limit the correctness of the block machine to certain normal cases in which, for example, no resetting signals come from the outside world during the time taken to process an instruction. This is discussed in Section 8.3.

#### 6 Representing the Problem

#### 6.1 The High Level

The high level or visible state of Viper

(ram,preg,areg,xreg,yreg,bflag,stop)

is represented in HOL as an object with the type

mem21\_32#word20#word32#word32#word32#bool#bool

where ram represents the memory (of 32-bit words addressed by 21-bit words); preg the program counter; areg, xreg and yreg the registers; bflag a general-purpose boolean flag; and stop the flag indicating an error requiring Viper to stop. The high level specification gives state changes for: illegal instructions (which stop the machine), no-ops, arithmetic-logic operations involving comparisons (whose the results are put in the bflag), other arithmetic-logical operations whose results go into one of the three registers, arithmetic-logical operations whose results go into

the program counter (i.e. jumps), write instructions, and procedure calls. The complete definition is supplied in the Appendix, and explanations can be found in [22]. For purposes of this paper all that is really required is the idea that a visible state (comprising the seven components) is transformed directly by the high level function into a new state upon inspection of the current instruction. The current instruction resides in the memory component of the state, ram, and is pointed to by the program counter component of the state, preg.

An example of a state transformation (which is treated at length in this paper, at the block level) is an addition ALU operation with overflow detection, whose results are placed in one of the three registers besides the program counter. In that case, the high level specifies a state in which (i) the program counter is incremented; (ii) the sum of the register source indicated and the memory source is computed and placed in the destination register indicated; and (iii) the value of the stopping flag (i.e. whether the sum overflows) is computed. We abbreviate the memory source as MEM\_ABBR(ram,preg) and the register source REGSELECT\_ABBR(areg,yreg,preg,ram)<sup>11</sup>.

Results are computed at the high level by a sub-function (called ALU'), the high level function representing the arithmetic-logic unit<sup>12</sup>. The function ALU' maps the function field, the memory selector field, the destination field, the register source, the memory source and the boolean flag to three values: a 32-bit computed value, a possible new value for the boolean flag, and a possible new value for the stopping flag. An example of an ALU non-comparison function is addition with overflow detection. In this case the ALU' function returns as the 32-bit computed value

```

ADD32(REGSELECT_ABBR(areg, xreg, yreg, preg, ram), MEM_ABBR(ram, preg))

```

where the addition function adds2 (on any two 32-bit words r and m) returns

TRIM34T032(WORD34((VAL33(SIGNEXT r)) + (VAL33(SIGNEXT m))))

Here, SIGNEXT represents sign-extension:

```

|- SIGNEXT w = WORD33(V(CONS(EL 31(BITS32 w))(BITS32 w)))

```

and TRIM34T032 simply drops the top two bits of the 34-bit sign-extended sum:

```

|- TRIM34T032 w = WORD32(V(TL(TL(BITS34 w))))

```

<sup>&</sup>lt;sup>11</sup>The memory abbreviation requires just the program counter and memory as parameters, as explained above. The register abbreviation needs in addition the four registers from amongst which it selects.

<sup>&</sup>lt;sup>12</sup>In the appendix, and the RSRE formulation, this function has no prime mark, but we add the prime here to distinguish it from the block level function which has the same general purpose but an entirely different type; it is unfortunate that the same name was originally used.

For the stopping flag, the function ALU, returns:

```

"(EL

32

(BITS34

(WORD34

((VAL33(SIGNEXT(REGSELECT_ABBR(areg,xreg,yreg,preg,ram)))) +

(VAL33(SIGNEXT(MEM_ABBR(ram,preg)))))) =

EL

31

(BITS34

(WORD34

((VAL33(SIGNEXT(REGSELECT_ABBR(areg,xreg,yreg,preg,ram)))) +

(VAL33(SIGNEXT(MEM_ABBR(ram,preg))))))))

```

This represents the overflow condition of the sum; the sum spans bits 0 to 33, and the test concerns bits 31 and 32<sup>13</sup>. When all definitions are unfolded in this example the sum of the register and memory sources works out to be:

```

WORD32

(V

(TL

(TL

(BITS34

(WORD34

((VAL33(SIGNEXT(REGSELECT_ABBR(areg,xreg,yreg,preg,ram)))) +

(VAL33(SIGNEXT(MEM_ABBR(ram,preg)))))))))))

```

That is, the sign-extended sources are added to form a 34-bit word whose top two bits are subsequently dropped. The stopping flag works out to be:

```

(EL

32

(BITS34

(WORD34

((VAL33(SIGNEXT(REGSELECT_ABBR(areg,xreg,yreg,preg,ram)))) +

(VAL33(SIGNEXT(MEM_ABBR(ram,preg)))))) =

EL

31

(BITS34

(WORD34

((VAL33(SIGNEXT(REGSELECT_ABBR(areg,xreg,yreg,preg,ram)))) +

(VAL33(SIGNEXT(REGSELECT_ABBR(areg,xreg,yreg,preg,ram)))) +

(VAL33(SIGNEXT(MEM_ABBR(ram,preg))))))))

```

(The boolean flag is not affected.) These expressions, of course, can be further unfolded according to the definition of SIGNEXT.

Another (quite straightforward) ALU operation is a procedure call. The main computed value in that case is the jump address, which is placed in the program counter:

```

WORD20(V(SEG(0,19)(BITS32(MEM_ABBR(ram,preg)))))

```

That is, the address part of the memory source is the address to which to jump. (There is no register source required for a procedure call.)

To illustrate the effect of a comparison type ALU operation on the high level state, we consider first equality test on the source and memory registers. In this case, the result of the comparison is placed in the boolean flag, and it is simply

<sup>&</sup>lt;sup>13</sup>This is a consequence of the high level definition; why the expression represents an overflow is another question.

For the less-than test (i.e. whether the value of the register source is less than the value of the memory source), the result of the comparison is

```

EL

32

(BITS34

(WORD34

((VAL33(SIGNEXT(REGSELECT_ABBR(areg,xreg,yreg,preg,ram)))) +

((VAL33(SIGNEXT(MEM_ABBR(ram,preg))) = 0) => 0 |

(VAL33(NOT33(SIGNEXT(MEM_ABBR(ram,preg))))) + 1))))

```

That is, the value of the sign-extended source is added to 0 if the value of the sign-extended memory is 0, and to the incremented value of the negated sign-extended memory value otherwise; and the thirty-second bit of that 34-bit sum is the result. (Given the equality and the less-than tests, all other desired comparisons can be constructed.)

Finally, we consider a simple non-ALU operation: an illegal-instruction stop. Various instuction schemata are not legal – for example, any one which tries to use the spare function fields 13, 14 or 15. Likewise, any one in which the program counter cannot be incremented without overflowing its twenty bits is illegal. For all such illegal instructions the new state specified at the high level will have all other registers unchanged but the stop flag set to true.

In all of these examples, the results are *logically inferred* in HOL from the definitions of the high level function and its sub-functions. This is achieved through a process of gradual unfolding of definitions in each case, using the particular case assumptions to simplify resulting expressions. Exactly the same process of unfolding is carried out at the block level, except that there the block level the representing function is not provided explicitly as at the top level, but has instead to be extracted from a partially pictorial representation before the unfolding process can be undertaken.

The examples of this section are compared to the block level results in Section 9. The first example (addition with overflow detection) is the main example of this report.

It should be stressed that the high level specification of Viper is incomplete as regards the actual Viper chip. The specification applies only to the fetch-decode-execute cycle, and ignors capabilities such as resetting, timing-out because of memory faults, pausing, single-stepping, externally forced errors, and so on – all of which are possible in the actual circuit, and all of which are represented in the block model. This means that the scope of any relation between the high level specification and the block model must be limited to the fetch-decode-execute

behaviour of Viper. Thus, because of the minimality of the high level model, any correctness property one states is bound to be rather unrealistic. It would be interesting, though beyond this report, to explore better high level specifications.

#### 6.2 The Block Level

At the block level there are ten functional units, or blocks. These are described and explained in more detail in [22], but in summary their names and general purposes are as follows:

- MEMORY\_BLOCK: Models the external memory, ram, in a simplified way;

- EXTERNAL\_BLOCK: Interfaces internal lines with the external world;

- DATAREG: Computes the data registers: the visible areg, xreg, yreg or preg (whichever is the destination), as well as three internal registers: the address (addr), instruction (inst) and temporary (treg) registers;

- TIMING\_COMB: Generates the timing (i.e. sequencing) values within each major state;

- MINOR: Keeps track of the current minor state;

- MAJOR: Keeps track of the current major state;

- TIMEOUT\_BLOCK: Provides a 64-cycle timeout facility<sup>14</sup>;

- DECODER: Generates the control values for the whole block based on the instruction code;

- FSELECT\_COMB: Extracts the function selector field from the instruction code;

- ALU\_COMB: Performs the arithmetic and logical operations to yield a 32-bit data result as well as a 9-bit word encoding the stopping conditions associated with the computation; and

- BANDSTOP\_BLOCK: Computes two boolean flags: the bflag of the visible state and a stop flag (not quite the same as in the visible state).

<sup>&</sup>lt;sup>14</sup>This is not relevant to the present analysis because of the simplified memory model used.

Each of these blocks is given a functional description in [22]; the HOL versions appear in their entirety in the Appendix. Their inter-connectedness is conveyed in Figure 1, below, which is a compendium (laid out slightly differently) of several diagrams from [22], to which the names of the internal lines count, ram, areg, xreg, yreg and preg have been added by the author. Boxes marked 'latch' or 'l' are latches, which cause a delay of one clock cycle (one time unit). These memory elements can be thought of as registers. Purely combinatorial blocks and sub-blocks (i.e. those without latches) are shown with the suffix '\_comb'. Patterns of feedback are indicated in the figure. The nine lines to or from the external world appear at the top of the figure (prefaced by 'e\_').

To save space, the *types* of the values on the lines are not shown in the diagram, but it can be assumed that they are known. For example, the type of the value on the inst line at any time is word12.

The parts of the Viper block model referred to are explained locally and partially as the need arises, but no attempt is made to present a coherent overall explanation. For that the reader must refer to [22].

#### 6.3 An Example

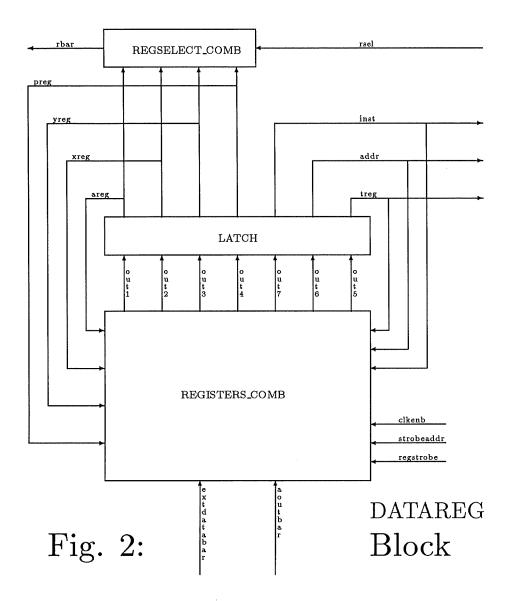

The nature of the block model and its representation in HOL can be illustrated by studying one of the blocks. We choose the DATAREG block (which can be found within Figure 1).

By way of motivation, the function of the whole dataged block is firstly to remember the four data values of the high level state: areg, xreg, yreg and preg. It is also to remember three internal values: a 32-bit temporary value called treg, a 12-bit value inst for holding the instruction code part of an instruction, and a 20-bit value addr for holding the address part of an instruction. Besides containing these seven registers, the dataged block computes new values for them. It outputs one of the four visible registers (whichever is indicated by the real line from the decoder block).

The new register values are computed on the basis of the old register values, as well as five incoming lines. The informal specification tells us the 'meanings' of these and their relations to the external lines<sup>15</sup>. The five incoming lines are:

extdatabar, a 32-bit input from the external interface which, though this is not deducible from the figure, comes from the memory block and represents incoming

<sup>&</sup>lt;sup>15</sup>This information is represented only in English prose in [22]. None of it is actually necessary for the formal proof.

data (e\_data\_in); aoutbar, the 32-bit data output of the arithmetic-logic unit; clkenb, a line from the decoder controlling when and which registers of dataged are to be loaded with new values; and finally, two boolean timing values, regstrobe and strobeaddr, from the timing block, which respectively indicate the stability of an operation, and when the address latch should be loaded.

The main sub-block of the DATAREG block is called REGISTERS (represented by REGISTERS\_COMB in Figure 1). That block is described in HOL by a function called REGISTERS which has the following HOL type: