Number 132

# Reasoning about the function and timing of integrated circuits with Prolog and temporal logic

Miriam Ellen Leeser

April 1988

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

#### © 1988 Miriam Ellen Leeser

This technical report is based on a dissertation submitted December 1987 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Queens' College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

## Reasoning about the Function and Timing of Integrated Circuits with Prolog and Temporal Logic

Miriam Ellen Leeser Queens' College Cambridge University

#### **Abstract**

The structure of circuits is specified with Prolog; their function and timing behavior is specified with interval temporal logic. These structural and behavioral specifications are used to formally verify the functionality of circuit elements as well as their timing characteristics. A circuit is verified by deriving its behavior from the behavior of its components. The derived results can be abstracted to functional descriptions with timing constraints. The functional descriptions can then be used in proofs of more complex hardware circuits.

Verification is done hierarchically, with transistors as primitive elements. Transistors are modeled as switch-level devices with delay. In order to model delay, the direction of signal flow through each transistor must be assigned. This is done automatically by a set of Prolog routines which also determine the inputs and outputs of each circuit component.

Interval temporal logic descriptions are expressed in Prolog and manipulated using PALM: Prolog Assistant for Logic Manipulation—With PALM, the user specifies rewrite rules and uses these rules to manipulate logical terms. In the case of reasoning about circuits, PALM is used to manipulate the temporal logic descriptions of the components to derive a temporal logic description of the circuit.

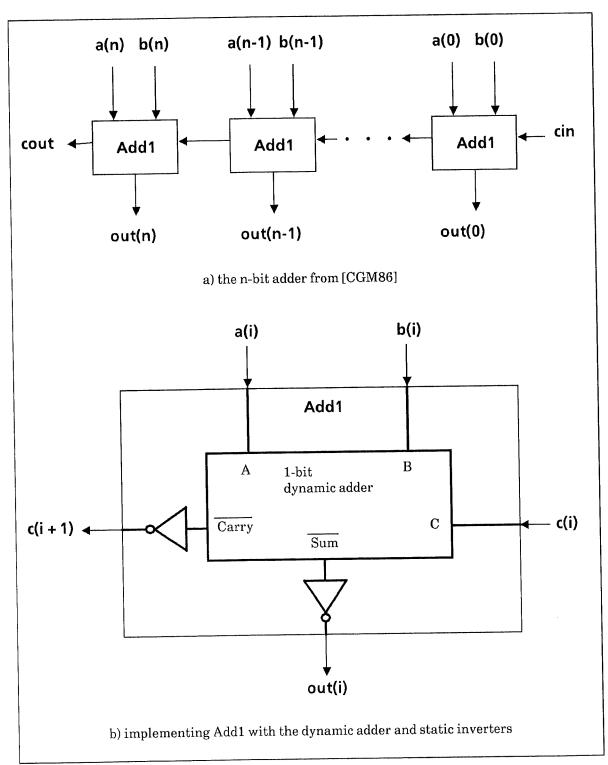

These techniques are demonstrated by applying them to several commonly used complementary metal oxide semiconductor (CMOS) structures. Examples include a fully complementary dynamic latch and a 1-bit adder. Both these circuits are implemented with transistors and exploit 2-phase clocking and charge sharing. The 1-bit adder is a sophisticated full adder implemented with a dynamic CMOS design style. The derived timing and functional behavior of the 1-bit adder is abstracted to a purely functional behavior which can be used to derive the behavior of an arbitrary n-bit adder.

## Contents

| 1 | Intr | roduction                                                  | 1 |

|---|------|------------------------------------------------------------|---|

|   | 1.1  | Motivation                                                 | 1 |

|   | 1.2  | Specifying Hardware                                        | 2 |

|   | 1.3  | Why Formal Hardware Verification?                          | 2 |

|   | 1.4  | Adding Timing Analysis to Functional Verification          | 3 |

|   | 1.5  | Synchronous CMOS Circuits                                  | 4 |

|   | 1.6  | Contributions                                              | 5 |

|   | 1.7  | Organization                                               | 5 |

| 2 | Rela | ated Work                                                  | 7 |

|   | 2.1  | Current Methods for Hardware Validation                    | 7 |

|   |      | 2.1.1 Simulation                                           | 8 |

|   |      | 2.1.2 Timing Verification                                  | 8 |

|   |      | 2.1.3 New Directions in Simulation and Timing Verification | 0 |

|   | 2.2  | Formal Hardware Verification                               | 0 |

|   |      | 2.2.1 First-Order Logic                                    | 1 |

|   |      | 2.2.2 Higher-Order Logic                                   | 2 |

|   |      | 2.2.3 Temporal Logic                                       | 4 |

|   |      | 2.2.4 Comparing Temporal Logic and Higher-Order Logic      | 7 |

|   |      | 2.2.5 Other Formalisms for Verification                    | 8 |

|   | 2.3  | Conclusions                                                | 0 |

#### CONTENTS

| 3 | Pro  | log for Circuit Specification and Manipulation                                | 21 |

|---|------|-------------------------------------------------------------------------------|----|

|   | 3.1  | Terminology                                                                   | 21 |

|   |      | 3.1.1 Specifying Circuits                                                     | 21 |

|   |      | 3.1.2 A Brief Review of Prolog                                                | 22 |

|   | 3.2  | Specifying Circuits in Prolog                                                 | 23 |

|   | 3.3  | Tools for Manipulating Prolog Circuit Specifications                          | 27 |

|   |      | 3.3.1 Automatic Determination of Signal Flow through MOS Transistors Networks | 27 |

|   |      | 3.3.2 Related Work: Prolog for Circuit Design                                 | 38 |

|   | 3.4  | Conclusions                                                                   | 39 |

| 4 | Inte | erval Temporal Logic                                                          | 40 |

|   | 4.1  | An Informal Introduction to ITL                                               | 41 |

|   | 4.2  | Formal Definitions of Some ITL operators                                      | 42 |

|   |      | 4.2.1 Syntax                                                                  | 42 |

|   |      | 4.2.2 Semantics                                                               | 43 |

|   | 4.3  | More ITL Operators                                                            | 45 |

|   | 4.4  | Extension of ITL                                                              | 46 |

|   |      | 4.4.1 Variables                                                               | 46 |

|   |      | 4.4.2 Signals                                                                 | 46 |

|   |      | 4.4.3 Operators for Signals                                                   | 47 |

|   |      | 4.4.4 Another Interpretation for Signal Strengths                             | 49 |

|   | 4.5  | Conclusions                                                                   | 50 |

| 5 | Usi  | ng ITL to Reason about the Behavior of Circuits                               | 53 |

|   | 5.1  | Hierarchical Verification                                                     | 54 |

|   | 5.2  | Modeling Combinational Elements                                               | 55 |

#### CONTENTS

|   | 5.3 | Mode                                                                 | ling Transistors                                                                                                                                                                                                               | 57                               |

|---|-----|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   |     | 5.3.1                                                                | Example 1: a CMOS Inverter                                                                                                                                                                                                     | 58                               |

|   |     | 5.3.2                                                                | Pass Transistors and Transmission Gates                                                                                                                                                                                        | 31                               |

|   | 5.4 | Mode                                                                 | ling Charge Storage                                                                                                                                                                                                            | 32                               |

|   | 5.5 | Clock                                                                | ing                                                                                                                                                                                                                            | 36                               |

|   |     | 5.5.1                                                                | Example 2: a Clocked 2-to-1 Multiplexer                                                                                                                                                                                        | 37                               |

|   | 5.6 | Concl                                                                | usions                                                                                                                                                                                                                         | 39                               |

| 6 | PA  | LM: P                                                                | rolog Assistant for Logic Manipulation 7                                                                                                                                                                                       | 70                               |

|   | 6.1 | Gener                                                                | al Purpose Features                                                                                                                                                                                                            | 70                               |

|   |     | 6.1.1                                                                | Compound Commands                                                                                                                                                                                                              | 76                               |

|   |     | 6.1.2                                                                | PALM Could be More Rigorous                                                                                                                                                                                                    | 30                               |

|   | 6.2 | Rules                                                                | for Reasoning about Circuits                                                                                                                                                                                                   | 31                               |

|   | 6.3 | Concl                                                                | ısions                                                                                                                                                                                                                         | 34                               |

| 7 | Exa | mples                                                                | 8                                                                                                                                                                                                                              | 5                                |

|   |     |                                                                      |                                                                                                                                                                                                                                |                                  |

|   | 7.1 | Exam                                                                 | ples using CMOS Complementary Logic                                                                                                                                                                                            | 35                               |

|   | 7.1 | Examp 7.1.1                                                          | Ples using CMOS Complementary Logic                                                                                                                                                                                            |                                  |

|   | 7.1 |                                                                      |                                                                                                                                                                                                                                | 37                               |

|   | 7.1 | 7.1.1                                                                | A shiftstage                                                                                                                                                                                                                   | 37<br>37                         |

|   | 7.1 | 7.1.1<br>7.1.2<br>7.1.3                                              | A shiftstage                                                                                                                                                                                                                   | 37<br>37                         |

|   |     | 7.1.1<br>7.1.2<br>7.1.3                                              | A shiftstage                                                                                                                                                                                                                   | 37<br>39                         |

|   |     | 7.1.1<br>7.1.2<br>7.1.3<br>A Dyr                                     | A shiftstage       8         A Shift Register       8         A Dynamic Latch       8         amic CMOS Full Adder       9                                                                                                     | 37<br>39<br>92                   |

|   |     | 7.1.1<br>7.1.2<br>7.1.3<br>A Dyr.<br>7.2.1                           | A shiftstage       8         A Shift Register       8         A Dynamic Latch       8         amic CMOS Full Adder       9         Operation of the Dynamic Adder       9                                                      | 37<br>37<br>39<br>92<br>94       |

|   |     | 7.1.1<br>7.1.2<br>7.1.3<br>A Dyr.<br>7.2.1<br>7.2.2                  | A shiftstage       8         A Shift Register       8         A Dynamic Latch       8         amic CMOS Full Adder       9         Operation of the Dynamic Adder       9         Setting the Direction of Signal Flow       9 | 37<br>39<br>92<br>94             |

|   |     | 7.1.1<br>7.1.2<br>7.1.3<br>A Dyr.<br>7.2.1<br>7.2.2<br>7.2.3         | A shiftstage                                                                                                                                                                                                                   | 37<br>39<br>92<br>94<br>97       |

|   |     | 7.1.1<br>7.1.2<br>7.1.3<br>A Dyr<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4 | A shiftstage                                                                                                                                                                                                                   | 37<br>39<br>92<br>94<br>97<br>95 |

#### CONTENTS

| 8  | Con            | Conclusions 1                             |             |  |

|----|----------------|-------------------------------------------|-------------|--|

|    | 8.1            | Issues and Improvements                   | 115         |  |

|    | 8.2            | Computer Aided Design with Formal Methods | 117         |  |

|    | 8.3            | Final Thoughts                            | 119         |  |

| A  | PAI            | LM Rules                                  | <b>120</b>  |  |

|    | A.1            | Basic Logic Rules                         | 121         |  |

|    | A.2            | Signal Rules                              | 122         |  |

|    | A.3            | ITL Rules                                 | 122         |  |

|    | <b>A.4</b>     | Circuit Rules                             | 122         |  |

| В  | $\mathbf{The}$ | Dynamic Latch Derivation                  | <b>24</b>   |  |

|    | B.1            | The Static Inverter                       | 125         |  |

|    | B.2            | The Clocked 2-to-1 Multiplexer            | <b>128</b>  |  |

|    | B.3            | The Inverting Multiplexer                 | 130         |  |

|    | B.4            | The Shiftstage                            | 135         |  |

|    | <b>B.5</b>     | The Dynamic Latch                         | 138         |  |

| Bi | bliog          | raphy                                     | L <b>47</b> |  |

## List of Figures

| 3.1 | The Component halfadd                            | 24         |

|-----|--------------------------------------------------|------------|

| 3.2 | The Component nand                               | 26         |

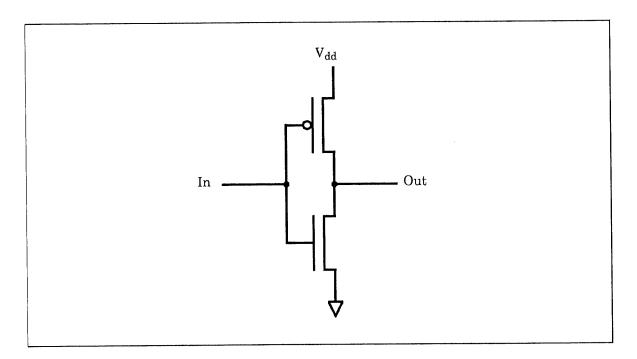

| 3.3 | A CMOS inverter                                  | 28         |

| 3.4 | Transistor Labelings                             | <b>3</b> 0 |

| 3.5 | A Static Register                                | 33         |

| 3.6 | A Full Adder                                     | 35         |

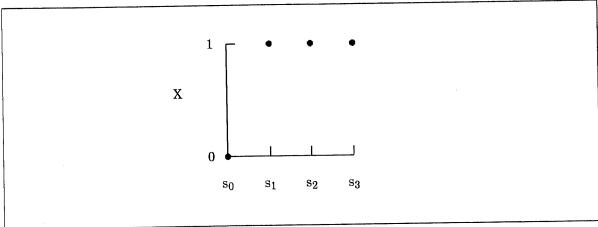

| 4.1 | A Rising Bit Signal                              | 41         |

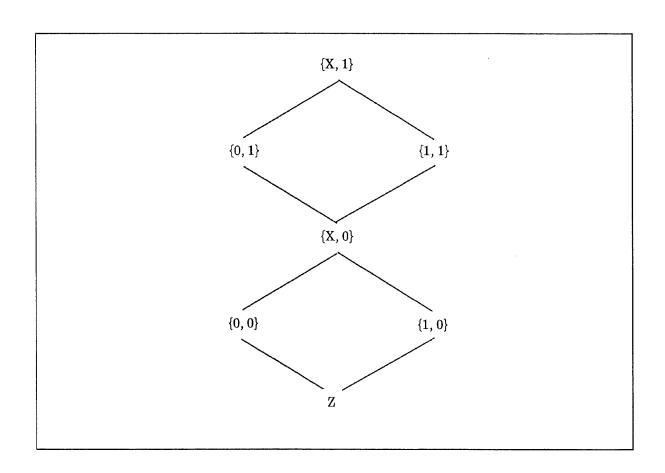

| 4.2 | The Lattice Model for Signals                    | 51         |

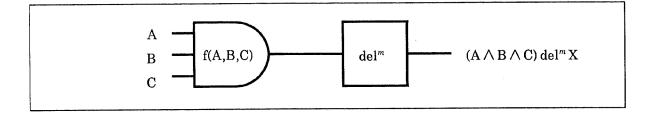

| 5.1 | Model of a 3-Input and Gate with Delay           | 56         |

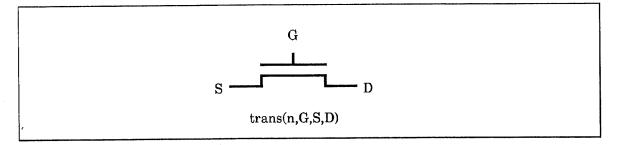

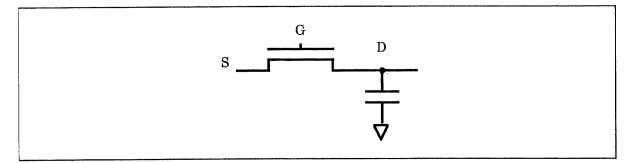

| 5.2 | An <i>n</i> -type Transistor                     | 58         |

| 5.3 | A CMOS Inverter                                  | 59         |

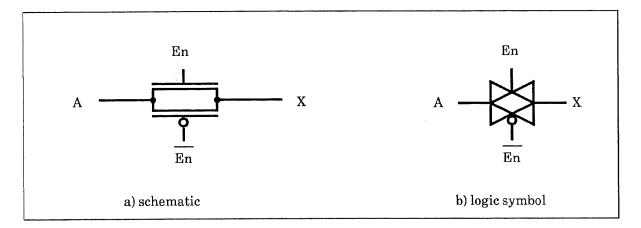

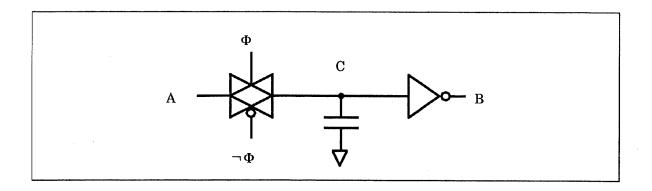

| 5.4 | A CMOS Transmission Gate                         | 62         |

| 5.5 | A CMOS Shift Register with Explicit Capacitances | 63         |

| 5.6 | A Pass Transistor with Explicit Capacitance      | 64         |

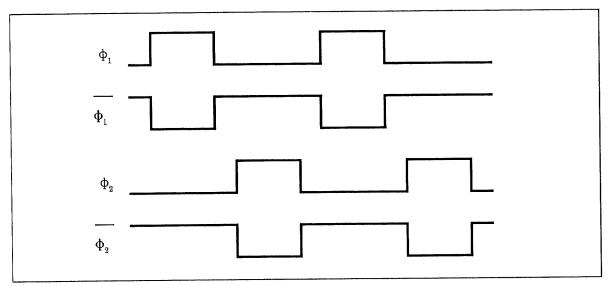

| 5.7 | 2-Phase Non-overlapping Clocks                   | 66         |

| 5.8 | A CMOS Clocked 2-to-1 Multiplexer                | 67         |

| 6.1 | PALM Commands                                    | 71         |

#### LIST OF FIGURES

| 6.Z  | Rules for the Equals Operator = '                     | 14             |

|------|-------------------------------------------------------|----------------|

| 6.3  | Some Definitions                                      | 75             |

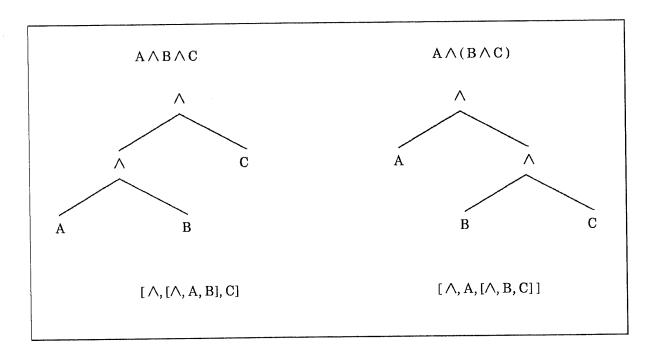

| 6.4  | Trees which Represent the Rule assoc-andl             | 76             |

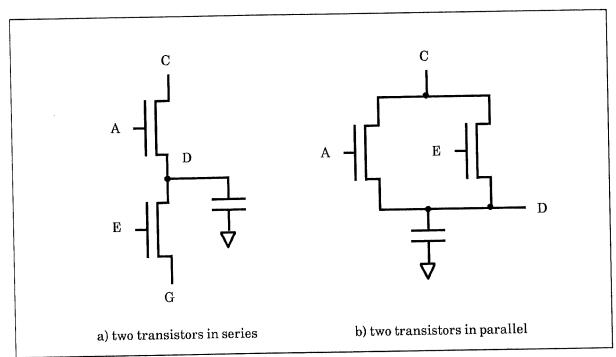

| 6.5  | Transistor Configurations                             | 32             |

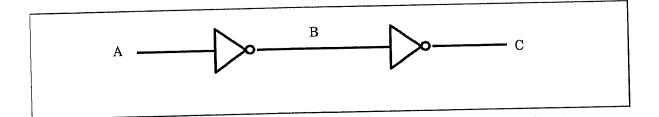

| 6.6  | Two Inverters in Series                               | 33             |

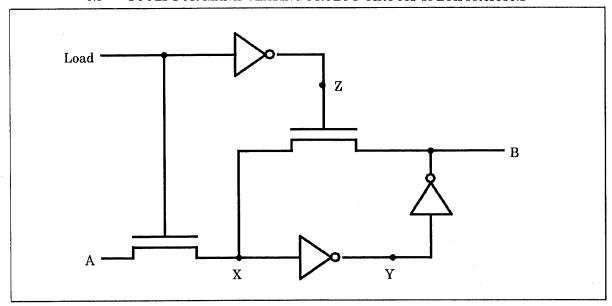

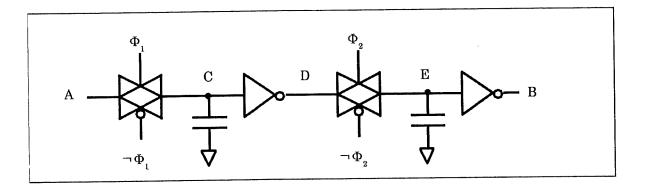

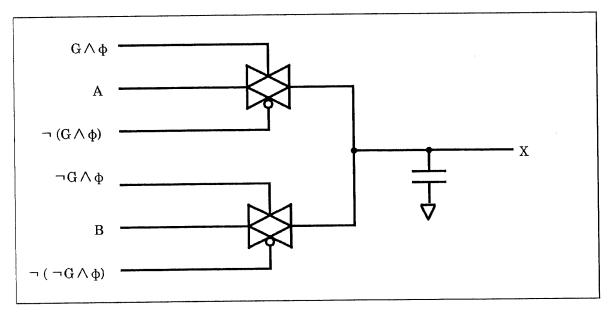

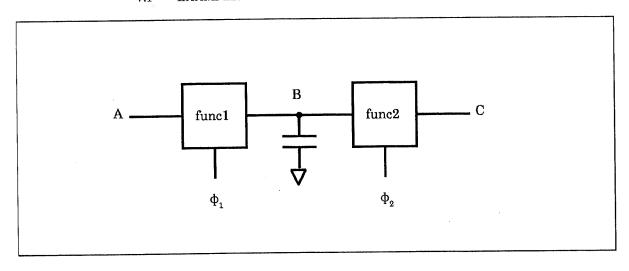

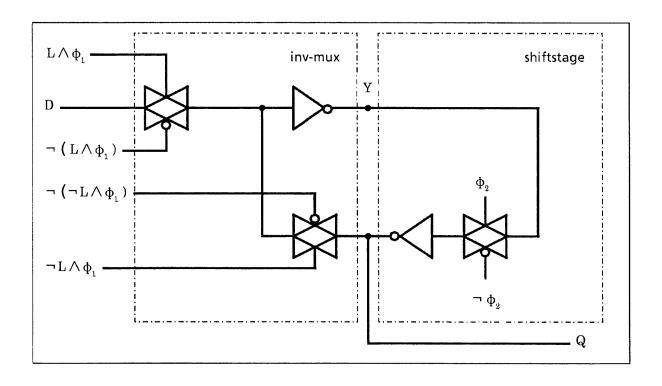

| 7.1  | An Element which Employs 2-phase Clocking             | 36             |

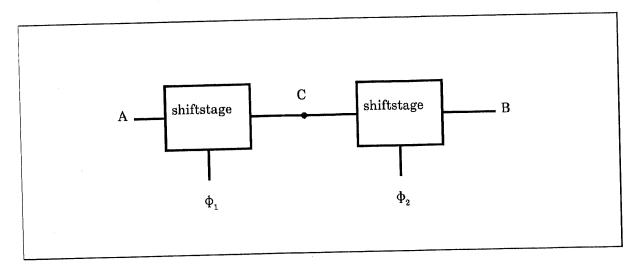

| 7.2  | A shiftstage                                          | 37             |

| 7.3  | A Shift Register                                      | 38             |

| 7.4  | A CMOS Dynamic Latch                                  | <b>)</b> 1     |

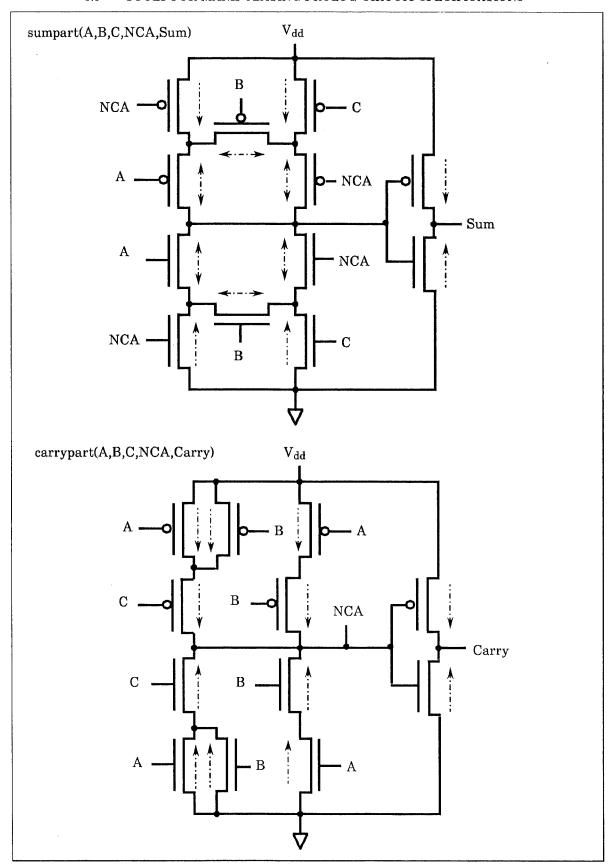

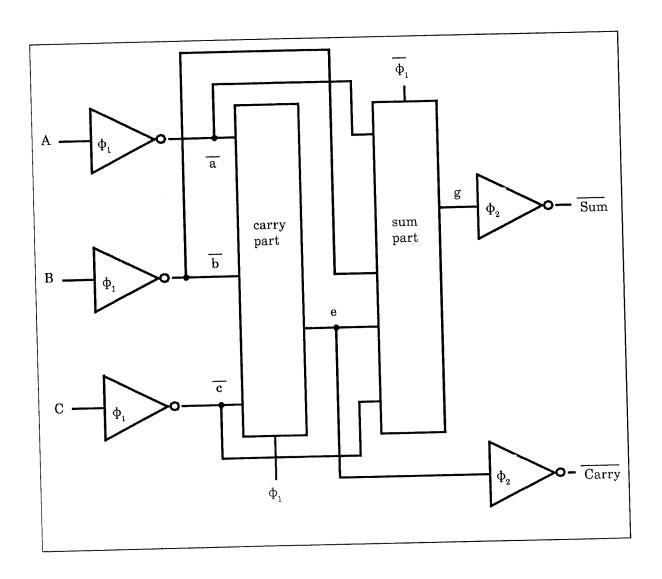

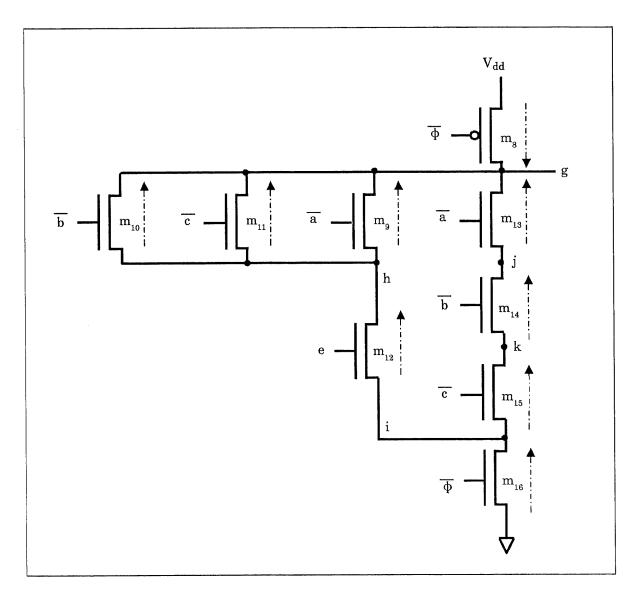

| 7.5  | A Dynamic 1-bit Adder                                 | <b>)</b> 3     |

| 7.6  | A C <sup>2</sup> MOS Inverter                         | <b>)</b> 4     |

| 7.7  | Dynamic CMOS Logic                                    | <b>)</b> 5     |

| 7.8  | One Cycle of Operation of the Dynamic Adder           | <del>)</del> 6 |

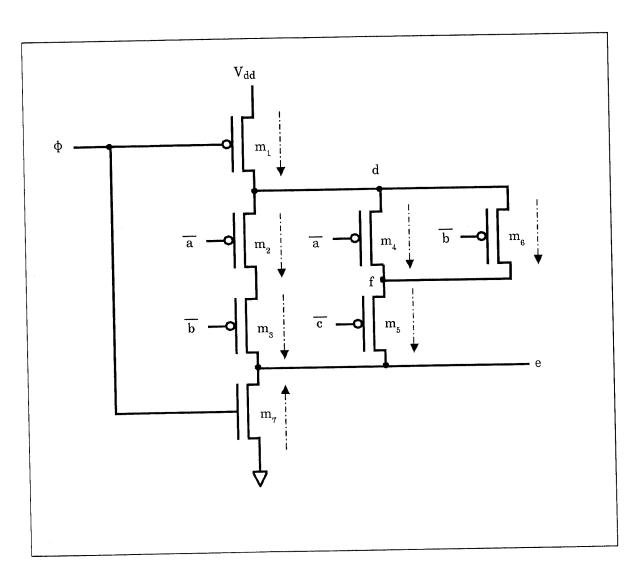

| 7.9  | The carrypart with Direction of Signal Flow Indicated | )1             |

| 7.10 | The sumpart with Direction of Signal Flow Indicated   | )4             |

| 7.11 | An n-bit Dynamic Adder                                | LΟ             |

## List of Tables

| 3.1 | Performance Results of Signal Flow with Different Backtracking Algorithms | 37  |

|-----|---------------------------------------------------------------------------|-----|

| 4.1 | Extended ITL Operators                                                    | 52  |

| 7.1 | Performance Results for the One Bit Dynamic Adder                         | 112 |

### Introduction

#### 1.1 Motivation

The increasing complexity of integrated circuits has generated interest in new methods for the computer aided design of these circuits. One such method is formal hardware verification — using techniques based on mathematical logic to formally prove that a circuit correctly implements its behavioral specification. This technique is applicable at many different levels of implementation and specification. For example, it can be proved that a correctly connected group of combinational gates implements an adder; that an adder, registers, and control logic implement an arithmetic logic unit (ALU); and that an ALU, memory busses, registers, microprogram section, and control logic correctly implement a central processing unit. Research has been done into behavioral verification at these levels. Investigations have also been done into relating the various levels with abstraction, and into formally describing the relative timing of signals. Recent research, however, has not concentrated on implementation details of concern to real designers. These details include the implementation of logic gates with transistors, and the timing considerations due to delays through these transistors. My research addresses the issues of formal verification applied to this low level of the design hierarchy: relating transistor level implementations of circuits to their functional specification, and formally deriving the timing behavior of these circuits.

#### 1.2 Specifying Hardware

I am interested in specifying and verifying hardware at the level of implementations of cells in a complementary metal oxide semiconductor (CMOS) design library. These cells are then used as building blocks when constructing larger integrated circuit designs.

Typically, the behavior of such cells is specified informally in English, their implementation given by a layout, and their timing specified with equations and timing diagrams. I describe their behavior and timing using interval temporal logic (ITL) and their implementation using Prolog.

I assume that hardware is described modularly and hierarchically. A chip is made up of a series of functional blocks which in turn are made up of functional blocks, and so forth, until the transistor level description is reached. Each level need not contain circuit elements all of the same type. For example, adders and transistors may be mixed at the same level of description.

This hierarchy does not imply that a designer is constrained to use a top-down refinement design style. Design is usually a combination of top-down refinement and bottom-up composition. No matter how the design is attacked, the design can be described in a hierarchy of design levels, and each adjacent pair of levels can be related formally.

#### 1.3 Why Formal Hardware Verification?

Formal hardware verification has several advantages over conventional methods such as simulation for verifying circuits. With formal verification, signals are manipulated symbolically. By proving that an implementation meets its specification, the designer is sure that it has that behavior for all cases; in simulation the designer can only be sure of the behavior for the cases tested. Another advantage of verification is the ability to exploit modularity. A functional block such as an adder need only be proved once no matter how many times it is used in the circuit. In addition, a portion of the design can be proved to meet its specification before the rest of the design is complete. Thus errors can be caught early in the design process. Modularity also allows small changes to a design to be

#### 1.4 ADDING TIMING ANALYSIS TO FUNCTIONAL VERIFICATION

handled easily since only those portions of the design which have been altered need to be reverified.

These advantages do not imply that formal verification will replace simulation. Formal verification can be viewed as another tool in the designer's tool box which gives added confidence in the correctness of designs. A drawback of verification is that one can never have complete confidence in the specification. It is useful to simulate a specification to check that it exhibits the required behavior.

A circuit is verified by showing that its behavior can be derived from the mathematical models of the behavior of the components which make it up. If the mathematical model does not capture a physical reality of the circuit, that physical reality will not be captured in the proof. For example, a proof system whose primitives are combinational elements without delay cannot derive delay characteristics of a circuit. Similarly, if charge-sharing is not modeled, charge-sharing bugs will not be detected. In these cases other tools such as timing analyzers and design rule checkers are required.

#### 1.4 Adding Timing Analysis to Functional Verification

Existing tools for timing analysis do not use formal techniques. The advantage of using formal methods for timing is that they allow timing models to be related to the higher level behavioral models of circuit elements using abstraction. The same descriptions of circuit implementations can be used to do timing as well as other analysis, and different levels of description can be related formally. The designer, therefore, has increased confidence that various aspects of the design are correct, since different tools are all working on the same representation of the design.

I derive low level timing details such as delay and set-up and hold times from interval temporal logic (ITL) [Mos83] descriptions of circuit components. The timing analysis is done in conjunction with behavioral verification since delay, for example, depends on the function of the circuit as well as the timing characteristic of its components.

#### 1.5 SYNCHRONOUS CMOS CIRCUITS

In addition, I express constraints on the behavior of inputs and outputs of a circuit component in interval temporal logic. These constraints, which express such conditions as when the inputs must be stable, are verified using the same formal techniques. They are verified when the component is composed with other components to form a larger functional block.

#### 1.5 Synchronous CMOS Circuits

The techniques for reasoning about circuits presented in this thesis can be applied to a wide range of technologies and design styles. My examples are restricted to synchronous Complementary Metal Oxide Semiconductor (CMOS) circuits [WE85]. I chose this class of circuits for several reasons. CMOS has become an important commercial technology. MOS lends itself to switch-level analysis. In many CMOS designs, the ratios of transistor sizes is not important as it is in nMOS. (This is not the case with such designs as RAM cells; I do not consider these.) Synchronous circuits lend themselves to a hierarchical, systematic design style, and avoid many of the problems which are associated with asynchrony. In addition, it is easier to reason about synchronous systems formally, and to formulate timing constraints.

I do not consider, in detail, the design and timing issues which arise from layout. Layout is an important aspect of VLSI design, and a significant proportion of delay in CMOS circuits is due to interconnect. The methods for deriving the timing behavior of a circuit can be extended to model circuits whose delay characteristics are derived from information extracted from the layout. A wire can be modeled as a simple case of a combinational element with delay.

The circuits discussed are synchronous CMOS circuits where all feedback loops are broken by clocks and there are no reconvergent branches in combinational logic. There are many practical VLSI designs which fall into this class of circuits. Within this framework I consider several different CMOS design styles, including full complementary CMOS and dynamic CMOS.

#### 1.6 Contributions

The main contributions of this thesis are:

- Automatically deriving characteristics of a circuit from the schematic. These characteristics include direction of signal flow through transistors and direction of ports of components. The direction of a port may be in, out, or bidirectional.

- Extending ITL to model capacitive effects which arise in MOS circuits. One such capacitive effect is charge storage on an undriven node.

- Using extended ITL to reason formally about the timing properties of circuits at the

transistor level. The behavior of a transistor is modeled in ITL as a switch with an

associated delay. These delays are used to derive the length of the different cycles

in clocked circuits.

- Expressing and reasoning about constraints in ITL. Constraints include set-up and hold times, and constraints on when a signal must be stable.

#### 1.7 Organization

In the next chapter, I present related work in hardware validation. I discuss languages and systems for specifying and verifying circuit behavior. I present both informal and formal approaches, and emphasize methods which model timing behavior.

Chapter 3 demonstrates how to specify circuit schematics in Prolog, as well as presenting tools for manipulating these Prolog specifications. These tools use the structure of the circuit to derive characteristics such as which ports are inputs and which are outputs. These characteristics are then used when proving other properties of the circuit.

Chapter 4 gives an introduction to interval temporal logic (ITL). Chapter 5 describes how ITL descriptions are used in verifying function and timing of circuits as well as reasoning about circuit constraints. In Chapter 6, I describe my Prolog system for rewriting logic equations, and show how this system is used for manipulating ITL equations.

#### 1.7 ORGANIZATION

In Chapter 7, I present several examples including a complementary CMOS dynamic latch and a 1-bit adder. Both these circuits are implemented with transistors and exploit 2-phase clocking and charge sharing. The 1-bit adder is a sophisticated full adder implemented with a dynamic CMOS design style. I use ITL and the system presented in Chapter 6 to derive the function and timing behavior of these circuits and to reason about constraints. In addition I derive constraints on the duration of the different clocking phases. I also show how the function of the 1-bit adder can be abstracted, and how the abstract behavior can be used in a proof of an n-bit adder.

Finally I present conclusions. I summarize the salient aspects of my approach, discuss issues and improvements, and consider how my approach could be incorporated into a computer aided design system for VLSI.

### Related Work

In this chapter, I present languages and systems which have been developed to aid designers in specifying and verifying their hardware designs. The emphasis is on tools which give designers information about the timing behavior of their circuits. First the current tools available for design validation are presented. These include simulators and timing verifiers. These tools have several drawbacks in that they do not exploit hierarchy and only validate behavior for specified inputs. Recent advances in these informal methods attempt to redress these drawbacks.

Formal verification methods for hardware overcome the drawbacks of simulation. In addition, they provide a means to formally relate the different levels of detail at which a circuit is described, and allow for incremental, hierarchical validation. Thus, a designer has more confidence that the design being validated is the same as that being fabricated. I discuss several representations and systems for formally reasoning about hardware. Here I emphasize systems which use higher-order logic or temporal logic to reason about circuits, and compare the advantages and disadvantages of these two formalisms.

#### 2.1 Current Methods for Hardware Validation

Two widely used methods for validating a design are simulation and timing verification. In simulation, a designer validates the behavior of a design by specifying the inputs and checking that the resulting outputs exhibit the desired behavior. In MOS timing verification, the timing of a circuit is derived by assuming that all transistors are conducting and then calculating the path with the longest delay through the circuit. These techniques usually operate on circuit descriptions which are flat rather than hierarchical. One

#### 2.1 CURRENT METHODS FOR HARDWARE VALIDATION

advantage of these approaches is that they are widely used. As a result of being used with real designs, circuit models tend to be accurate and algorithms used are efficiently implemented.

#### 2.1.1 Simulation

Most simulators used to verify VLSI circuits are either switch-level or mixed-mode. With switch-level simulation [Bry81], large networks of transistors are modeled as nodes connected by switches which have an associated conductance strength. Logic states on nodes are represented by signals which are modeled as values and strengths. A circuit is simulated by applying inputs specified by the designer to a model of the circuit and calculating the resulting outputs. When a steady state is reached, the result is reported and a new set of inputs is driven through the circuit. Every transition in the simulation takes one unit of time. This use of timing makes computation easier, but bears little relation to the time a circuit actually requires to settle. In addition, simulation only models the behavior of the circuit for the inputs specified. In general, the number of input combinations required to fully simulate a circuit is exponential in the number of inputs. Thus, simulating a circuit completely is often impractical, even for simple circuits.

Mixed-mode simulators are capable of simulating circuits which are described at several different levels of detail. A commonly used mixed-mode simulator is MOTIS [AB\*80], [CL\*84], which simulates circuits described at the transistor level, logic gate level and functional level. MOTIS also handles several different timing models including unit delay, multiple delay and low level timing. With a multiple delay model, different delays are used for different circuit components and for propagating rising and falling pulses. With a low level timing model, voltages are treated as continuous and time is modeled as a sequence of discrete time steps. Mixed-mode simulators exploit some hierarchy in the description of circuits, but still require the user to provide inputs and interpret the outputs.

#### 2.1.2 Timing Verification

Two widely used MOS timing verifiers are TV [Jou83] and Crystal [Ous83]. These timing verifiers are similar to switch-level simulators in that they operate on a transistor level

#### 2.1 CURRENT METHODS FOR HARDWARE VALIDATION

description of the circuit and model transistors as ideal switches. The difference is that simulators simulate the behavior of a circuit for a given set of inputs, while timing verification is independent of input values. The object of timing verification is to identify the slowest paths through a circuit and to determine the maximum possible clock speed. First the direction of signal flow through each transistor is determined; then the delays through paths in the circuit are calculated assuming that all transistors are conducting. Direction of signal flow is determined either automatically or from hints from the designer. TV and Crystal differ in the way paths are traced through a network and in the way delays are calculated. TV uses breadth-first search to exhaustively search the entire circuit, and separately calculates minimum and maximum propagation delays. Crystal uses a depth-first search algorithm and provides an average propagation delay. Both handle different phases of clock cycles by specifying that different clocks cannot be active at the same time.

These timing verifiers report the slowest or n slowest paths to the user. A problem with timing verification is that it is frequently difficult for the user to identify how to improve the behavior of these slowest paths. Since the circuit structure is flat, timing verifiers do not recognize bottlenecks that affect several paths. Such bottlenecks would be more obvious from a hierarchical circuit structure. In addition, if several parallel paths exhibit the same timing behavior, they will all be reported. Another problem is that the entire circuit must be re-analyzed if a portion of the design is modified to improve the timing behavior. Jouppi [Jou87] presents an interactive timing assistant (IA) to help alleviate some of these problems. IA proposes design changes and provides incremental timing analysis.

A further drawback of timing verification is the separation of timing from function. The slowest paths predicted may never arise in practice. These paths would not be detected if timing and function were considered together. In addition, certain errors cannot be identified. For example, the relation between signals on different clock phases is not checked. Thus, timing problems which arise because signals do not behave according to certain timing constraints are not identified. In order to find these, some form of verification which incorporates timing and functional verification must also be done.

#### 2.1.3 New Directions in Simulation and Timing Verification

New systems for design validation address some of the shortcomings discussed above. The most common changes are allowing symbolic inputs to simulators, and exploiting hierarchy in design validation.

MOSSYM [Bry85] is an extension of Bryant's switch-level simulator which allows the user to specify inputs symbolically as well as with boolean variables. An advantage of this approach is that the user can choose between conventional simulation, symbolic simulation or a hybrid. A disadvantage is that the user has to interpret the outputs.

Lin and Mead [LM86] present a hierarchical timing simulator. This approach is used to model synchronous circuits similar to those presented in this thesis. They assume that input and output ports of components have been determined before simulation begins, and assume that an input may only change once in a given clock period. These assumptions are not checked. Functional and timing behavior is validated. This involves simulating a component, and then replacing that component with its derived behavior. The behavior can be derived analytically as well as through simulation. One drawback is that design validation must be bottom up. In other words, a designer cannot specify a component at a high level, later give a more detailed representation, and show that these two representations are equivalent.

#### 2.2 Formal Hardware Verification

In the previous section I presented some commonly used design validation techniques and discussed their advantages and disadvantages. I also presented some new techniques which redress some of these disadvantages.

In this section I describe formal methods for design verification. These methods address many of the disadvantages mentioned above. Hierarchical design is supported, and different levels of description can be formally related. Localized changes to the circuit require that only the altered components be re-verified. Inputs and outputs are represented symbolically rather than by values. Assumptions about designs can be expressed formally and

verified along with verification of behavior. The major drawback of these systems is that they have not been widely used to verify real designs. As a result, the models of circuit behavior are not as well developed. In addition, some of these approaches have not been mechanized, which limits their acceptance by designers.

Since I am interested in the timing as well as the functional behavior of circuits, I discuss the way time is modeled. Specifically, I present formal methods which use higher-order logic and those which use temporal logic, and I discuss the relative merits of these two approaches. I also present other formalisms for specifying and verifying hardware, especially those which represent time or deal with low level details of circuit operation. First, I discuss two systems which use first-order logic.

#### 2.2.1 First-Order Logic

Several approaches to formal hardware verification have been based on first-order logic. The approaches presented in this section, [Bar84], [Hun86], automate hardware verification and have been used to verify complex hardware designs. Drawbacks in the use of first-order logic include difficulty in expressing timing in a detailed manner, and difficulty in expressing abstraction between different levels of description. Systems which use higher-order logic do not experience these difficulties. Two such systems are presented in the next section.

#### Verify

Verify [Bar84] is a Prolog system which attempts to automatically prove that the behavior of the implementation of a digital system is equivalent to the specification. Verify uses Prolog as a hardware description language. The behavior of a component is specified as a finite state machine with next state and output equations. There is an implicit clock; at each clock tick the state variables and outputs are updated. Timing at a more realistic level is not considered. With Verify, circuits can be described and verified down to the transistor level. The transistor model employed is a simple unidirectional, switch-level model. Different levels of description can be related in a limited manner, but abstraction functions cannot be defined by the user.

#### Boyer-Moore Theorem Prover

Hunt [Hun86] uses the Boyer-Moore theorem prover to prove correct a 16-bit microprogrammed microprocessor implemented at the register-transfer level. The behavior of combinational circuits is described by recursively defined functions. Sequential circuits are modeled using self-recursive functions which have an explicit clock argument. These functions call themselves recursively once each clock tick. Thus time is discrete and behavior at any given level is related to the representation of a single clock. The theorem prover is mechanical; its operation is guided by heuristics. Since the logic used is first-order and there are no quantifiers, Hunt has difficulty formally relating clocks at different levels of description of the microprocessor. He overcomes this difficulty by using oracles: functions which guess the exact number of time steps a low level representation needs to execute to be equivalent to the next higher level specification. Such oracles cannot be represented in first-order logic. If higher-order logic is used as the specification language, abstraction between levels can be expressed directly, and such oracles are not required.

#### 2.2.2 Higher-Order Logic

Higher-order logic provides several advantages over first-order logic, including a more direct way of expressing abstraction and a more elegant way of representing time with signals modeled as functions from time to values. I describe two important systems which employ higher-order logic to reason about hardware.

#### HOL

The HOL (Higher-Order Logic) system was developed by Mike Gordon for specifying and verifying hardware [Gor85b]. HOL is being used by many people at Cambridge University as well as elsewhere [CGM86]. Several large examples from real designs are being verified, including the VIPER microprocessor [Coh87]. My work has been influenced by the approach taken by HOL. A hardware component is described in HOL with a logical formula, components are composed by anding them together, and internal connections are hidden using existential quantification. Verification proceeds by showing that a structure correctly implements a specification. This involves expanding the structure by the

behavioral description of its parts, and deriving a description of behavior which implies the specified behavior. The HOL system mechanizes some aspects of the verification of circuits.

A major difference between my approach and the HOL approach is the way time is modeled. In temporal logic, time is implicit in the logical operators. In higher-order logic, time is usually represented by an explicit time variable. For example, the behavior of an inverter with input In and output Out and delay m is expressed in HOL by:

$$invert(In, Out, m) \equiv_{def} \forall t.Out(t+m) = \neg In(t)$$

The same inverter, described in ITL, has the behavior:

$$invert(In, Out, m) \equiv_{def} \Box len \ m \supset (\neg In \rightarrow Out)$$

Note that in HOL, the signals In and Out are functions from time to values.

Herbert [Her86] uses HOL to verify the timing and function of digital circuits. Primitive components are gates with propagation delay such as the inverter described in HOL above. The proofs proceed by verifying the function and timing of a circuit using these timing level models, and then abstracting to a synchronous level model which expresses function only, subject to constraints on the timing behavior of the signals. The synchronous behavior of the inverter in HOL is:

$$invert(In, Out) \equiv_{def} \forall t.Out(t) = \neg In(t)$$

The constraints are that In and Out are stable around t. Herbert uses this approach to derive the timing constraints on the inputs and outputs of a d-type flipflop built up from nor gates. Since the primitive components of his proofs are logic gates, Herbert doesn't consider the special requirements of verifying the timing of transistor level descriptions of circuits.

Dhingra [Dhi87] uses HOL to formally describe and verify the rules for combining components with the CLIC design style, a successor of the NORA design style [GDM83]. This work complements that done in my derivations since the components of the adder presented in Section 7.2 fit into the framework of the CLIC design style. Dhingra formally

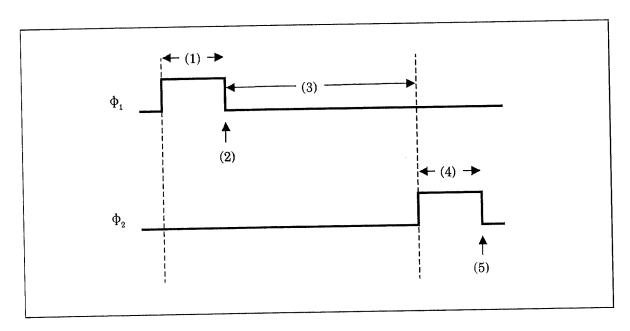

proves that well-defined inputs will produce well-defined outputs provided that components are connected according to the rules of the design style. He does not however model low level timing details of circuits. For example, his transistor models do not have delay. He introduces time into his descriptions by describing two-phase non-overlapping clocks where each phase has duration of unit length, and assumes the duration is long enough for correct circuit operation. This is a coarser level of detail than that which I use.

#### **VERITAS**

Hanna and Daeche also use higher-order logic to specify and reason about circuits [HD86a]. Their theory of time includes formalizations of time instants, durations and intervals, where an interval starts at a time instant and has a specified duration. As in HOL, time is explicitly part of the behavioral specification, and signals are functions from time to values. In [HD86b], a d-type flipflop similar to that presented by Herbert is verified, and similar timing constraints are formally derived.

#### 2.2.3 Temporal Logic

Temporal logic has been used for specifying software, hardware and communications protocols. One of the earliest papers on using temporal logic for hardware [Boc82] describes specifying and manually verifying an implementation of a self-timed arbiter. In this example, temporal logic is used to specify the sequence rather than the relative timing of events. In the following, I discuss examples of temporal logic applied to circuit design in cases where the relative timing of events is modeled or where the verification technique has been automated.

#### ITL and Tempura

Moszkowski uses ITL to specify and reason about digital circuits [Mos83]. Since my work was motivated by his, the circuit descriptions are similar. A major difference is that the primitive components he uses to describe the behavior of larger components are delayless combinational elements and memory elements, while mine are MOS transistors

with delay. Moszkowski presents a definition of pass transistor behavior, but does not model its detailed timing behavior and does not show how this description can be used in larger MOS circuits. Also, Moszkowski does not reason about different signal strengths in ITL. Another difference is the way constraints are handled. Moszkowski includes such constraints as set-up and hold times as part of the behavioral definition. His descriptions generally have one clock signal, so he does not relate the behavior of different clocks.

Tempura is an executable programming language based on a subset of ITL [Mos86]. The Tempura interpreter simulates this subset by finding values for the Tempura variables which result in the temporal logic formulas being valid. Moszkowski shows how this approach can be used to simulate ITL descriptions of circuits. Such simulation is useful for checking that the specification does in fact describe the desired behavior of the device. Modifying Tempura to handle my extensions to ITL, described in Section 4.4, would provide a useful tool for simulating my ITL specifications.

#### CTL and SML

A propositional temporal logic called CTL (Computation Tree Logic) has been used to specify the behavior of asynchronous and sequential circuits [BCDM86], [DC86]. The behavior of a circuit is specified in CTL and compared with the expected behavior of a gate level representation of the circuit. EMC (Extended Model Checker) checks the CTL specification against a finite state graph which represents the behavior of the gate level description of the circuit. In the case of asynchronous circuits, this finite state graph is generated by a preprocessor which combines flow-table models of the behavior of gates to form the state graph of the circuit being verified. No quantitative timing parameters are used; gates are assumed to have arbitrary delay. In the case of sequential circuits, there are two techniques for generating state graphs from the circuit. The first is to simulate the circuit using a mixed gate and switch-level simulator similar to MOSSIM [Bry81]. The simulator uses a unit delay model for all elements. The second is to compile the state graph from a hardware description language representation of the circuit. The language SML (State Machine Language) was developed for this purpose. These SML descriptions can also be used to generate different regular hardware structures such as PLAs, PALs or ROMs.

The main advantage of this approach is that it is mechanized. A major disadvantage is that the finite state graph which is generated is not hierarchical so its size grows rapidly as the complexity of the circuit grows. In addition, temporal logic is used only to specify the sequence of events. Thus the delay models used do not realistically capture the timing behavior of the circuits modeled.

#### LTTL and Tokio

LTTL (Linear Time Temporal Logic) is used to specify hardware at the register-transfer level and above [FTM83]. As with CTL, the examples presented use temporal logic to reason about the functional and sequential behavior rather than the low level timing behavior of circuits. Temporal logic assertions are made about a circuit, and these assertions are checked against a Prolog description of the operation of the circuit. This verification proceeds by expanding both the temporal logic and the Prolog description into behaviors of the current state and the next state; and then comparing these descriptions. Verification is done automatically. In addition, the logic programming language Tokio [FKTM86] executes LTTL specifications. The result is a simulation of a specification similar to that provided by Tempura. However, the underlying model of execution for Tokio is logic programming. Advantages and disadvantages of this work are similar to those for CTL. This approach has the additional benefits of exploiting hierarchy in circuit design and providing a tool to simulate the temporal logic specification. Disadvantages include the fact that low level timing considerations are not modeled.

#### ETL

Fusaoka et al. [FST84] use ETL (Extended Temporal Logic) to describe and reason about VLSI circuits. ETL, first presented by Wolper [Wol82], extends propositional temporal logic with operators for regular expressions. VLSI circuits are modeled down to the transistor level. The transistor model is unidirectional and specifies how the drain voltage behaves as a function of the source voltage when the gate signal rises or falls. Low level timing details modeled include the different delays associated with a rising pulse and a falling pulse being propagated through an inverter. A temporal logic description of the

behavior of a circuit is derived by composing temporal logic descriptions of the behaviors of the components. The behavior of a circuit is validated by verifying that the specification of the input signals anded with the temporal logic description of the circuit implies a specification of the output signals. Note that the user must specify the inputs and outputs, so the result resembles simulation more than formal verification.

As an example, a dynamic latch circuit similar to that discussed in Section 7.1.3 is presented [FST84]. Their circuit uses only one clock and charge storage is not modeled. The latch is modeled as having unit delay, and low level timing details of the components are suppressed. In addition, the specification of the input signals is not related to the state of the clock signal, even though the specified behavior is only true if a clock signal begins at the correct time. Some timing information about the output is derived in this example, but it is not very detailed and is also not related to the behavior of the clock.

#### 2.2.4 Comparing Temporal Logic and Higher-Order Logic

Temporal logic and higher-order logic are formalisms which have been used to specify and verify hardware. Each formalism has certain advantages and disadvantages. In temporal logic there are no explicit time variables; time is implicitly part of the temporal operators. As a result, the specifications of behaviors are more succinct. In addition, there is no need to express such information as an order over time variables. In higher-order logic descriptions, time variables are explicit and signals are functions from time to values. Behavior specifications are frequently more complex. The advantage of higher-order logic is that it is not necessary to have special proof rules to deal with the temporal logic operators, so the proof system may be less complex.

Temporal logics can be embedded in higher-order logic. Gordon and Hale [GH87] have shown how ITL can be embedded in HOL. There are several advantages in doing this, including the ability to mix a temporal logic description of behavior with explicit time representations. In [Sub86a], timing behaviors are described by such a mixture of temporal and higher-order logic formalisms.

#### 2.2.5 Other Formalisms for Verification

I discuss a few other systems for formally reasoning about systems. Specifically, I discuss systems which model low level characteristics of hardware. Such low level considerations include timing of combinational elements, geometric layout, and transistor level modeling.

#### Circal

Milne uses Circal to specify the structure and behavior of circuits [Mil86a]. Structure can be specified hierarchically. A component is specified by a name and a set of ports. Circal supports parallel composition of components and hiding of ports. When components are composed, similarly labeled ports are joined. Behavior is described by sequences of events on ports. The behavior of each component is specified as a finite state machine. Time may either be expressed implicitly or explicitly. If time is explicit, then the time variable must have a port at each device. In this case, input and output events may only occur when a time tick or time event occurs. Different grains of time may be modeled and these can be formally related. Specifications of behavior in Circal tend to be lengthy. For example, the behavior of a wire with an explicit representation of time and a one unit time delay requires four lines of description. Verification of device behavior proceeds by specifying the behavior of a device at an abstract level, specifying the behavior of the components of the device at a lower level, and proving that the two are equivalent.

#### $\mu FP$

$\mu$ FP [She86], [She83] is a VLSI design language based on the functional programming language FP which captures both behavioral and geometric information about a circuit. The circuits described are regular array circuits whose behavior is either combinational or can be defined by a finite state machine. The  $\mu$  operator introduces memory into the functional descriptions of circuits. Circuit behavior is described by functions from streams of inputs to streams of outputs. Circuits are manipulated hierarchically. A behavioral description of a circuit is transformed by applying algebraic laws. The resulting layout is therefore correct by construction.  $\mu$ FP successfully combines reasoning about the function

and low level implementation details. However, the class of circuits which can be modeled is restricted since only synchronous circuits can be described. In addition, the model of time used is discrete, and all clock signals must be related to the same underlying clock. Thus, low level timing considerations are not expressed.

#### A Compositional Model of MOS Circuits

Winskel describes a compositional model for MOS circuits [Win87a]. This formal model is based on Bryant's lattice of voltage values which have different resistive and capacitive strengths. Circuit behaviors are modeled as static configurations where a static configuration is the set of steady states a circuit can adopt. A static configuration is characterized by voltage values and strengths, internal voltage sources and signal flow information. These static configurations place constraints on the way ports can interact with the environment. Two circuits can be composed if the ports which are connected in the process impose consistent constraints on the environment. In [Win87b], Winskel shows how his model can be formally related to Gordon's switch-level model which does not take into account resistive and capacitive signal strengths.

Winskel does not deal with time explicitly. Time may be introduced by viewing it as a sequence of static configurations where each static configuration has an associated time variable. The assumption is made that all input signal durations and clock periods are sufficiently long for the circuit to settle into a steady state before the environment changes.

#### Silica Pithecus

Silica Pithecus is a system for verifying the digital behavior of synchronous systems [Wei86]. Weise is mainly concerned with verifying low level aspects of the behavior of nMOS circuits. Verification proceeds by calculating the analog behavior of a circuit implementation, abstracting that behavior to the digital level, and comparing the result to the specification provided by the user. The system uses a bidirectional transistor model, and models resistive and capacitive strengths. Signals are functions from time to voltages and strengths. The system can detect charge sharing bugs, ratio bugs, threshold drops,

#### 2.3 CONCLUSIONS

and races and hazards. It does not handle capacitive coupling and general feedback in circuits. Timing verification is also not handled. The assumption is made that a circuit settles into a steady state before the inputs change. This system reasons about constraints on the behavior of signals in a manner similar to that which I use.

#### 2.3 Conclusions

In this chapter, I have discussed informal and formal methods for reasoning about circuits. By using formal methods to validate a hardware design, several advantages are gained over informal methods. These advantages include the ability to control the complexity of verification through hierarchical analysis, and the ability to formally relate the different levels of description. With experience and further research, formal methods may also gain the advantages currently exhibited by informal methods: maturity and widespread acceptance.

My research differs from previous work in the level of hardware designs verified. I specify and verify function and timing of circuits built from MOS transistors modeled at a detailed level. This research complements much of the work described above.

In the rest of this thesis I describe how Prolog and ITL can be used to specify and formally verify the timing and functional behavior of CMOS circuits. In the next chapter, I describe how to specify circuits using Prolog, and how the specifications can be used to derive characteristics of these circuits. I then go on to describe how these specifications are used in formally reasoning about circuit behavior.

## Prolog for Circuit Specification and Manipulation

Circuits can be specified, simulated and reasoned about using logic programming. In this chapter I describe the use of the logic programming language Prolog to represent the structure of circuits. These Prolog descriptions directly reflect the structure and hierarchy of a circuit as shown in a circuit schematic. Furthermore, important characteristics of circuits can be automatically derived from these specifications.

First I define some terminology and give a brief review of Prolog. Next I describe the specification method and present an example. I then describe tools I have written for manipulating these circuit descriptions. These tools include programs for automatically deriving the direction of signal flow through transistor networks and deriving port directions from the schematic. Finally I discuss related research into Prolog tools for hardware design.

#### 3.1 Terminology

#### 3.1.1 Specifying Circuits

A circuit is composed of a set of components. Components can be composed hierarchically, where components are specified in terms of constituent components. At the bottom of the hierarchy are primitive components. I describe CMOS circuits; the primitive components are n-type and p-type transistors and power and ground sources. There are no strict rules about the levels of hierarchy. One component may be made up of primitive as well as non-primitive components.

#### 3.1 TERMINOLOGY

Each component has ports for external connections. A port may be an input, an output, or bidirectional. A node is a junction of ports. Nodes which are external to a component are formed by connecting one of the ports of that component to one or more ports of other components. Nodes which are internal to a component are formed by connections of the ports of the constituents of that component.

#### 3.1.2 A Brief Review of Prolog

Logic programming is based on the Predicate Calculus. An introduction to Prolog (PRO-gramming in LOGic), a widely used logic programming language, is given in [CM84]. In this section I present some key concepts and terminology, especially those used to specify and manipulate circuits. I use Edinburgh Prolog syntax.

In Prolog, terms are constant symbols, variables or compound terms. Constant symbols are either integers, or written with an initial lower case letter, or a string of non-alphanumeric symbols. Variables are written with an initial upper case letter. An n-ary compound term is written as  $f(t_1, ..., t_n)$  where f is a constant symbol called the functor, and each  $t_i$   $(1 \le i \le n)$  is a term called an argument.

A list is another commonly used compound term with special Prolog syntax. A list of length 0 is written []. A list of length n is written  $[t_1, \ldots, t_n]$ .  $t_1$  is called the head of the list, and  $t_2, \ldots, t_n$  are elements of a list called the tail. The list having head h and tail l can also be written [h|l].

Formulas are written as Horn clauses, a subset of the formulas of Predicate Calculus. The Horn clause:

$$P:-Q_1,Q_2,\ldots,Q_a$$

is equivalent to the Predicate Calculus formula:

$$\forall x_1, \ldots, x_m (\exists y_1, \ldots, y_n Q_1 \land Q_2 \land \ldots \land Q_q) \supset P$$

where P and the  $Q_i$   $(1 \le i \le q)$  stand for compound terms, the  $x_j$   $(1 \le j \le m)$  are variables appearing in P and possibly in the  $Q_i$ , and the  $y_k$   $(1 \le k \le n)$  stand for variables appearing in the  $Q_i$  and not in P. P is the head of the Horn clause, the  $Q_i$  are the body. A clause with no body is called a unit clause.

#### 3.2 SPECIFYING CIRCUITS IN PROLOG

Clauses are used as a program to which questions (or goals) can be posed. The strategy used by Prolog for the execution of goals combines a simple backtracking strategy together with a pattern matching algorithm known as unification. Two terms are matched according to the unification algorithm if there is a most general substitution for the variables in the terms such that the terms may be made equal. In logic programming, unification is a general purpose feature used for passing input and output parameters and for incremental construction of data structures. When using Prolog as a hardware description language, unification is used for propagating signal values through a circuit.

#### 3.2 Specifying Circuits in Prolog

Clocksin [Clo87] presents and compares three different methods of specifying circuits in Prolog. These are the functional method, the extensional method and the definitional method. I give brief descriptions of the first two methods, and describe in more detail the method which I employ: the definitional method.

#### The Functional Method

In this method, a functional representation of circuits is used. An output of a component is described by a function applied to arguments which are the inputs to the component. These arguments may in turn be functions. For example, the component halfadd shown in Figure 3.1 is described as:

$$xor(A, B)$$

.

$not(nand(A, B))$ .

This method has two disadvantages. First, only acyclic circuits can be specified. This excludes many practical circuits. Second, a separate expression must be used to represent each output of a circuit. In addition, functional specifications quickly become very complex, even for simple circuits.

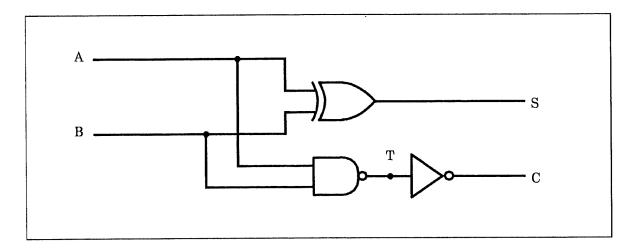

Figure 3.1: The Component halfadd

#### The Extensional Method

The extensional method represents each component and connection with a separate clause. Prolog constants are used to name connections. For example, the halfadd in Figure 3.1 component can be described using the relations component and connect. The arguments of component are the name of the component, a list of inputs and a list of outputs. The binary predicate connect describes connections between ports:

```

component(xor,[a, b],[c]).

component(nand,[a, b],[c]).

component(not,[a, b]).

connect(a,xor(a)).

connect(b,xor(b)).

connect(a,nand(a)).

connect(b,nand(b)).

connect(nand(c),not(a)).

connect(xor(c), s).

connect(not(b), c).

```

#### 3.2 SPECIFYING CIRCUITS IN PROLOG

This method does not have the same drawbacks as the functional method. However, disadvantages arise since modules are not represented as a single term. It is therefore difficult to do certain kinds of circuit manipulations. In addition, hiding internal lines is cumbersome so expressing modularity is not straightforward.

#### The Definitional Method

In this method, a circuit is represented as a set of Horn clauses. A component with n ports is represented as a predicate of arity n whose head represents the component being defined. The body of the predicate is a composition of the constituent components which define the component. Constituents are composed with the comma connective. The order of the components in the body is not important. The ': -' connective of Prolog is reinterpreted to mean 'is defined by'. A node is represented by a unique, like-named variable. A node which is named by a variable not appearing in the head of the clause is an internal node.

The component halfadd depicted in Figure 3.1 is specified as:

$$halfadd(A, B, S, C) := xor(A, B, S), nand(A, B, T), invert(T, C).$$

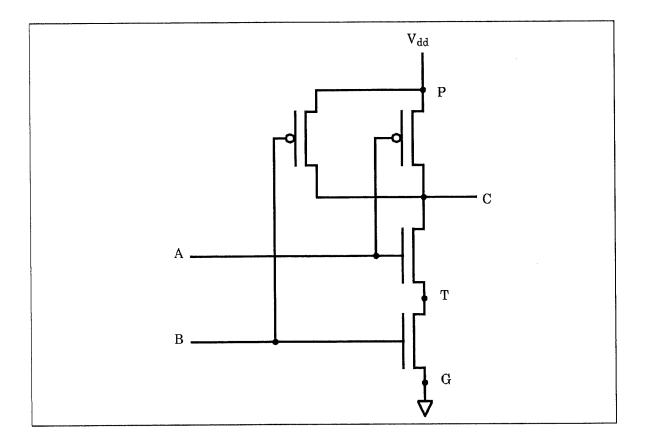

The variable T defines the 'hidden' node between the output of the nand gate and the input of the inverter. Figure 3.2 shows the definition of the nand gate in terms of primitive elements. A transistor is specified as trans(X, G, A, B) where X specifies the type of transistor (either n or p); G is the gate and A and B are the channel nodes (source and drain). Component nand is specified as:

$$\mathsf{nand}(A,B,C): - \mathsf{pwr}(P).\mathsf{trans}(p,B,P,C).\mathsf{trans}(p,A,P,C). \\ \mathsf{trans}(n,A,C,T).\mathsf{trans}(n,B,T,G).\mathsf{gnd}(G).$$

Note that the ports of these components do not have directions specified.

Figure 3.2: The Component nand

#### Advantages of the Definitional Method

Specifying circuits in this manner has several advantages. The descriptions directly reflect the structure and hierarchy of a circuit as shown in a schematic, and are therefore easy to write. These descriptions also lend themselves to easy modular specification for several reasons. The component name is explicitly part of the specification. Internal connections are named by variables which do not appear in the head of the clause and are effectively hidden. In addition, the definition of ports of components is inherently non-directional. This is important for specifying components, such as pass transistors and transmission gates, which have bidirectional ports.

Another advantage is that the specifications can be manipulated or directly executed by Prolog systems. Clocksin [Clo87] describes how Prolog specifications of circuits can be directly executed. In the next section I describe other tools for manipulating these specifications.

# 3.3 Tools for Manipulating Prolog Circuit Specifications

I have written several Prolog procedures for manipulating descriptions of MOS circuits. These tools analyze the circuits hierarchically. Examples of such tools include code to automatically determine the direction of signal flow and the direction of ports of components in hierarchically specified MOS circuits. In the next subsection I describe this code. Then, I describe work others have done in developing Prolog tools for circuit design.

Other procedures I have written identify all the components directly connected to a given node in a circuit and identify all the primitive components directly connected to a given node. I have also written routines to extract circuit components from a network of circuit elements. These tools are used with the techniques described in this thesis; their implementation is not described further.

# 3.3.1 Automatic Determination of Signal Flow through MOS Transistors Networks

Determining the signal flow through transistors is often a necessary precursor for further circuit analysis. For example, both Crystal [Ous83] and TV [Jou83] require flow analysis before they can proceed with timing analysis. Many formal methods for circuit verification [Bar84] and design simplification [Clo87] depend on signal flow being specified in advance. Some design verification methods do not require preliminary flow analysis, but proofs are easier to compute if the results of flow analysis are available [Gor85a]. One way to provide signal flow information is to manually specify the input and output roles of components' ports. Some systems [Bar84],[Ous83] rely on manual specifications entirely. However, automatic signal flow determination can reduce the designer's workload, particularly for the case of MOS transistors, which, due to the symmetry of source and drain nodes, are capable of conducting in different directions at different times. TV [Jou83] automatically determines signal flow in nMOS transistor networks free of bidirectional transistors and specification errors. TV uses nine rules to determine the direction of transistors. In addition to the general Kirchoff current law, TV uses information about the types of circuits used in the design methodology.

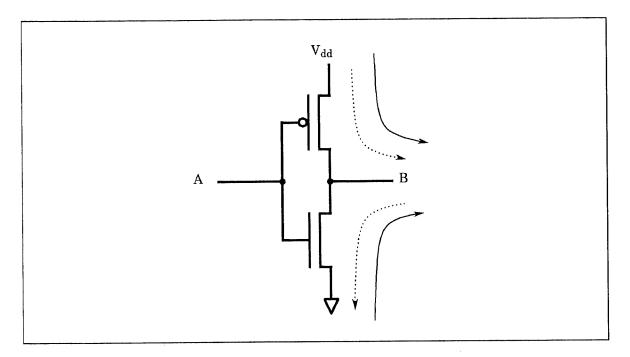

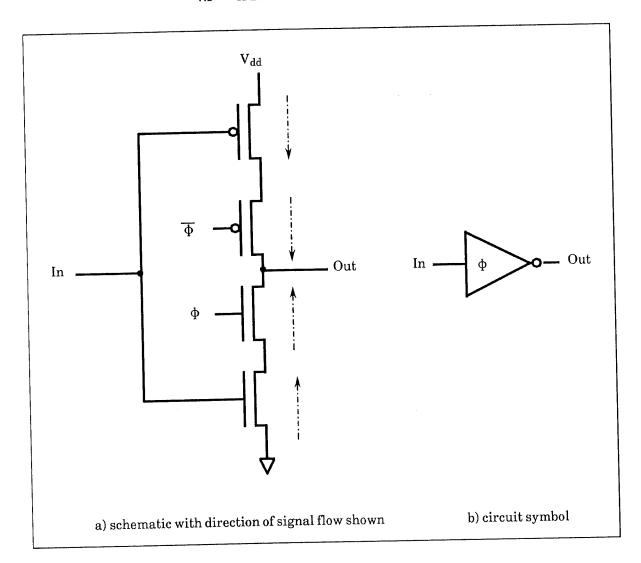

Figure 3.3: A CMOS inverter

The method described in this section was originally presented in [CL86]. It is intended for hierarchically specified MOS transistor networks that contain bidirectional transistors, and where there is no information about any particular design methodology. The method is data independent; it does not use knowledge of the values of inputs to a circuit. The analysis is static; it is only dependent on the circuit topology. In essence, we are determining the flow of information through a network assuming all transistors are turned on. Although it is unlikely that this configuration will occur in practice, we are able to determine those transistors whose direction will always remain the same. Transistors which can support signal flow in either direction are labeled bidirectional. Clearly we label some transistors bidirectional which, due to the inputs provided, will only propagate signals in one direction in practice. However, the algorithm is guaranteed to correctly find all bidirectional transistors, and will not incorrectly label any unidirectional transistor. This procedure will be able to determine the direction of a large percentage of transistors in most circuits. It will not provide much useful information about a design that relies heavily on bidirectional transistors; however, such designs are unusual.

Signal flow may be viewed as the propagation of logic levels, either high or low, through a network. Power and ground connections are viewed as sources of signal flow. Inputs to a component and outputs from a component are sources and sinks of signal flow, respectively. Note the difference between signal flow and the more traditional view of current flow where power acts as a source of current flow and ground acts as a sink. For example, consider the CMOS inverter in Fig 3.3. The dotted arrows show the direction of current flow through the transistors; the solid arrows show the direction of signal flow. Using the definition of signal flow we can derive the input node and output node of the inverter. This will be shown later.

#### The Method

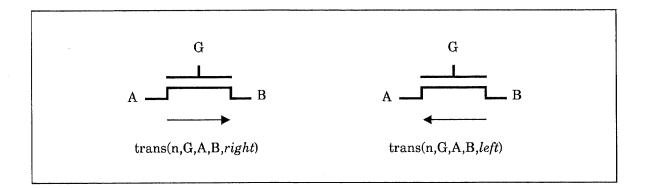

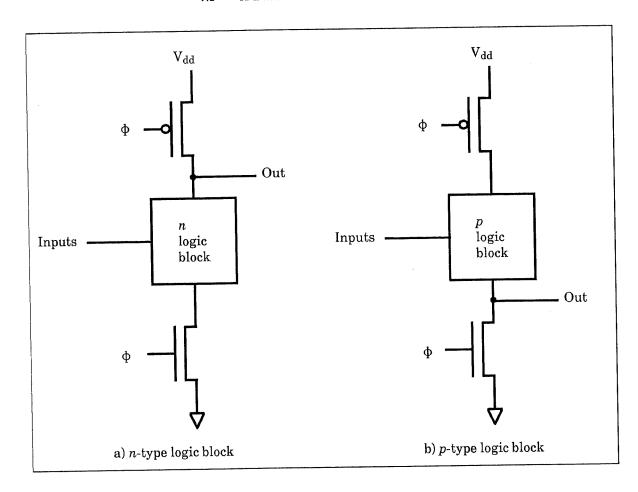

The input to the direction finder is a circuit specification. Primitive components are ptype and n-type transistors and power and ground supplies. Ports of components may be sinks or sources of signal flow or both. The task of determining the direction of signal flow can be viewed as a consistent labeling problem [Mak77]. To solve the problem, it is necessary to associate with each transistor a label drawn from the set {right, left}. Refer to Figure 3.4. If the two non-gate terminals of a transistor are arbitrarily named A and B, the label right is assigned to a transistor for which terminal A is a sink of signal flow and terminal B is a source of signal flow. The label left is assigned to a transistor for which terminal A is a source of signal flow and terminal B is a sink of signal flow. For a circuit consisting of m transistors, the number of unconstrained labelings is  $2^m$ . The problem is to assign labels to transistors such that a constraint is met: each node of a circuit must be connected to at least one sink and at least one source of signal flow. Moreover, if a node is directly connected to power or ground, then at most one source of signal flow (the power or ground itself) is allowed. This constraint is called the Signal Law. The Signal Law is a consequence of Kirchoff's current law. For a circuit containing bidirectional transistors, multiple solutions to the consistent labeling problem are admitted. In other words, there may be more than one possible labeling of a circuit that satisfies the Signal Law. A bidirectional transistor will be labeled right in one solution and left in another.

The direction of ports (whether they are used as inputs or outputs) is an additional constraint on the solution. With this method there is a choice of whether to attempt to derive the direction of ports automatically (at the risk of obtaining a weak solution) or to use a specified direction of ports to constrain the search for labelings of transistors.

Figure 3.4: Transistor Labelings

#### Implementation

The method is implemented in Prolog, using depth-first search through the hierarchical circuit specification to exhaustively enumerate the directions of transistors. The method compounds the direction finding of transistors with establishing the direction of ports of non-primitive components. Unlike previous approaches [Jou83], the whole circuit is not flattened into a set of primitive components. First, the outermost component is decomposed into its constituents, then the direction of the ports of each of these components is established, and finally it is confirmed that the hidden nodes of the circuits obey the Signal Law. If a component is not primitive then the direction of its ports is established recursively.