Number 108

# Workstation design for distributed computing

Andrew John Wilkes

June 1987

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 http://www.cl.cam.ac.uk/

### © 1987 Andrew John Wilkes

This technical report is based on a dissertation submitted June 1984 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Wolfson College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

#### Preface

I would like to thank all my colleagues for their enthusiasm, encouragement, and for many stimulating discussions; David Singer, Jon Gibbons, Steve Crawley, Dan Craft and Kathy Carter deserve particular mention. Tony King designed and built the hardware that is described herein with great skill—there would be little to report upon without his efforts. Jim Mitchell provided much useful advice during the project's early stages. Neil Wiseman and Roger Needham have been continually supportive, and I have benefited much from the stimulating environment provided by the Computer Laboratory.

The Hewlett-Packard Company kindly provided me with the time and resources to revise this dissertation. I would particularly like to thank Steve Boettner for his support. Jon Gibbons gave freely of his expertise (and evenings) in the process of producing the illustrations.

Above all, I would like to thank Marjan Burggraaff for her continual good humour, tolerance and assistance during the course of writing this thesis.

This dissertation is not substantially the same as any that I have submitted for a degree or diploma or other qualification at any other University. I further state that no part of it has already been or is being concurrently submitted for any such degree, diploma or other qualification.

Except where specific reference is made in the text to the work of others, this dissertation is entirely my own work and includes nothing which is the outcome of work done in collaboration.

Copyright © 1984 Andrew John Wilkes. All rights reserved.

### Contents

| 1 | Introduct                                            | ion                                                                                                                                                                                                    |                          |

|---|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|   | 1.1<br>1.2                                           | The Domain schema                                                                                                                                                                                      | . 1                      |

| 2 | Execution                                            | domains                                                                                                                                                                                                | . 4                      |

|   | 2.1<br>2.2<br>2.3<br>2.4<br>2.5                      | Non-networked systems Local area network systems The personal computer approach The Cambridge Distributed System Execution domains—summary                                                             | 5<br>7<br>11             |

| 3 | Storage d                                            | lomains                                                                                                                                                                                                | 17                       |

|   | 3.1<br>3.2                                           | Files                                                                                                                                                                                                  | 19<br>22                 |

| 4 | Entities .                                           |                                                                                                                                                                                                        | 23                       |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8 | Concepts and definitions Storage objects Active entities and concurrency control Keeping entities consistent Putting entities into perspective Protection by projection Coercions Related work Summary |                          |

| 5 | Terminal                                             | domains                                                                                                                                                                                                | 45                       |

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5                      | Display technology  Variable intensity techniques  Image representation techniques  Host: image-representation coupling  Conclusion                                                                    | 49<br>51<br>61           |

| 6 | Terminal                                             | domain software                                                                                                                                                                                        | 69                       |

|   | 6.1<br>6.2<br>6.3<br>6.4<br>6.5                      | Physically distributed terminal domains Terminal independence Screen management Input tool handling Existing terminal domains for LAN systems Summary                                                  | 71<br>77<br>83<br>89     |

| 7 | The Rain                                             | bow Workstation                                                                                                                                                                                        | 95                       |

|   | 7.1<br>7.2<br>7.3                                    | Goals                                                                                                                                                                                                  |                          |

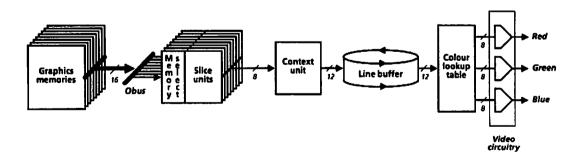

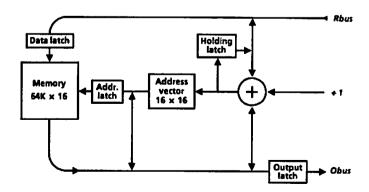

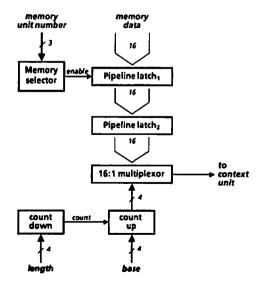

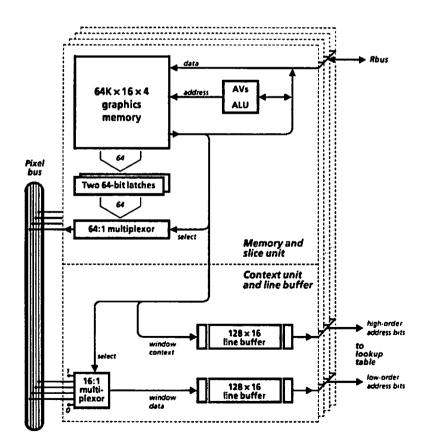

| 8 | The Rain                                             | bow Display video pipeline                                                                                                                                                                             | 103                      |

|   | 8.1<br>8.2<br>8.3<br>8.4                             | The graphics memories The slice units The context unit The line buffers                                                                                                                                | 104<br>107<br>110<br>111 |

|    | 8.5<br>8.6                           | The lookup table                                                                                                     | 113<br>114                      |

|----|--------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 9  | Non-video                            | display hardware                                                                                                     | 115                             |

|    | 9.1<br>9.2<br>9.3<br>9.4<br>9.5      | Bus structure                                                                                                        | 115<br>116<br>126<br>129<br>131 |

| 10 | Software                             | for the Rainbow Workstation                                                                                          | 132                             |

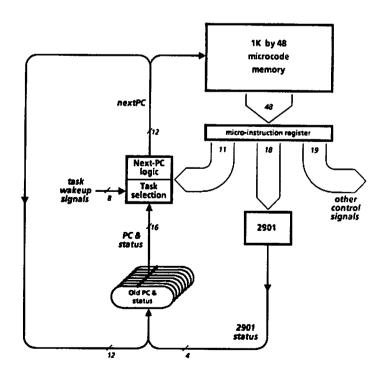

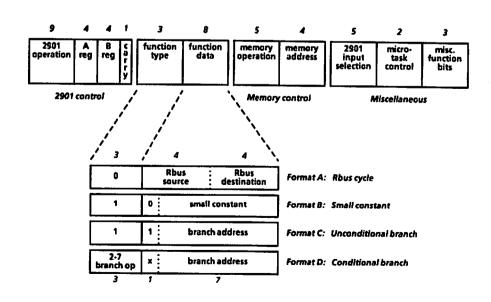

|    | 10.1<br>10.2<br>10.3<br>10.4<br>10.5 | The Programming Environment Microcode for the 2901 Microcode support Image manipulation software Input tool handling | 132<br>134<br>141<br>145<br>148 |

| 11 | Evaluatio                            | n                                                                                                                    | 151                             |

|    | 11.1<br>11.2<br>11.3<br>11.4         | Project goals Hardware Scalability Software                                                                          | 151<br>152<br>156<br>161        |

| 12 | Conclusion                           | on                                                                                                                   | 163                             |

| Ap | pendix I.                            | Bibliography                                                                                                         | 164                             |

### 1. Introduction

This thesis discusses some aspects of the design of computer systems for local area networks (LANs), with particular emphasis on the way such systems present themselves to their users. Too little attention to this issue frequently results in computing environments that cannot be extended gracefully to accommodate new hardware or software and do not present consistent, uniform interfaces to either their human users or their programmatic clients. Before computer systems can become truly ubiquitous tools, these problems of extensibility and accessibility must be solved. The work described here has concentrated on one possible approach, which has emphasised support for program development on LAN-based systems.

### 1.1 The Domain schema

To provide a framework for much of the discussion which follows, I shall make use of the concept of domains. A domain is defined here as a region in which reside a set of resources and their manager, which is responsible for their allocation and control. Seen from outside, the domain is itself a resource with a single uniform interface—that of its manager. In this context a resource is something whose use is subjected to an allocation policy; processors, disc space, virtual memory and screen space are all examples of resources. Various types of domains can be identified: execution domains provide the physical memory and processing capability necessary for the execution of a task or process; storage domains are responsible for the maintenance of long term state information, and contain, allocate and manage resources such as disc space; terminal domains provide connection paths to end users that may be interactive (e.g. terminals and graphics screens) or not (e.g. line printers and card readers). A domain behaves like an instance of a module or an abstract data type; it needs initialising when it is created and finalising when it is terminated, and it implements a protected abstract data type with a limited number of operations. (The internal implementation details of a domain cannot always remain entirely hidden; for example, note needs to be taken of the machine architecture and virtual machine environment provided by an execution domain.)

$<sup>^{1}</sup>$  I shall reserve the term user exclusively for referring to humans, and use the term client to indicate a software or hardware entity.

consisting of a domain containing a minicomputer with its own local disc storage.

The lifetime of a domain may exceed that of the domain or system of which it is a part. Consider the case of a timesharing system which is a component of a distributed operating system based on a local area network. When the LAN is taken down for engineering work, the timesharing system may still continue to function for its own locally attached terminals. Conversely, a domain may outlive some of its components. This is one of the reasons for replicating parts of systems in an attempt to increase the reliability of the whole.

The domain model will be used to characterise existing systems, both centralised and distributed, in order to compare the mechanisms they use for resource control. As a framework, it can help to extract the architecture of a resource management scheme from its implementation details. Note that it is an expositive, rather than prescriptive, model: it aims to provide a basis for discussion rather than suggest a particular implementation.

It is interesting to note the work described in [Liskov82], in which constructs called guardians are added to an extended version of CLU. A guardian can be thought of as an abstraction of a node containing one or more processors or other resources: as such, it is an almost exact analogue of a domain manager. Guardians are but one of many possible realisations of the domain scheme, and so their semantics are necessarily more restrictive than those of the general model discussed here.

### 1.2 Thesis organisation

This thesis is divided into three parts. The first is a short review of existing execution resource allocation schemes that looks at a range of systems from single processors to loosely coupled multiprocessor networks, with an emphasis on local area network systems.

The second part is concerned with how secondary storage is managed in such systems. It briefly discusses ways in which underlying storage systems can be distributed and controlled, and then presents a scheme for organising data based on the use of long-term typesafe objects. This scheme promises many of the performance benefits associated with conventional files, and yet is able to express complex interrelationships between bodies of data and to cope with the constant change which characterises programming environments.

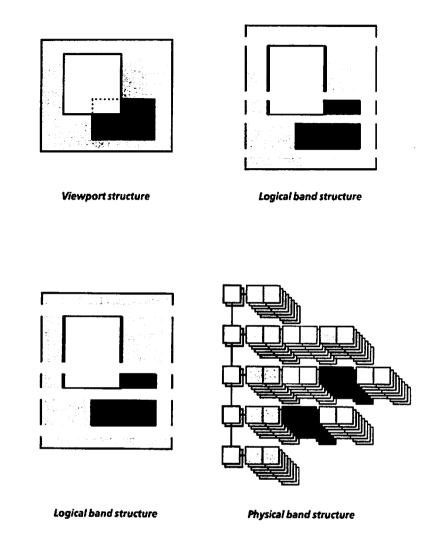

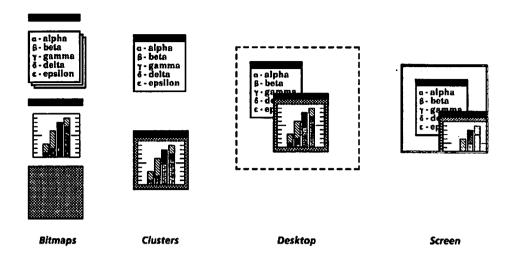

Finally (and this represents the main part of the work described), a partial implementation of a terminal domain is presented, in the form of a design for a graphics workstation specifically tailored to the requirements of local area network systems. The workstation provides hardware support for windowing by dynamically mapping images onto a screen at display refresh time. Most other display systems have to achieve the effect of windowing by image generation techniques, which can consume much of their power if reasonable response times are to be attained. Some of the implementation tradeoffs made by other workers are discussed, followed by the ones that were adopted for the prototype display. Software as well as hardware aspects of the project are covered, and the section concludes with a discussion of possible future work that could be attempted using the system described as a basis.

## PART I

Execution domains

### 2. Execution domains

Execution domains are those components of computer software systems that manage processor and memory resources, typically in order to provide some form of virtual machine abstraction. Such an abstraction serves two roles. It simplifies the environment that a client program sees by removing unnecessary interactions with other clients and a variety of hardware interfaces. It also allows real hardware to be multiplexed between several virtual machines. With separate protection domains available to the domain manager and its clients (provided by a supervisor state, memory management hardware or disjoint physical processors, for example), virtual machine interfaces can be enforced; without them, they can only work by consensus.

### 2.1 Non-networked systems

If an execution domain is to encompass many physical machines, methods for resource allocation amongst them are necessary. Two extreme methods can be observed: loosely coupled systems with a collection of largely autonomous processors and no overall execution domain; and tightly coupled systems where a single global execution domain manages physical resources to present the illusion of a single, large system. The systems that have been built to run on local area networks cover most points between these two, and will be discussed further below.

Loosely coupled systems are by far the commonest arrangement. Their components can usually be viewed as almost disjoint systems. Workloads and resources are physically partitioned at system installation time, with little or no opportunity for automated resource management. Consequently, they will not be considered further in this discussion.

Tightly coupled systems demonstrate a range of techniques for achieving the illusion of a uniprocessor system. They seem to have two main functions: to enhance the performance of machines in which the central processor unit (cpu) is a bottleneck, and to increase the overall availability of a system by replicating some of its components. The first function is achieved in two different ways, both of which typically make use of shared memory as the communication medium. In one scheme extra processors, akin to the main cpu, are added to increase the raw instruction execution rate. There is usually less than a unit increase in throughput for each cpu added because of memory contention: for example, a dual processor IBM 370/168 runs only 1.8 times as fast as a uniprocessor. The other scheme

adds specialised processors to offload some particular part of the main processor's workload, such as input/output or floating point manipulations. Increasing the availability. of a system by replicating some of its components needs a somewhat different approach. The first step towards this goal is to limit the interactions between components at the hardware level, to reduce the likelihood of correlated failures. The second is to replicate critical components such as processors, interprocessor links like backplane buses, device controllers, and controller ports on the devices themselves. Additionally, data may be replicated by writing multiple copies of it onto separate devices, either simultaneously or by using some form of stable storage protocol. Finally, mechanisms for failure detection are crucial if recovery is to be initiated before any erroneous outputs have been generated or acted upon.

### 2.2 Local area network systems

The degree of coupling in a system is largely a reflection of the amount of communication between its components. Loosely coupled execution domains are often a product of links with low bandwidth or high latency, while shared memory and high-speed interprocessor buses encourage more tightly coupled domain management. Developments in communication technology have made possible local area networks that combine some properties of both wide-area and high-speed links: physical extents of about a kilometre and bandwidths in the range 1-10 MHz are readily achieved with very low error rates and small signalling delays. Much greater bandwidths are likely to be commercially available in the near future as the result of developments in fibre optics. Examples of extant LANs include the Xerox Ethernet [Metcalfe76], the Cambridge Ring [Wilkes79, Needham79], and the token rings used by Apollo and the Distributed Computer System [Apollo81, Farber72]. Such networks provide sufficiently high bandwidths and signalling rates to allow the construction of global execution domains that extend across the whole network. (Even though its bandwidth and size are not characteristic of local area networks, the ARPANET [Heart70, McQuillan77] has been used in this fashion [Thomas73, Cohen74]. Indeed, the ARPANET can itself be thought of as running a single distributed computation in a large global execution domain encompassing its switching processors.)

The distributed system designs that local area networks make possible rely upon powerful, cheap processors based on very large scale integration (VLSI) technology. The cost of a machine is to a large degree dependent on the level of integration achieved in its logic circuitry, because hardware cost is related almost entirely to the number of chips rather than their complexity. The level of integration that can be achieved for a particular machine is dictated by the absolute performance required, because of the need to use different technologies for each performance class. It is still the case that higher performance is only achieved at the expense of integration levels (assuming similar architectures). In 1980, integration levels of roughly 68 000, 2 000 and 500 transistors per chip were achieved for a microcomputer, a mainframe and a super-computer respectively [Agnew82]. As technologies improve, so does performance at a given integration level: some of the new VLSI-based microcomputers are beginning to rival traditional 'minicomputers' in power [Hansen82]. The current architectural trend towards reducedcomplexity designs is likely to result in an increase in the absolute performance achievable at a given integration level. One consequence is that Grosch's Law-that the power of a machine is proportional to the square of its price-no longer holds [Grosch53, Kelly-Bootle81, Siewiorek82a, GordonBell82]. Rather than running many unrelated applications on a single, large mainframe, it is often more economical to divide up the workload and use the smallest machines that can handle the parts in a reasonable elapsed time. A persuasive argument for this strategy in the business community is the freedom it offers to distribute processing power and data to match organisational structures. Sometimes this concern is even more important than cost [Clark80].

The price and performance advantages of small processors are not yet reflected in peripherals, where economies of scale still predominate. LAN-based operating systems can take advantage of the availability of cheap processing power that can be distributed as required, and still reap the benefits of concentrating most peripherals onto a few server machines that make their resources available to the rest of the network. In addition, more absolute performance may be required than is available from current-generation VLSI processors, and so there may still be a need to centralise large-scale computing power.

There are many approaches to building local area network systems, although locational transparency for at least some resources seems to be a common goal. One group of systems is constructed from machines that have their own peripherals, no one site being distinguished in the role of server to the others (e.g. SODS/OS [Sincoskie80] and LOCUS [Popek81]). A few examples emphasise the migration of processes to balance the processor load across the nodes (e.g. [Casey77] and SODS/OS). This first group is characterised by

the highest degree of locational transparency, often presenting what looks like a generic timesharing system interface to its users with no indication of where data are being processed, stored or otherwise manipulated.

A second group is formed by those systems that provide locational transparency for only a few services, with processors and filing systems not usually amongst them—instead, these functions are supplied on a node dedicated to an individual user. The network is used only for relatively infrequent sharing operations, often on explicit user request. Xerox, at their Palo Alto Research Center (PARC), were probably the earliest proponents of this 'personal computer' scheme. Since then, several systems have been modelled on it (e.g. the PERQ [ThreeRivers79], Xerox's own Star [Seybold81], various CAD systems [Versatec83, Werner83], Apple's Lisa [Lisa83], MIT's Nu-machine [Ward80] and the ETH Lilith [Wirth81]).

In the middle ground lie a few systems that aim to combine some of the better features of the two extreme approaches. Examples of this are the Apollo AEGIS operating system [Apollo81] and the software running on the Symbolics LISP machines [Weinreb81]. They both provide locational transparency for resources such as servers and files, but retain the personal computer approach for processing power. Washington's Eden project is aiming in much the same direction [Lazowska81, Almes83]. A slightly different approach is that of the Cambridge Distributed System, where the local area network is used to decouple users physically from all of the central system services—processors as well as file storage, authentication and session management. Once a processor has been acquired for a session it is effectively treated as a personal machine, thus gaining the benefits of simple software and predictable performance, which are the desirable properties of the 'personal machine' approach.

Since the Cambridge and Xerox models form the background to much of the work described in this thesis, a short review of each of them is provided by way of introduction to what follows.

### 2.3 The personal computer approach

The approach adopted by Xerox PARC is based on the view that computing hardware is cheap—so cheap, in fact, that everybody can have a processor. PARC designed a novel computer specifically for this purpose (the Alto [Thacker81]), made it suitable for putting into an office, gave it a local area network connection so that it could communicate with its fellows, and built it in large enough numbers that many members of the staff could be given one. The result was a success, for which there seem to be a number of reasons: the personal nature of the machines was popular; they were always available when wanted; their bitmapped screens were capable of providing an engaging, flexible user environment; and there was no advantage to computing in the early hours of the morning. Each machine had a removable disc cartridge, allowing relatively speedy access to local files as well as the ability for a user to move to another machine if necessary (e.g. if one broke down). The local area network proved to be much more important than its designers had originally anticipated, providing access to resources that could not be replicated for every Alto, such as high-quality, high-speed printers, bulk disc storage, and gateways to other networks.

The personal computer approach does not use a machine-based execution domain manager. Instead, human managers take over this role and allocate machines to people on a long-term basis. In practice, there are never enough machines to go around, which leads to slightly more dynamic resource allocation techniques being used—such as sign-up sheets.

One of the major benefits of a personal computer is also one of its limitations: its lower performance bound is the same as its upper bound. By comparison with an environment that is—even only occasionally—resource deficient (such as many timesharing systems) the reduced variability of response time with a personal computer is often cited as a considerable improvement. In practice, the difference is becoming less and less noticeable as greater degrees of multiprogramming are adopted on personal machines. In addition, sufficient resources must be allocated to each individual to cope with their peak processing (and disc and I/O) needs: the time-averaging effect that may be possible in a shared resource system cannot be used. Economically viable personal machines cannot easily do many of the large computations at which mainframes excel, because they are simply not powerful enough. (Processor cycles may not be the bottleneck: I/O throughput or real memory may be the limiting factors in the performance of an application, and these may be independent of the processor power available.) Certain large calculations can be divided up into manageable chunks that can proceed in parallel on a number of small machines [Schoch82]; others are naturally arranged in this fashion (e.g. the stages of a pipe in

It can be argued that the technology of computer hardware is advancing at a sufficient rate for such a static resource allocation policy to be viable before very long. There are two obvious rebuttals that can be made. To begin with, there is always a desire for more processing power than can sensibly be put into an office-like environment. The class of problems that can be addressed by a given cpu cycle rate in reasonable time is limited, often as much by aiming to improve human productivity as by fundamental hardware limitations. There are a number of trends that aggravate this:

- The desire to do more in a given time, such as some human reaction interval or a screen refresh period. An example is the continuing trend towards higher quality graphics: from black and white to grey scale and then colour, with increasing spatial resolution and heightened image realism.

- A wish to perform a fixed set of operations more quickly, especially if they fall into a critical path in a production process. (For example, the machine intensive parts of the edit/compile/debug cycle, or the execution speed of an interpretive system.)

- Absolute limitations on human resources and capabilities may necessitate tradeoffs that would otherwise be considered undesirable, such as the use of automatic program generators or very high-level languages. While such approaches can dramatically increase their users' productivity, they tend to make heavy demands on underlying computing resources. With time they will be used more, simply in order to allow problems to be tackled that would otherwise be insoluble in any reasonable time.

The economic issue (as well as the environmental one) hinges largely upon the current level of technology. Systems that can be built within the limitations of the production technology of their day (such as those exemplified by high chip integration levels) are much more likely candidates for the personal computer approach than ones that cannot. As personnel costs continue to rise faster than hardware ones, 'within' in this sense will encompass more and more functionality from a given level of technology over time. Acting against this trend is the comparable growth in the functional support a person requires to work effectively.

<sup>■</sup> UNIX is a registered trademark of Bell Laboratories.

The set of problems it would be desirable to handle on personal computers is growing rapidly. Today's most advanced hardware may provide sufficient performance to prototype tomorrow's applications, but it cannot usually implement them in a form suitable for largescale dissemination. Its promise is always of better products for the future. Of course, in a few years time, the prototype will be replaced with something of comparable power, consuming a fraction of the volume, electricity and air conditioning load, but there is no guarantee that this next stage will be adequate to serve the needs of applications developed to stretch the prototypes of today. Current trends would seem to indicate that we will continue to traverse this cycle, with each circuit taking several years to complete, although improving VLSI design tools are helping to shorten it a little. The Dorado [Lampson80] is a good example of this: as a prototyping engine for high-performance personal workstations it has been very successful; as an item of office furniture, less so. Environmental concerns have forced the processor to be relegated to a remote machine room, with video cable connecting it to a display and keyboard in the user's office. (Although the cable is relatively cheap, laying it is not; furthermore, the physical separation makes it difficult to add new interactive I/O devices [Pier83].)

There seem to be two consequences of the fact that current technology (realistically, two to three year old technology as far as products are concerned) is unsuitable for the tasks being required of it if the additional constraint of residing in an office is imposed. The first is that personnel costs have not yet risen high enough (or management has not yet acknowledged that they have) to encourage widespread adoption of the expensive solutions that powerful personal machines still seem to be. The second is that there are still grounds for adopting a more dynamic resource allocation policy than the static worstcase provision that characterises the personal computer policy. A scheme that could pool cpu resources as well as peripherals would be very attractive if it were able to timemultiplex them over a community of users while making similar guarantees as the more distributed system about response times and availability. Given such constraints, the physical implementation of a solution should be a secondary concern. There is no question that high-performance machines should be integrated into the computing resources available to users from their terminals—the variances in approach are merely expressions of different beliefs of how best this should be accomplished.

The second major objection to the purely personal approach is that it makes sharing data more difficult than it is with a centralised scheme. In a system with a large shared disc pool it is almost as easy to access another's files as one's own. There need be no replication of files, since everybody can share a single copy. Even if a central file repository is provided for a personal computer environment, it is often more expensive to access a remote file than a local one. A common result is that a copy is taken of items of interest, plus the operating system and utilities. This replication provides speedier access, resistance to failure of the central repository—and great difficulties when an-item has to be updated. In a user community sharing a large body of data, this can be very inconvenient, especially when changes are occurring on a relatively short timescale [Lauer81]. Exacerbating this is the fact that some users may not connect into the central repository until several months after a change is announced. There are some who would argue that this decoupling between updates and private copies of objects is beneficial, because it allows people to ignore 'improvements' they do not like. Unfortunately, while it is relatively easy to implement an isolationalist philosophy on top of a communal service, the converse is not true—at least, not if timeliness of update is to be maintained [Schmidt82]. Finally, the 'programming in the large' technologies all seem to rely upon efficient, speedy access to a communal body of software and data. Data management is simplified considerably if the need to handle physical distribution is not an issue beyond some very low level (it need not be hidden completely, of course). In short, it would seem that the benefits of easily sharing data outweigh the occasional drawbacks.

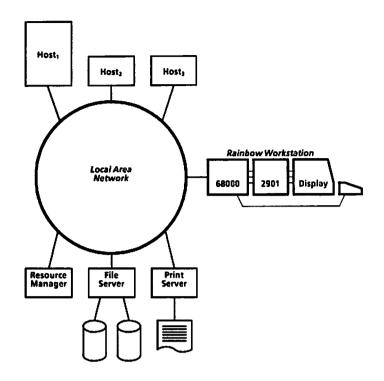

### 2.4 The Cambridge Distributed System

The other LAN-based system to be discussed here is the Cambridge Distributed System (CDS). Its main characteristics are that its components are distributed over a number of machines connected through a Cambridge Ring, and that instead of permanently allocating processors to users, they are pooled into a processor bank and lent out on request [Wilkes80, Needham82]. The distributed nature of the operating system trades off the complexity of providing interprocessor communication against that of sharing one machine between several tasks, and it uses many small (Z80-based) machines to handle just one control function apiece. The simplicity of these machines means that they are both cheap and very reliable. They provide services such as processor bank management (essentially the resource allocation policy part of an execution domain manager), authentication, session management and the multiplexing of a single ring connection amongst several terminals.

The machines in the processor bank are relegated to a (logical) basement and never touched by users: all access is via the ring. Rather than being permanently associated with a single user, they are allocated on request to act as personal machines for the duration of a session. The resource allocator can be informed of the type of computation to be done when a machine is requested, and will attempt to match one of the processors at its disposal to the particular need. A range of machines with different capabilities can be accommodated, and the best use made of each of them. When the load is light, an individual can carry out a limited form of multiprocessing by acquiring more than one processor, each with its own separate terminal connection. (This is almost the only support for an execution domain that extends over more than one machine.) If the maximum number of simultaneous sessions is less than the size of the user community, less hardware need be provided than for the straightforward personal computer approach. This circumstance appears to be a frequent occurrence in many environments.

In effect, by allocating reusable resources (such as machines or disc space) in smaller units, it is possible to time or space-multiplex a larger user community onto the same hardware. The important metric (for processing power) is the difference between the guaranteed and average response times: by making them more and more dissimilar, longer integration periods for load averaging become possible. This approach is taken to extremes on timesharing systems by reducing the timeslice from the duration of a session to a fraction of a second. Intermediate algorithms in which a processor is allocated only for the duration of a command have been suggested, but these either ignore the effects of long-lived programs such as editors (which may tie up a machine for an hour or more), or require that such programs execute in a user's 'home' machine. Significantly improved hardware utilisation would only result if the duration of the commands were to be well below that of the sessions users have with the system. Furthermore, human efficiency is severely compromised if the multiplexing is not transparent below some level: people have state and threads of execution, too, and disrupting them can be irritating and counterproductive.

The CDS provides a central disc repository to avoid many of the problems of replicated data noted with the Xerox approach. To some extent, this organisation was dictated by the late binding of individuals to processors adopted by the CDS. The locally-attached cache of a private personal machine is of little use over any period longer than a session (at least for the storage of private data). Unfortunately, removing the code for handling a local

disc and replacing it by that needed to access the central file server complicated, rather than simplified, the standard ring operating system [Knight82]. It seems that this was largely a result of the need for more complicated error handling machinery in distributed systems, which are much more prone to transient failures of individual components. The underlying LAN is very reliable when running (an error rate of roughly 1 in 1011 is quoted), but surprisingly complex protocols seem to be necessary to cope with the ring's occasional outages and-more importantly-contention at key machines such as centralised resource managers. The CDS as a whole is not notably more robust than a timesharing system because it contains many components that are not replicated (such as the resource and session managers), all of which are necessary for successful operation. On the other hand, high availability should be achievable with lower incremental cost because of the separation of critical components from general processing elements.

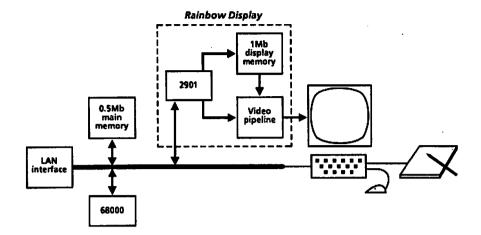

The machines in the processor bank are mostly half-megabyte Motorola 68000 systems, each with a ring interface as its only peripheral. The ring interface contains a 6809 microprocessor, and so is able to carry out a number of housekeeping functions on behalf of the CDS, such as booting and debugging its 68000. The system's emphasis upon supplying raw machines to its users has resulted in certain consequences that affect the design of the remainder of the CDS. One of these is the requirement that no component of the CDS reside in a user's machine, partly because the lack of memory management on the processor bank systems means that there would be no way to protect such software against malicious or erroneous user programs, and partly because it is felt that no restrictions should be imposed on the software run in the machine. In practice, there is encouragement for all user operating systems to support a 'dead man's handle' protocol with the resource manager. The mechanism can be circumvented by choosing a long timeout period, but the advantages of early detection in case of a crash tend to be sufficiently beneficial that this is not often done.

Although there is no intrinsic reason why the CDS could not make use of a sophisticated operating system with memory management to support multiple virtual processors, it does not do so. One reason seems to be the confusion between the need for memory protection hardware and the provision of multi-user operating systems. It has repeatedly been stated that "a personal machine has no use for protection" and this view seems to have coloured the attitudes of the CDS designers. The argument goes that protection is necessary for a multi-user machine, to prevent denial of service or corruption of other users' data, but is unnecessary for a single-user one because there is nobody else to be hurt if something goes wrong. This last is, in my opinion, a non sequitur. Why should users be denied facilities when their machine happens to be personal rather than shared? Many personal machines use multitasking operating systems, and the additional support needed for memory protection or virtual memory is small and relatively well understood, given suitable hardware. Ironically, the CDS processor bank machines are used mostly for program development—which is probably the activity that would benefit most from memory protection. It is also claimed that multi-user operating systems are inherently much more complex than single-user ones, and that this causes difficulties that should be avoided if at all possible. However, the example of VM/CMS on VM/370 shows that provision of multiple virtual machines can be much simpler than a conventional operating system for the same hardware [Donovan75]. The multi-user version of RSX-11M is not significantly more complicated than the single-user version, since almost all operating system primitives have to be provided by both. It is not the multi-user nature of such operating systems that is expensive to provide, but their multi-programming functionality—and this is something that is necessary for all but the most trivial of application systems. Given multiprogramming and process isolation (e.g. via memory management), a multi-user system requires relatively little extra work, especially in systems that already have to deal with authentication issues 'in the large' over the network.

The CDS approach of separating computers from their users seems to work well, given the price/performance ratio of currently available hardware: it does indeed allow more effective use to be made of limited processing resources than can be achieved by permanently assigning them to individuals. The computing power can indeed be hidden in a remote machine room, leading to economies of scale, maintenance, and fewer environmental restrictions. A user can access more processing power than a personal computer could provide, either by using several machines simultaneously, or by being granted control of a large machine for the duration of a session.

There are some areas where the CDS approach has drawbacks. The first is in the performance of the central file system, which seems to be the limiting factor on overall CDS performance. This means that many resource management techniques that would appear attractive at first sight are unusable (e.g. running a command in another free machine than the user's 'home' one, thereby attempting to make still better use of the processor

resources available). The overheads of booting a processor bank machine are considerable: even on a completely empty system, it takes several seconds. (By comparison, RSX-11M takes a fraction of a second to construct a new virtual machine and load a program into it—on hardware roughly comparable to that used by the CDS.) Some of these problems could be alleviated by making use of virtual machines provided by a processor that could support several of them at a time. Of course, a multiprocessing operating system that could isolate its clients from each other's effects would be needed if security and authentication were to be enforced. One advantage to be gained is the much lower initialisation overheads that can be achieved by such systems when setting up a virtual machine. Another is economical support for services for which it would be difficult to justify dedication of a complete physical machine, either because of their very low resource requirements or the infrequency of their use. There need be less concern about tying up the single copy of a resource if the system can build new instances of it on demand. (In practice, the CDS implementation uses this technique for a few specialised applications such as error logging. In my opinion its use should be viewed as a strength, not a weakness.)

The second drawback is that a significant portion of the hardware must be running before the system can be used at all. Whereas an environment of homogeneous personal machines will degrade relatively gracefully when some of them fail, the same is not true of the CDS because its critical components are not replicated.

The final difficulty is the decoupling of processors from the terminals through which they communicate. This sometimes leads to extended end-to-end delays and reduced bandwidth between applications and their users. Some of the techniques that work well in a personal computer—such as a memory-mapped display—cannot be duplicated across a network in a simple fashion (because of bandwidth limitations, for example). Many of these difficulties arise because of the limited amount of intelligence provided at the terminal end. The terminal concentrator provides only a very few, rather primitive, screen management functions, and no full-screen support at all. I would suggest that the view that "it is not, therefore, necessary for computing power to be available in [the user's] terminal, nor indeed if it were would it have any clearly differentiated role to play" [Wilkes80] is no longer tenable if user interfaces with more grace and power than virtual teleprinters are to be supported. The provision of high-quality, timely interaction facilities needs more processing power than a Z80-based terminal multiplexor can supply.

### 2.5 Execution domains—summary

Execution domains come in a variety of shapes and forms. The simplest are those to be found on single-user uniprocessor machines; some of the most complex on tightly coupled multiprocessor machines designed for high availability. Execution domain management for local area networks comes somewhere in between, with a bias in practice towards the personal machine approach. Both the Xerox and Cambridge distributed computing schemes are based on the availability of cheap processing power as a result of recent advances in technology, particularly in the area of VLSI. Each emphasises different areas, each has various drawbacks and advantages. The Xerox one favours guaranteed response time and local computing power at the expense of network transparency in data and processor management. The CDS favours centralised, pooled resources to reduce hardware costs at the expense of locally-available processing power for user interfaces, but tries to make short-term guarantees about response times by dedicating hardware for the duration of a session.

I believe that the CDS approach offers better scope for taking advantage of a range of processor and peripheral hardware technologies, but that it does not (in the form first proposed) offer enough power locally to individuals. This causes signalling delay and bandwidth difficulties when communicating with a simple character display device, and means that there is essentially no mechanism capable of supporting 'dumb' bitmapped displays. If local processing power were to be available, there is some chance that it could remove these infelicities. In particular, by choosing a judicious split between front-end and back-end processing responsibilities, the low-variance response time characteristics of a personal computer could be provided while still taking advantage of the resource pool supplied by the rest of the system. Choosing such a division would entail selecting a useful mid-point between providing too much processing power in the front end (and thus making it expensive to replicate), or too little, which would be unduly constraining in terms of the front-end's functionality. One approach to designing just such a machine is the topic of the latter part of this thesis.

# PART II

Storage domains

### 3. Storage domains

The storage domain component of a computer system is responsible for the management of state whose bulk or persistence requirements preclude the use of (semiconductor) main memory for its implementation. Typical implementation techniques are based on moving magnetic media (discs, tapes, drums), although a few specialised niches are filled by the likes of bubble memories and optical recording methods. As with processor technology, there have been enormous advances in storage subsystems in recent years, with the general trend being towards greater data capacity in both absolute terms and storage density. Coupled with these have been similar—although not so pronounced—decreases in access times and failure rates. One general characteristic remains, however: the time penalty for touching an object on secondary storage is several orders of magnitude greater than if it were in local main memory. This speed dichotomy and the volatile nature of data in primary memory are the main reasons for the traditional existence of the storage domain as such a visible object.

Traditionally, the permanent data storage and speed-differential suppression functions of the storage domain have been interwoven. A 'file system' was used to store permanent data: it was carefully optimised to minimise unnecessary secondary storage traffic, and application programmers were acutely aware of the distinction between primary and secondary memory. With the advent of virtual memory, the visibility of this boundary was reduced, and programmers concerned themselves less with explicit management of dynamic data space, until with the introduction of mapped files in the style of Multics [Organick72], the difference between permanent and dynamic data was eliminated after an initial mapping operation. The logical conclusion of this line of development has been the idea of a workspace in which objects reside, with the implementation completely hiding the distinction between primary and secondary storage. This approach has been used to good effect by some LISP, APL and Smalltalk systems.

The idea of atomicity was found to be a convenient addition to a simple read/write interface. If a sequence of actions is atomic, then either all of the changes effected occur, or none do. When they do occur, they behave as though they were made visible to the outside world at a single instant (all intermediate states are hidden from view). Usually, atomicity is combined with the properties of permanence (once committed, a change will not be lost) and revocability (until a change is committed, it may be undone). The major benefit of atomicity is that it guarantees certain behavioural properties when updates are

made to a shared pool of data, and thus acts as a framework for such operations (in much the same way that serial execution of instructions in a uniprocessor forms the framework for conventional programming).

A property of most implementations of atomicity is that they introduce a distinction between transactional storage and 'ordinary' storage that does not support atomic operations. Main memory usually comes into the latter category, although some memorymapped architectures can provide somewhat finer granularity. One reason for the distinction is that there are often considerable performance gains to be had from using non-transactional storage [Mitchell82]. In the past, transactional storage has largely been associated with so-called database systems, which usually also provide rather elaborate data structuring and manipulation facilities. More recently, the trend has been towards supporting transaction facilities at a lower level so that they are available to more clients; several file systems have been built with varying degrees of sophistication in this regard [Sturgis80, Dion81, Popek81]. To date, transaction support does not seem to have been provided for workspace-oriented environments.

Since real transactions take non-zero time to execute, a mechanism for enforcing their serialisation is useful, and some form of locking is generally used for this purpose. Lock granularities and locking strategies vary; all attempt to maximise throughput and take the greatest advantage of available concurrency while retaining the serialisability property of transactions. As always, there are tradeoffs to be made between the potential benefits of increased parallelism and fewer deadlocks on the one hand, and the costs of administering finer granularities or more elaborate strategies on the other.

An important concern for the implementors of a storage domain in a distributed system is data location—be it explicitly visible or hidden inside the virtual address system. Storage sites can be distributed in much the same way as processor power is, although economies of scale in the cost and performance of peripheral devices favours concentration rather than dispersement. Some existing systems have opted for a purely decentralised approach (e.g. the early Alto environment at PARC, the current Lilith one at ETH), some for a purely centralised one (e.g. the Cambridge File Server), and some for partly centralised ones (e.g. a Xerox Star system with a shared file server). A few (like LOCUS and Aegis) provide network-wide locational transparency for data. The majority of systems that are not purely centralised use local storage as a cache for a central repository, which

may itself be a multi-site entity (e.g. the Xerox DFS [Sturgis80] and proposed Spice file server [Accetta80]). Cache management may be visible at the user level or not, depending upon the particular implementation.

Support for multiple storage sites offers the ability to increase the availability of data through replication. Failure modes common to all systems include media and storage hardware failures; in a network environment, server crashes and network partitioning are also potential sources of trouble. Physical distribution may provide assistance with the latter two, but also introduces problems that a single-site system does not have. Careful attention needs to be paid to the difficulties that multiple updatable copies of replicated objects can bring to algorithms and consistency-and this applies to those location strategies that make use of caches as well as those that just replicate permanent data. The problems are similar to those encountered in shared-memory multiprocessors with separate hardware caches, and the solutions proposed to date for secondary storage management have many of the same properties as their hardware counterparts. There are a few differences, however. For example, sufficient information may be available about the semantic content of data held by a storage domain for relaxed updates to be usable (cf. LOCUS, Grapevine [Birrell82] and the Xerox Clearinghouse [Oppen81]). Also, continued operation in the face of network partitioning is not usually a characteristic of tightly coupled multiprocessor systems.

### 3.1 Files

The previous section concentrated on the lower-level facilities that a storage domain might supply. Once they are provided, how should the interface to client programs best be organised? Of course, the answer to this depends to a large degree upon the problem domain being addressed: batch payroll programs are likely to have different requirements than interactive syntax-directed editors or program development environments. I choose to limit the scope of the discussion here to the requirements of an "(experimental programming) environment" in the sense of [Deutsch80]; nevertheless, much of what is to follow is of more general applicability.

The commonest abstraction presented by storage domains is that of a *file*, which usually has properties like its size, creation time, and stored data, and may include a particular record structure and owner or protection information. Most traditional storage

domains encourage the use of an access method to manipulate the contents of a file; these have roughly the status of an abstract type manager although the long-term binding between manager and instance of state is usually weak or non-existent. It is often observed that clustering of the data associated with the properties of a file is beneficial to performance. A common implementation technique is to store such information in a file header, which also contains pointers to the user-data property. The principal disadvantage of this scheme as far as a experimental programming environment is concerned is that the list of stored properties is fixed by the storage domain manager. (One counter-example is the Symbolics Lisp machine file system [Symbolics81], but this restricts user properties to less than 512 bytes, including their tags.) To extend the properties (with distributed dependency trees or time evolution maps, for example), another way has to be found to store the new information. Invariably one of two things then happens: either the standard utilities (such as compiler, spelling corrector, linker) have to be modified to cope with a new user-data format, or a different set of utilities are not cognisant of the need for special action engendered by the use of a second file to store the extra data. The classic example of the latter is a copy program.

The difficulties here appear to be arising because traditional storage management schemes do not distinguish between accessing information and accessing its representation. They mainly concern themselves with the latter problem, and give little or no support for the former. When representation schemes were sufficiently simple, this tactic was not at all bad—indeed, very successful systems have been built in just this fashion, with all the clients agreeing in advance how some datum is to be stored, indexed, and interlocked to prevent inadvertent corruption. However, this approach becomes less and less attractive as the complexity of software systems increases. Numerous practitioners have observed that procedural, rather than data-structure, abstractions alleviate many of the difficulties noticed with the earlier system. They also lend themselves better to current language design methodologies, and so it seems only natural to ask how they could best be applied to this problem.

One of the first issues that arises is that of binding: if a representation is to be accessed only via a procedural interface then some way is needed to tie the data and its associated interface together. A single procedural abstraction can often be used to access many individual data items, and so it becomes worthwhile to separate the interface from the

data—i.e. the binding is not a simple agglomeration of the two into one structure. Some form of indirection is needed, and this in turn requires a naming mechanism that can identify the object being referred to.

Returning for the moment to traditional storage domain systems, observe that the majority provide only textual naming schemes, designed to be (more or less) human-oriented. Unfortunately, these are usually unsuitable for the binding required-here, being neither unique over space or time, nor convenient or efficient for machine-oriented manipulation. The latter problem is easily solved by adopting some internal binary identifier structure that is fixed-length, compact, and relatively easy to look up; the former is worthy of a little more consideration.

Why is uniqueness required of the naming scheme—or, more correctly, what are the naming domains over which uniqueness is to be preserved and what are the consequences of failing to do so? The latter is the easier question to answer: failing to guarantee uniqueness over the chosen domain means both that the wrong object may be selected for an operation and that there will be no general way to detect this (other than by observing the potentially catastrophic errors that may result). If locationally transparent access is desired, then space uniqueness for names is usually a prerequisite. Given this as a goal, it seems desirable to advocate an identifier format that is globally unique—i.e. the domain over which uniqueness is guaranteed is the universe of computer systems. This will ensure that the uniqueness property will not be compromised when two existing systems are joined. It will also allow objects to be migrated freely between systems without fear of name conflicts.

The justification for uniqueness over time is the need to identify specific instances of data, not just the most recent one. An obvious example occurs when a module that has long been linked into a program is to be debugged, and the symbol table information that corresponds to the instance of the module at hand is needed. Time uniqueness can be achieved by encoding a timestamp into a name, but more efficient techniques are available that consume fewer bits to similar effect. In the same way that globally space-unique identities are implicitly limited to the space currently reachable by man, a time span needs to be defined after which recycling of temporally-unique identifiers is acceptable. Values around a hundred years are not too difficult to achieve with reasonable object creation rates, and would appear to be ample given current system lifetime expectations.

### 3.2 Summary

This chapter has presented a short overview of some of the more pertinent aspects of storage domain technology as they affect networked computer systems. The next chapter discusses one possible way of organising storage domains at the next level of abstraction, to build procedurally accessed, typesafe, persistent objects with some characteristics that would seem to make them well suited for use in programming environments.

### 4. Entities

This chapter presents a scheme for organising data and helping with the dynamic aspects of information structuring. It is based on the idea of typesafe *entities*, which play a role roughly equivalent to that of files in a traditional storage management scheme, together with a standardised way of handling the properties of such objects.

### 4.1 Concepts and definitions

### 4.1.1 Entities

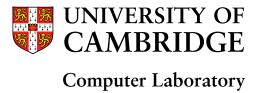

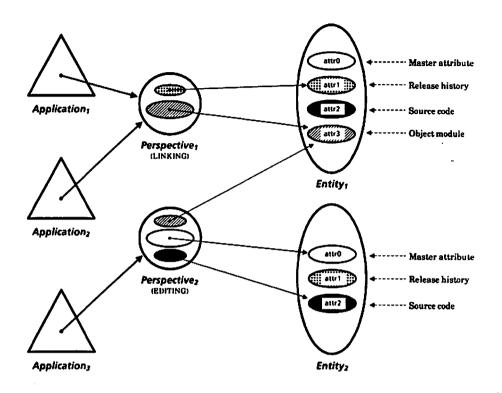

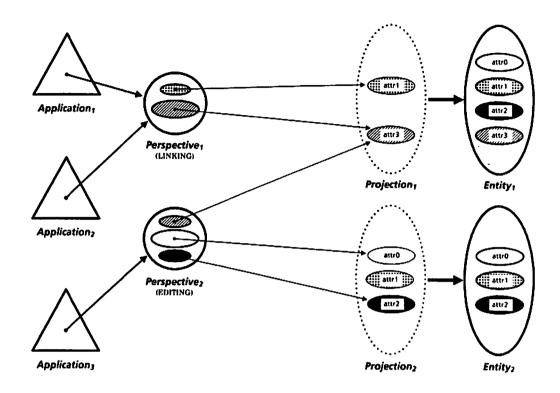

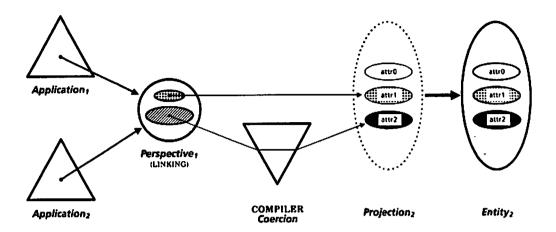

An entity is a named object made up of a collection of attributes, each of which represents some aspect of the whole (figure 4.1). An entity corresponds to a file; an attribute is akin to the individual items of data held by traditional file systems, such as last-modified dates and file data components. Entities are uniquely identified by an entity identifier (or entityID), which is a globally unique name over both space and time. The exact form of these unique identifiers (UIDs) is not particularly important, although it needs to be long enough to supply a sparse name space for many objects if a capability-based access control mechanism is to be used (as envisaged here), and identifiers should be easy to generate in a distributed fashion.

It is convenient to think of entities as containers for attributes. An entity can have more than one instance of an attribute of a given type or class, such as timestamp, but the class is then further qualified to indicate the use to which the attribute is being put (e.g. source code timestamp, object module timestamp). This attribute instance identifier (another UID) must be unique in the entity. (There is no sensible way to support positional attribute identification when the number and composition of the attributes can vary through time.) In effect, this puts an upper limit on what an entity is: it is unlikely, for example, to contain several temporal variants of a piece of text, although it might perform an organisational role and contain pointers to other entities that each hold a variant. (Such pointers would probably be managed by an attribute with a directory-like interface.)

A certain simplicity would result if an entity could be defined as a rigidly typed object in its own right, with its set of attributes (and thus its complete class specification) fixed at creation time once and for all. [Crawley81] proposed just such a model. Unfortunately,

Figure 4.1. Entities and attributes

this simplification is unacceptable since any change to the list of attributes would necessitate a change in the type of the entity, which is inappropriate for the applications envisaged here. To accommodate the kinds of operations that occur in a programming environment, it must be easy to change the set of attributes of an entity. Evolution and change are the norm in program development and systems that model the real world [Atkinson77, Date77, Heering81, Lauer81]. [Schrodt82] reports on the considerable benefits that can be gained from a flexible system.

### 4.1.2 Attributes

Each attribute supplies a typesafe procedural interface to its clients and may have one or more associated values, which it is convenient to have the entity hold on its behalf. Insisting on a procedural interface to an attribute results in an encapsulated data type, and also makes it possible to upgrade an implementation without changing its external interface (e.g. to improve its performance). The encapsulation affords the opportunity to synthesise attributes: for example, two attributes could separately store 'untabbed text' and 'tab stops' in the entity, and another one could merge them on request to produce 'tabbed text'. 'Object module' could be automatically derived from 'source code' and 'compilation control file' by an attribute implementation that invoked a suitable compiler.

One of the attributes is designated as the *master attribute*, and it is this one that receives notification of global operations on the entity itself. It is the only mandatory attribute, and must provide the operations initialise, finalise, open, close, add\_attribute and delete\_attribute, which are interpreted as operations on the entity itself. This scheme avoids the need to handle objects of type 'entity' explicitly. Different kinds of entity can be constructed by using different master attribute classes and implementations; furthermore, this can be achieved without introducing any new mechanisms. The simplest form of master attribute makes no attempt to impose any access constraints upon its clients. An entity controlled by one may be likened to a jungle, as anybody may come up to it and add new attributes. As with introducing animals to a real jungle, adding attributes may be deleterious (to the attribute or to the entity). More selective master attributes can be devised and may be likened to keepers of safari parks, who, presumably, take care to avoid introducing zebras into a lion enclosure.

### 4.1.3 Kernels

Preservation of the typesafeness of entity interfaces is the responsibility of language dependent kernels that execute in some protection domain isolated from their clients. These kernels map a client's operation requests onto invocations of the relevant functions provided by attributes of the target entities. Each entity contains a data area private to these kernels containing the information needed to define the entity's structure: a list of attributes together with their implementations, classes, instance types and state.

### 4.1.4 Implementations and replicas

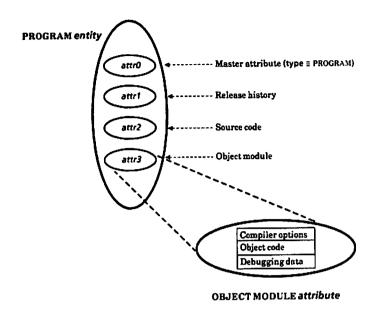

As with languages like Mesa and Modula-2, the *implementation* of an attribute is an object distinct from its specification or class. Each attribute in an entity contains a pointer to the particular piece of code that is its implementation—its *implementationID* (figure 4.2). This binding makes it possible for several different versions of the same attribute class to be active at once, with different organisations for their internal states. Provided the different implementations all adhere faithfully to their class specifications, an external client should be unable to distinguish between them other than in the area of performance. There is no need for an elaborate external version number scheme to determine the correct

Figure 4.2. Attributes, implementations and classes

format of the saved state given to a type manager, as is required in systems in which the binding between state and manager is weak or non-existent. (As [Keedy82] notes, most traditional filing systems fall into this category.) Instead, the entity system provides precisely the correct form of binding in the implementationID for the attribute.

Since it is expected that entities could be used in a multilanguage environment, the concept of implementations is broadened slightly to include *replicas*, which are variants of a particular implementation for different languages, hardware architectures or operating systems. Whereas different implementations of one class need not use the same internal data structures for their saved state, all the replicas of an implementation must do so. All the replicas for an implementation share the same class specification, translated as necessary into different implementation languages.

The implementationID of an attribute is the entityID for the entity that will provide the implementation's replicas, each of which has a separate attribute instance type. Loading an implementation is thus a recursive process; termination occurs because the implementations of the attribute instances that hold replicas (which are known as *loaders*) are bound into the runtime kernel, and so are always memory resident. (Strictly, only the first such

loader need be so bound; provided it can itself load other loaders, the mechanism for a bootstrap has been established.) The binding employed to make the replicas themselves can be early or late: the former would require a link stage to include any needed subroutine modules; the latter external symbol resolution at load time.

Supporting multiple implementations for an attribute type allows its internal data structures to be chosen for optimal performance in a particular application while preserving the external specification. The process that chooses the implementation can be as simple or as complex as desired. ([Sherman83] discusses some of the issues involved.) It clearly has to be driven by performance and behavioural advice from the particular application; in the absence of such hints, some default implementation needs to be identified. If the initial guess is wrong and it is important to correct it, the data held by an attribute must be copied (and hence reformatted) into another one that then replaces it. That this is possible is a consequence of the late binding of attribute instance identifiers to the implementation and saved state of the attribute. The longevity of the binding between entityIDs and entities means that doing the same for complete entities is only possible if there is a similar indirection between the entityID and the underlying storage (of which more below).

The very late binding to implementations means that the most recent version of an attribute (complete with the latest bug fixes) is used whenever an entity is accessed. Some care thus needs to be exercised: much of the benefit of the scheme can be lost if implementations are 'improved' in situ in a cavalier fashion. Optimisations for one particular access style might prove to be the exact opposite for another. Rather, a new implementation should be made available for use by new objects as they are created; if desirable, it may also be made the new default.

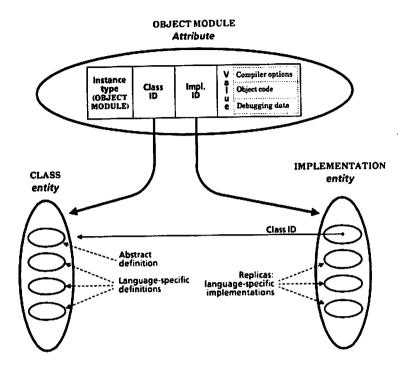

### 4.2 Storage objects

The two major roles of the entity system are to provide state storage and to organise its access. A convenient internal abstraction is that of *storage objects*, whose sole purpose is to handle state saving [Crawley81a]. Each storage object provides storage for the attributes of a single entity by supplying one or more *value stores*: simple, indexed byte arrays with a flexible upper bound (figure 4.3). Each value store is tagged with the identity of its owning attribute, so that it can be garbage collected in a simple way. The

storage object contains a data area private to the entity kernel in which the latter stores the description of the entity structure, including the classes, implementationIDs and instance types of the attributes.

Each storage object resides on a storage medium under the control of a storage manager that is responsible for whatever is necessary to handle a particular underlying storage resource. Storage objects, like entities, have unique identifiers (storage object identifiers or SOIDs), which contain a medium identifier and a medium-specific handle onto the storage object itself. It is expected that the number of storage medium instances will be small compared to the number of storage objects; nevertheless, relatively lengthy medium identifiers may still be convenient in order to simplify UID generation when using a distributed name generation scheme.

To a first approximation, SOIDs and entityIDs are identical: both can uniquely identify an entity and its saved state. The main reason for distinguishing SOIDs (which are largely internal names) from entityIDs (which are freely available to applications and attribute implementations) is that the latter will contain access-rights information that the former do not need. The primary protection model envisaged for entities is a capability-like one, with different instances of entityIDs for the same object conferring different access rights to their wielders. A simple way of achieving this is to concatenate an encoded representation of the access rights (such as a value in a sparse address space) onto a name (such as a

Figure 4.3. Storage objects

SOID) that merely identifies the subject entity. It might also prove convenient to provide an indirection between the name of an entity and the name of its storage object, so that the latter can be migrated or replicated for greater reliability, availability or performance. This could be provided on per-storage medium basis, but it may be more convenient to have it available for all entities in the system.

I choose to assume that storage managers may perform asynchronous garbage collection, mainly because of the advantages that implicit object management brings with it [Deutsch80]. The cost of insisting on a suitable interface to the storage object level is relatively low; more importantly, non-compliance early on is not easily rectified if the decision is later reversed. An asynchronous garbage collector needs some structure in common between itself and the entity system that the former can traverse during its nodemarking phase and that the latter can use to ensure the continued existence of storage objects. One of the simplest such arrangements is the inclusion of a link store in the kernel-private portion of each storage object. Putting an SOID into a link store that is itself accessible by following a path from the root node would ensure the continued existence of the storage object named by the SOID. Only SOIDs in link stores would have such existence properties. (The construction of an entityID from an SOID and an accessrights field simplifies this; the garbage collector only needs the SOID portion.) One consequence of this arrangement is that an attribute can act as a directory by providing a mapping between names and entityIDs in the form of SOID/access-rights pairs. Most existing file systems completely separate directories (or indices) from data files; in the entity system there is still a distinction, but it is made intra-object rather than interobject. Like a value vector, a slot in the link store is tagged with its owning attribute.

### 4.2.1 Providing value stores

Strategies for building and maintaining vector-of-byte storage abstractions are relatively well understood, and have formed the basis of file systems for some time now. However, there are some relevant second-order effects that result from the data access clustering assumed by the entity model. A basic tenet of this model is that data can (and will) be organised in a way that causes accesses to be grouped more or less tightly around a relatively small number of named centres—the entities. If, as seems likely, the overheads of name resolution and address binding for an entity are comparable to the costs of file

location in a more traditional system, benefits will only be achieved by making the cost of subsequent accesses to internal value and link stores small by comparison with those of accessing other entities. Such efficiency is clearly important for small attributes, since they will be quite numerous; potentially large ones should also be handled without overt penalties in time or space, preferably without the implementation appearing different to client applications.

One possible storage manager implementation would allocate byte arrays (value stores) completely independently of one another, regardless of their size. Whilst the simplicity of such an approach is attractive, as well as its trivial mapping onto an existing file system, lookup overheads and disc fragmentation would pose severe problems. An alternative might be to build each entity on a single traditional file (provided by some existing disc management system) and have the storage manager do its own division of the file into multiple value stores. This is almost as unsuitable as the first: many optimisations that can usefully be applied to a real storage medium (such as locality of reference) are inappropriate for a virtual one because they require knowledge of physical layout, which is precisely the information that the file abstraction is hiding.

The suggested approach is something of a compromise, and relies upon the assumption that many attributes will know in advance some details about their likely storage requirements. The problem is one of choosing some common abstraction that can be used to represent this knowledge that is both sufficiently general to be a worthwhile performance hint and at the same time simple enough to be easy to generate.