#### Specification and Verification II

- Topic of course is the Specification and Verification of Hardware

- Assumes familiarity with Specification and Verification I (which concerns software, particularly using Hoare logic)

- The two courses are really a single course

The notes contain general and background material for the course. Some of the material in them may not be covered in the lectures. Some details and examples are only presented in the lectures. The examinable material is what is actually covered in the lectures

#### Starting today

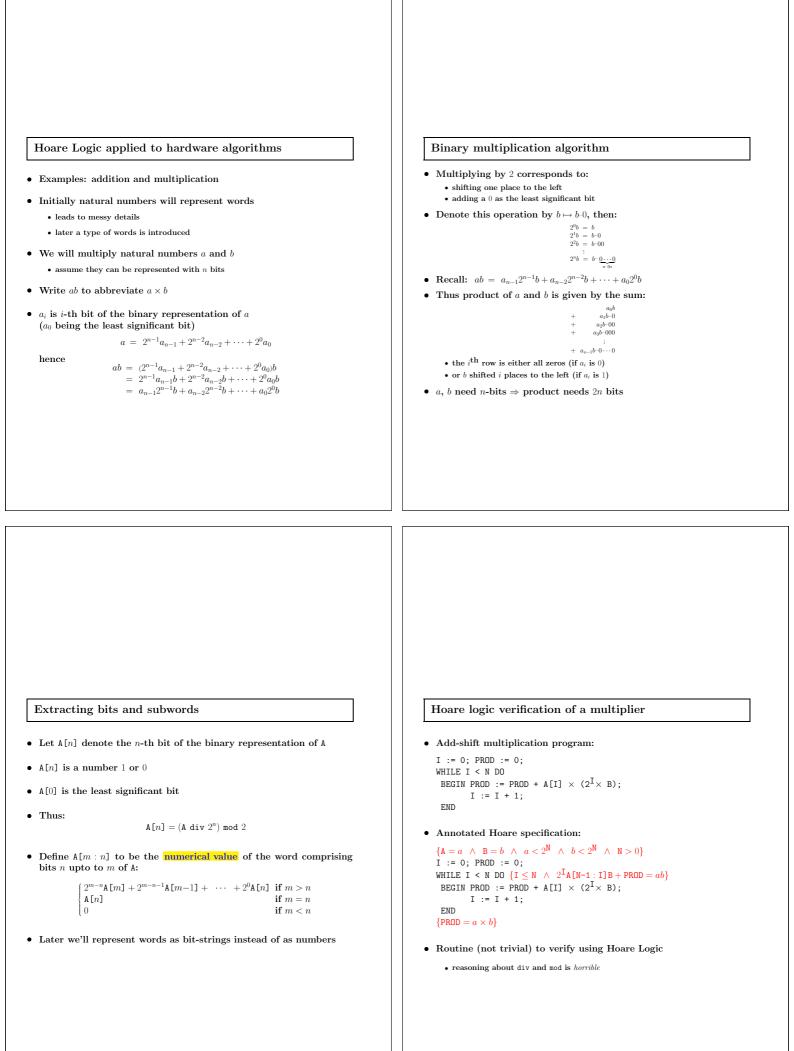

• Hardware oriented Hoare logic examples

• apply Specification and Verification I ideas to hardware

- Modelling data

- words as numbers or as bit arrays

- Programs as hardware

- synthesis to state machines

- Compare program behaviour with hardware behaviour

intermediate states visible

- Motivate temporal logic

- need to specify more than relationship between input and final result

#### Hoare Logic, Higher Order Logic and Temporal Logic

- Hoare logic can be used to verify programs in HDLs

- Hoare logic can be embedded in higher order logic

• see last part of Specification and Verification I

- Higher order logic will be used to represent hardware structures

- Temporal logic (see later):

- is used to specify properties

- can be embedded in higher order logic

- Hoare Logic is for data reasoning, temporal logic for time (control)

- Need to chose appropriate logic all live inside higher order logic

- Goal: software and hardware modelled in same language

- hardware description languages get programming features: ...SystemVerilog

#### Hardware Oriented Programs

- Hoare logic can be used to verify hardware algorithms

- can reason about programs to develop hardware

- not yet 'Industry Standard' practice

- interesting research direction: applications to hardware/software co-design?

- Hoare logic *ideas* appear in some industrial methods

- Intel's Symbolic Trajectory Evaluation (STE) {stimulus} <hardware model> {response}

- Assertion Based Verification (ABV) for hardware annotates HDL source with assertions

#### Using FOR-commands instead of WHILE

```

\vdash \{\mathbf{A} = a \land \mathbf{B} = b \land a < 2^{\mathbf{N}} \land b < 2^{\mathbf{N}} \land \mathbf{N} > 0\}

PROD := 0;

FOR I := 0 UNTIL N-1 DO

BEGIN PROD := PROD + A[I] × B;

B := 2×B;

END

{PROD = a × b}

```

- Program corresponds directly to hardware (i.e. more like HDL)

- three registers A, B and PROD

- initially PROD is set to 0

- A and B contain numbers to be multiplied

- I-th step of the multiplication:

- adding A[I]  $\times$  B to PROD

- then shifting B one bit to the left (i.e. multiplying it by 2)

## Textbook multiplier

• Simple textbook add-shift multiplier:

- Optimised version of naive algorithm

- Can apply Hoare logic methods to verify correctness

- see notes for (horrible) details of Hoare-style proof

#### Words as bit-strings (see notes for full details)

- Distinguish words from numbers different type

Advantages: corresponds more to intuition words have a size

Disadvantage: can't use off-the-shelf theory of arithmetic

- Size of a word is denoted by |w|

- *n*<sup>th</sup> bit of *w* denoted by *w*[*n*]

- w[m:n] denotes bits m to n of w

- The word corresponding to a bit b is  $\mathtt{Bw}(b)$

- Bv(b) is the number represented by bit b

- V(w) is the natural number represented by word w

- W n maps number m to the n-bit word representing it

- Concatenation of  $w_1$  with  $w_2$  denoted by  $w_{1-}w_2$

- $w\{n \leftarrow b\}$  denotes a word such that w[n] = b and is identical to w at

- all other bit positions (pad w with 0s at left if n ≥ |w|)

The addition w<sub>1</sub> ⊎ w<sub>2</sub> of w<sub>1</sub> and w<sub>2</sub> is defined by:

- The addition  $w_1 \oplus w_2$  of  $w_1$  and  $w_2$  is defined by  $w_1 \boxplus w_2 = \mathbb{W} (\max(|w_1|, |w_2|) + 1) (\mathbb{V}(w_1) + \mathbb{V}(w_2))$

- b.w equals w if b = T and equals W |w| 0 if b = F

#### Words vs bits

- w[n:n] is the 1-bit word consisting of w[n]

- w[n] : bool

- w[n:n]: word

- Bits and 1-bit words are different types

- The word corresponding to a bit b is  $\mathtt{Bw}(b)$

- Thus: Bw(b)[0] = b

#### **Representing Numbers**

- Natural number:  $b_{n-1} \cdots b_0$  represents  $2^{n-1} \times b_{n-1} + 2^{n-2} \times b_{n-2} + \cdots + 2^0 \times b_0$

- Integer:  $b_{n-1} \cdots b_0$  represents

$-2^{n-1} \times b_{n-1} + 2^{n-2} \times b_{n-2} + \dots + 2^0 \times b_0$

- this is the two's complement representation

- V(w) is the natural number represented by a w $V(b_{n-1}\cdots b_0) = 2^{n-1} \times b_{n-1} + 2^{n-2} \times b_{n-2} + \cdots + 2^0 \times b_0$

- Words can represent other values

e.g. floating point numbers; opcodes

- Bv(b) is the number represented by b

Verification by enumeration

Bv(T) = 1 and Bv(F) = 0

## Arithmetic on bits and words

- The sum of bits a and b and a carry-in bit c

- is computed by  $a \oplus b \oplus c$  (where  $\oplus$  is 'exclusive or')

- and the carry-out by  $(a \wedge b) \vee (c \wedge (a \oplus b))$

### • This is verified by:

$\begin{array}{ll} & \mathtt{Bv}(a \oplus b \oplus c) &= & (\mathtt{Bv}(a) + \mathtt{Bv}(b) + \mathtt{Bv}(c)) \ \mathtt{mod} \ 2 \\ & \mathtt{Bv}((a \wedge b) \vee (c \wedge (a \oplus b))) &= & (\mathtt{Bv}(a) + \mathtt{Bv}(b) + \mathtt{Bv}(c)) \ \mathtt{div} \ 2 \end{array}$

Sum: 1 1 0 0 0 1 0 1 0 0  $1 \ 0 \ 0$ 1 1 0 1 1 0 0 0 1 0 1 0 0 1 1 0 0 0 0 0 Carry:  $1 \ 1 \ 0$ 1 1 1 0 1  $1 \ 0 \ 0$ 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0

Verification of a ripple-carry adder of any size

• Let R be:  $2^{I}Bv(CARRY) + V(SUM[I-1:0]) = V(A[I-1:0]) + V(B[I-1:0]) \land A = w_1 \land B = w_2$

# • Consider the following annotated specification:

$$\begin{split} & \left\{ \mathbf{A} = w_1 \ \land \ \mathbf{B} = w_2 \ \land \ \mathsf{SUM} = \mathbf{W} \ \mathbf{N} \ \mathbf{0} \ \land \ \mathsf{CARRY} = \mathbf{F} \ \land \\ & |w_1| \leq \mathbf{N} \ \land \ |w_2| \leq \mathbf{N} \ \land \ \mathbf{N} > \mathbf{0} \right\} \\ & \mathsf{FOR} \ \mathbf{I} \ := \mathbf{0} \ \mathsf{UNTIL} \ \mathsf{N} - \mathbf{1} \ \mathsf{DO} \ \left\{ R \right\} \\ & \mathsf{BEGIN} \\ & \mathsf{SUM} \ [\mathbf{I}] := \mathbf{A} \ [\mathbf{I}] \oplus \mathsf{B} \ [\mathbf{I}] \oplus \mathsf{CARRY}; \\ & \mathsf{CARRY} := (\mathbf{A} \ [\mathbf{I}] \land \mathsf{B} \ [\mathbf{I}]) \lor (\mathsf{CARRY} \land (\mathbf{A} \ [\mathbf{I}] \oplus \mathsf{B} \ [\mathbf{I}])); \\ & \mathsf{END} \\ & \left\{ 2^{\mathsf{N}} \mathsf{Bv} \ (\mathsf{CARRY}) + \mathsf{V} \ (\mathsf{SUM} \ [\mathsf{N} - \mathbf{1} : \mathbf{0}]) \ = \ \mathsf{V} (\mathbf{A} \ [\mathsf{N} - \mathbf{1} : \mathbf{0}]) + \mathsf{V} (\mathsf{B} \ [\mathsf{N} - \mathbf{1} : \mathbf{0}]) \\ & \mathbf{A} = w_1 \ \land \ \mathbf{B} = w_2 \\ \end{split}$$

- A, B are N-bit words, SUM, CARRY are truthvalues, I is an integer

- Proof horrible (omitted)

# Word multiplication program Topic shift: From programs to hardware (i.e. synthesis) • Simple add-shift multiplication • Consider a ripple-carry adder FOR I := O UNTIL N-1 DO • Annotated correctness specification: BEGIN $SUM[I] := A[I] \oplus B[I] \oplus CARRY;$ $\{ V(A) = a \land V(B) = b \land PROD = W(2N)0 \land \}$ $CARRY:=(A[I] \land B[I]) \lor (CARRY \land (A[I] \oplus B[I]));$ $|\mathbf{A}| \leq \mathbf{N} \wedge |\mathbf{B}| \leq \mathbf{N} \wedge \mathbf{N} > 0\}$ END FOR I:=O UNTIL N-1 DO $\{2^{\mathbf{I}} \mathsf{V}(\mathsf{A[N-1:I]})b + \mathsf{V}(\mathsf{PROD}) = ab \land \mathsf{V}(\mathsf{B}) = 2^{\mathbf{I}}b\}$ • If a particular value of N is fixed, then the program can be unrolled BEGIN into the normal circuit for an adder. PROD := PROD ⊕ A[I].B; B := B-0 • For example take N = 3 to get: END FOR I := 0 UNTIL 2 DO $\{V(PROD) = ab\}$ BEGIN $SUM[I] := A[I] \oplus B[I] \oplus CARRY;$ • Can generate VCs and prove them (horrible – omitted) $CARRY:=(A[I] \land B[I]) \lor (CARRY \land (A[I] \oplus B[I]));$ END Combinational logic N=3 adder 3-bit adder: FOR I := 0 UNTIL 2 DO • Derived program is combinational logic: BEGIN $SUM[0] := A[0] \oplus B[0];$ $\texttt{SUM[1]:=A[1]} \oplus \texttt{B[1]} \oplus \texttt{(A[0]} \land \texttt{B[0])};$ $CARRY:=(A[I] \land B[I]) \lor (CARRY \land (A[I] \oplus B[I]));$ $\texttt{SUM[2]:=A[2]} \oplus \texttt{B[2]} \oplus$ END $((A[1] \land B[1]) \lor$ $((A[0] \land B[0]) \land (A[1] \oplus B[1]));$ Assuming initially CARRY = F; FOR-command unrolls to: $SUM[0] := A[0] \oplus B[0] \oplus F;$ CARRY :=(A[2] $\land$ B[2]) $CARRY:=(A[0] \land B[0]) \lor (F \land (A[0] \oplus B[0]));$ $SUM[1] := A[1] \oplus B[1] \oplus CARRY;$ (((A[1]∧B[1])∨ $CARRY := (A[1] \land B[1]) \lor (CARRY \land (A[1] \oplus B[1]));$ $((A[0] \land B[0]) \land (A[1] \oplus B[1]))) \land$ $(A[2] \oplus B[2]));$ $SUM[2] := A[2] \oplus B[2] \oplus CARRY;$ $CARRY := (A[2] \land B[2]) \lor (CARRY \land (A[2] \oplus B[2]));$ • These are independent assignments Symbolically executing yields logic equations: $\bullet$ boolean expressions for computing the values of SUM and CARRY directly in terms of the A[0], A[1], A[2], B[0], B[1] and B[2] $SUM[0] := A[0] \oplus B[0];$ $SUM[1] := A[1] \oplus B[1] \oplus (A[0] \land B[0]);$ $SUM[2] := A[2] \oplus B[2] \oplus$ • This process yields logic for adders of arbitrary (fixed) bit-widths $((A[1] \land B[1]) \lor ((A[0] \land B[0]) \land (A[1] \oplus B[1])));$ CARRY :=(A[2] $\land$ B[2]) $\lor$ • Hoare Logic verifies any adder generated this way $(((A[1] \land B[1]) \lor ((A[0] \land B[0]) \land (A[1] \oplus B[1]))) \land$ $(A[2] \oplus B[2]));$

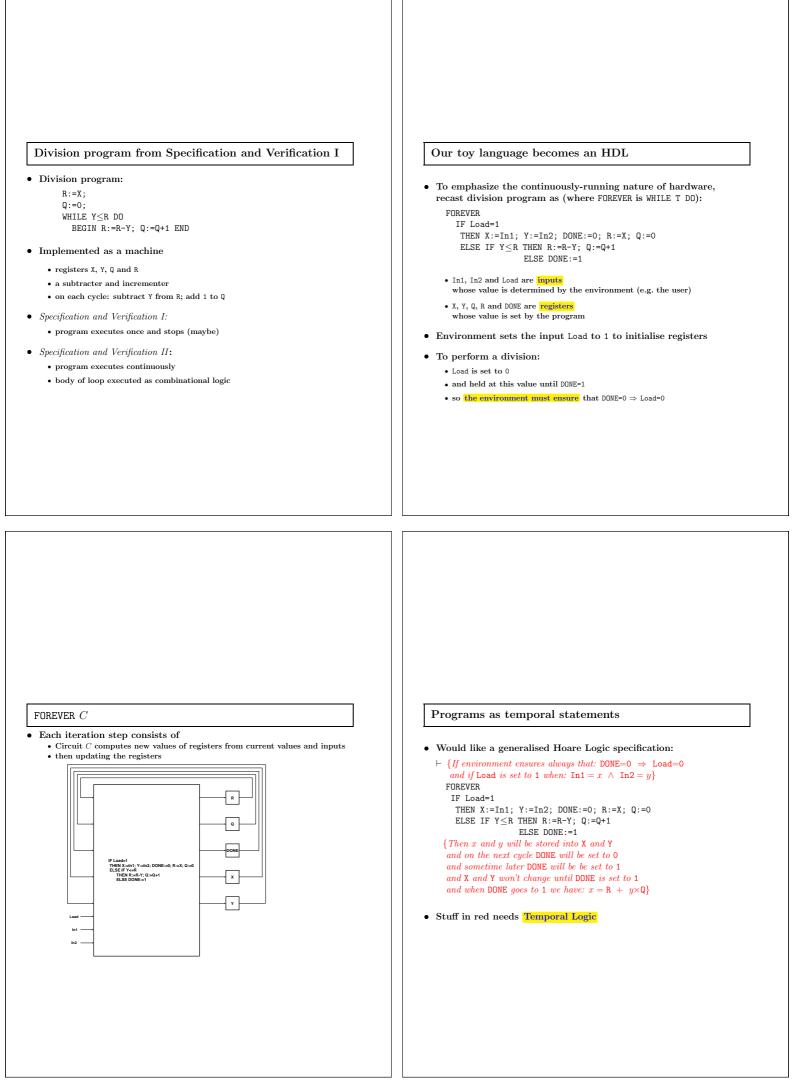

#### What about non-combinational logic?

- Unrolling commands to combinational logic is sensible for the adder

- Less so for multipliers

- straightforward to unroll a multiplier into combinational logic

- but resulting Boolean expressions will be huge

- evaluating in one clock cycle likely to make the cycle time too slow

- Usually multipliers are sequential machines

- compute the product over a number of cycles

- might do the add and shift in a single cycle which would take N cycles

- might do add and shift on separate cycles, taking  $2\mathbb{N}$  shorter cycles

- Decision of whether to implement a particular function as combinational or sequential logic, and if sequential, how much to do each cycle, is a decision which depends on engineering issues

#### Specifying cycles

- Abstract view of multiplier:

- computes a single state change

- from initial values of the registers

- to final values

- Adequate for functional correctness

i.e. it does multiplication

- Less abstract views needed for timing analysis

## HDLs and events

- HDLs allow operations to be scheduled to clock cycles

- Statements can be prefixed by

the symbol

introduces an event control

- Multiplier that takes N cycles: FOR I := 0 UNTIL N-1 D0

R := (R[0].B \overline R[2N-1:N]) - R[N-1:1]

R = CARRY - P - A

- In Verilog, event controls can be more detailed

- @(posedge clk) or @(negedge clk)

# Need more than Hoare Logic

- Programs with added event controls can still be reasoned about using Floyd Hoare logic

- relation between initial and final state unchanged

- $\bullet\,$   ${\tt @}\,{\rm 's}$  just determine intermediate states at clock ticks

```

• Consider this silly program:

FOR I := 0 UNTIL N-1 DO

BEGIN

```

```

•SUM := R[0].B ⊕ R[2N-1:N];

B := ¬B;

•R := SUM-R[N-1:1];

```

- B := ¬B;

- END

- Same initial-final relation, but B oscillates

- Hoare specifications only deal with initial-final relation, not intermediate states

- Temporal logic enables properties of intermediate states to be specified

e.g. B stable (false for silly program above)

#### Brief history of temporal logic

- 1950s: philosophers invent temporal logic (A.N. Prior of Oxford)

- 1970s: Burstall, Pnueli, Lamport use temporal logic for programs

- 1980s: Emerson, Clarke and other introduce model checking

- 1980s: hardware verification examples studied

- 1990s: model checking catches on: Intel hires many logicians for P7 verification. Uses STE. Currently developing higher order logic tools (*reFL*<sup>ed</sup>).

- 1997: Amir Pnueli gets the Turing Award in recognition of his contribution to the applications of temporal logic

- 2004: temporal notation for properties debated and standardised

semantics: CTL versus LTL

syntax: PSL and SVA 'aligned'

- 2005 onwards: Assertion Based Verification (ABV) grows

dynamic checking of properties by simulation (e.g. used at ARM)

static checking by model checking

- 2008: Clarke, Emerson & Sifakis get Turing prize for model checking

- 2008: Clarke gets 2008 CADE Herbrand Award

- Note: work on formal methods leads to high prestige awards!

## Rest of the course

- First look at 'raw' higher order logic for specification and verification

- temporal logic is a notation for specifying properties of traces

- first look at reasoning directly about traces in higher order logic

- Towards the end of the course we return to temporal logic

- look at its constructs

- semantics via a shallow embedding in higher order logic

- look at the 'Industry Standard' logic PSL

- overview some key ideas for model checking temporal logic properties